(54) ЭЛЕМЕНТ ПАМЯТИ

| название | год | авторы | номер документа |

|---|---|---|---|

| Элемент памяти для постоянного запоминающего устройства и способ его изготовления | 1989 |

|

SU1642888A1 |

| ВЕРТИКАЛЬНЫЙ МДП-ТРАНЗИСТОР ИНТЕГРАЛЬНОЙ СХЕМЫ | 1997 |

|

RU2108641C1 |

| БиКМОП-ПРИБОР И СПОСОБ ЕГО ИЗГОТОВЛЕНИЯ | 2003 |

|

RU2282268C2 |

| Способ изготовления полупроводниковых структур | 1990 |

|

SU1774398A1 |

| СПОСОБ ИЗГОТОВЛЕНИЯ САМОСОВМЕЩЕННЫХ ТРАНЗИСТОРНЫХ СТРУКТУР | 2008 |

|

RU2377691C1 |

| ЭЛЕМЕНТ ПАМЯТИ ДЛЯ ПОСТОЯННОГО ЗАПОМИНАЮЩЕГО УСТРОЙСТВА | 1989 |

|

RU1604054C |

| СПОСОБ ИЗГОТОВЛЕНИЯ КМОП ИС БАЗОВЫХ МАТРИЧНЫХ КРИСТАЛЛОВ (БМК) | 1996 |

|

RU2124252C1 |

| Элемент памяти для постоянного запоминающего устройства и способ его изготовления | 1989 |

|

SU1655242A1 |

| СПОСОБ ФОРМИРОВАНИЯ КМОП-СТРУКТУР С ПОЛИКРЕМНИЕВЫМ ЗАТВОРОМ | 1992 |

|

RU2056673C1 |

| СПОСОБ ИЗГОТОВЛЕНИЯ САМОСОВМЕЩЕННОГО БиКМОП ПРИБОРА | 2005 |

|

RU2295800C1 |

1

Изобретение относится к вычислительной технике и может быть использовано в перепрограммируемых постоянных запоминающих устройствах.

Известен элемент памяти с двойным поликремниевым затвором, содержащий полупроводниковую подложку р-типа с концентрацией примеси 2-5-10 см- с высоколегированными областями второго типа проводимости, являющимися сток-истоковыми областями. Между этими областями на поверхности подложки последовательно расположены, образуя многослойную структуру, первый диэлектрический слой/ первый проводящий СЛОЙ, второй диэлектрический слой, второй проводящий слой. Первый проводящий слой полностью электрически изолирован и служит для накопления и хранения электрического заряда. Второй проводящий слой играет роль управляющего затвора. Толщина подзатворнбго и межзатворного диэлектрических слоев 0,1 и 0,15 мкм соответственно (1 .

Недостатком этого элемента памяти является низкая надежность, обусловленная необходимостью использования ультрафиолетового облучения для стирания информации.

Наиболее близким по технической сущности к изобретению является элемент памяти с тройной поликремниевой р.азводкой, содержащий кремниевую подложку первого типа проводимости, включёиощую легированные сток-истоковые области второго типа проводимости и четыре изолированных поликремниевых затвора. Первый управляющий

10 затвор выполнен из первого слоя поликремния и изолирован от подложки слоем диэлектрика. Плавающий затвор выполнен из второго слоя поликремния, изолирован слоем диэлектрика от подложки и первого затвора и перекрывает по крайней мере часть первого управляющего затвора. Второй управляющий затвор изолирован слоем диэлектрика от подложки, первого управляюгощего и плавающего затворов и перекрывает по крайней мере часть плавающего затвора. Третий управляющий затвсэр изолирован слоем диэлектрика от подложки первого, второго управляю25щих и плавающего затворов и перекрывает по крайней мере часть плавающего затвора, причем второй и третий управляющие затворы виполнены из третьего слоя поликремния. Все затворы изолированы друг от друга и от

30

подложки термическим окислом толщиной не менее 0,1 мкм 2,

Недостатком этого элемента памяти является низкая надежность, обусловленная большим временем заряда плавающего затвора и высокими управляющими напряжениями.

Цель изобретения - повышение надежности элемента памяти.

Поставленная цель достигается тем,что в элементе памяти, содержащем подложку, выполненную из полупроводникового материала первого типа проводимости с двумя легированными областями второго типа проводимости, первый изолирующий слой, нанесенный частично на поверхность подложки с перекрытием первой легированной области, первый управляющий слой поликристаллического полупроводникового материсша, нанесенный на первый изолирующий слой, второй изолирующий слой, нанесенный частично на поверхность первого управляющего слоя с перекрытием поверхности подложки, включая частично вторую легированную область, второй управляющий слой поликристалл ического полупроводникового материала, нанесенный на второй изолирующий слой, третий изолирующий слой и нанесенный на него третий управляющий слой поликристаллического полупроводникового материала, третий изолирующий слой нанесен частично на вторую легированную область подложки, второй управляющий слой и частично на поверхность первого управляющего слоя.

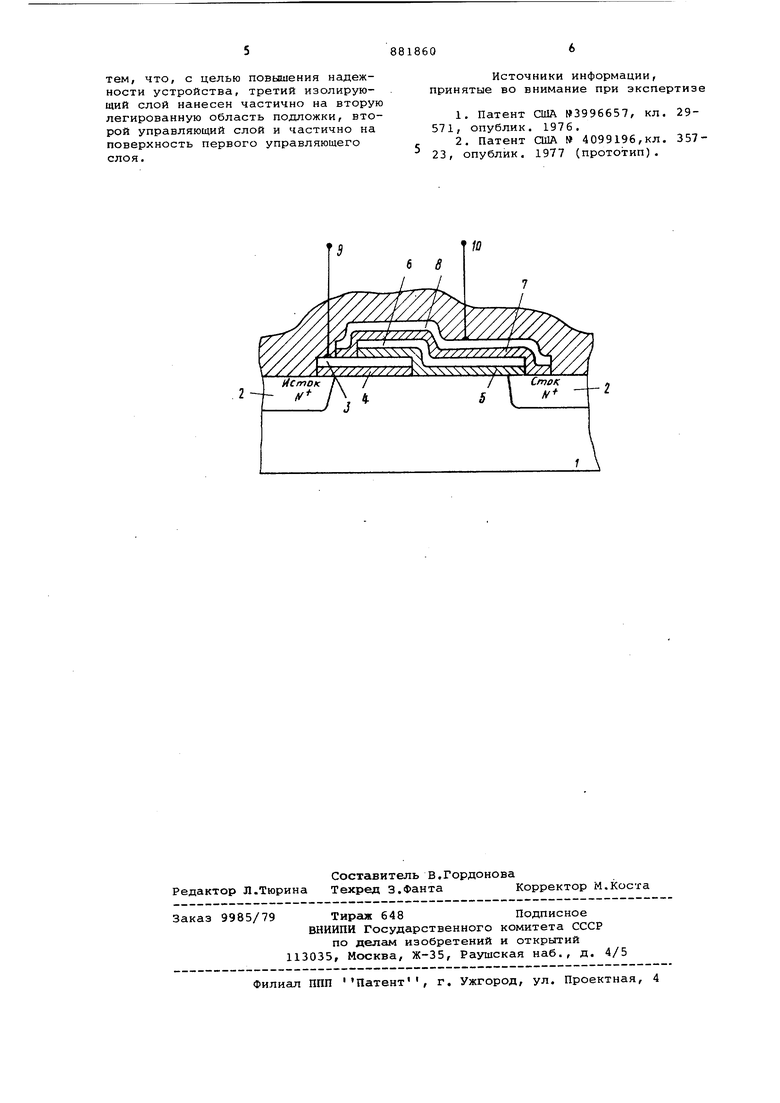

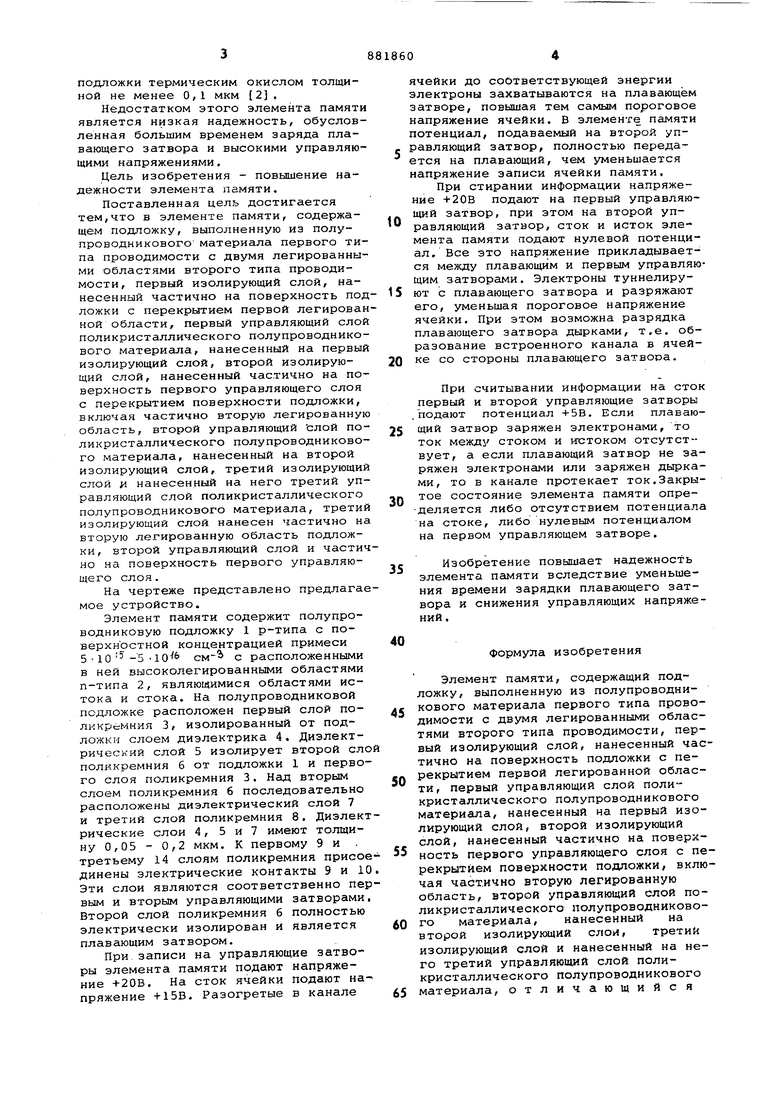

На чертеже представлено предлагаемое устройство.

Элемент памяти содержит полупроводниковую подложку 1 р-типа с поверхностной концентрацией примеси 5 10 -5-10 см с расположенными в ней высоколегированными областями п-типа 2, являющимися областями истока и стока. На полупроводниковой подложке расположен первый слой поликремния 3, изолированный от подложки слоем диэлектрика 4. Диэлектрический слой 5 изолирует второй сло поликремния 6 от подложки 1 и первого слоя поликремния 3, Над вторым слоем поликремния 6 последовательно расположены диэлектрический слой 7 и третий слой поликремния 8. Диэлектрические слои 4, 5 и 7 имеют толщину 0,05 - 0,2 мкм. К первому 9 и . третьему 14 слоям поликремния присоединены электрические контакты 9 и 10 Эти слои являются соответственно первым и вторым управляющими затворами, Второй слой поликремния б полностью электрически изолирован и является плавающим затвором.

При записи на управляющие затворы элемента памяти подают напряжение +20В. На сток ячейки подают напряжение +15В. Разогретые в канале

ячейки до соответствующей энергии электроны захватываются на плавающем затворе, повышая тем самым пороговое напряжение ячейки. В элементе памяти потенциал, подаваемый на второй уп- равляющий затвор, полностью передается на плавающий, чем уменьшается напряжение записи ячейки памяти.

При стирании информации напряжение +20В подают на первый управляющий затвор, при этом на второй упoравляющий затвор, сток и исток элемента памяти подают нулевой потенциал. Все это напряжение прикладывается между плавающим и первым управляющим затворами. Электроны туннелиру5 ют с плавающего затвора и разряжают его, уменьшая пороговое напряжение ячейки. При этом возможна разрядка плавающего затвора дырками, т.е. образование встроенного канала в ячей0ке со стороны плавающего затвора.

При считывании информации на сток первый и второй управляющие затворы

/подают потенциал +58. Если плавающий затвор заряжен электронами, то

S ток между стоком и истоком отсутствует, а если плавающий затвор не заряжен электронами или заряжен дырками, то в канале протекает ток.Закрытое состояние элемента памяти опре0

делается либо отсутствием потенциала на стоке, либо нулевым потенциалом на первом управляющем затворе.

Изобретение повЕлшает надежность

5 элемента памяти вследствие уменьшения времени зарядки плавающего затвора и снижения управляющих напряжений .

0

Формула изобретения

Элемент памяти, содержащий подложку, выполненную из полупроводникового материала первого типа прово5димости с двумя легированными областями второго типа проводимости, первый изолирующий СЛОЙ, нанесенный частично на поверхность подложки с перекрытием первой легированной обласOти, первый управляющий слой поликристаллического полупроводникового материала, нанесенный на первый изолирующий слой, второй изолирующий слой, нанесенный частично на поверх5ность первого управляющего слоя с перекрытием поверхности подложки, включая частично вторую легированную область/ второй управляющий слой поликристаллического полупроводникового материала, нанесенный на

0 второй изолирующий слои, третий изолирующий слой и нанесенный на него третий управляющий слой поликристаллического полупроводникового материала, отличающийся

тем, что, с целью повышения надежности устройства, третий изолирующий слой нанесен частично на вторую легированную область подложки, второй управляющий слой и частично на поверхность первого управляющего слоя.

Источники информации, принятые во внимание при экспертизе

10

Авторы

Даты

1981-11-15—Публикация

1980-03-21—Подача