Изобретение относится к электронной технике и может быть использовано в коммутирующих цепях как аналоговых, так и щфровых полупроводниковых приборов, а также для создания автоматизированных перестраиваемых систем и систем с изменяемой архитектурой.

Цель изобретения - расширение функциональных возможностей за счет обеспечения двусторонней передачи сигнала.

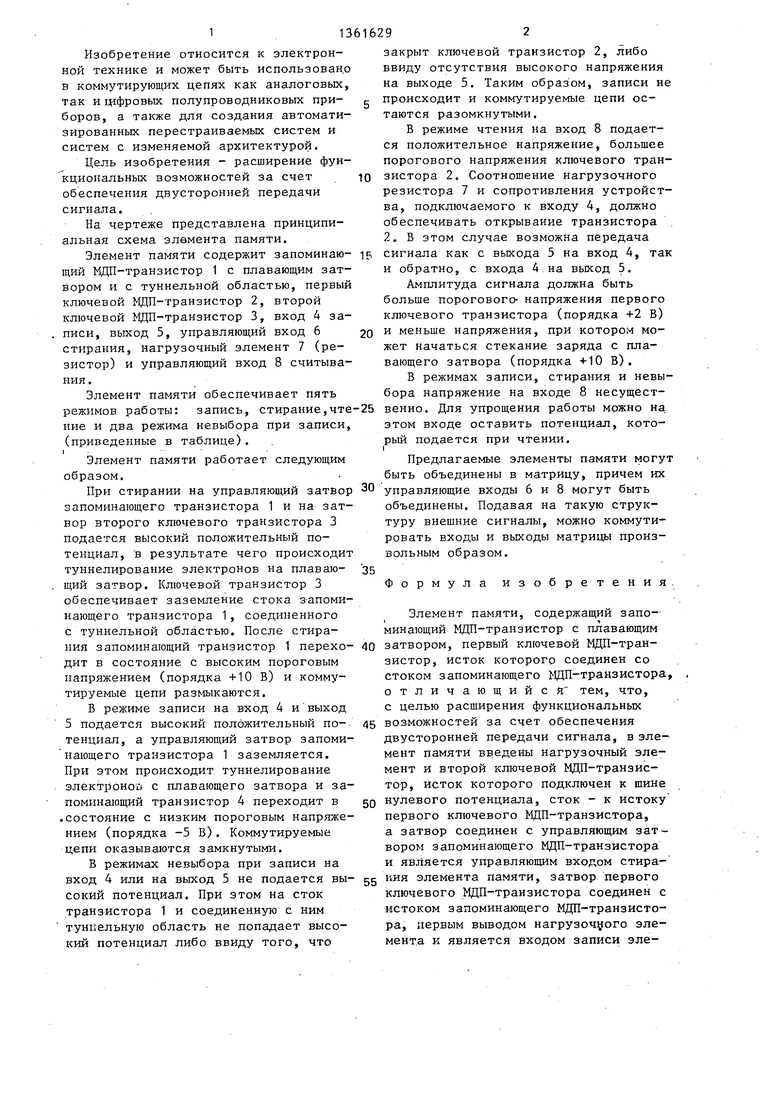

На чертеже представлена принципиальная схема элемента памяти.

Элемент памяти содержит запоминаю- щий МДП-транзистор 1 с плавающим затвором и с туннельной областью, первый ключевой МДП-транзистор 2, второй ключевой МДП-транзистор 3, вход 4 записи, выход 5, управляющий вход 6 стирания, нагрузочный элемент 7 (резистор) и управляющий вход 8 считывания .

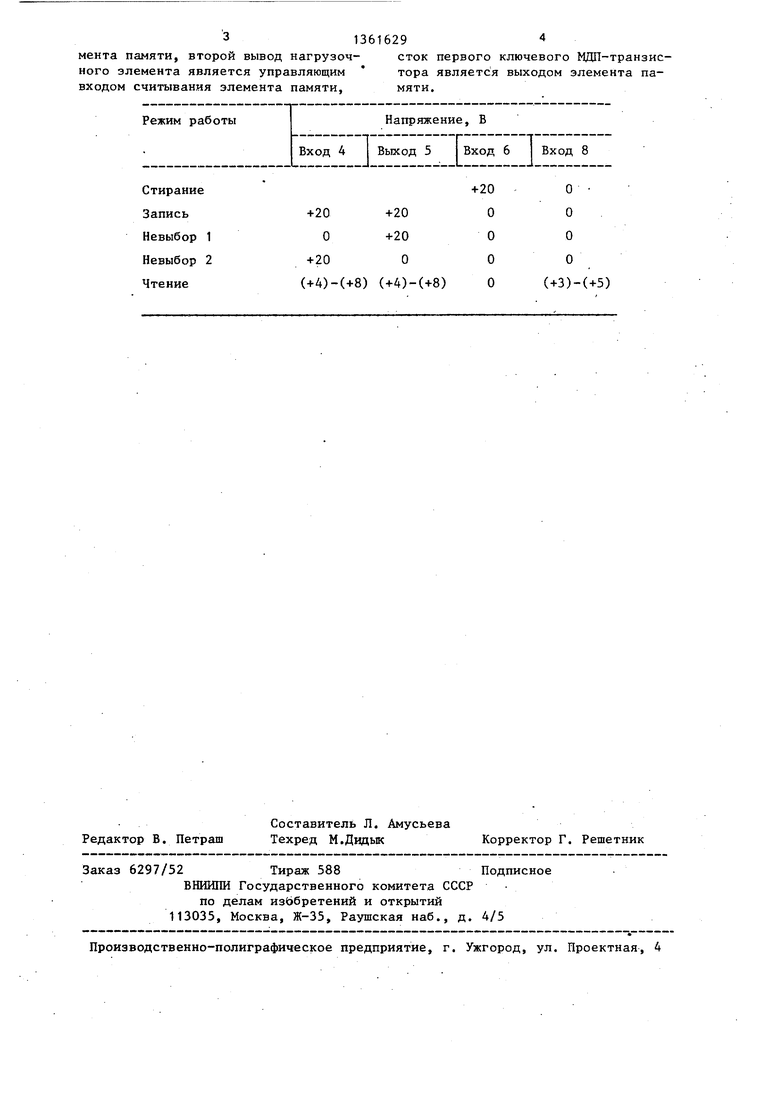

Элемент памяти обеспечивает пять

режимов работы: запись, стирание,чте-25 венно. Для упрощения работы можно на.

ние и два режима невыбора при записи

(приведенные в таблице). i .

Элемент памяти работает следующим

образом.

При стирании на управляющий затвор запоминающего транзистора 1 и на затвор второго ключевого транзистора 3 подается высокий положительный потенциал, в результате чего происходит туннелирование электронов на плавающий затвор. Ключевой транзистор 3 обеспечивает заземление стока з-апоми- нающего транзистора 1, соединенного с туннельной областью. После стирания запоминающий транзистор 1 переходит в состояние с высоким пороговым напряжением (порядка +10 В) и коммутируемые цепи размыкаются.

В режиме записи на вход 4 и выход 5 подается высокий положительный потенциал, а управляющий затвор запоми- нающего транзистора 1 заземляется. При этом происходит туннелирование электронов с плавающего затвора и запоминающий транзистор 4 переходит в .состояние с низким пороговым напряжением (порядка -5 В). Коммутируемые цепи оказываются замкнутыми.

В режимах невыбора при записи на вход 4 или на выход 5 не подается высокий потенциал. При этом на сток транзистора 1 и соединенную с ним туннельную область не попадает высокий потенциал либо ввиду того, что

5

0

закрыт ключевой транзистор 2, либо ввиду отсутствия высокого напряжения на выходе 5, Таким образом, записи не происходит и коммутируемые цепи остаются разомкнутыми.

В режиме чтения на вход 8 подается положительное напряжение, большее порогового напряжения ключевого транзистора 2. Соотношение нагрузочного резистора 7 и сопротивления устройства, подключаемого к входу А, должно обеспечивать открывание транзистора 2, В этом случае возможна передача сигнала как с выхода 5 на вход 4, так и обратно, с входа 4 на выход 5.

Амплитуда сигнала должна быть больше порогового- напряжения первого ключевого транзистора (порядка +2 В) и меньше напряжения, при котором может начаться стекание заряда с плавающего затвора (порядка +10 В).

В режимах записи, стирания и невыбора напряжение на входе 8 несущест5

0

0

5

0

5

этом входе оставить потенциал, который подается при чтении. I

Предлагаемые элементы памяти могут быть объединены в матрицу, причем их управляющие входы 6 и 8 могут быть объединены. Подавая на такую структуру внешние сигналы, можно коммутировать входы и выходы матрицы произвольным образом.

Формула изобретения.

Элемент памяти, содержащий запоминающий МДП-транзистор с плавающим затвором, первый ключевой МДП-транзистор, исток которого соединен со стоком запоминающего ЩП-транзистора, отличающийся тем, что, с целью расширения функциональных возможностей за счет обеспечения двусторонней передачи сигнала, в элемент памяти вв.едены нагрузочный элемент и второй ключевой МДП-транзис- то-р, исток которого подключен к шине нулевого потенциала, сток - к истоку первого ключевого МДП-транзистора, а затвор соединен с управляющим затвором запоминающего МДП-транзистора и является управляющим входом стирания элемента памяти, затвор первого ключевого МДП-транзистора соединен с истоком запоминающего МДП-транзистора, первым выводом нагрузочного элемента и является входом записи эленого элемента является управляющим входом считывания элемента памяти.

Редактор В. Петраш

Составитель Л. Амусьева Техред М.Дидык

Заказ 6297/52 Тираж 588Подписное

ВНИИПИ Государственного комитета СССР

по делам изЬбретений и открытий 113035, Москва, Ж-35, Раушская наб., д. 4/5

Производственно-полиграфическое предприятие, г. Ужгород, ул. Проектная, 4

тора является выходом элемента памяти.

Корректор Г. Решетник

| название | год | авторы | номер документа |

|---|---|---|---|

| Программируемый элемент памяти | 1977 |

|

SU649035A1 |

| Матричный накопитель для постоянного запоминающего устройства | 1988 |

|

SU1531169A1 |

| Формирователь напряжения записи | 1989 |

|

SU1681334A1 |

| Элемент памяти | 1984 |

|

SU1163356A1 |

| Формирователь записи-считывания для запоминающих устройств | 1978 |

|

SU765873A1 |

| Ячейка памяти | 1985 |

|

SU1367043A1 |

| Запоминающее устройство с перезаписью информации | 1974 |

|

SU570920A1 |

| Адресный дешифратор для полупроводникового постоянного запоминающего устройства | 1980 |

|

SU960949A1 |

| УСИЛИТЕЛЬ ЗАПИСИ-СЧИТЫВАНИЯ ДЛЯ ЗАПОМИНАЮЩИХ УСТРОЙСТВ | 1987 |

|

SU1612801A1 |

| МАТРИЧНЫЙ НАКОПИТЕЛЬ ДЛЯ ПОСТОЯННОГО ЗАПОМИНАЮЩЕГО УСТРОЙСТВА | 1981 |

|

SU1025259A1 |

Изобретение относится к элект- :ронной технике и может быть использовано в коммутирующих цепях как аналоговых, так и цифровых полупроводниковых приборов, а также для создания автоматизированных перестраиваемых систем с изменяемой архитектурой. Целью изобретения является расширение функциональных возможностей за счет обеспечения двусторонней передачи сигнала. Поставленная цель достигается введением нагрузочного элемента 7 и второго ключевого МДП- транзистора 3. В данном элементе возможна коммутация цепей между собой при подаче программирующих импульсов по коммутирующим цепям. 1 ил. 1 табл.

| Алексенко А.Г., Шагурин И.И | |||

| Микросхемотехника | |||

| - М.: Радио и связь, 1982, с | |||

| Способ получения нерастворимых лаков основных красителей в субстанции и на волокнах | 1923 |

|

SU132A1 |

| Электроника, 1980, № 25, с.49-50. | |||

Авторы

Даты

1987-12-23—Публикация

1986-07-03—Подача