Известны сумматоры параллельного действия с одновременным переносом, дешифраторы переноса которых состоят из диодно-трансформаторных вентилей со встречным включением обмоток.

В предлагаемом сумматоре для упрощения каждый выход дешифратора переноса соединен через схему «ИЛИ» с вентилями, соответствующими всем предшествующим разрядам. Один вход каждого вентиля подключен к выходу переноса предыдущего разряда, а второй через диодную собирательную схему - к выходу триггера данного разряда и к аналогичному входу последующего.

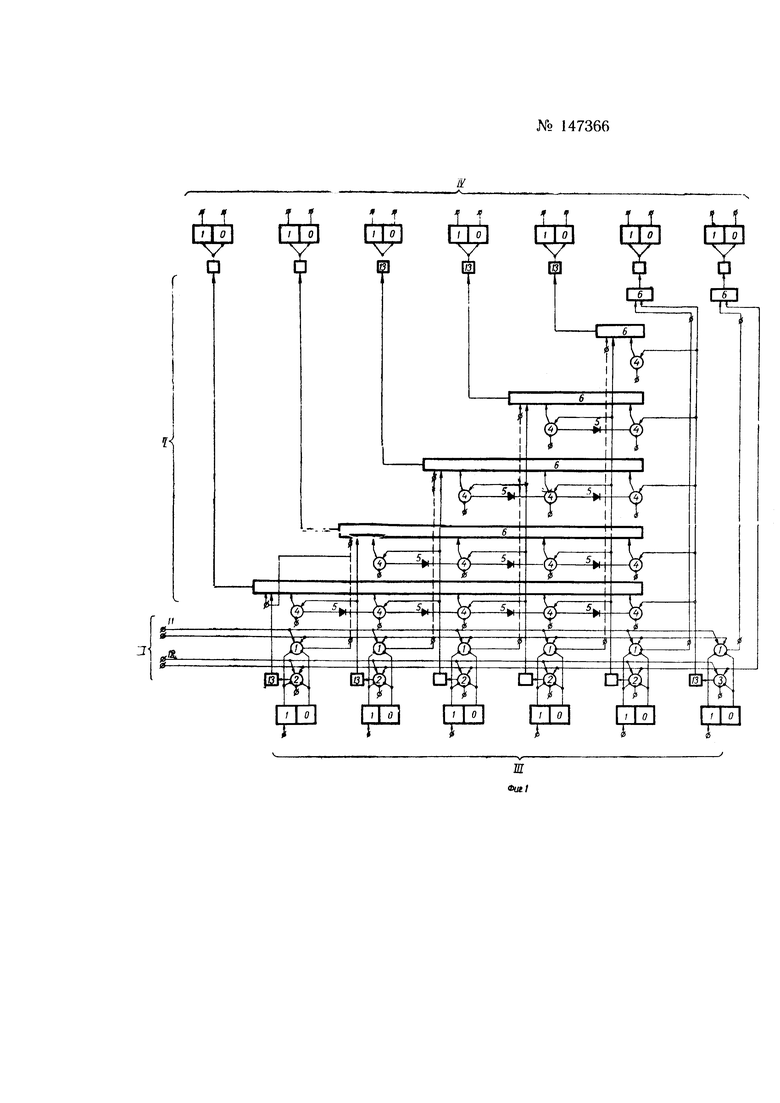

На фиг. 1 приведена функциональная схема описываемого сумматора; на фиг. 2 - схема диодно-трансформаторного вентиля.

Описываемый сумматор состоит из n (по числу разрядов) блоков I вентилей передачи кодов, дешифратора II одновременного переноса, регистра III первого числа и регистра IV второго числа и суммы. Блок I вентилей передачи кодов предназначен для выработки импульсов суммирования по модулю «2» и суммирования переносов и состоит в любом разряде, кроме n-ого, из вентилей 1 и 2 (n-ый разряд состоит из вентилей 1 и 3).

Дешифратор II переноса состоит из диодно-трансформаторных вентилей 4 со встречным включением обмоток. В каждом разряде дешифратора содержится к вентилей 4, связанных друг с другом однонаправленной диодной связью 5 по потенциальным управляющим входам. Такое построение каждого разряда в дешифраторе позволяет получить импульс переноса на выходе при наличии кода «1» как в одном предыдущем разряде, так и в группе предыдущих разрядов. Импульсные входы вентилей 4 раздельные. На них поступают импульсы переноса с предыдущих разрядов. Выходы вентилей 4 объединяются схемами 6 «ИЛИ», с которых импульсы переноса поступают на счетный вход триггера сумматора.

Каждый вентиль 4 имеет два режима работы: запрещения и разрешения. Если хотя бы один из диодов открыт по управляющему потенциальному входу, то в момент импульса ток потечет по обмоткам 7 и 8, соответственно запрещающей и рабочей, включенным встречно. В результате на выходной обмотке 9 появится сигнал положительной полярности (что достигается подбором сопротивления 10 и чисел витков обмоток 7 и 8). Если все диоды закрыты по управляющим потенциальным входам, то ток в момент импульса будет проходить только по рабочей обмотке 8, наводя на выходной обмотке 9 отрицательный импульс, использующийся в последующих схемах.

Сумматор работает по двухтактному принципу. В первом такте происходит суммирование по модулю «2». Импульсы с шин 11 «передача первого числа прямым или обратным кодом» поступают на вентили 1 и, в зависимости от кода числа в регистре III, на счетный вход триггера данного разряда сумматора через соответствующую схему 6 «ИЛИ». Во втором такте импульсы «суммирования переносов» прямым или обратным кодом по шинам 12 поступают на вентили 2, которые выдают сигналы переноса, поступающие через формирователи 13 на вертикальные импульсные шины дешифратора и непосредствено в следующий (к-1)-й разряд сумматора.

В случае кода 11…11 в группе предыдущих разрядов сумматора и при наличии переноса из разряда, предшествующего группе, дешифратор выработает сигналы переноса, которые поступят одновременно во все нужные разряды сумматора.

В случае кода «О» в каком-либо разряде сумматора во всех разрядах дешифратора часть вентилей 4, лежащая справа от этого разряда, будет запрещена. Перенос, выработанный в этой части, на выход не пройдет. Для исключения такта суммирования «1» дополнения блок I вентилей n-ного разряда построен таким образом, чтобы производить это суммирование «1» дополнения в момент суммирования переносов.

Описанное выполнение предлагаемого сумматора позволяет упростить его устройство и обусловливает полезность его применения.

| название | год | авторы | номер документа |

|---|---|---|---|

| ПАРАЛЛЕЛЬНЫЙ СУММАТОР НА ФЕРРИТ-ТРАНЗИСТОРНЫХ МОДУЛЯХ | 1970 |

|

SU277409A1 |

| ПОСЛЕДОВАТЕЛЬНЫЙ ДЕСЯТИЧНЫЙ НАКАПЛИВАЮЩИЙ СУММАТОР С ПАРАЛЛЕЛЬНЫМ СДВИГОМ | 1969 |

|

SU250544A1 |

| ПСЕВДОСЛУЧАЙНЫХ СИГНАЛОВ | 1970 |

|

SU283286A1 |

| ДВОИЧНЫЙ ПАРАЛЛЕЛЬНЫЙ СУММАТОР НАКАПЛИВАЮЩЕГО ТИПА | 1973 |

|

SU378844A1 |

| ГЕНЕРАТОР ИМПУЛЬСОВ | 1968 |

|

SU231218A1 |

| Электронный двоичный реверсивный счетчик | 1960 |

|

SU134487A1 |

| ДВУХТАКТНЫЙ СУММАТОР СО СКВОЗНЫМ ПЕРЕНОСОМ | 1970 |

|

SU278222A1 |

| ДВОИЧНОЕ АРИФМЕТИЧЕСКОЕ УСТРОЙСТВО | 1968 |

|

SU210491A1 |

| Однотактный реверсивный триггер | 1972 |

|

SU440774A1 |

| Цифровой кусочно-линейный аппроксиматор | 1973 |

|

SU549818A1 |

Сумматор параллельного действия с одновременным переносом, дешифратор переноса которого состоит из диодно-трансформаторных вентилей со встречным включением обмоток, отличающийся тем, что, с целью упрощения устройства, в нем каждый выход дешифратора переноса соединен через схему «ИЛИ» с вентилями, соответствующими всем предшествующим разрядам, и один вход каждого вентиля подключен к выходу переноса предыдущего разряда, а второй через диодную собирательную схему - к выходу триггера данного разряда и к аналогичному входу последующего.

Авторы

Даты

1962-05-25—Публикация

1961-02-17—Подача