Известны Двоичные арифметические устройства, содержащие параллельный накопительный сумматор, регистр множимого-делителя и регистр множителя-частного, а также вентили.

Предлагаемое устройство отличается от известных тем, что выходы триггеров регистра множимого-делителя связаны с первыми входами вентилей, вторые входы которых объединены и подсоединены к выходам схем сборки, входы которых подключены к шинам сигнала переноса предыдущего разряда и инверсии переноса с предыдущего разряда. Единичный выход регистра множимого-делителя связан через первый вентиль с нулевым входом триггера предыдущего разряда, нулевой выход через второй с единичным входом.

Это позволяет упростить устройство.

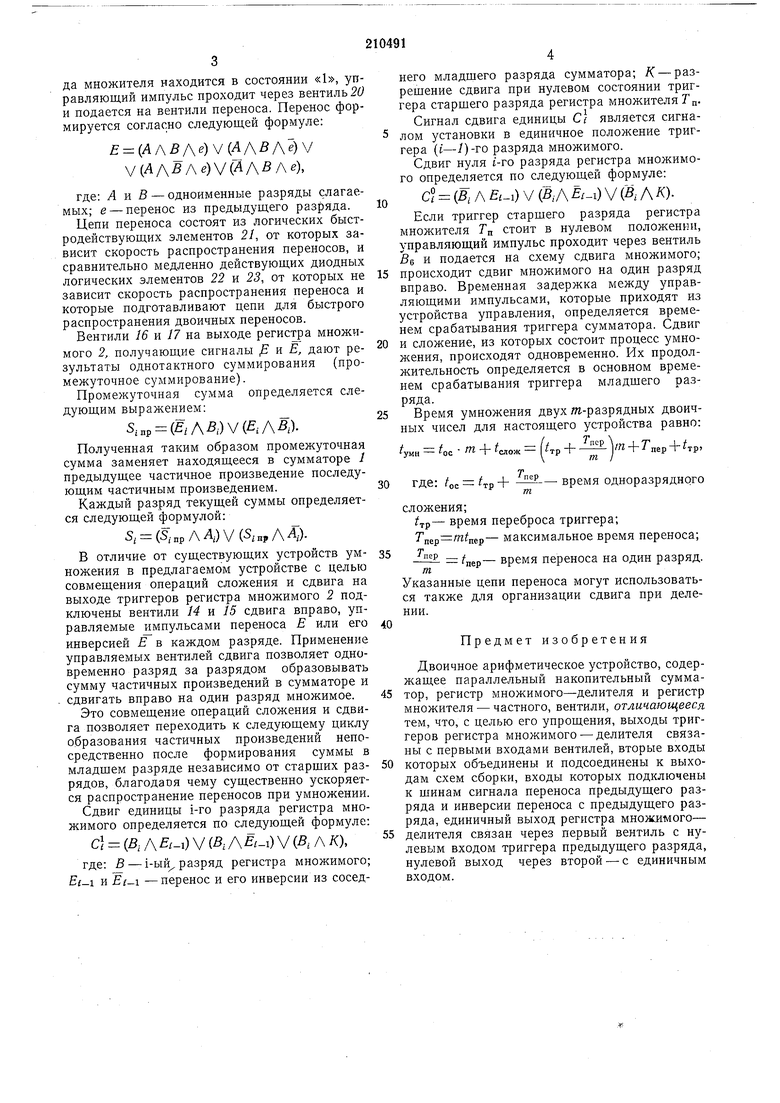

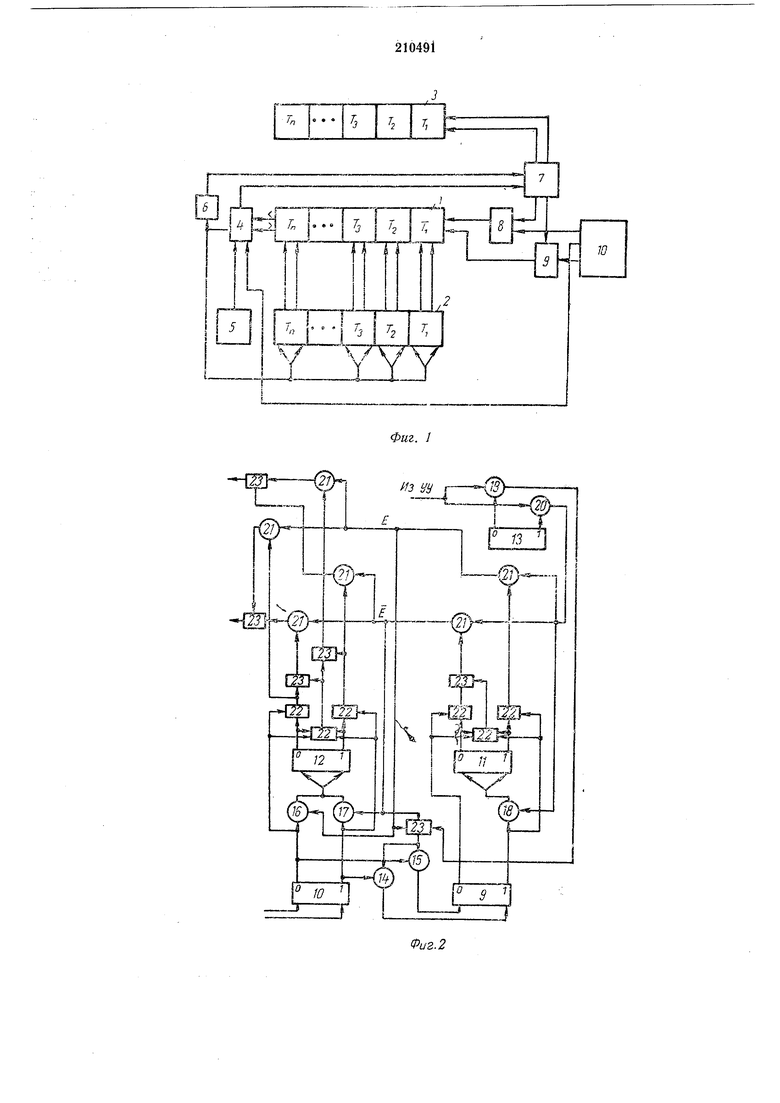

На фиг. 1 представлена блок-схема предлагаемого устройства; на фиг. 2 - детальная блок-схема устройства умножения.

В состав арифметического устройства входят двоичный накопительный сумматор /, регистр 2 множимого (делителя, второго слагаемого), регистр 3 частного (множителя), схема 4 управления операциями сложения (вычитания) при делении и преобразованием кода делителя, триггер 5 запоминания кода делителя, элемент задерл ки 6, схема 7 управления занесением и сдвигом разрядов частного и сложением (вычитанием), схемы 9 н 10 «ИЛИ и устройство местного управления 8.

При выполнении операций сложения сигнал в младший разряд сумматора приходит из устройства управления 8. Этот сигнал по цепи переноса и его инверсии, переписывая разряд за разрядом содержимое регистра 2 в сумматор / с одновременным преобразованием содержимого сумматора 1 в окончательный результат.

Специфика предлагаемого арифметического устройства иллюстрируется детальной блоксхемой и описанием работы этой схемы для случая умножения.

На схеме (фиг. 2) показаны два последних разряда множимого и регистра суммы и один старший разряд (управляющий) регистра множителя. Схема состоит из регистра множимого на триггерах 9 и 10, регистра суммы на триггерах // и 12, триггера 13 старшего разряда множителя, вентилей 14 и 15 сдвига множимого вправо, вентилей 16-18 промежуточного суммирования, вентилей 19 и 20 управления умнолсеиием, вентилей 21 в цепи образования переносов и его инверсий. Устройство содержит также диодные логические схемы 22 «И и схемы 23 «ИЛИ. Из зстройства управления поступают последовательности импульсов, число которых зависит от числа разрядов сомножителей. Если триггер 13 старшего разряда множителя находится в состоянии «1, управляющий импульс проходит через вентиль 2У и подается на вентили переноса. Перенос формируется соглас.но следующей формуле: (А Л ) V () V j((), где: А и В - одноименные разряды слагаемых; е - перенос из предыдущего разряда. Цепи переноса состоят из логических быстродействующих элементов 21, от которых зависит скорость распространения переносов, и сравнительно медленно действующих диодных логических элементов 22 и 23, от которых не зависит скорость распространения переноса и которые подготавливают цепи для быстрого распространения двоичных переносов. Вентили 16 и 17 на выходе регистра множимого 2, получающие сигналы Д и , дают результаты однотактного суммирования (промежуточное суммирование). Промежуточная сумма определяется следующим выражением: s,p (,AA-)V(cA-s;). Полученная таким образом промежуточная сумма заменяет находящееся в сумматоре / предыдущее частичное произведение последующим частичным произведением. Каждый разряд текущей суммы определяется следующей формулой: 5, (5;.прЛА)У(5,„рЛ4)В отличие от существующих устройств умножения в предлагаемом устройстве с целью совмещения операций сложения и сдвига на выходе триггеров регистра множимого 2 подключены вентили 14 и 15 сдвига вправо, управляемые пульсами переноса Е или его инверсией Е в каждом разряде. Применение управляемых вентилей сдвига позволяет одновременно разряд за разрядом образовывать сумму частичных произведений в сумматоре и сдвигать вправо на один разряд множимое. Это совмещение операций сложения и сдвига позволяет переходить к следующему циклу образования частичных произведений непосредственно после формирования суммы в младщем разряде независимо от старших разрядов, благодаоя чему существенно ускоряется распространение переносов при умножении. Сдвиг единицы i-ro разряда регистра множимого определяется по следующей формуле: С (В, Л -i) V (В, л Et-i) V (В, л К), где: В - i-ый разряд регистра множимого; EI-I и EC-I -перенос и его инверсии из соседнего младщего разряда сумматора; К - разрещение сдвига при нулевом состоянии триггера старшего разряда регистра множителя Гц. Сигнал сдвига единицы d является сигналом установки в единичное положение триггера (i-1)-го разряда множимого. Сдвиг нуля t-ro разряда регистра множимого онределяется по следующей формуле: С (В, л i-i) V (ДА -0 V № Л К). Если триггер старшего разряда регистра мнол ителя Т„ стоит в нулевом положении, управляющий импульс проходит через вентиль Бб и подается на схему сдвига множимого; происходит сдвиг множимого на один разряд вправо. Временная задержка между управляющими импульсами, которые приходят из устройства управления, определяется временем срабатывания триггера сумматора. Сдвиг и сложение, из которых состоит процесс умножения, происходят одновременно. Их продолжительность определяется в основном временем срабатывания триггера младшего разряда. Время умножения двух/тг-разрядных двоичных чисел для настоящего устройства равно: -Р + Tp, умн - ос Г слож - тр Ь где: /ос тр время одноразрядного сложения; гтр- время переброса триггера; Тпер т/„ер- максимальное время переноса; - /пер- время переноса на один разряд. Указанные цепи переноса могут использоваться также для организации сдвига при делении. Предмет изобретения Двоичное арифметическое устройство, содержащее параллельный накопительный сумматор, регистр множимого-делителя и регистр множителя - частного, вентили, отличающееся тем, что, с целью его упрощения, выходы триггеров регистра множимого - делителя связаны с первыми входами вентилей, вторые входы которых объединены и подсоединены к выходам схем сборки, входы которых подключены к шинам сигнала переноса предыдущего разряда и инверсии переноса с предыдущего разряда, единичный выход регистра множимого- делителя связан через первый вентиль с нулевым входом триггера предыдущего разряда, нулевой выход через второй - с единичным входом.

| название | год | авторы | номер документа |

|---|---|---|---|

| МНОЖИТЕЛЬНО-ДЕЛИТЕЛЬНОЕ УСТРОЙСТВО | 1968 |

|

SU217718A1 |

| Устройство для умножения двоичных чисел | 1973 |

|

SU482741A1 |

| Арифметическое устройство | 2016 |

|

RU2632411C1 |

| АРИФМЕТИЧЕСКОЕ УСТРОЙСТВО ПАРАЛЛЕЛЬНОГО | 1973 |

|

SU362295A1 |

| Арифметическое устройство | 1978 |

|

SU711570A1 |

| АРИФМЕТИЧЕСКИЙ ВЫЧИСЛИТЕЛЬ | 2004 |

|

RU2292580C2 |

| Арифметическое устройство | 1978 |

|

SU687982A1 |

| Вычислительное устройство | 1980 |

|

SU957203A1 |

| Устройство для умножения | 1976 |

|

SU651341A1 |

| ВЫЧИСЛИТЕЛЬНАЯ ОТКРЫТАЯ РАЗВИВАЕМАЯ АСИНХРОННАЯ МОДУЛЬНАЯ СИСТЕМА | 2009 |

|

RU2453910C2 |

Даты

1968-01-01—Публикация