Данное устройство относится к вычислительной технике.

Известны параллельные сумматоры на феррит-транзисторных модулях, содерж.аа1ие регистры суммы, схемы переноса, вентили. В этих устройствах сигнал с выхода кансдого разряда регистра суммы подается в последующий разряд через вентиль на счетный вход триггера, куда подсоединена и шина ввода.

Описываемый сумматор отличается тем, что в нем один счетный вход элемента запрета соединен с шиной ввода, другой непосредственно и через согласующий элемент - со вторым и первым выходами элемента запрета предыдущего разряда регистра сумматора. Это позволяет повысить быстродействие и упростить устройство.

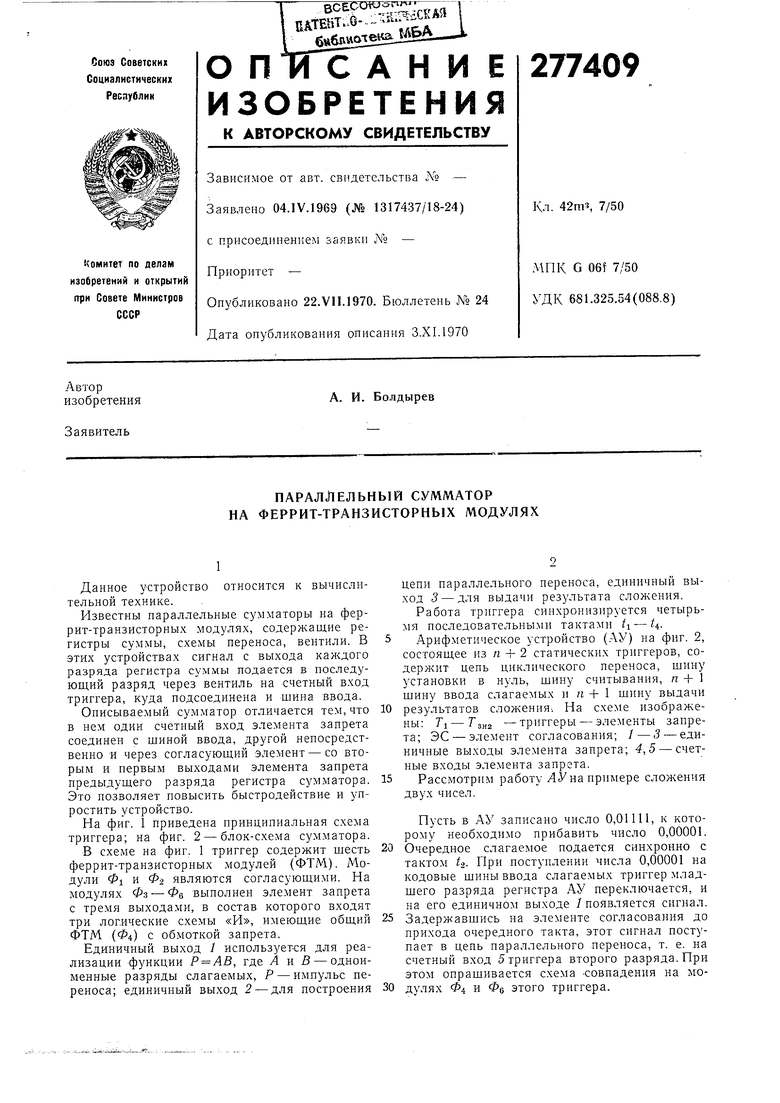

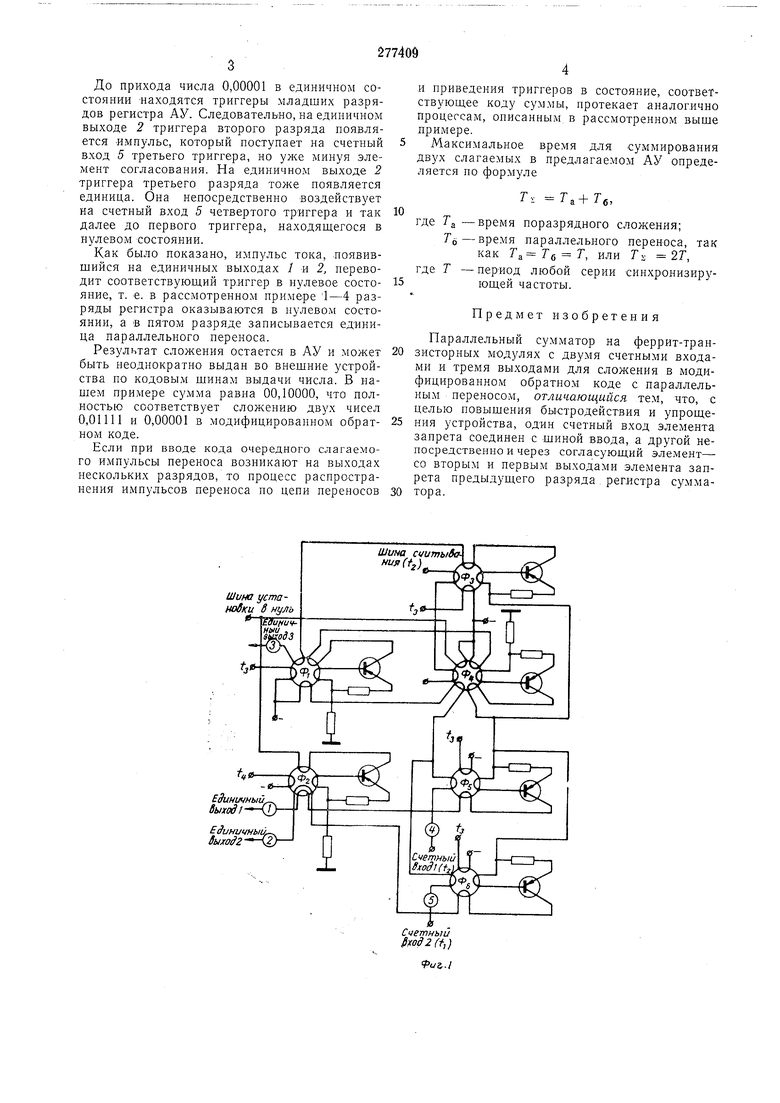

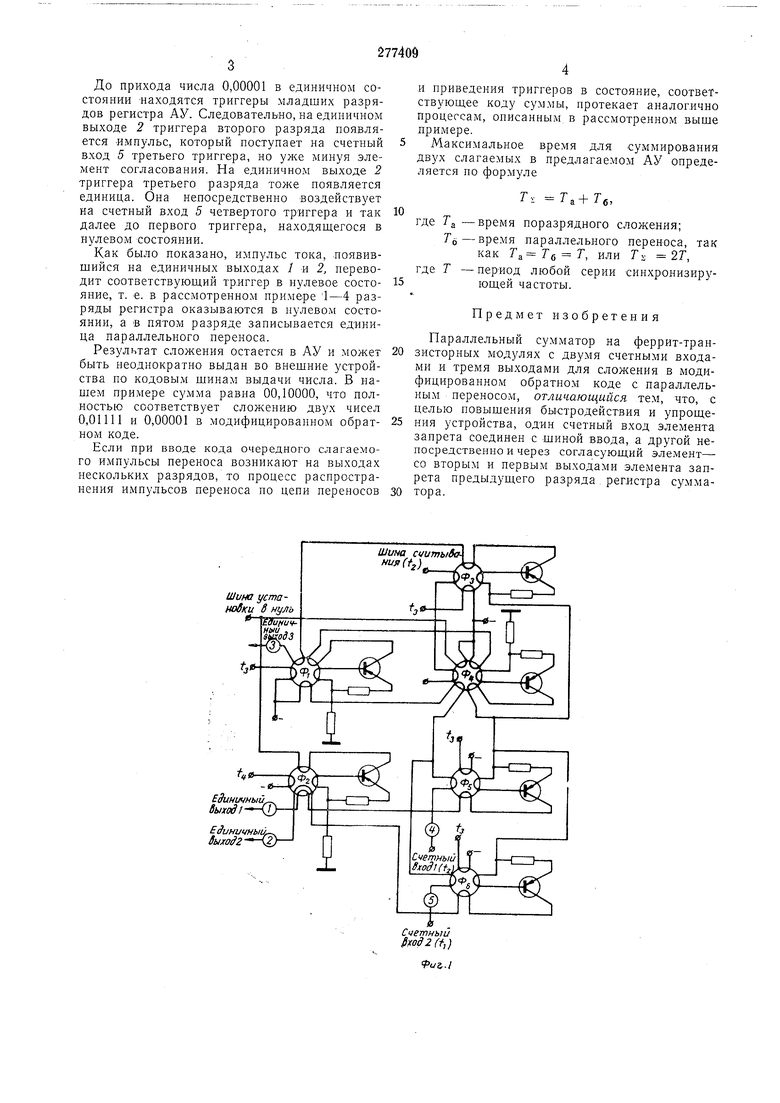

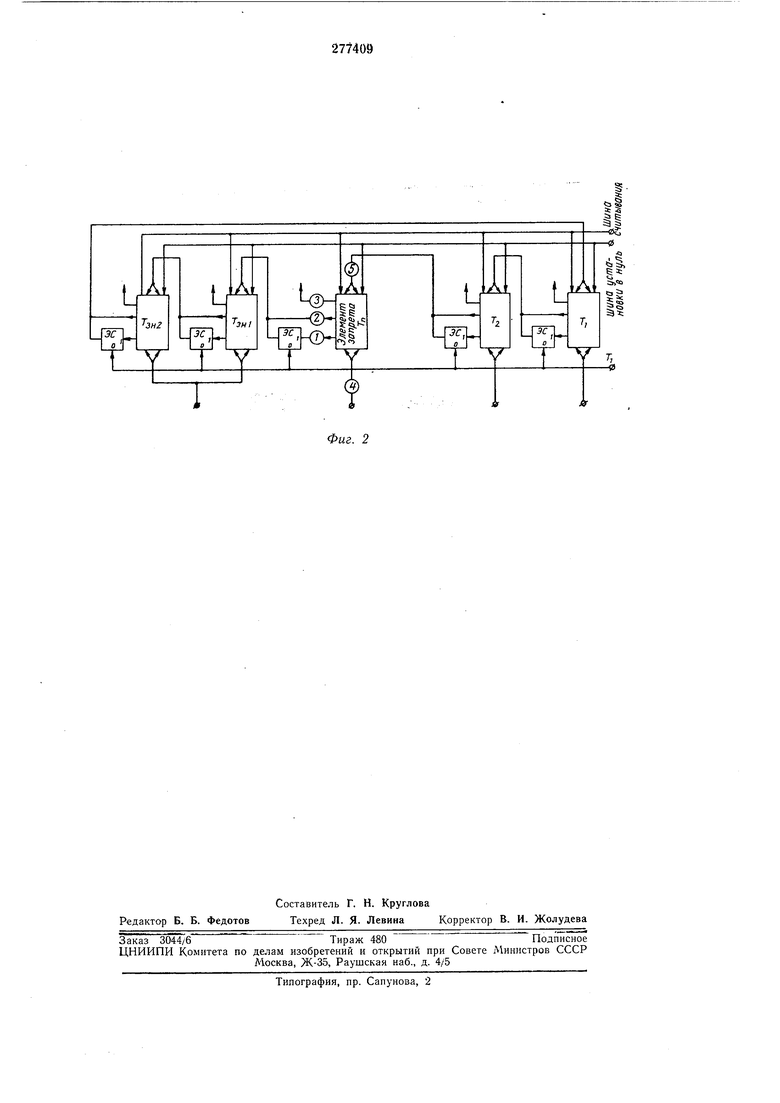

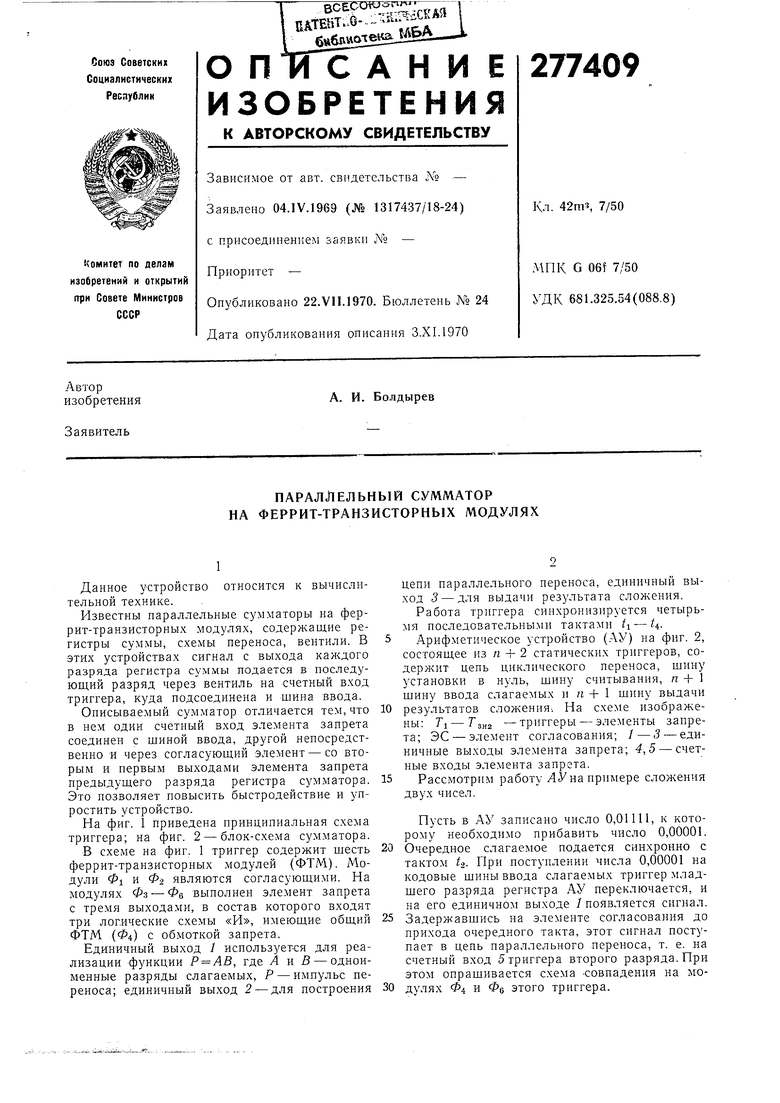

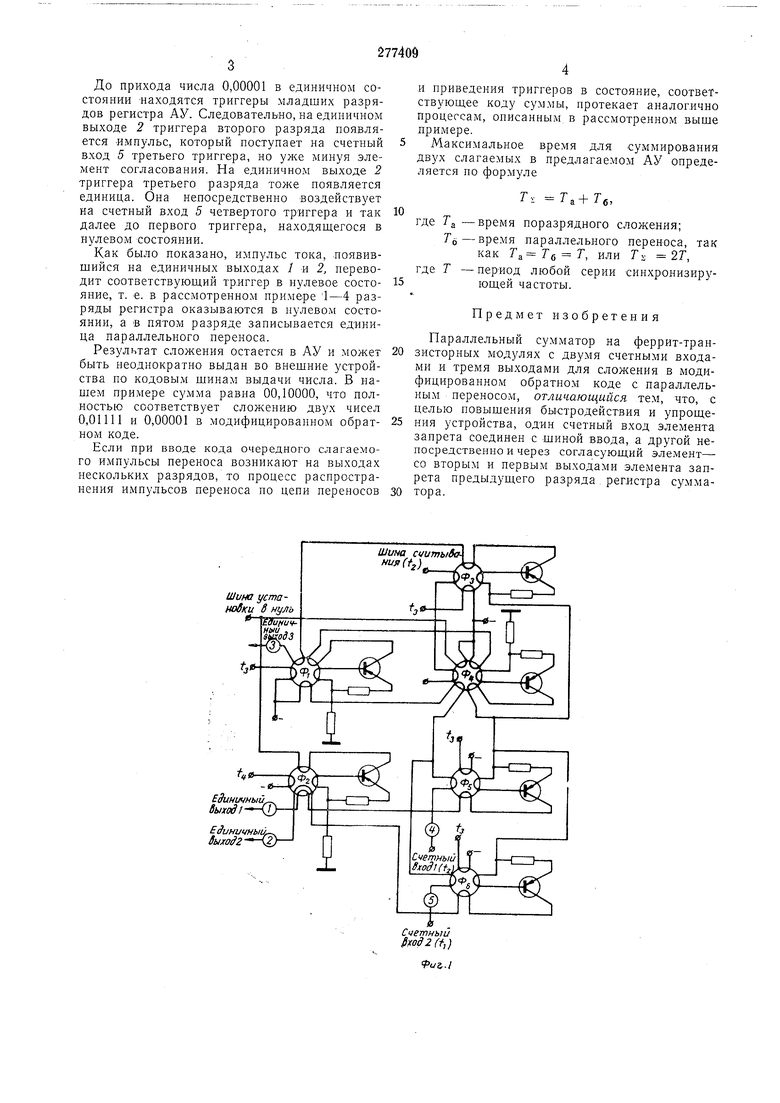

На фиг. 1 приведена принципиальная схема триггера; на фиг. 2 - блок-схема сумматора.

В схеме на фиг. 1 триггер содержит шесть феррит-транзисторных модулей (ФТМ). Модули Ф1 и Ф-2 являются согласующими. На модулях Фз--Фб выполнен элемент запрета с тремя выходами, в состав которого входят три логические схемы «И, имеющие общий ФТМ (Ф4) с обмоткой запрета.

цепи параллельного переноса, единичный выход 3 - для выдачи результата сложения.

Работа триггера синхронизируется четырьмя последозательными тактами ti - /4Арифметнческое устройство (.) на фиг. 2, состоящее из я + 2 статических триггеров, содержит цепь циклического переноса, шипу установки в нуль, шину считывания, п + I шину ввода слагаемых и п + 1 шину выдачи результатов сложения.. На схеме изображены: TI - Тзп2 -триггеры - элементы запрета; ЭС - элемент согласования; /-3 - единичные выходы элемента запрета; 4,5 - счетные входы элемента запрета.

Рассмотрим работу ЛУ на примере сложения двух чисел.

Пусть в АУ записано число 0,01111, к которому необходимо прибавить число 0,00001. Очередное слагаемое подается синхронно с тактом t.y. При поступлении числа 0,00001 на кодовые шины ввода слагаемых триггер младшего разряда регистра АУ переключается, и на его единичном выходе /появляется сигнал. Задержавшись на элементе согласования до прихода очередного такта, этот сигнал поступает в цепь параллельного переноса, т. е. на счетный вход 5 триггера второго разряда. При этом опрашивается схема .совпадения на модулях Ф4 и Фб этого триггера.

До прихода числа 0,00001 в единичном состоянии находятся триггеры младших разрядов регистра АУ. Следовательно, на единичном выходе 2 триггера второго разряда появляется Импульс, который поступает на счетный вход 5 третьего триггера, но уже минуя элемент согласования. На единичном выходе 2 триггера третьего разряда тоже появляется единица. Она непосредственно воздействует на счетный вход 5 четвертого триггера и так далее до первого триггера, находящегося в нулевом состоянии.

Как было показано, импульс тока, .появившийся на единичных выходах 1 и 2, переводит соответствующий тр.иггер в нулевое состояние, т. е. в рассмотренном примере 1-4 разряды регистра оказываются в нулевом состоянии, а В пятом разряде записывается единица параллельного переноса.

Результат остается в АУ и может быть неоднократно выдан во внешние устройства по кодовым шинам выдачи числа. В нашем примере сумма равна 00,10000, что полностью соответствует сложению двух чисел 0,01111 и 0,00001 в модифицированном обратном коде.

Если при вводе кода очередного слагаемого импульсы переноса возникают на выходах нескольких разрядов, то процесс распространения импульсов переноса по цепи переносов

И приведения триггеров в состояние, соответствующее коду суммы, протекает аналогично процессам, описанным в рассмотренном выше примере.

Максимальное время для суммирования двух слагаемых в предлагаемом АУ определяется по формуле

Га+7«,

где Га -время поразрядного сложения;

Го-время параллельного переноса, так

как Т,, Тб Т, или Ts 2Т, где Г -период любой серии синхронизирующей частоты.

Предмет изобретения

Параллельный сумматор на феррит-транзисторных модулях с двумя счетными входами и тремя выходами для в модифицированном обратном коде с параллельным переносом, отличающийся тем, что, с целью повышения быстродействия и упрощения устройства, один счетный вход элемента запрета соединен с шиной ввода, а другой непосредственно и через согласующий элемент- со вторым и первым выходами элемента запрета предыдущего разряда . регистра сумматор а.

| название | год | авторы | номер документа |

|---|---|---|---|

| СТАТИЧЕСКИЙ ТРИГГЕР | 1967 |

|

SU224900A1 |

| Накапливающий сумматор | 1991 |

|

SU1800454A1 |

| НАКАПЛИВАЮЩИЙ СУММАТОР | 1993 |

|

RU2043650C1 |

| Накапливающий сумматор | 1989 |

|

SU1702375A1 |

| К-значный фазоимпульсный сумматор | 1971 |

|

SU450163A1 |

| Параллельный накапливающий сумматор | 1979 |

|

SU911517A1 |

| Арифметическое устройство | 1979 |

|

SU842794A1 |

| ДВОИЧНЫЙ ПАРАЛЛЕЛЬНЫЙ СУММАТОР | 1971 |

|

SU315179A1 |

| ДВОИЧНЫЙ ПАРАЛЛЕЛЬНЫЙ СУММАТОР НАКАПЛИВАЮЩЕГО ТИПА | 1973 |

|

SU378844A1 |

| Сумматор параллельного действия | 1974 |

|

SU531157A1 |

Шино установки 8 нуль

0

ВЗиничиый А/гя /--с/

ЕduHU4Hbiu

Счетный KodKf,}

I I 0 I I

ts

Фиг. 2

5o

li

V

/

Даты

1970-01-01—Публикация