Јъ

1

4Ь

СЛ О

Изобретение относится к электро- . измерительной технике и предназначено для поверки (аттестации) систем автоматического контроля.

Цель изобретения состоит в повышении достоверности поверки измерительных компараторов за счет контроля их статических и динамических метрологических (точностных) характеристик с учетом случайной погрешности контроля.

Способ осуществляют следующим образом.

Измеряется математическое ожидание задержки между одноименными фрон,- тами (положительными или отрицательными) выходных сигналов поверяемого и образцового измерительных компаного компаратора, вводят начальный интервал задержки фронта выходного сигнала образцового измерительного

компаратора, при сравнении моментов появления одноименных фронтов выходных сигналов измерительных компараторов изменяют (регулируют) первоначально введенный интервал задержки

на временной квант, кратный, максимально допустимому интервалу задержки, но меньший его, в большую или меньшую сторону соответственно при опережающем или запаздывающем момен5 тах появления одноименных фронтов выходных сигналов задержанного одного относительно другого из указанных измерительных компараторов, последнее действие повторяют заданное

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство поверки измерительных компараторов | 1989 |

|

SU1649476A2 |

| Устройство для измерения синусоидального напряжения | 1982 |

|

SU1104428A1 |

| Устройство для измерения и контроля параметров аналого-цифровых преобразователей | 1981 |

|

SU1005297A1 |

| Устройство для определения математического ожидания погрешности аналого-цифровых преобразователей | 1983 |

|

SU1149407A1 |

| Устройство для градуировки измерительных преобразователей давления | 1983 |

|

SU1137366A1 |

| Устройство для измерения времени задержки отсчета аналого-цифровых преобразователей | 1985 |

|

SU1280697A1 |

| Устройство для измерения динамических характеристик аналого-цифровых преобразователей | 1982 |

|

SU1067598A1 |

| Устройство для поверки преобразователей фаза-код | 1990 |

|

SU1774298A1 |

| Устройство для настройки и поверки импульсной электроразведочной аппаратуры | 1988 |

|

SU1679444A2 |

| Устройство для контроля аналого-цифрового преобразователя сигналов изображения | 1982 |

|

SU1016851A1 |

Изобретение относится к контролю измерительных устройств, в частности компараторов. Цель изобретения - повышение точности. Способ реализован в устройстве, в котором сигналы источника 1 постоянного испытательного сигнала и генератора 2 случайно-изменяющегося сигнала подаются соответственно на поверяемый и образцовый компараторы 3 и 4. Состояние выходов компараторов отслеживают триггеры 5 и 6, информация с которых передается на элементы 7,8 совпадения и блок 9 принятия решения. Поступление информации через элементы 11 и 14 задержки на входы цифрового компаратора 13 и элемента И-НЕ 13 осуществляется по тактовым импульсам генератора 10 импульсов стабильной частоты. Итерационный процесс оценки погрешности поверяемого компаратора 3 организован на реверсивном счетчике 15 с помощью инвертора 16 и задатчика 17. 2 с.п. ф-лы, 3 ил.

раторов, связанное с амплитудно-час- 20 число раз, при этом величину неиден- тотными характеристиками линейныхтичности образцового и поверяемого

(аттестуемого) измерительных компараторов определяют по их амплитудночастотным характеристикам и дисперчастей и дисперсиями собственных случайных шумов измерительных компа- рат оров выражениями.

Для измерения математического ожи- 25сиям собственных аддитивных шумов дания указанной задержки одновремен-через измеренное значение математи- но подают на соответствующие входыческого ожидания между одноименными поверяемого (аттестуемого) и образ-(положительными (цф) или отрица- цового измерительных компараторов тельными (l) фронтами выходных сиг- случайно изменяющийся сигнал с равно-30налов образцового и поверяемого (ат- мерным спектром в пределах полосы .тестуемого) измерительных компарато- пропускания образцового измеритель-ров из выражения

16

+ N. f IlMjuQI - tKcCioOlM dw|

WB

)il d

Ы

1

Ui-ui N 1 )1- - iKaCjw)1} dw

о .

N, B |Kn(jW))aw1du

де M{tn«ii, .

- математические ожида- 45 ния длительностей интервалов задержки соответственно между положительными и от- i рицательными фронта- 50 ми выходных сигналов;

U0(juO|,

| Кп( jui) - модули амплитудно-

частотных характеристик образцового и поверяемого измерительных компараторов)

частотным характеристикам и диспер(1)

Ы

(2)

П

, - дисперсии собственных аддитивных шумов образцового и поверяемого измерительных компараторов;

Nc - интенсивность равномерного спектра испытательного случайно изменяющегося сигнала;

ыа - верхняя граница полосы частот, ъ которой измеряют неидентичность об- . разцового и поверяемого измерительных компараторов, устанавливаемая

14

в пределе равной верхней граничной частоте образцового измерительного компаратора.

Для вывода равенства, связывающего математические ожидания квадратов длительностей интервалов задержки, например, между положительными фронтами выходных сигналов образцового и поверяемого измерительных компараторов с дисперсиями собственных аддитивных шумов образцового и поверяемого измерительных компараторов, модулями амплитудно-частотных характеристик образцового и поверяемого измерительных компараторов и параметрами испытательного сигнала представим алгоритм работы предлагаемого устройства в виде адекватного итерационного выражения

, enf(n+t )t « (ndt) .,(to + ndt) - U3 -,

- htye(te + ndt , (ndt)) + + 40(to + nut + „, () - UJ},

где С„ф (п+

+1)4 tj, iXndt) -длительности интервалов задержки на (п+1)-м и , n-м тактах измерения i

&t - период следования импульсов

lira Ms htyi(t,+nAt)+n.1(t +n/Jt) lim M,, 4Jhtyb (t6+nJt+

+ „4, ( + ()) - Uj}

it lim D , (tc+ ndt)+ 4,(t0+ nut) - U - hryc(t0+nflt + „+

+ Тп ()) + 1e(t0+ n&t+ )) - С , де MVi + llit-K

M . -} - операторы мате.матического ожидания 50 по указанным случайным переменным;

у,-, ч,со

иу.(-),55

let ) случайные последовательности, независимые между собой, что вытекает из фи5674

стабильной частоты генератора ; y,() и 5y0(to+n4t +

+ п (n/3t)) - выходные сигналы измерительных компараторов поверяемого и обЮразцового соответственно в указанные моменты времениl H.,(te+ndt) и 15le(te+n-St +

f + nop(ndt)) - аддитивные шумы

поверяемого и образцового измерительных компа20рат Ьров соответственно в указанные моменты

времени

|i,e,o

|0, 9 - 0 ,

где 6 - значение аргумента функции

,указанное в формуле U - значение постоянного испытательного сигнала, который подается на вторые входы иэ- мери т ель ных к омпар а т ор ов. Для сходимости алгоритма, пред- ставленного в итерационной форме (3), необходимо и достаточно, чтобы выполнялись условия

(4)

(5)

зической сущности работы устройства} -} - оператор дисперсии по тем же случайным последовательностям)

С - некоторая постоянная величина,которая определяет случайную составляющую погрешности аттестации.

514 74

Постоянная С выбирается, исходя из технико-экономических требований, которые предъявляются к устройству аттестации.5

Выходные сигналы у (), Ус() и шумы Ц,(1) 10() распределены нормально, так как на входы измерительных компараторов подается положительный случайный процесс с нормаль- 10 ным законом распределения. Поэтому равенство (5) после преобразования по оператору математического ожидания приводится к виду

. (и), . (6)

где Фу, + i.,(U), v о to (U) ФУНКЦИИ Лапласса, которые можно представить в нормированном виде

U

6г +

V1

ф(.

U

.

) (7)

или

U

U

VAtt

(8)

откуда следует равенство

, 1

Vo

б +6 6 +61

(9)

V t г«

Для того,чтобы из полученного равенства найти в явном виде искомое значение математического ожидания длительностей интервала задержки представляют выходной сигнал образцового измерительного компаратора с погрешностью второго порядка малости в следующем виде:

yb(t0+ndt+/aB4(nut)) у (to + (10 + ndt) + y0(t0+n,at) -Dn4,(nAt),

где У0() - первая производная выходного сигнала образцового измерительного компаратора в указанный момент времени.

Определяя дисперсию по всем указанным случайным величинам, получают с погрешностью второго порядка малости

6l (t0+nflt+fnit(ndt))

Чв

6V

гС П4 (nat) r (о), (11)

5

0

где

УО

(о) ()

дисперсия выходного сигнала образцового измерительногокомпаратора без учета аддитивного шума, вторая производная от автокорреляционнойфункции того же выходного сигнала в нулевой точке (т.е. при Јпф(ndt) 0)}

))

- второй начальный момент,равный

(n/tt)) + + M(,(n/lt)))

При выводе формулы учитывают, что для нормального случайного процесса его значение и значение первой производной в совпадающие моменты времени независимы. Разрядность реверсивного счетчит ка можно выбрать такой, при которой

(n4t))ЈM(€n$(n4t)j2. Поэтому (n4t)l ))}1.

Эквивалентная схема измерительного компаратора состоит из последовательно соединенных безынерционного нелинейного звена и инерционного линейного звена. Поэтому дисперсии выходного сигнала и его автокорреляционную функцию можно выразить через модули амплитудно-частотных характеристик образцового и поверяемого измерительных компараторов. Подставляя соответствующие значения модулей амплитудно-частотных характеристик в равенство (9) с учетом того, что входной сигнал имеет равномерную спектральную плотность в полосе частот (О, WB), получают приведенное

выше выражение.

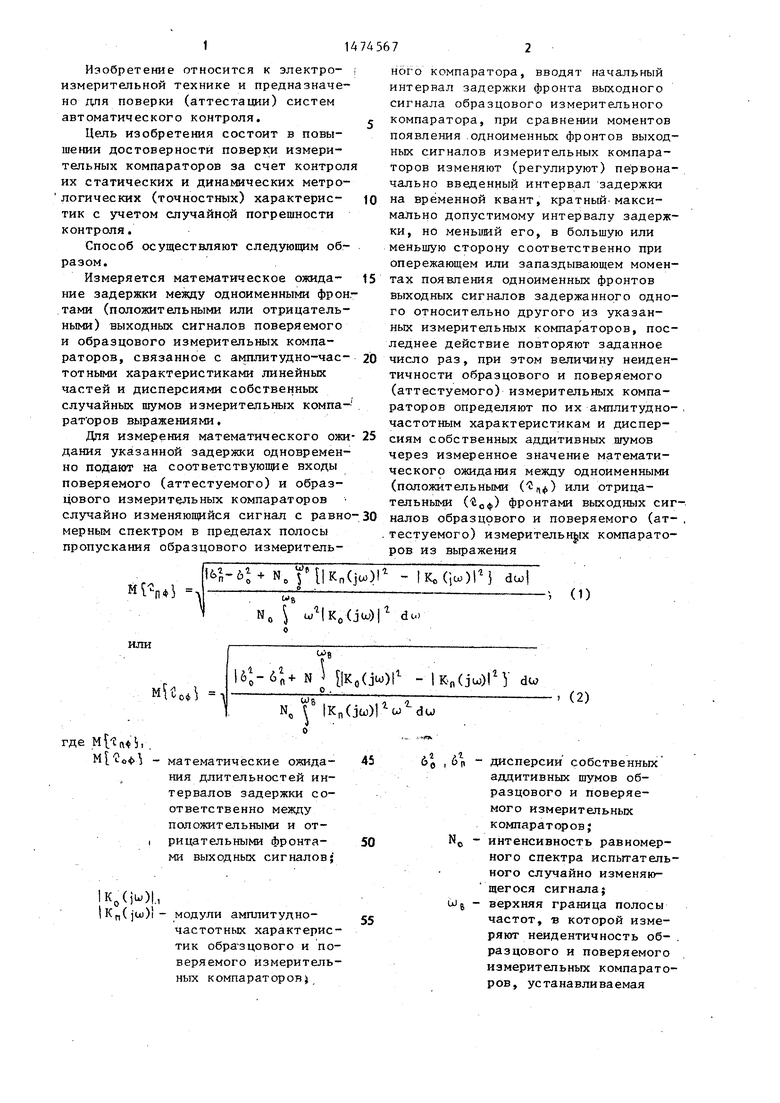

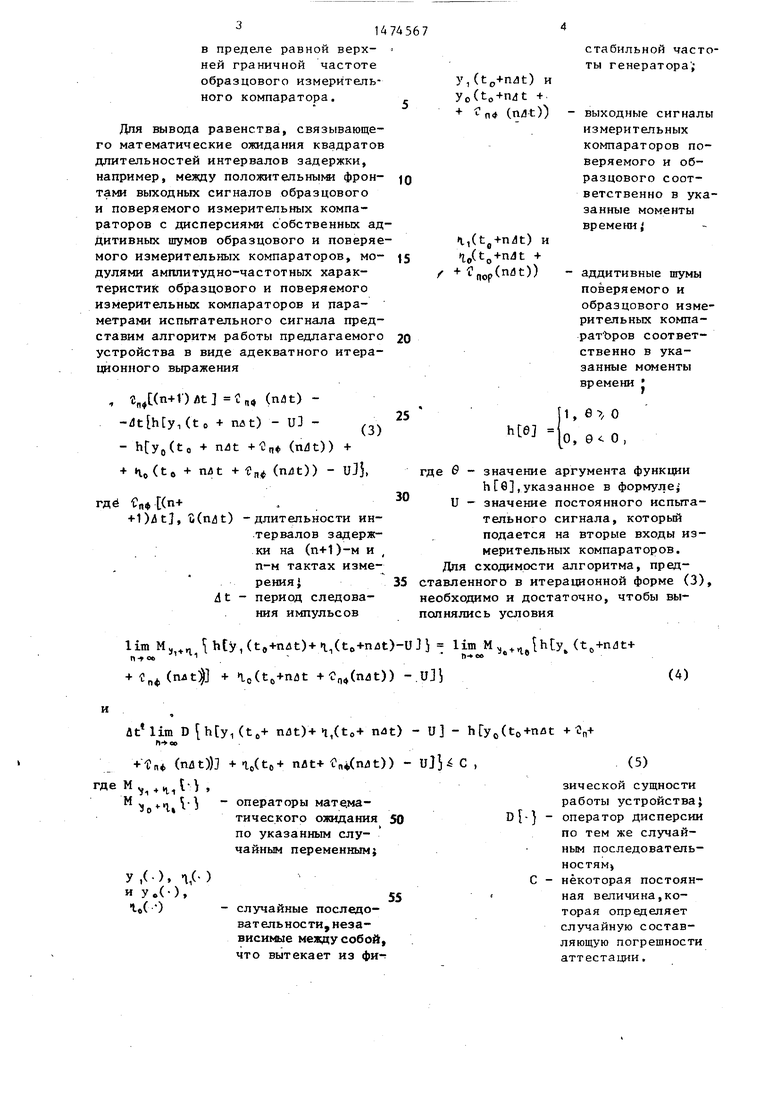

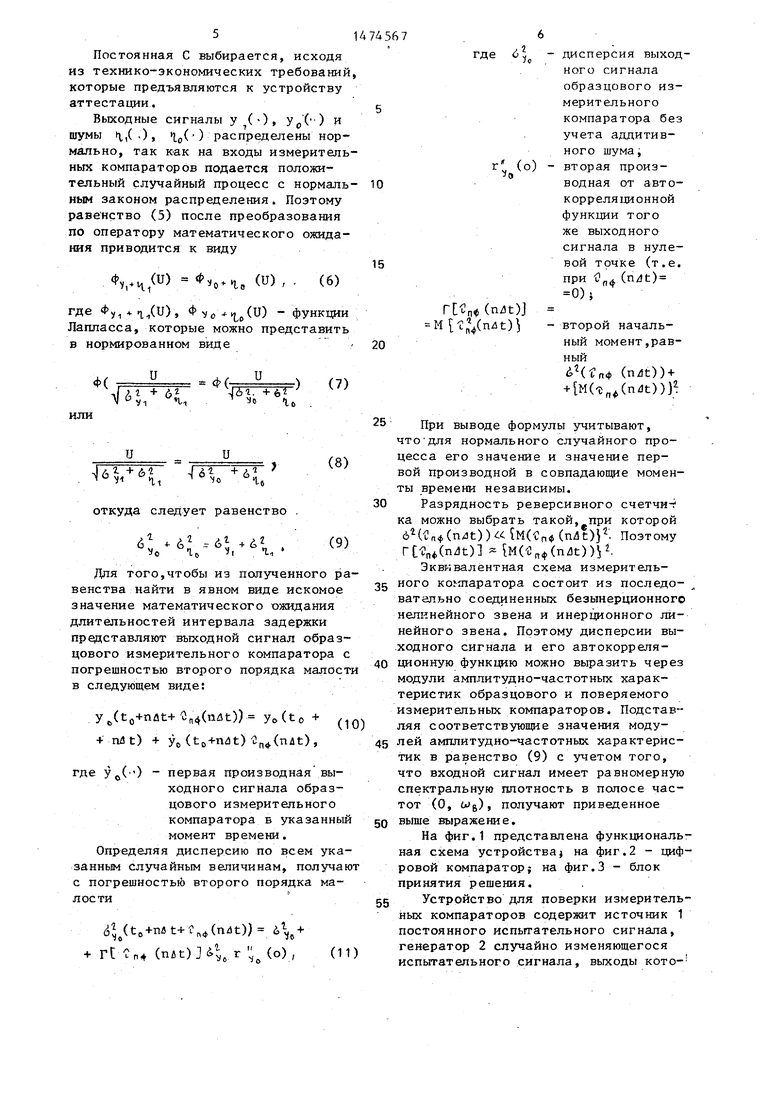

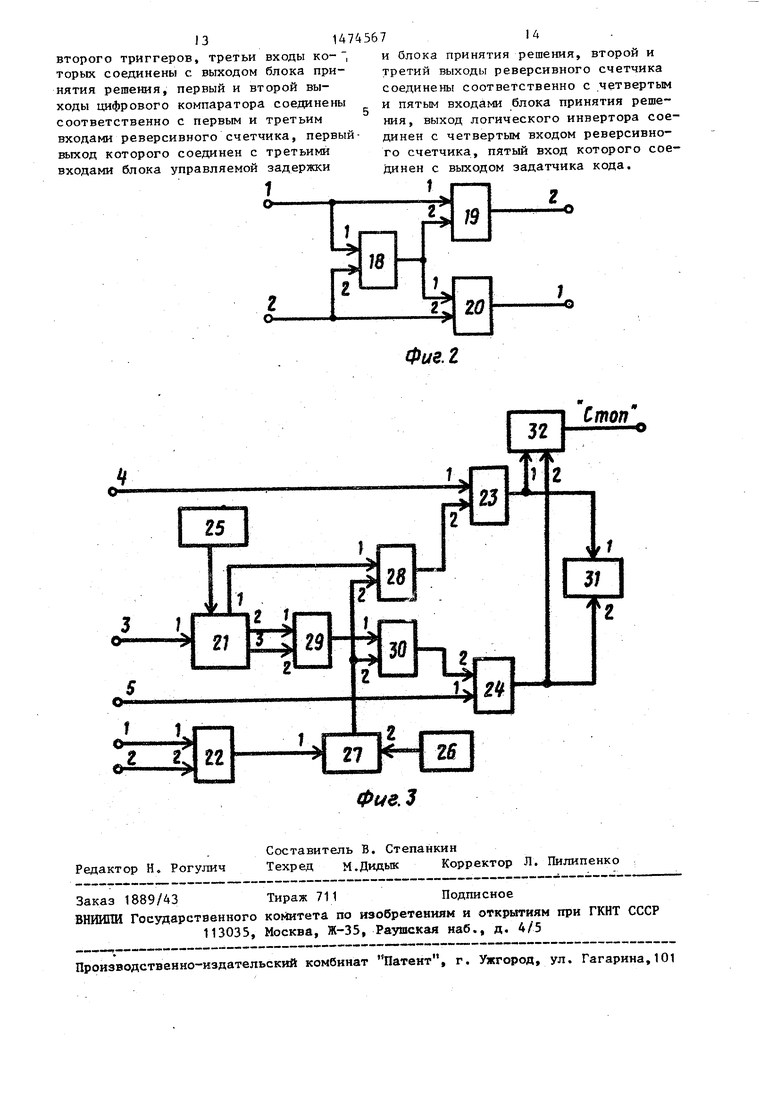

На фиг.1 представлена функциональная схема устройства j на фиг.2 - цифровой компаратор; на фиг.З - блок принятия решения.

Устройство для поверки измерительных компараторов содержит источник 1 постоянного испытательного сигнала, генератор 2 случайно изменяющегося испытательного сигнала, выходы которых соответственно соединены с первыми и ВТОРЫМИ входами измерительных поверяемого 3 и образцового 4 компараторов,выходы которых соецинены с первыми (стробирующими) входами триггеров 5 и 6 соответственно,прямые выходы которых соединены: первого триггера 5 - с первым входом первого элемента 7 совпадения, второго триггера 6 - с первыми входами элемента 8 совпадения и блока 9 принятия решения, вторые входы элементов 7 и 8 совпадения соединены с выходом генератора 10 импульсов стабильной частоты, выход первого элемента 7 совпадения соединен через элемент 11 задержки с первыми входами цифрового компаратора 12 и логического элемента ИЛИ-НЕ 13 с повышенным временем задержки распространения, выход второго элемента 8 совпадения соединен с первым входом блока 14 управляемой задержки, второй вход которого соединен с одноименными входами блока 9 принятия решения, логического элемента ИЛИ-НЕ 13, реверсивного счетчика 15, входом логического инвертора 16 - с повышенным временем задержки распространения и внешним

входом устройства Пуск, выход блока 14 управляемой задержки соединен с вторым входом цифрового компаратора 12 и третьим входом логического элемента ИЛИ-НЕ 13, выход которого соединен с вторыми входами Сброс триггеров 5 и 6, а третьи D-входы которых соединены с выходом Стоп блока 9 принятия решения, первый Меньше и второй Больше выходы цифрового компаратора 12 соединены соответственно с первым вычитающим и третьим суммируюшим входами реверсивного счетчика 15, первый счетный выход которого соединен с третьим входами блока 14 управляемой задержки и блока 9 принятия решения, второй Меньше нуля и третий Переполнение выходы реверсивного счетчика 15 соединены соответственно с четвертым и пятым входами блока 9 принятия решения, выход логического инвертора 16 соединен с четвертым входом реверсивного счетчика 15,пятый вход которого соединен с выходом задатчика 17 кода.

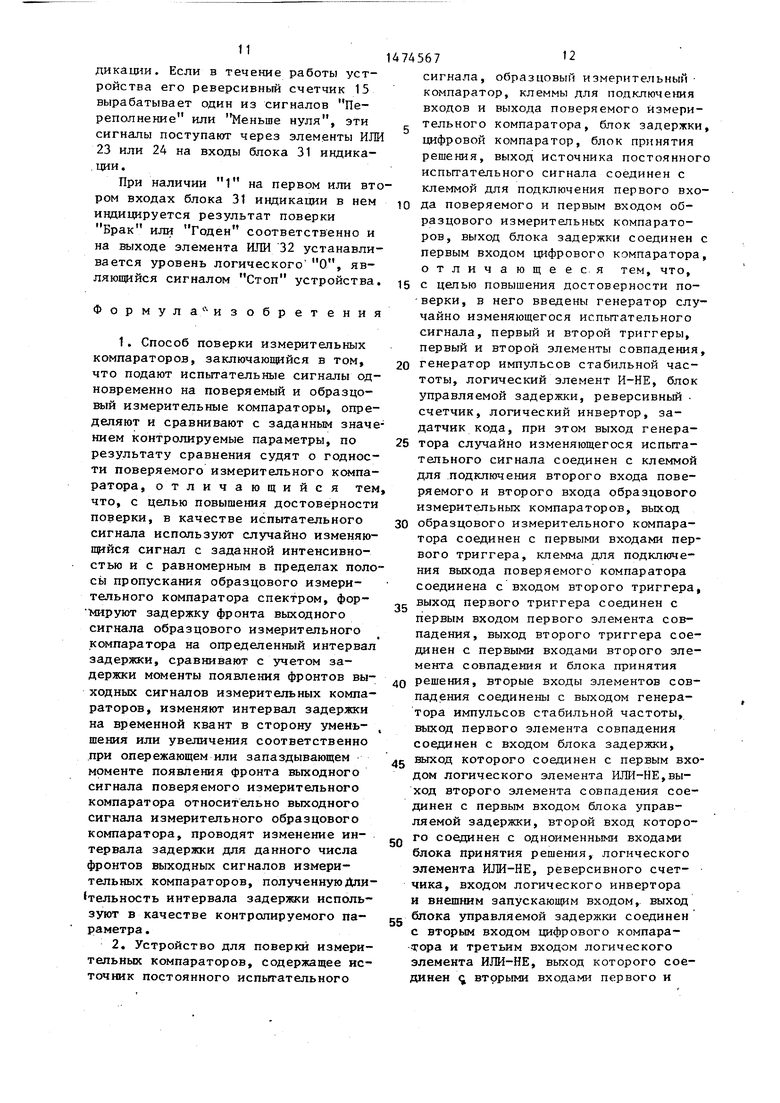

Цифровой компаратор 12 () содержит три логических элемента И-НЕ 18-20, первые входы элементов

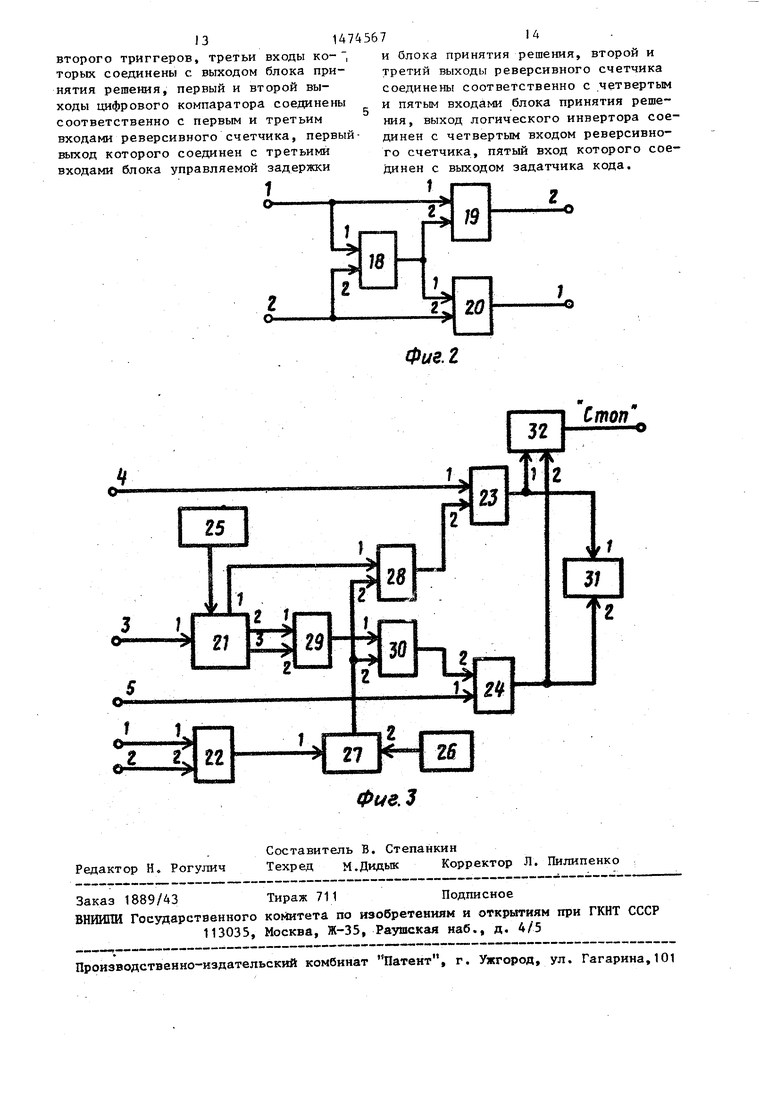

И-НЕ 18 и 19 соединены с первым внешним входом цифрового компаратора,вторые входы элементов И-НЕ 18 и 20 5 соединены с вторым внешним входом цифрового компаратора, выход элемента И-НЕ 18 соединен с вторым и первым входами соответственно элементов И-ЧЕ 19 и 20, выходы которых явЮ ляются соответственно вторым и третьим выходами цифрового компаратора. Блок 9 принятия решения (фиг.З) содержит элемент 21 сравнения кодов, счетчик 22, логические элементы ИЛИ

5 23 и 24, первые входы которых являются внешними входами блока соответственно третьим, первым, четвертым и пятым, а второй вход блока - вторым входом счетчика 22, задатчи0 ки 25 и 26 кодов, определяющие соответственно величину допуска и число итераций (сравнений), выходы которых соединены с вторыми входами соответственно элементов 21 и 27

5 сравнения кодов, выходы элементов 21 сравнения кодов соединены соответственно: первый Меньше - с первым входом элемента 28 совпадения, второй Больше и третий Равно - с

0 первым и вторым входами логического элемента ИЛИ 29, выход которого соединен с первым входом элемента 30 совпадения, выход счетчика 22 соединен с первым входом элемента 27

с сравнения кодов, выход которого соединен с вторыми входами элементов 28 - и 30 совпадений, выходы которых соединены с вторыми входами соответственно логических элементов ИЛИ 23

Q и 24, выходы последних соединены соответственно с первыми и вторыми входами..элемента 31 индикации и логического элемента ИЛИ 32, выход которого является внешним выходом блока Стоп.

Устройство работает следующим образом.

Постоянный и случайно изменяющийся испытательные сигналы с выходов соответственно источника t постоянного испытательного сигнала и генератора 2 случайно изменяющегося испытательного сигнала сравниваются поверяемым 3 и образцовым 4 измерительными компараторами и на их выходах появляются импульсные сигналы, которые в силу неидентичности метрологических (точностных) характеристик компараторов имеют сдвинутые

5

0

5

относительно друг друга одноименные (положительные и отрицательные) фронты. Работа устройства начинается по внешнему положительному импульсу Пуск, по которому происходит сброс реверсивного счетчика 15 и счетчика 22 блока 9 (фиг.З) и начальная установка внутреннего счетчика блока 14 управляемой задержки, при этом на D-входах триггеров 5 и 6 устанавливается 1, с некоторой задержкой вырабатывается отрицательный импульс (проинвертированный импульс Пуск) на выходе логического инвертора 16, а также на выходе логического элемента ЙЛИ-НЕ 13, при этом соответственно происходит установка на выходе счетчика 15 кода, задаваемого задатчиком 17 кода, и сброс триггеров 5 и 6, после чего работа устройства осуществляется циклически. Каждый цикл начинается с установкой в 1 любого из триггеров 5 и 6 по первому появившемуся положительному (или отрицательному) фронту выходных сигналов измерительных компараторов 3 или 4 и заканчивается сбросом триггеров 5 и 6 по импульсу с выхода элемента ИЛИ-НЕ 13. В цикле происходит следующее; высокий уровень выходного сигнала каждого триггера 5 и 6 открывает соответственно элемент 7 или 8 совпадения для прохождения импульсов с генератора 10, при этом импульсы с выхода элемента 8 совпадения задерживаются блоком 14 управляемой задержки на число периодов, задаваемое инверсным кодом на его третьем выходе, который в л каждом цикле переписывается во внут- . ренний счетчик блока 14 первым импульсом, приходящим на его первый вход.

На выходе блока 14 управляемой задержки и, следовательно, на втором входе цифрового компаратора 12 появится фронт, сдвинутый относительно переднего фронта первого импульса, прошедшего через элемент 8 совпадения, на заданную дискретную Временную задержку. Если на первый вход цифрового компаратора 12 с начала цикла до этого момента не пришел импульс с выхода элемента 7 совпадения, это означает, что введенная дискретная задержка фронта выходного сигна- ла образцового компаратора 4 меньше реальной текущей задержки одноимен147456710

кого фронта выходного сигнала поверяемого измерительного компаратора 3. Если на обоих входах цифрового компаратора 12 появились фронты одновременно, это означает равенство введенной и реальной текущей задержек, если же к первому входу цифрового компаратора 12 фронт пришел

20

25

TQ раньше, чем на его второй вход, Оэто означает, что первым на триггер поступил фронт с выхода поверяемого измерительного компаратора 3. Указанные условия выполняются с погреш 5 ностью дискретности, определяемой периодом следования тактовых импульсов 10 генератора.

Элемент 11 задержки компенсирует паразитную задержку прохождения сигнала в блоке 14 управляемой задержки. В соответствии с указанными условиями цифровой компаратор 12 (фиг,2) в первом и третьем случаях вырабатывает отрицательный импульс соответственно на первом выходе Меньше и втором выходе Больше, 1 во втором случае оставляет высокие уровни обоих выходов без изменения, а реверсивный счетчик 15 уменьшает

Зо или увеличивает на 1 выходной код по заднему (положительному) фронту импульса, поданного соответственно на первый или третий его входы.Элемент ИЛИ-НЕ 13 по любому положительному импульсу на его входах вырабатывает отрицательный импульс, сбрасывающий триггеры 5 и 6 в исходное нулевое состояние и задержанный относительно входного на такую задержку, которая гарантирует срабатывание за это время цифрового компаратора 12 и реверсивного счетчика 15.

Блок 9 принятия решения работает следующим образом (фиг.З). Счетчик 22 подсчитывает число срабатываний триггера 6 устройства и при достижении этим числом значения, заданного в задатчике 26 кода (число итераций), элемент 27 сравнения кодов открывает элементы 2б и 30 совпадений. Элемент 21 сравнения кодов сравнивает текущий инверсный код длительности вводимого интервала задержки с заданным значением допуска и при выполнении устройством заданного числа итераций результат сравнения с его выходов поступает через открытые элементы 28 и 30 совпадений и элементы ИЛИ 23 и 24 на входы блока 31 ин35

40

45

50

55

0

5

раньше, чем на его второй вход, Оэто означает, что первым на триггер поступил фронт с выхода поверяемого измерительного компаратора 3. Указанные условия выполняются с погреш5 ностью дискретности, определяемой периодом следования тактовых импульсов 10 генератора.

Элемент 11 задержки компенсирует паразитную задержку прохождения сигнала в блоке 14 управляемой задержки. В соответствии с указанными условиями цифровой компаратор 12 (фиг,2) в первом и третьем случаях вырабатывает отрицательный импульс соответственно на первом выходе Меньше и втором выходе Больше, 1 во втором случае оставляет высокие уровни обоих выходов без изменения, а реверсивный счетчик 15 уменьшает

о или увеличивает на 1 выходной код по заднему (положительному) фронту импульса, поданного соответственно на первый или третий его входы.Элемент ИЛИ-НЕ 13 по любому положительному импульсу на его входах вырабатывает отрицательный импульс, сбрасывающий триггеры 5 и 6 в исходное нулевое состояние и задержанный относительно входного на такую задержку, которая гарантирует срабатывание за это время цифрового компаратора 12 и реверсивного счетчика 15.

Блок 9 принятия решения работает следующим образом (фиг.З). Счетчик 22 подсчитывает число срабатываний триггера 6 устройства и при достижении этим числом значения, заданного в задатчике 26 кода (число итераций), элемент 27 сравнения кодов открывает элементы 2б и 30 совпадений. Элемент 21 сравнения кодов сравнивает текущий инверсный код длительности вводимого интервала задержки с заданным значением допуска и при выполнении устройством заданного числа итераций результат сравнения с его выходов поступает через открытые элементы 28 и 30 совпадений и элементы ИЛИ 23 и 24 на входы блока 31 ин5

0

5

0

5

11

дикации. Если в течение работы устройства его реверсивный счетчик 15 вырабатывает один из сигналов Переполнение или Меньше нуля, эти сигналы поступают через элементы ИЛИ 23 или 24 на входы блока 31 индикации.

При наличии 1 на первом или втором входах блока 31 индикации в нем индицируется результат поверки Брак или Годен соответственно и на выходе элемента ИЛИ 32 устанавливается уровень логического О, являющийся сигналом Стоп устройства.

Формула л изобретения

20

25

47456712

сигнала, образцовый измерительный компаратор, клеммы для подключения входов и выхода поверяемого иэмери- 5 тельного компаратора, блок задержки, цифровой компаратор, блок принятия решения, выход источника постоянного испытательного сигнала соединен с клеммой для подключения первого вхо10 да поверяемого и первым входом образцового измерительных компараторов, выход блока задержки соединен с первым входом цифрового компаратора, отличающееся тем, что,

15 с целью повышения достоверности поверки, в него введены генератор случайно изменяющегося испытательного сигнала, первый и второй триггеры, первый и второй элементы совпадения, генератор импульсов стабильной частоты, логический элемент И-НЕ, блок управляемой задержки, реверсивный счетчик, логический инвертор, за- датчик кода, при этом выход генератора случайно изменяющегося испытательного сигнала соединен с клеммой для подключения второго входа поверяемого и второго входа образцового измерительных компараторов, выход образцового измерительного компаратора соединен с первыми входами первого триггера, клемма для подключения выхода поверяемого компаратора соединена с входом второго триггера, выход первого триггера соединен с первым входом первого элемента совпадения, выход второго триггера соединен с первыми входами второго элемента совпадения и блока принятия решения, вторые входы элементов совпадения соединены с выходом генератора импульсов стабильной частоты, выход первого элемента совпадения соединен с входом блока задержки, выход которого соединен с первым входом логического элемента ИЛИ-НЕ,выход второго элемента совпадения соединен с первым входом блока управляемой задержки, второй вход которого соединен с одноименными входами блока принятия решения, логического элемента ИЛИ-НЕ, реверсивного счетчика, входом логического инвертора и внешним запускающим входом, выход блока управляемой задержки соединен с вторым входом цифрового компаратора и третьим входом логического элемента ИЛИ-НЕ, выход которого соединен с. вторыми входами первого и

30

35

40

45

50

55

второго триггеров, третьи входы ко- торых соединены с выходом блока принятия решения, первый и второй выходы цифрового компаратора соединены соответственно с первым и третьим входами реверсивного счетчика, первый- выход которого соединен с третьими входами блока управляемой задержки

и блока принятия решения, второй и третий выходы реверсивного счетчика соединены соответственно с четвертым и пятым входами блока принятия решения, выход логического инвертора соединен с четвертым входом реверсивного счетчика, пятый вход которого соединен с выходом задатчика кода.

Фиг. 2

| Вондаревский А.С., Фролов Я.Н | |||

| Электронная промышленность, 1985, вып | |||

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Способ образования коричневых окрасок на волокне из кашу кубической и подобных производных кашевого ряда | 1922 |

|

SU32A1 |

| Устройство для охлаждения водою паров жидкостей, кипящих выше воды, в применении к разделению смесей жидкостей при перегонке с дефлегматором | 1915 |

|

SU59A1 |

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

Авторы

Даты

1989-04-23—Публикация

1987-06-25—Подача