1Ч

Изобретение относится к измерительной технике и предназначено для автоматического контроля и измерения параметров аналого-цифровых преобразователей (АЦП),. а также может быть использовано при построении информационно-измерительных систем.

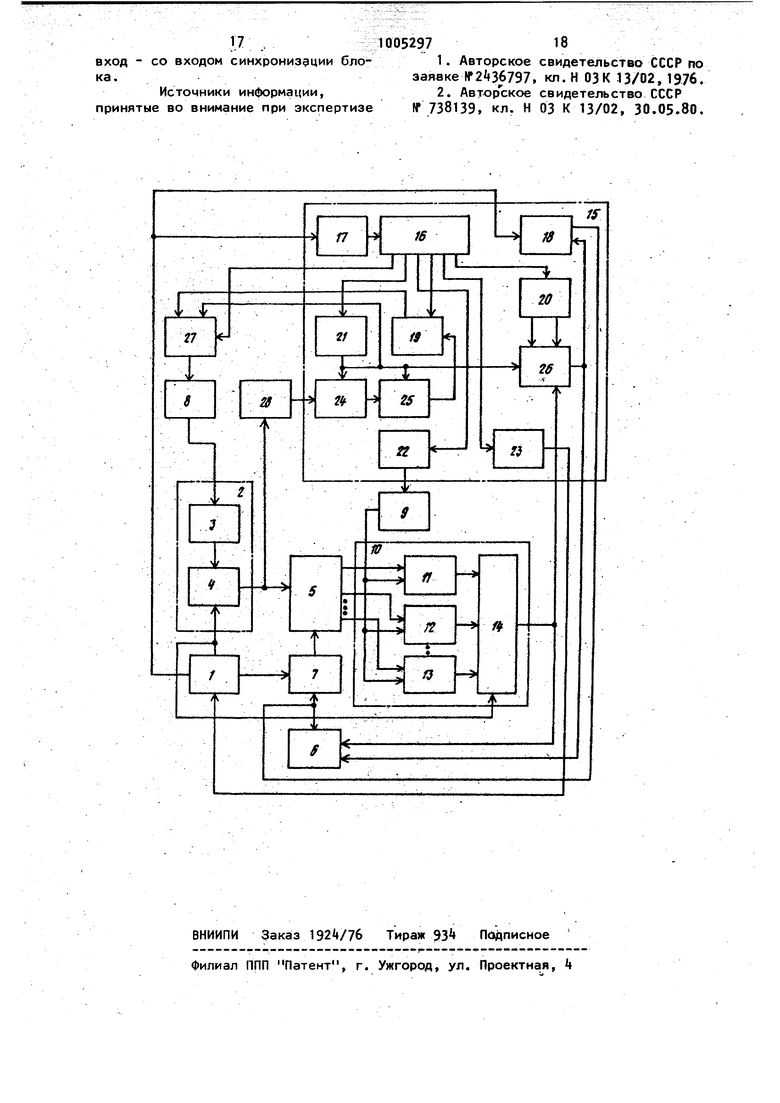

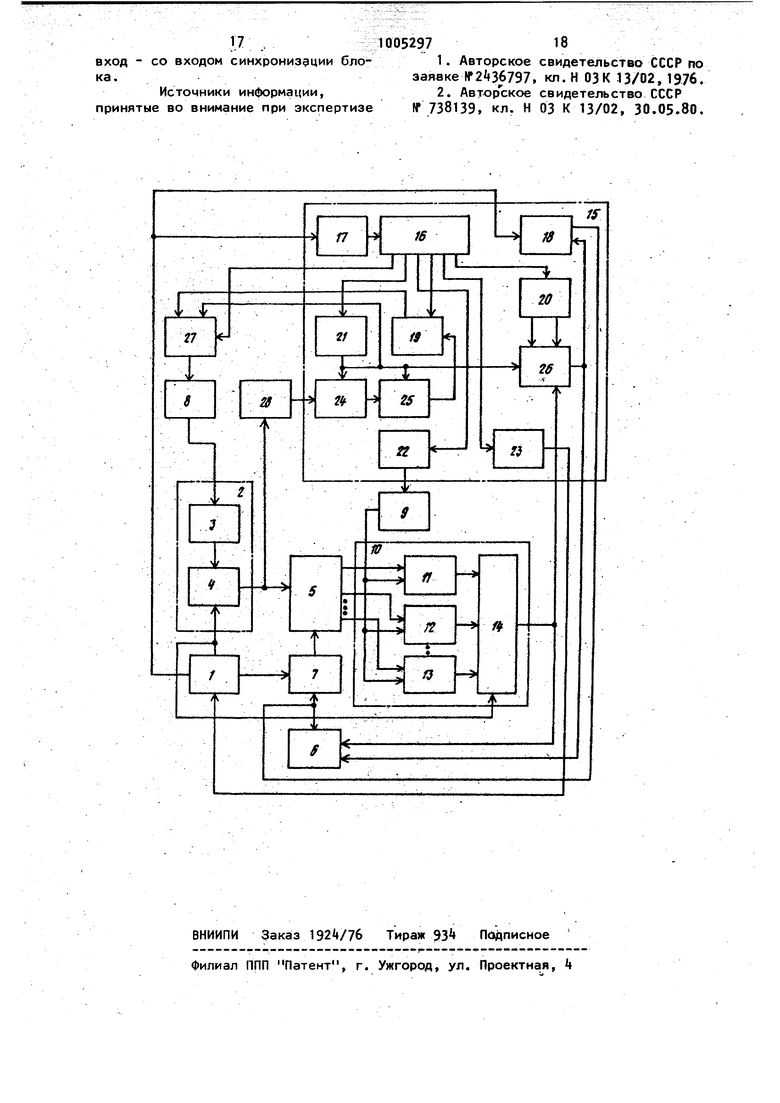

Известно устройство для проверки аналого-цифровых преобразователей, содержащее источник входного сигнала, выход которого соединен с первыми входами образцового и проверяемого аналого-цифровых преобразователей и через умножитель частоты соединен с первым входом вентиля, второй вход которого соединен с выходом счетчика, а второй вход соединен с первым выходом переключателя, второй выхОд которого соединен с первым входом элемента ИЛИ, а вход через кнопку соединен с входной шиной устройства, второй вход элемента ИЛИ соединен с выходом вентиля и с входом первого делителя частоты, выход которого соединен с входом счетчика, выход элемента ИЛИ соединен с вторыми входами образцового и проверяемого аналогоцифровых преобразователей, а выход второго делителя частоты соединен с входами регистрирующего устройства, выход элемента ИЛИ через линию задержки соединен с первым входом реверсивного счетчика, второй вход которого соединен с выходом проверяемого аналого-цифрового преобразователя, выход образцового аналого-цифрового преобразователя соединен с первым входом устройства сравнения ко дов, второй вход которого соединен с выходом реверсивного счетчика, а первый , второй и третий выходы соединены соответственно с входом генератора импульсов и с третьим и четвертым входами реверсивного счетчика, пятый вход которого соединен с выходом генератора импульсов и входом второго делителя частоты С 1. Однако данное устройство не обеспечивает достаточную точность измерения параметров аналого-цифровых пр образователей и имеет ограниченные функциональные возможности. Известно устройство для измерения характеристик аналого-цифровых преобразователей, содержащее источник входного сигнала, выход которого соединен с первыми входами образцового и проверяемого аналого-цифровых преобразователей, причем выход образцового аналого-цифрового преобразователя соединен с первым входом блока сравнения кодов, второй вход которого соединен с выходом реверсивного счетчика, а первый, второй и третий выходы соединены соответственно с вх дом генератора импульсов и с первым и вторым входами реверсивного сметчика, третий вход которого соединен выходом генератора импульсов и входом делителя частоты, выход элемента ИЛИ через линию задержки соединен с четвертым входом реверсивного счетчика, пятый вход которого соединен с выходом проверяемого аналогоцифрового преобразователя, первый вход вентиля соединен с выходом три)- гера, первый вход которого соединен с первым выходом переключателя, второй выход которого соединен с первым входом элемента ИЛИ, а вход через кнопку соединен с входной шиной устройства, второй вход элемента ИЛИ соединен с выходом вентиля, выход элемента ИЛИ соединен с вторыми входами проверяемого и образцового аналого-цифровых преобразователей, выхо делителя частоты соединен с входами регистрирующего блока, причем синхро низатор подключен своим выходом к управляющему входу вентиля, а входом - к четвертому выходу блока срав нения кодов и к первому входу задатчика максимальной погрешности, второй вход которого соединен с выходом генератора, а выходы задатчика максимальной погрешности, образцового и проверяемого аналого-цифровых преобразователей подключены к входам элемента памяти, при-этом выход вентиля подключен к входу счетмика коли чества измерений, выход которого под ключен к входу счетчика количества измерений, выход которого подключен к управляющему входу делителя частоты и второму входу триггера tzj. Однако данное устройство имеет ограниченные функциональные возможности, так как оно позволяет определять лишь значения статической погрешности преобразования проверяемых АЦП. Целью изобретения яёляется расширение функциональных возможностей и повышение достоверности результатов исследований. Поставленная цель достигается тем, что в устройство для измерения и контроля параметров аналого-цифровых преобразователей, содержащее источник входного сигнала, выход которого соединен с первыми входами проверяемого и образцового аналого-цифровых преобразователей, управляемый генератор импульсов, управляемую линию задержки и регистрирующий блок введены первый и второй преобразователи код-напряжение, коммутатор кодов, блок компараторов и вычислительный блок, причем выход первого преобразователя код-напряжение соединен с первым входом источника входного сигнала, а вход соединен с выходом коммутатора кодов, первый, второй и третий входы которого соединены соответственно с первым, вторым и третьим выходами вычислительного блока , четвертый выход которого соединен со входом второго преобразователя код-напряжение, пятый - со входом управляемого генератора импульсов, шестой - с первым входом регистрирующего блока, седьмой - со вторым входом последнего и первым входом«рправляемой линии задержки, при этом первый и второй входы соединены с первым выходом управляемого генератора импульсов, третий вход - с выходом образцового аналого-цифрового преобразователя, а четвертый с третьим входом регистрирующего блока и с выходом блока.компараторов, информационные входы которого соответственно соединены с выходами проверяемого аналого-цифрового преобразователя, управляющий вход соединен с выходом второго преобразорателя код-напряжение, а вход синхронизации соединен со вторым выходом управляемого генератора импульсов и со вторым входом источника входного сигнала, а третий выход - со вторым входом управляемой линии задержки, выход которого соединен со вторым входом проверяемого аналого-цифрового преобразователя. Кроме того, вычислительный блок содержит первый и второй счетчики импульсов, дешифратор, узел вычитания кодов, сумматор, узел сравнения кодов и первый, второй, третий, четвертый и пятый регистры, причем выходы дешифратора подключены соответственно к первым входам первого, второго, третьего, четвертого , и пятого регистров и к третьему выходу блока, второй же выход его соединен с выходом первого регистра, второй вход которого соединен с выходом сумматора, первый вход которого соединен с выходом узла вычитания кода, первый зход которого соединен с третьим входом блока, а второй вход соединен с выходом второго регистра, вторым входом сумматора, первым выходом блока и с первым выходом узла сравнения кодов, второй вход которого, соединен с четвертым входом блока, а третий и четвертый входы с выходами третьего регистра, а выход соединен с шестым выходом блока и с первым входом первого счетчика, второй вход которого соединен со вторым входом блока, а выход соединен с седьмым выходом бло ка, первь1й вход которого через второ счетчик соединен со входом дешифратора, а четвертый и пятый выходы блока соединены соответственно с выходами четвертого и пятого регистР Блок компараторов содержит и компараторов, первые входы которых соединены с информационными входами бл ка, вторые входы с управляемым входо блока, а выходы соответственно со 8x дами регистра запоминания кода, выход которого соединен с выходом блока, а управляющий вход - со входом синхронизации блока. На чертеже представлена схема уст ройства для измерения, и контроля параметров аналого-цифровых преобразов телей, содержащего управляемый генератор 1 импульсов, источник 2 входно го сигнала, состоящий из управляемого источника 3 тока и диодного комму татора , проверяемый аналого-цифровой преобразователь 5 регистрирующий блок б, управляемую линию задерж ки 7 первый преобразователь 8 код-н пряжение, второй преобразователь 9 код-напряжение, блок 10 компараторов состоящий из компараторов 11-13 и ре гистра 1 запоминания кода, вычислительный блок 15, состоящий из дешифратора 16, счетчиков 17 и 18 импу.гТьсов, регистров узла 2k вычитания кодов, сумматора 25 и узла 26 сравнения кодов, коммутатор 27 кодов, образцовый аналого-цифровой преобразователь 28. Устройство работает следующим образом. Устройство позволяет производить контроль уровней напряжений логических О и 1 выходного кода проверяемого ана/юго-цифрового преобразователя (АЦП) 5. Для контроля напряжения логического О на выходах АЦП 5 с дешифратора 16 вычислительного блока 15 на вход регистра 21 поступает код нулевой точки (Np) диапазона изменения входного сигнала проверяемого АЦП 5 (т.е. код входного сигнала, соответствующего выходному коду АЦП 5 вида 00,...,00). Одновременно с дешифратора 16 на регистр 23 поступает код команды для управляемого генератора 1. По данной команде формируетсярежим работы управляемого генератора 1 (потенциальный режим) и осуществляется его запуск. Тактовые импульсы с управляемого генератора 1 поступают на счетчики 17 и 18 импульсов вычислительного блока 15 для синхронизации работы отдельных узлов устройства. Первый тактовый импульс с управляемого генератора 1, поступающий на счетчик 17, формирует с дешифратора 16 команду на коммутатор кодов 27, согласно которой через коммутатор кодов 27 на вход первого преобразователя 8 код-напряжение поступает код (Np) нулевой точки диапазона, записанный в регистре 21. На выходе преобразователя 8 устанавливается соответствующее значение напряжения, которое поступает на управляемый источник 3 тока источника 2 входного сигнала. Под воздействием напряжения с выхода преобразователя 8 управляемый источник 3 тока генерирует соответствующее значение тока, который через диодный коммутатор Ц поступает на нагрузку, которой является входное сопротивление проверяемого АЦП 5. Диодный коммутатор k управляется выходным сигналом управляемого генератора 1 импульсов, В потенциальном режиме работы управляемого генератора 1 выходной сигнал является потенциалсми, обеспечивающим открытое состояние диодного коммутато7pa 4. Таким образом, на нагрузке точника 2 входного сигнала, которой является входное сопротивление АЦП 5 формируется сигнал , соответствующий нулевой точке диапазона. Данное значение сигнала измеряется образцовым АЦП 28 и получаемый кодовый эквивалент NP характеризуется погрешностью, вносимой преобразователем 8 и источником 2. Коды м с регистра 21 и rJ с образцового АЦП 28 вычитаются в узле 2Ц вычитания кодов, а полученная разность добавляется в сумматоре 25 к величине NQ , поступающей с регистра 21. Скорректированное значение кодаNO N(,-(Wo-No ) хранится б регистре 19 и с его выхода поступает на коммутатор кодов 27. Начиная со второго цикла работы устройства, по команде с дешифратора 16 коммутатор кодов 27 передает скорректированное значение кодовЫ -Коррекция значения входного сигнала проверяемого АЦП 5 до значения, соответствующего выходному коду вида . 00,.. ..00, продолжается аналогично на протяжении и циклов, количество которых априорно выбирается из условия обеспечения заданной точности установ ки. По истечении м циклов работы устройства, количество которых фиксирует ся счетчиком 17, с дешифратора 16 на регистр 23 поступает новая команда на управляемый генератор 1, дополнительно разрешающая выдачу синхроимпульса с управляемого генератора 1 на управляемую линию задержки 7. При этом величина задержки, заведомо превышающая время переходных процессов АЦП 5 задается соответственно числу, записанному в счетчике 18 вычислительного блока 15. Задержанный синхроимпульс с выхода управляемой линии задержки 7 запускает проверяемый АЦП 5 который осуществляет преобразование нулевого входного сигнала в соответст вующее значение кода. Выходной код АЦП 5 поступает на первые входы компараторов 11-13 блока 10 компараторов, на вторые входы которых nocTyna, ет опорное напряжение с выхода второго преобразователя 9 код-напряжение. соответствующее верхней ( по абсолютной величине) границе диапазона напряжений логического О. Значение верхней границы диапазона напряжения логического нуля задается кодом, поступающим с дешифратора 16 вычислительного блока 15 и хранящемся в реис- гистре 22, выход которого подключен 10052978 ко входу преобразователя 9 код-напряжение. Максимальное количество компараторов 11-13 соответствует количеству разрядов выходного кода АЦП 5. Выходные разряды АЦП 5° в которых напряжение логического нуля лежит в допустимых пределах (т.е. меньше опорного сигнала), при сравнении с ним дают на соответствующих выходах компараторов логический О, а разряды, где напряжение О больше опорного сигнала (т.е. выходит за границы допустимого), проявляют себя появлением логической 1 на выходах соответствующих компараторов. Выходы компараторов t1-13 подключены к регистру 1А запоминания кода блока 10 компараторов, где фиксируется выходной код АЦП 5 по управляющему сигналу . е генератора 1. С выхода регистра I выходной код АЦП 5 поступает на регистрирующий блок 6. Наличие логических 1 в разрядах данного кода говорит о неверной работе соответствующих разрядов проверяемого АЦП 5. Аналогично производится контроль значений напряжения логической 1 в выходных разрядах АЦП 5. При этом на входе проверяемого АЦП 5 устанавливается максимальное значение входного сигнала (т.е. такое, которое соответствует выходному коду АЦП 5 вида 11,..., 11 ), а в регистр 22 записывается код напряжения, соответствующего нижней (по абсолютной ве 3ичине границе диапазона напряжений логической 1. Выходной код АЦП 5 поступает на регистрирующее устройство 6. Наличие логических О в разрядах выходного кода говорит о неверной работе соответствующих разрядов проверяемого АЦП 5. Так как с помощью регистра 22 и преобразователя 9 возможно задание различных опорных сигналов для компараторов 11-13 данное устройство позволяет разбраковывать по уровню напряжений логических О и 1 различные по типу применяемой логики аналого-цифровые преобразователи. При исследовании статической погрешности преобразования АЦП 5 устройство работает следующим образом. С дешифратора 16 вычислительного блока 15 на вход регистра 21 поступает код (Мц) поверяемой точки диапазона изменения входного сигнала. 91 АЦП 5 (где к - номер точки). Дальнейший процесс формирования входного сигнала Uj с заданной точностью аналогичен описанному выше режиму. Задержанный синхроимпульс с выхода управляемой линии задержки 7 запускает проверяемой АЦП 5, который осуществляет преобразование напряжения Uj к-й поверяемой точки диапазона в соответствующее значение, выходного кода (N) АЦП 5. Зафиксированный выходной код (NjJ) проверяемого АЦП 5 поступает на регистрирующий блок 6 и на узел 2б сравнения кодов вычислительного блока 15. Узел 2б сравнения кодов срёвнивает.начальный кодовый эквивалент (NI) поверяемой точки диапазона изменения входного сигнала АЦП 5 поступающий с регистра 21, и полученный в результате преобразования выходной код N проверяемого АЦП 5. При этом вычисляется абсолютное значение статической погрешности преобразования АЦП 5 Ak | N |, - кодовом представлении и происходит сравнение полученного значения статической погрешности АЦП 5 с заданными из регистра 20 вычислительного блока 15 допустимыми значениями статической погрешности. В результате вырабатывается сигнал Норма, свидетельствующий о том, что у проверяемого АЦП 5 статическая погреш,..,,,.v, ... „-..Jность не превышает допустимых значений в допусковой области) и передается на регистрирующий блок 6. В противном случае значение абсолютной статической погрешности дк и преобра |. зованное значение N поверяемой точки индицируется на регистрирующем бло ке 6. Аналогично производится измере ние и контроль статической погрешнос ти преобразования АЦП 5 для любой точ ки диапазона изменения входного . Устройство позволяет также измерят и контролировать динамические характе ристики проверяемого АЦП 5, а именно время преобразования и динамическую погрешность преобразования, В режиме измерения времени преобразования аналогично описанному (для режима измерения статической погрешности) производится измерение проверяемым АЦП 5 фиксированного входного сигнала )UK|, соответствующего к-й точке диапазона изменения входного сигнала. Цифровой эквивалент )W|( I из9710меряемого сигнала } UK I фиксируется в блоке 10 компараторов и запоминается в регистре 1 запоминания кода. Далее с дешифратора 16 на регистр 23 вычислительного блока 15 поступает новая команда на управляемый генератор 1 импульсов, которая переводит генератор 1 в динамический режим работы ( на выходе генератора формируются импульсы напряжения фиксированной длительности и амплитуды. Таким образом, управляющий сигнал, поступаю-, щий с генератора 1 на диодный коммутатор Ц источника 2 входного сигнала, является импульсом, временные характёристики которого определяют время существования фиксированного входного сигнала I (JK I на входе проверяемого АЦП 5. По этой же команде на управляемый генератор 1 импульсов осуществляется его запуск и импульс синхронизации со второго выхода генератора 1 поступает „через управляемую линию задержки 7 на второй вход проверяемого АЦП 5 с задержкой, ,величина которой заведомо больше расчетного значения времени переходных процессов проверяемого АЦП 5 ( TqpjjppojjJ и задается числом, записанным в счет-. чике 18 импульсов. Таким образом первое преобразованное значение проверяемого АЦП 5, полученное в.динамическом режиме, фиксируется в блоке 10 компараторов относительно нижней границы диапазона напряжения логической 1 задаваемой преобразователем 9 и запоминается в регистре И. Это значение не будет отличаться от соответствующего значения выход 1 Vr I кз cii/л w кода АЦП 5 в статическим режи Данное значение ) с регистра запоминаниякодов поступает на узел 26 сравнения кодов вычислительного блока 15. Узел 2б сравнения кодов сравнивает начальный кодовый эквивалент (Njc) поверяемой точки диапазона изменения входного сигнала АЦП 5, поступающий на схему 26 с регистра 21, и полученный в результате преобразования выходной код проверяемого АЦП 5 () . При этом вычиспяется абсолютное значение погрешности преобразования АЦП 5 АК ((() в кодовом представлении и происходит сравнение полученного значения погрешности преобразования АЦП 5 с заданными из регистра 20 допустимыми знамениями, погрешности. Если погрешность преобразования проверяемого АЦП 5 R данном цикле не превышает допустимых значений V в допусковой области), то вырабатывается сигнал Норма и по этому сигналу, поступагощему на счет чик 18, значение задержки уменьшается на единицу. Уменьшенное на единицу значение задержки поступает на управляемую линию задержки 7 и регистрирующий блок 6, но не регистрируется, так как на регистрирующий блок 6 так же поступает сигнал Норма с выхода узла 26 сравнения кода и запрещает регистрацию текущего значения задержки . о Описанный цикл измерения входного прямоугольного импульса проверяемым АЦП 5 повторяется Ш раз с той лишь разницей, что интервал времени от момента b-f поступления измеряемого импульса (Uic) на первый вход проверяемого АЦП 5 до момента Ь поступления на второй вход АЦП 5 синхроимпульса с выхода управляемой линии задержки 7 постоянно в каждом цикле уменьшается на одну единицу дискретности задания задержки. Для гм-го цикла измере ния сигнал (j подается в течении времени пЛ () t . Очевидно, если при т-ом измерении величина задержки, задаваемая управляемой линией задер) 7 станет меньше времени переходных процессов Тперпрац Р° веряемого АЦП 5 то на входе АЦП 5 в момент прихода запускающего импульса с управляемой линии задержки 7 не успевает установиться полное значение входного сигнала 0. ив резуль тате преобразования на выходе АЦП 5 появляется код , отличный от N, который фиксируется в регистре 1 за поминания кода блока 10 компараторов. В данном hi-oM цикле сравнение выходного кода АЦП 5 с начальным кодовым эквивалентом (,Nt(,) поверяемой точки диапазона в узле 2б сравнения кодов, а также вычислен-, ного значения погрешности с границами допусковой области погрешности пр образования покажет, что погрешность преобразования превышает допустимые значения. На выходе узла 26 сравнения кодов не будет сформирован сигнал Норма, что запрещает дальнейшее уменьшение значения задержки в счетчике 18 импульсов и разрешает регистрацию зафиксированного значения задержкой с выхода счетчика 18 в регистрирующем блоке 6. Данное зна чение задержки соответствует иско;мому значению времени переходных процессов во входных цепях проверяемого АЦП 5, являющемуся одной из составляющих собственно времени преобразования Т„р Т„еу Тфор„ В режиме определения времени формирования выходного кода Т «|цявдв проверяемого АЦП 5 аналогично описанному (для режима измерения времени переходных процессов) задается динамический режим работы устройства. Управляемый генератор 1 импульсов по команде с регистра .23 вычислительного блока 15 переведен в динамический режим. На выходе источника 2 входного сигнала АЦП 5 формируется сигнал (и), являющийся прямоугольным импульсом, нормированным по амплитуде (и циклов коррекции в статическом режиме) и по длительности, который определяется временными характеристиками управляющего импульса с первого выхода генератора 1 на вход диодного коммутатора А. Производится запуск генератора 1 по команде с регистра 23. Импульс синхронизации со второго,выхода генератора 1 поступает через управляемую линию задерх ки 7 на второй вход проверяемого АЦП 5 с задержкой относительно заднего фронта измеряемого импульса (Ок) , величина которой заведомо больше расчетного значения времени формирования выходного кода проверяемого АЦП 5 и задается числом, записанным в счетчике 18 импульсов. Кроме того, длительность входного измеряемого импульса (UK) на первом входе проверяемого АЦП 5, задаваемая с управляемого генератора 1, больше расчетного значения собственно времени преобразования проверяемого АЦП 5. Таким образом, первое преобразованное значение Мц проверяемого АЦП 5 полученное в динамическом режиме, фиксируется в блоке 10 компаратора и запоминается в регистре 1 запоминания кода по управляющему сигналу ( прямоугольный импульс) с первого выхода генератора 1. Это значение не отличается от соответствующего выходного кода АЦП 5 в статическом режиме. Данное значение кода (N ) с выхода регистра 1k поступает на узел 26 сравнения кодов вычислительного блока 15 Узел 2б сравнения кодов сравнивает начальный кодовый эквивалент (NK) Кй точки диапазона изменения входного сигнала АЦП 5 с регистра 21 и полученное значение кода N . При этом, если погрешность преобразования АЦП 5 в данном цикле не превыша ет допустимых значений, то вырабаты вается сигнал Норма, и по этому сигналу, поступающему на счетчик 18 импульсов, записанное в счетчике зна чение задержки уменьшаетея на одну единицу. Уменьшенное на единицу зна чение задержки поступает на управля емую линию задержки 7 и регистрирую щий блок 6, но не регистрируется, так как на регистрирующий блок 6 поступает также сигнал Норма, запрещающий регистрацию теку1чего значения задержки. Описанный цикл -измерения входного прямоугольного импульса ( U ) проверяемого АЦП 5 повторяется g рэз с той лишь разницей, что интервал времени от момента Ь поступления на второй вход АЦП 5 синхроимпульса с выхода управляемой линии задержки 7 до момента -Ьд, окончания измеряемого импульса Щ(. ) на первом входе проверяемого АЦП 5 постоянно уменьшаетс в каждом цикле измерения на одну еди ницу дискретности задания задержки. Для 5-го цикла измерения сигнал Уц на первом входе проверяемого АЦП 5 закончится относительно поступающего на второй вход проверяемого АЦП 5 с выхода управляемой линии задержки 7 синхроимпульса по истечении временного интервала ,--ta-ttz-(S-n. Очевидно, если при 5-ом цикле измерения величина задержки, задаваемая управляемой линией задержки 7, о момента -t окончания импульса входного сигнала (UK) относительно момента -fc поступления на второй вход АЦП 5 синхроимпульса станет меньше времени формирования выходного кода проверяемого АЦП, 5 ( выход ной код АЦП 5 (NK } , поступающий по следним на вход блока 10 компараторов в момент окончания управляющего импульса на входе синхронизации регистра запоминания кода и являющийся последним запомненным в ре.гистре значением выходного кода АЦП 5 за время существования управляющего импульса на входе синхронизации регистра Н, не будет совпадать с кодом . В данном 5-ом цикле сравнения выходного кода АЦП 5 М,.) который зафиксирован в регистре 1 бпока 10 KOMnnpaTOpf B с началь ным кодовым эквивалентом (N ц) точки диапазона в узле 26 сравнения кодов, а также вычисленного значения погрешности с границами допусковой области погрешности преобразования покажет, что погрешность преобразования в данном S-ом цикле измерения превышает допустимые значения. На выходе узла 2б не будет формирован сигнал Норма, что запрещает дaльнe 1шee уменьшение значения задержки в счетчике 18 и разрешает регистрацию зафиксированного значения задержки с выхода счетчика 18 в регистрирующем блоке 6. Данное значение задержки соответствует искомому значению времени формирования выходного кода проверяемого АЦП 5. Это вторая составляющая собственно времени преобразования АЦП 5. I . Устройство позволяет произвести измерение и контроль динамической погрешности преобразования ( в общем случае построение переходной характеристики проверяемого АЦП 5. Данный режим реализуется аналогично режиму измерения времени переходных процессов АЦП 5. Разница заключается в том, что задаются разные значения величины задержки {число в счетчике 18) синхроимпульса, поступающего со второго выхода генератора 1 через линию задерхжи 7 иа второй вход АЦП 5 относительно момента прихода - измеряемого сигнала О , . В результате фиксируем выходной код АЦП 5C.N ) и абсолютное значение, динамической погрешности преобразования АЦП 5 для текущего значения задержки и получаем переходную характеристику АЦП 5. Это позволяет производить оперативный анализ переходной характеристики по различным критериям. При колебательном характере переходной характеристики исключается неоднозначность определения времени преобразования проверяемого АЦП 5. Все это определяет повышение достоверности результатов исследования. Таким образом, устройство позволяет измерять и контролировать значения напряжений логического О и 1 на выходах проверяемого АЦП, а также разбраковывать АЦП по этому критерию, позволяет также измерять и контролировать динамические характег)йстики проверяемых АЦП время преоПрлзов.чнмя, динамическую погрешность и моетные динамические параметры ЛЦГ1 ( ир«мн переходных процессов, время формирова ния выходного кода). Последние позв ляют выявить степень влияния отдель ,ных узлов исследуемых АЦП на их динамические характеристики. Возможность измерения динамической погреш ности АЦП предполагает оперативное отображение кривой переходного процесса установления кода на выходе исследуемого АЦП С переходнаяхарактеристика АЦП) и анализ характерных точек данной кривой. В частности, при колебательном характере переход ной характеристики исключается неоднозначность определения времени преобразования АЦП, что в свою очередь повышает достоверность результатов исследования. формула изобретения ,1 . Устройство для измерения и контроля параметров аналого-цифровы преобразователей, содержащее источни входного сигнала, выход которого со единен с первыми входами проверяемо и образцового аналого-цифровых преобразователей, управляемь|й гене-: ратор импульсов,управляемую линиию задержки и регистрирующий блок, отличающееся тем, что, с целью расширения функциональных возможностей и повышения достоверности результатов исследования, в него введены первый и второй преобразователи код-напряжение, коммутатор кодов, блок компараторов и вычислительный блок, причем выход пер вого преобразователя код-напряжение соединен с первым входом источника входного сигнала, а вход соединен с выходом коммутатора кодов, первый второй и третий входы которого соединены соответственно с первым, вт рым и третьим выходами вычислительного блока, четвертый выход которого соединен со входом второго преоб разователя код-напряжение, пятый входом управляемого генератора импульсов, шестой - с первым входом регистрирующего блока, седьмой со вторым входом последнего и первым входом управляемой линии задерж ки, при этом первый и второй входы соединены с первым выходом управляемого генератора импульсов, третий вход - с выходом образцового аналого-цифрового преобразователя, а чет вертый - с третьим входом регистри716рующего блока и с выходом блока компараторов, информационные входы которого соответственно соединены с выходами проверяемого аналого-цифрового преобразователя, управляющий вход соединен с выходом второго преобразователя код-напряжение, а вход синхронизации соединен со вторым выходом управляемого генератора импульсов и со вторым входом источника входного сигнала, а третий выход со вторым входом управляемой линии заде|эжки, выход которой соединен со вторым входом проверяемого аналогоцифрового преобразователя. 2,.Устройство по п. 1, о т л и чающееся тем, что вычислительный блок содержит первый и второй счетчики импульсов, дешифратор, узел вычитания кодов, сумматор, узел сравнения кодов и первый, второй, третий, четвертый и пятый регистры, причем выходы дешифратора подключены соответственно к первым входам первого, второго, третьего, четвертого, пятого регистров и третьему выходу блока, второй выход его соединен с выходом первого регистра, второй вход которого соединен с выходом сумматора, первый вход которого соединен с выходом узла вычитания кода, первый вход которого соединен с третьим входом блока, а второй вход соединен с выходом второго регистра, вторым входом сумматора, первым выходом блока и с первым выходом узла сравнения кодов, второй вход которого соединен с четвертым входом блока, а третий и четвертый входы с выходами третьего регистра, а выход соединен с шестым выходом блока с первым входом первого счетчика , второй вход которого соединен со вторым входом блока, а выход соединен с седьмым выходом блока, первый вход которого через второй счетчик соединен со входом дешифратора, а четвертый и пятый выходы блока соединены соответственно с выходами четвертого и пятого регистров. 3. Устройство по п. 1, о т л и чающееся тем, что блок компараторов содержит л компараторов, первые входы которых соединены с информационными входами блока, вторые входы с управляемым входом блока, а выходы соответственно со входами регистра запоминания кода, выход которого соединен с выходом блока, а управляющий

17 ,1ff0529718

вход - со входом синхронизации бло-1. Авторское свидетельство СССР по

ка.заявке fPai 36797, кл.Н 03К 13/02J 1976.

Источники информации,2. Авторское свидетельство СССР

принятые во внимание при экспертизеff 738139, кл. Н 03 К 13/02, 30.05.80.

| название | год | авторы | номер документа |

|---|---|---|---|

| Измеритель характеристик аналого- цифРОВыХ пРЕОбРАзОВАТЕлЕй | 1978 |

|

SU819950A1 |

| Аналого-цифровой преобразователь | 1980 |

|

SU884127A1 |

| Устройство для контроля аналого-цифрового преобразователя | 1986 |

|

SU1585897A1 |

| Устройство для ввода информации | 1983 |

|

SU1145336A1 |

| Устройство для измерения динамических параметров быстродействующих аналого-цифровых преобразователей | 1987 |

|

SU1522401A1 |

| Устройство для автоматизированного контроля параметров | 1988 |

|

SU1647520A1 |

| Устройство контроля многоканального аналого-цифрового преобразователя сигналов изображения | 1988 |

|

SU1555919A1 |

| Устройство для регистрации аналогового процесса | 1989 |

|

SU1774379A1 |

| Устройство для поверки цифроаналоговых преобразователей | 1987 |

|

SU1578809A1 |

| Устройство контроля аналого-цифровых преобразователей | 1988 |

|

SU1711327A1 |

Авторы

Даты

1983-03-15—Публикация

1981-02-23—Подача