Изобретение относится к измерительной технике и может быть использовано, например, для бесконтактного измерения скорости движения длин- номерных материалов.

Целью изобретения является повышение точности измерения за счет устранения погрешности измерения,вызванной операциями двойного преобра- зования информативного сигнала и возможными сбоями начала или окончания отсчета временных интервалов.

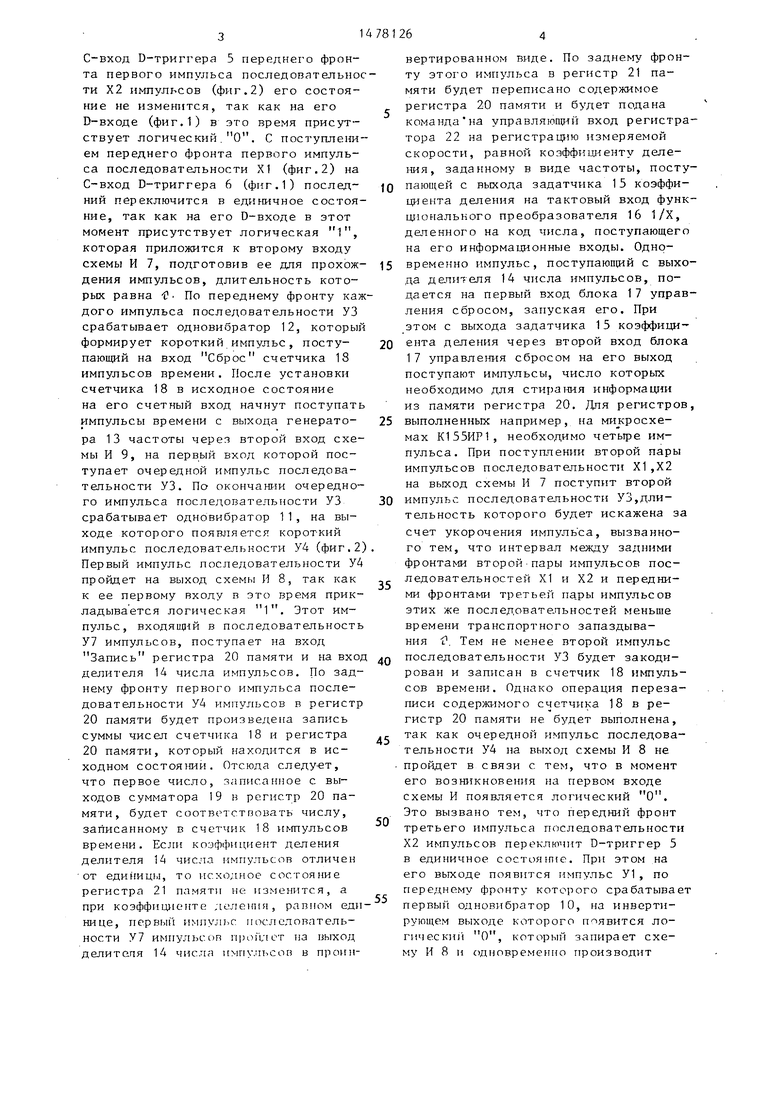

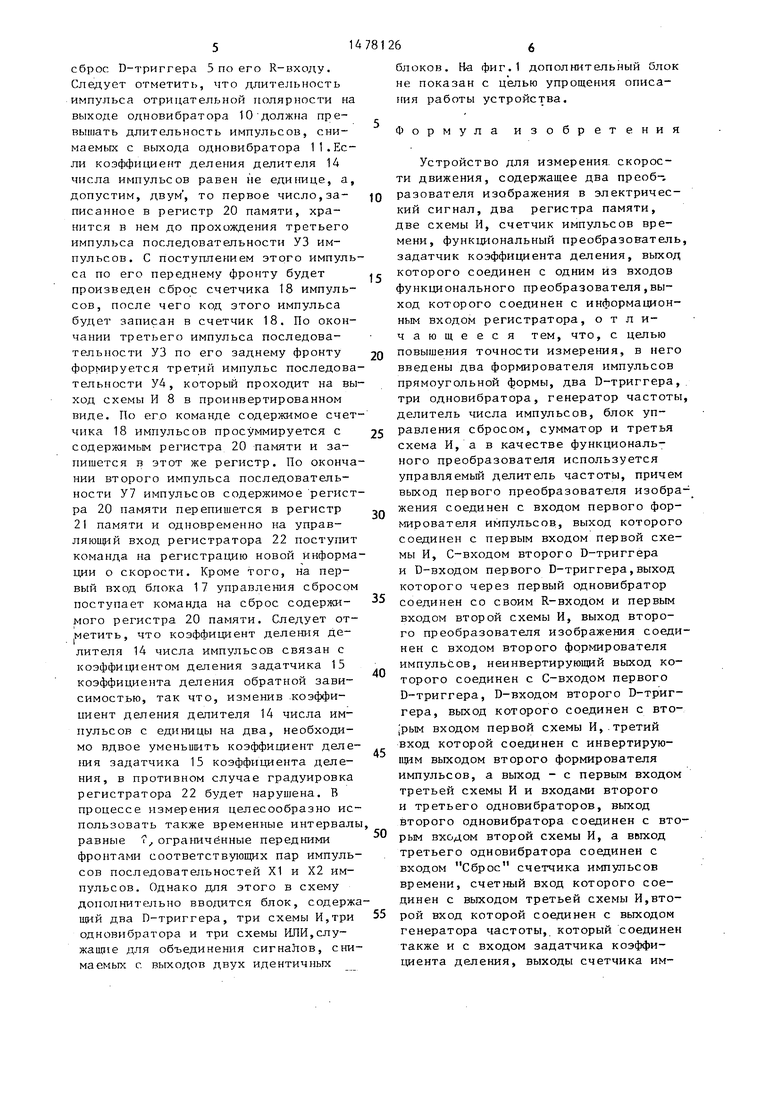

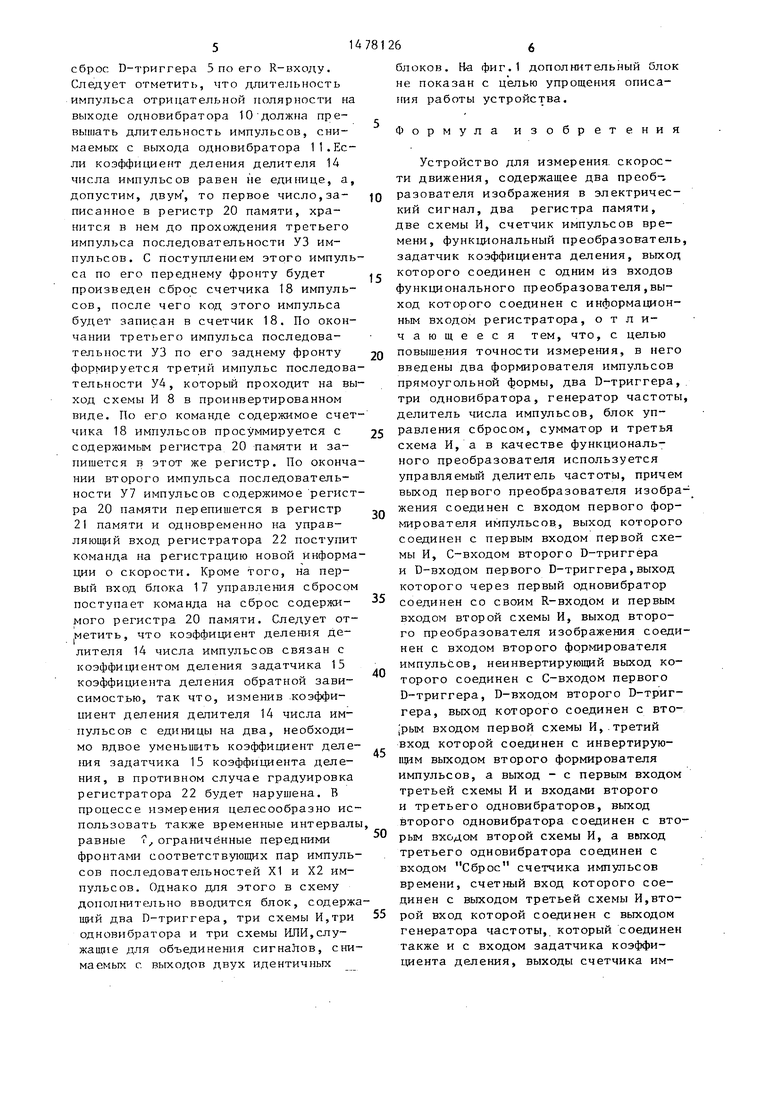

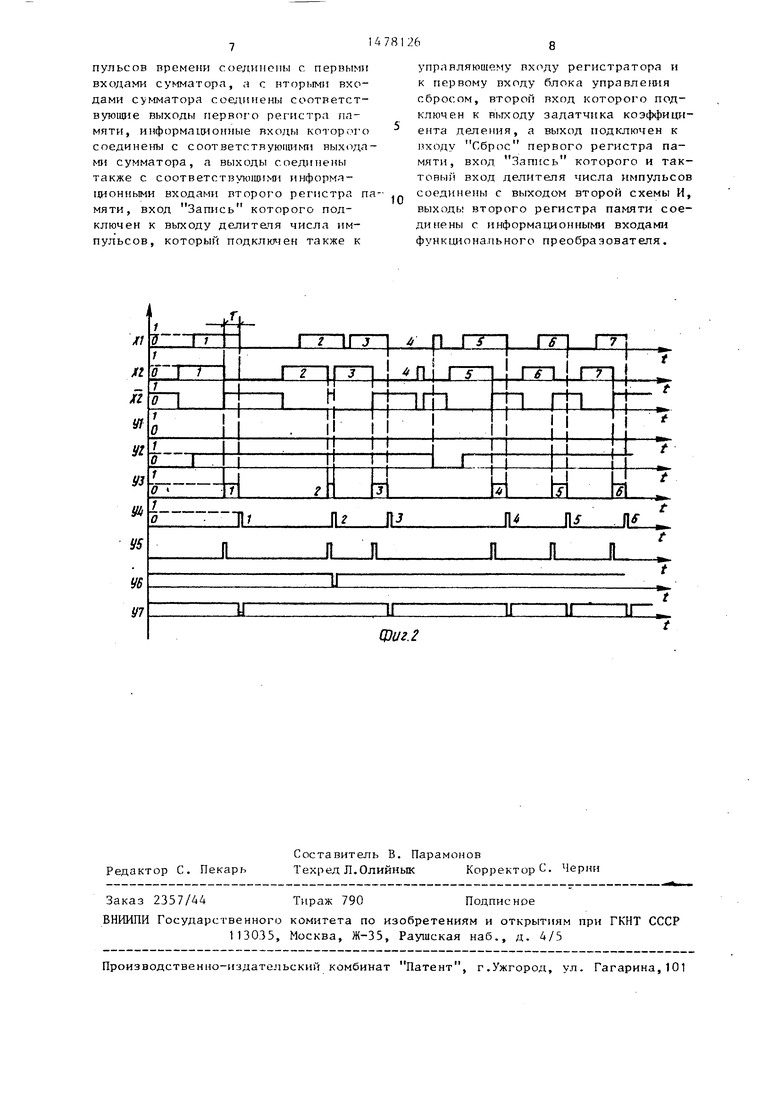

На фиг.1 представлена функциональная схема устройства для измерения скорости движения; на фиг.2 - временные диаграммы сигналов на выходах отдельных элементов.

Устройство для измерения скорости движения (фиг.1) содержит два преобразователя 1 и 2 оптического изображения в электрический сигнал, два формирователя 3 и 4 импульсов прямоугольной формы, два D-триггера 5 и 6, три схемы И 7-9, три одновиб- ратора 10-12, генератор 13 частоты, делитель 14 числа импульсов, задат - чик 15 коэффициента деления, функциональный преобразователь 16 1/Х, блок 17 управпения сбросом, счегчик 18 импульсов времени, сумматор 10, регистры 20 и 21 памяти и регистратор 22. Выход преобразователя 1 изображе гия в электрический сигнал подключен к входу формироватепя j импульсов, выход которого соединен с первым входом первой схемы И /, с С-входом второго D-триггера 6 и D-входом первого D-триггера 5, выход которого через первый одновибратор 10 соединен со своим R-входом и первым входом второй схемы И 8. Выход второго преобразователя 2 изображения в -электрический сигнал соединен с входом формирователя 4 импульсов, неинвёртирукнций выход которого соединен с С-входом первого D-триггера 5 и D-входом второго D-триггера 6, выход которого соединен с вторым входом схемы И 7, третий вход которо подключен к инвертирующему выходу формирователя 4 импульсов, а выход - к первому входу третьей схемы И 9 и входам второго и третьего одновиб- раторов 11 и 12 соответственно, при- чем выход второго одновибратора 11 соединен с вторым входом схемы И 8, а выход третьего одновибратюра 12 соединен с входом Сброс счетчика

18 импульсов времени, счетный вход которого соединен с выходом схемы И 9, второй вход которой соединен с выходом генератора 13 частоты, который соединен с также с входом задат- чика 15 коэффициента деления, выход которого соединен с входом функционального преобразователя 16 1/X и -с вторым входом блока 17 управления сбросом, первый вход которого соединен с выходом делителя 14 числа импульсов, который соединен также с входом Запись регистра 21 памяти и управляющим входом регистратора 22. Выходы счетчика 18 импульсов времени соединены с соответствующими входами первого слагаемого сумматора 19, а с входами второго слагаемого сумматора 19 соединены соответствующие выходы первого регистра 20 памяти, информационные входы которого соединены с соответствующими выходами сумматора, а выходы соединены также с соответствующими информационными входами второго регистра 21 памяти, выходы которого соединены с информационными входами функционального преобразователя 16 1/Х, выход которого соединен с информационным входом регистратора 22. Выход схемы И 8 подключен к входу делителя 14 числа импульсов и к входу Запись регистра 20 памяти, вход Сброс которого подключен к выходу блока 17 управления сбросом.

Устройство (фиг.1) работает следующим образом.

На входы преобразователей 1 и 2 изображения в электрические сигналы поступают случайные оптические сигналы z(t) и z(t+Ј) с транспортным запаздыванием С, которые преобразуют их в электрические сигналы x(t) и x(t+t), подаваемые на входы формирователей 3 и 4. С неинвертирующего выхода формирователя 3 импульсы Х1 поступают на D-вход D-триггера 5, С-вход D-триггера 6 и на первый вход схемы И 7, на третий вход которой поступают импульсы Х2 с инвертирующего выхода формирователя 4, с неинвертирующего выхода которого импульсы Х2 подаются на С-вход D-триггера 5 и на D-вход D-триггера 6. Допустим, что все бистабильные элементы в исходном состоянии на своих прямых (неинверсных) выходах имеют логические О. Тогда с поступлением на

С-вход D-триггера 5 переднего фронта первого импульса последовательности Х2 импульсов (фиг.2) его состояние не изменится, так как на его D-входе (фиг.1) в это время присутствует логический О. С поступлением переднего фронта первого импульса последовательности Х1 (фиг.2) на С-вход D-триггера 6 (фиг.1) послед- ний переключится в единичное состояние, так как на его D-входе в этот момент присутствует логическая 1, которая приложится к второму входу схемы И 7, подготовив ее для прохож- дения импульсов, длительность которых равна f. По переднему фронту каждого импульса последовательности УЗ срабатывает одновибратор 12, который формирует короткий импульс, посту- пающий на вход Сброс счетчика 18 импульсов времени. После установки счетчика 18 в исходное состояние на его счетный вход начнут поступать импульсы времени с выхода генерато- ра 13 частоты через второй вход схемы И 9, на первый вход которой поступает очередной импульс последовательности УЗ. По окончании очередного импульса последовательности УЗ срабатывает одновибратор 11, на выходе которого появляется короткий импульс последовательности У4 (фиг.2) Первый импульс последовательности У4 пройдет на выход схемы И 8, так как к ее первому входу в это время прикладывается логическая 1. Этот импульс, входящий в последовательность У7 импульсов, поступает на вход Запись регистра 20 памяти и на вход делителя 14 числа импульсов. По заднему фронту первого импульса последовательности У4 импульсов в регистр 20 памяти будет произведена запись суммы чисел счетчика 18 и регистра 20 памяти, который находится в исходном состоянии. Отсюда следует, что первое число, записанное с выходов сумматора 19 в регистр 20 памяти, будет соответствовать числу, записанному в счетчик 18 импульсов времени. Если коэффициент деления делителя 14 числа импульсов отличен от единиц,, то исходное состояние регистра 21 памяти не изменится, а при коэффициенте деления, рапном единице, первый ИМПУЛЬС последовательности У7 импульсоп пройдет на выход делителя 14 числа ИМПУЛЬСОВ в проин

JQ15 20 25 30 - д

5

0

5

картированном виде. По заднему фронту этого импульса в регистр 21 памяти будет переписано содержимое регистра 20 памяти и будет подана команда на управляющий вход регистратора 22 на регистрацию измеряемой скорости, равной коэффициенту деления, заданному в виде частоты, поступающей с выхода задатчика 15 коэффициента деления на тактовый вход функционального преобразователя 16 1/Х, деленного на код числа, поступающего на его информационные входы. Одновременно импульс, поступающий с выхода делителя 14 числа импульсов, подается на первый вход блока 17 управления сбросом, запуская его. При этом с выхода задатчика 15 коэффициента деления через второй вход блока 17 управления сбросом на его выход поступают импульсы, число которых необходимо для стирания информации из памяти регистра 20. Для регистров, выполненных например, на микросхемах К155ИР1, необходимо четыре импульса. При поступлении второй пары импульсов последовательности Х1,Х2 на выход схемы И 7 поступит второй импульс последовательности УЗ,длительность которого будет искажена за счет укорочения импульса, вызванного тем, что интервал между задними фронтами второй пары импульсов последовательностей Х1 и Х2 и передними фронтами третьей па.ры импульсов этих же последовательностей меньше времени транспортного запаздывания t1 Тем не менее второй импульс последовательности УЗ будет закодирован и записан в счетчик 18 импульсов времени. Однако операция перезаписи содержимого счетчика 18 в регистр 20 памяти не будет выполнена, так как очередной импульс последовательности У4 на выход схемы И 8 не пройдет в связи с тем, что в момент его возникновения на первом входе схемы И появляется логический О. Это вызвано тем, что передний фронт третьего импульса последовательности Х2 импульсов переключит D-триггер 5 в единичное состояние. При этом на его выходе появится импульс У1, по переднему фронту которого срабатывает первый одновибратор 10, на инвертирующем выходе которого появится логический О, который запирает схему И 8 и одновременно производит

сброс D-триггерл 5 по его R-входу. Следует отметить, что длительность импульса отрицательной полярности на выходе одновибратора 10 должна превышать длительность импульсов, снимаемых с выхода одновибратора 11.Если коэффициент деления делителя 14 числа импульсов равен не единице, а, допустим, двум , то первое число, записанное в регистр 20 памяти, хранится в нем до прохождения третьего импульса последовательности УЗ импульсов. С поступлением этого импульса по его переднему фронту будет произведен сброс счетчика 18 импульсов, после чего код этого импульса будет записан в счетчик 18. По окончании третьего импульса последовательности УЗ по его заднему фронту формируется третий импульс последовательности У4 , который проходит на выход схемы И 8 в проинвертированном виде. По его команде содержимое счетчика 18 импульсов просуммируется с содержимым регистра 20 памяти и запишется в этот же регистр. По окончании второго импульса последовательности У7 импульсов содержимое регистра 20 памяти перепишется в регистр 21 памяти и одновременно на управляющий вход регистратора 22 поступит команда на регистрацию новой информации о скорости. Кроме того, на первый вход блока 17 управления сбросом поступает команда на сброс содержимого регистра 20 памяти. Следует отметить, что коэффициент деления делителя 14 числа импульсов связан с коэффициентом деления задатчика 15 коэффициента деления обратной зависимостью, так что, изменив коэффициент деления делителя 14 числа импульсов с единицы на два, необходимо вдвое уменьшить коэффициент деления задатчика 15 коэффициента деления, в противном случае градуировка регистратора 22 будет нарушена. В процессе измерения целесообразно использовать также временные интервалы равные , ограниченные передними фронтами соответствующих пар импульсов последовательностей Х1 и Х2 импульсов. Однако для этого в схему дополнительно вводится блок, содержащий два D-триггера, три схемы И,три одновнбратора и три схемы ИЛИ,служащие для объединения сигналов, снимаемых с выходов двух идентичных

блоков. Н-а фиг.1 дополнительный блок не показан с целью упрощения описания работы устройства.

Формула изобретения

Устройство для измерения скорости движения, содержащее два преоб0 разователя изображения в электрический сигнал, два регистра памяти, две схемы И, счетчик импульсов времени, функциональный преобразователь, задатчик коэффициента деления, выход которого соединен с одним из входов функционального преобразователя,выход которого соединен с информационным входом регистратора, о т л и- чающееся тем, что, с целью

Q повышения точности измерения, в него введены два формирователя импульсов прямоугольной формы, два D-триггера, три одновибратора, генератор частоты, делитель числа импульсов, блок уп5 равления сбросом, сумматор и третья схема И, а в качестве функционального преобразователя используется управляемый делитель частоты, причем выход первого преобразователя изображения соединен с входом первого формирователя импульсов, выход которого соединен с первым входом первой схемы И, С-входом второго D-триггера и D-входом первого D-триггера,выход которого через первый одновибратор соединен со своим R-входом и первым входом второй схемы И, выход второго преобразователя изображения соединен с входом второго формирователя импульсов, неинвертирующий выход которого соединен с С-входом первого D-триггера, D-входом второго D-триггера, выход которого соединен с вто- рым входом первой схемы И, третий вход которой соединен с инвертирующим выходом второго формирователя импульсов, а выход - с первым входом третьей схемы И и входами второго и третьего одновибраторов, выход второго одновибратора соединен с вторым входом второй схемы И, а ввгход третьего одновибратора соединен с входом Сброс счетчика импульсов времени, счетный вход которого соединен с выходом третьей схемы И,вто5 рой вход которой соединен с выходом генератора частоты, который соединен также и с входом задатчика коэффициента деления, выходы счетчика им0

5

0

5

0

пульсов времени соединены с первыми входами сумматора, а с вторыми входами сумматора соединены соответствующие выходы первого регистра памяти, информационные входы которого соединены с соответствующими выходами сумматора, а выходы соединены также с соответствующими информационными входами второго регистра памяти, вход Запись которого подключен к выходу делитапя числа импульсов, который подключен также к

управляющему входу регистратора и к первому входу блока управления сбросом, второй вход которого подключен к выходу задатчика коэффициента деления, а выход подключен к ВХОДУ Сброс первого регистра памяти, вход Запись которого и тактовый вход делителя числа импульсов соединены с выходом второй схемы И, выход ; второго регистра памяти соединены с информационными входами функционапьного преобразователя.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для обработки и передачи информации учета товарной нефти | 1983 |

|

SU1129625A1 |

| РАДИОИЗОТОПНЫЙ ТОЛЩИНОМЕР ПОКРЫТИЙ | 1990 |

|

SU1729188A1 |

| РАДИОИЗОТОПНЫЙ ТОЛЩИНОМЕР ПОКРЫТИЙ | 1989 |

|

SU1685130A1 |

| Измеритель динамических характеристик | 1987 |

|

SU1532901A1 |

| УСТРОЙСТВО ДЛЯ РАЗЛИЧЕНИЯ ЛИНЕЙНО-ЧАСТОТНО-МОДУЛИРОВАННЫХ СИГНАЛОВ | 1984 |

|

SU1841016A1 |

| Устройство для поворота вектора | 1982 |

|

SU1076910A1 |

| Двухканальное устройство для акустико-эмиссионного контроля | 1988 |

|

SU1508140A1 |

| Устройство для счета предметов | 1986 |

|

SU1387026A1 |

| Частотный детектор | 1982 |

|

SU1137563A1 |

| Устройство для обработки и передачи информации учета товарной нефти | 1987 |

|

SU1413645A1 |

Изобретение относится к области измерительной техники и может быть использовано для бесконтактного измерения скорости движения. Цель - повышение точности измерения. Случайные оптические сигналы с транспортным запаздыванием τ поступают на входы преобразователей 1, 2 изображения в электрические сигналы, которые формируются блоками 3, 4 и поступают на входы Д-триггеров 5,6 и схему И 7. По переднему фронту импульса длительностью τ на выходе схемы И 7 одновибратором 12 формируется импульс сброса в нуль счетчика 18, а по заднему фронту одновибратором 11 - импульс записи содержимого сумматора 19 в регистр памяти 20. Импульс на выходе схемы И 7 открывает ключ 9 и импульсы от генератора 13 поступают на счетный вход счетчика 18, который формирует код, пропорциональный времени транспортного запаздывания между входными сигналами τ. Этот код суммируется с кодом с выхода первого регистра памяти 20 и записывается в этот же регистр. После нескольких циклов измерения, количество которых задается делителем 14, происходит запись содержимого регистра 20 в регистр 21, а затем сброс регистра 20. Функциональный преобразователь преобразует код времени транспортного запаздывания на выходе регистра 21 в частоту, пропорциональную скорости движения, которая поступает на регистратор 22. 2 ил.

| Измеритель скорости движения объекта | 1984 |

|

SU1216733A1 |

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| СПОСОБ ОСАДКИ ЦИЛИНДРИЧЕСКИХ ЗАГОТОВОК | 0 |

|

SU247756A1 |

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

Авторы

Даты

1989-05-07—Публикация

1987-03-02—Подача