залусх

Изобретение относится к радиоизмерительной технике и может быть использовано в быстродействующих измерителях временных характеристик флуктуа- ций амплитуды и фазы сигналов микроволнового диапазона частот, работающих как в непрерывном, так и в импульсном режимах.

Цель изобретения - повышение точ- ности измерителя флуктуации,

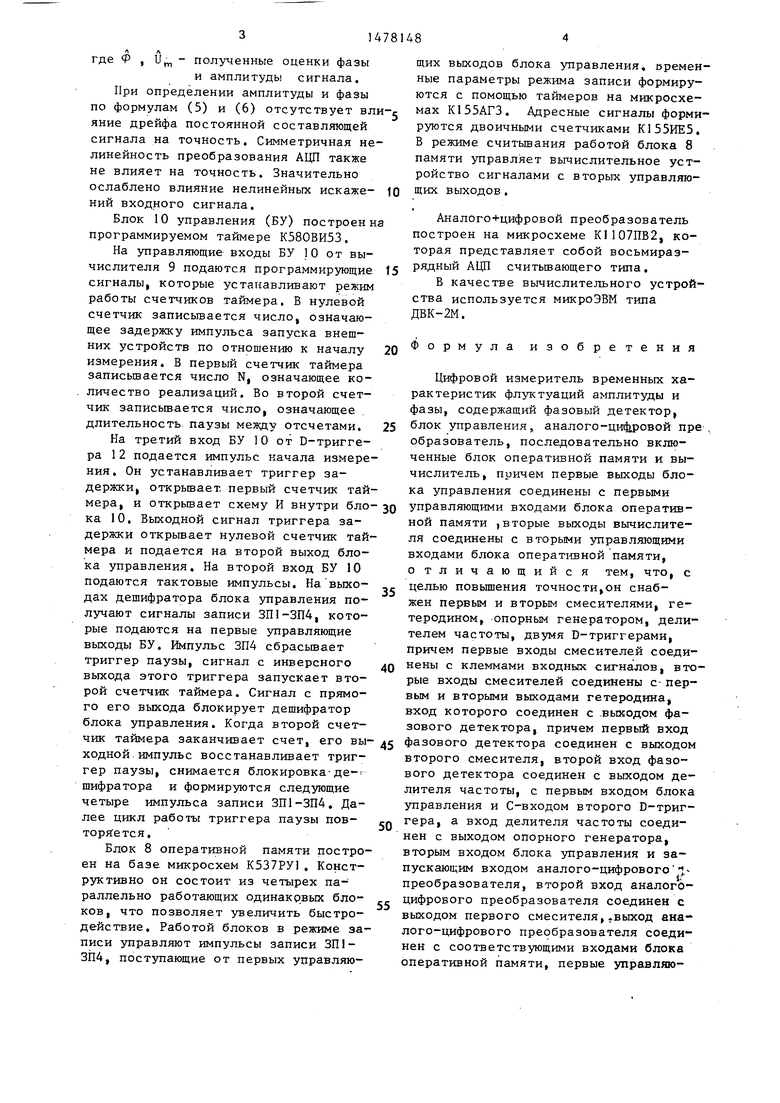

На чертеже приведена структурная схема измерителя.

Измеритель содержит смесители 1

дом D-триггера 11,3 D-триггер 11 соединен с шиной единичного потенциала.

Цифровой измеритель работает следующим образом.

Смесители 1 и 2 преобразовывают высокочастотные колебания на фиксированную частоту Fnp . При этом информация о амплитуде и фазе входных сигналов пропорционально переносится на колебания, выделяемые на выходах первого и второго смесителей. Частота опорного генератора F в четыре раза превышает значение проме

| название | год | авторы | номер документа |

|---|---|---|---|

| РАДИОПЕЛЕНГАТОР | 2012 |

|

RU2505831C2 |

| Устройство измерения частотных характеристик группового времени запаздывания четырехполюсников | 1988 |

|

SU1631511A1 |

| Фазометр | 1985 |

|

SU1298685A1 |

| ДЕМОДУЛЯТОР ШИРОКОГО ИСПОЛЬЗОВАНИЯ | 1993 |

|

RU2128399C1 |

| ФАЗОВЫЙ ПЕЛЕНГАТОР | 2011 |

|

RU2458355C1 |

| СПОСОБ ОБНАРУЖЕНИЯ ЖИВЫХ ОБЪЕКТОВ И УСТРОЙСТВО ДЛЯ ЕГО ОСУЩЕСТВЛЕНИЯ | 2010 |

|

RU2442186C1 |

| СПОСОБ И УСТРОЙСТВО ДЛЯ ИЗМЕРЕНИЯ ЗАЗОРОВ (ВАРИАНТЫ) | 2006 |

|

RU2307999C1 |

| Измеритель параметров импульсов | 1984 |

|

SU1164631A1 |

| АДАПТИВНЫЙ ЛАЗЕРНЫЙ ДОПЛЕРОВСКИЙ ЛОКАТОР | 1990 |

|

RU2012013C1 |

| УСТРОЙСТВО ДЛЯ РАСПОЗНАВАНИЯ ВИДОВ МАНИПУЛЯЦИИ ЦИФРОВЫХ СИГНАЛОВ | 2005 |

|

RU2309414C2 |

Изобретение относится к области радиоизмерительной техники и может быть использовано в быстродействующих измерителях временных характеристик флуктуаций амплитуды и фазы сигналов микроволнового диапазона частот. Целью изобретения является точность и расширение функциональных возможностей. Поставленная цель достигается тем, что в цифровой измеритель временных характеристик флуктуаций амплитуды и фазы, содержащий фазовый детектор 4, блок управления 10, аналого-цифровой преобразователь 7, блок памяти 8 и вычислитель 9, дополнительно введены смеситель 1, гетеродин 3, смеситель 2, опорный генератор 6 и два триггера 11 и 12. Точность измерения увеличена за счет использования импульсно-фазовой автоподстройки частоты с дополнительным делителем частоты для получения моментов двукратной квадратуры. 1 ил.

и 2, гетеродин 3, фазовый детектор 4, 15 жуточной частоты (Fnp), так как на

делитель 5 частоты, опорный генератор 6, аналого-цифровый преобразователь 7, блок 8 оперативной памяти, вычислитель 9, блок 10 управления, первый и второй D-триггеры 11 и 12. 20

Первый вход смесителя 1 соединен с клеммой измеряемого входного сигнала, первый вход смесителя 2 соединен с клеммой опорного входного сигнала. Вторые входы смесителей 1 и 2 соеди- нены с выходами гетеродина 3. Вход гетеродина 3 соединен с выходом фазового детектора 4. Выход опорного генератора 6 соединен с запускающим ° входом аналого-цифрового преобразо- 30 вателя 7, вторым входом блока 10 управления и входом делителя 5 частоты, выход которого соединен с вторым входом фазового детектора 4, первым входом блока 10 управления и с С-входом 35 D-триггера 12, Второй вход аналого- цифрового преобразователя 7 соединен с выходом смесителя 1 измерительного канала. Выход аналого-цифрового преобразователя 7 соединен с информаци- 40 онными входами блока 8 оперативной памяти, выходы которого соединены с информационными входами вычислителя 9. Вторые выходы вычислителя 9 соединены с вторыми управляющими входами 45 блока 8 оперативной памяти, а первые управляющие выходы вычислителя 9 соединены с управляющими входами блока 10 управления. Первые управляющие входы блока 8 оперативной памяти сое-,/ч динены с управляющими выходами блока 10 управления. Сигнал с первого выхода блока 10 управления подан на R-входы D-триггеров 11 и 12. Прямой выход D-триггера 11 подключен к

D-входу D-триггера 12, выход которого соединен с третьим входом блока 10 управления, клемма сигнала внешнего запуска соединена с С-вхофазовый детектор 4 подается сигнал частотой (Fon/4) Fn(s . Триггеры 1 1 и 12 обеспечивают синхронизацию на чала каждой реализации с сигналом опорного генератора, независимо от момента подачи внешнего импульса з пуска Таким образом, обеспечивает возможность усреднения нескольких реализаций. Запуск преобразователя аналог-код (АЦП) происходит с перио дом Т, ТПр/4, поэтому за один пер од колебания Fn получают четыре оце ки значения его мгновенного напряже ния соответственно

11, U0 + Umsin(P);

иг U0 +Umsin(P + /2)

U0 +Umcos(P);

U, U0 + Uwsin(m)

(1)

(2) (3) (4)

U0 -u sinCP );

U«. U0 + Umsin(P-t-37-/2)

U0 - и собСФ ),

где и,и - мгновенные значения сиг нала;

UM -- амплитуда сигнала;

UQ - постоянная составляющая входного сигнала;

Ф - фаза сигнала.

I.

Блок 10 управления через заданны интервалы времени Тг выдает в блок четыре импульса записи, которые фик сируют в памяти выходные коды АЦП U и я. Ц U4. Зафиксированная в блок реализация содержит данные о флукту циях амплитуды и фазы сигнала.

Вычислитель 9 определяет оценки амплитуды и фазы сигнала по считанным из блока 8 оценкам мгновенных значений Щ-и.. При этом использую ся следующие алгоритмы вычисления

Р ATAN((U4- U,)/(Ug-U4)). (5

V o.s-Jaj,- и,)г+ (W (6

жуточной частоты (Fnp), так как на

фазовый детектор 4 подается сигнал с частотой (Fon/4) Fn(s . Триггеры 1 1 и 12 обеспечивают синхронизацию начала каждой реализации с сигналом опорного генератора, независимо от момента подачи внешнего импульса запуска Таким образом, обеспечивается возможность усреднения нескольких реализаций. Запуск преобразователя 7 аналог-код (АЦП) происходит с периодом Т, ТПр/4, поэтому за один период колебания Fn получают четыре оценки значения его мгновенного напряжения соответственно

11, U0 + Umsin(P);

иг U0 +Umsin(P + /2)

U0 +Umcos(P);

U, U0 + Uwsin(m)

(1)

(2) (3) (4)

U0 -u sinCP );

U«. U0 + Umsin(P-t-37-/2)

U0 - и собСФ ),

где и,и - мгновенные значения сигнала;

UM -- амплитуда сигнала;

UQ - постоянная составляющая входного сигнала;

Ф - фаза сигнала.

I.

Блок 10 управления через заданные интервалы времени Тг выдает в блок 8 четыре импульса записи, которые фиксируют в памяти выходные коды АЦП U, и я. Ц U4. Зафиксированная в блок 8 реализация содержит данные о флуктуа циях амплитуды и фазы сигнала.

Вычислитель 9 определяет оценки амплитуды и фазы сигнала по считанным из блока 8 оценкам мгновенных значений Щ-и.. При этом используются следующие алгоритмы вычисления .

Р ATAN((U4- U,)/(Ug-U4)). (5)

V o.s-Jaj,- и,)г+ (W (6)

где Ф , Um - полученные оценки фазы и амплитуды сигнала.

При определении амплитуды и фазы по формулам (5) и (6) отсутствует вл яние дрейфа постоянной составляющей сигнала на точность. Симметричная нелинейность преобразования АЦП также не влияет на точность. Значительно ослаблено влияние нелинейных искаже- ний входного сигнала.

Блок 10 управления (БУ) построен н программируемом таймере К580ВИ53.

На управляющие входы БУ 10 от вычислителя 9 подаются программирующие сигналы, которые устанавливают режим работы счетчиков таймера. В нулевой счетчик записывается число, означающее задержку импульса запуска внешних устройств по отношению к началу измерения. В первый счетчик таймера записывается число N, означающее количество реализаций. Во второй счетчик записывается число, означающее длительность паузы между отсчетами.

На третий вход БУ 10 от D-тригге- ра 12 подается импульс начала измерения. Он устанавливает триггер задержки, открывает первый счетчик тай

мера, и открывает схему И внутри бло- JQ управляющими входами блока оператив35

40

ка 10. Выходной сигнал триггера задержки открывает нулевой счетчик таймера и подается на второй выход блока управления. На второй вход БУ 10 подаются тактовые импульсы. На выходах дешифратора блока управления получают сигналы записи ЗП1-ЗП4, которые подаются на первые управляющие выходы БУ. Импульс ЗП4 сбрасывает триггер паузы, сигнал с инверсного выхода этого триггера запускает второй счетчик таймера. Сигнал с прямого его выхода блокирует дешифратор блока управления. Когда второй счетчик таймера заканчивает счет, его вы- 45 ходной импульс восстанавливает триггер паузы, снимается блокировка-де-- шифратора и формируются следующие четыре импульса записи ЗП1-ЗП4. Далее цикл работы триггера паузы повторяется.

Блок 8 оперативной памяти построен на базе микросхем К537РУ1. Конструктивно он состоит из четырех параллельно работающих одинаковых блоков, что позволяет увеличить быстродействие. Работой блоков в режиме записи управляют импульсы записи ЗП1- ЗП4, поступающие от первых управляю50

55

ной памяти ,вторые выходы вычислителя соединены с вторыми управляющими входами блока оперативной памяти, отличающийся тем, что, с целью повышения точности,он снабжен первым и вторым смесителями, гетеродином, опорным генератором, делителем частоты, двумя D-триггерами, причем первые входы смесителей соединены с клеммами входных сигналов, вто рые входы смесителей соединены с- первым и вторыми выходами гетеродина, вход которого соединен с выходом фазового детектора, причем первый вход фазового детектора соединен с выходом второго смесителя, второй вход фазового детектора соединен с выходом делителя частоты, с первым входом блока управления и С-входом второго D-тригге ра, а вход делителя частоты соединен с выходом опорного генератора, вторым входом блока управления и запускающим входом аналого-цифрового 1- преобразователя, второй вход аналого- цифрового преобразователя соединен с выходом первого смесителя,.выход аналого-цифрового преобразователя соединен с соответствующими входами блока оперативной памяти, первые управляюс

5

0

5

щих выходов блока управления, временные параметры режима записи формируются с помощью таймеров на микросхемах К155АГЗ. Адресные сигналы формируются двоичными счетчиками К155ИЕ5. В режиме считывания работой блока 8 памяти управляет вычислительное устройство сигналами с вторых управляющих выходов.

Аналого+цифровой преобразователь построен на микросхеме К1107ПВ2, которая представляет собой восьмиразрядный АЦП считывающего типа.

В качестве вычислительного устройства используется микроэвм типа ДВК-2М.

Формула изобретения

Цифровой измеритель временных характеристик флуктуации амплитуды и фазы, содержащий фазовый детектор, блок управления, аналого-цифровой пре образователь, последовательно включенные блок оперативной памяти и вычислитель, причем первые выходы блока управления соединены с первыми

35

40

45

0

5

ной памяти ,вторые выходы вычислителя соединены с вторыми управляющими входами блока оперативной памяти, отличающийся тем, что, с целью повышения точности,он снабжен первым и вторым смесителями, гетеродином, опорным генератором, делителем частоты, двумя D-триггерами, причем первые входы смесителей соединены с клеммами входных сигналов, вторые входы смесителей соединены с- первым и вторыми выходами гетеродина, вход которого соединен с выходом фазового детектора, причем первый вход фазового детектора соединен с выходом второго смесителя, второй вход фазового детектора соединен с выходом делителя частоты, с первым входом блока управления и С-входом второго D-тригге ра, а вход делителя частоты соединен с выходом опорного генератора, вторым входом блока управления и запускающим входом аналого-цифрового 1- преобразователя, второй вход аналого- цифрового преобразователя соединен с выходом первого смесителя,.выход аналого-цифрового преобразователя соединен с соответствующими входами блока оперативной памяти, первые управляю514781486

щие выходы вычислителя соединены сго D-триггера, выход которого подклюуправлякяцими входами блока управле-чен к третьему входу блока управления,

ния, причем первый выход блока управ-причем С-вход первого D-триггера подления подключен к R-входам первого иключей к клемме внешнего запуска,

второго D-триггеров, выход первогоD-вход первого D-триггера соединен с

D-триггера соединен с D-входом второ-шиной единичного потенциала.

| Головченко В.Г., Гойжевский В.А | |||

| Обзор методов смещения частоты | |||

| Современные методы и аппаратура для измерения параметров радиоцепей | |||

| - Доклады всесоюзного симпозиума | |||

| - Новосибирск, 1974, с.116-118 | |||

| Лесняк В.Н | |||

| Быстродействующий цифровой вычислитель фазы | |||

| Труды радиотехнического института АН СССР | |||

| Шеститрубный элемент пароперегревателя в жаровых трубках | 1918 |

|

SU1977A1 |

| Цифровой измеритель характеристик фазовых флуктуаций | 1981 |

|

SU993148A1 |

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Федорков Б.Г., Телец В.А., Дегтяренко В.П | |||

| Микроэлектронные циф- роаналоговые и аналого-цифровые преобразователи | |||

| - М.: Радио и связь, 1984, с.81. | |||

Авторы

Даты

1989-05-07—Публикация

1987-06-10—Подача