Настоящее изобретение касается в основном радиоприемников и демодуляторов с использованием цифровой обработки данных символа, представляющего аналоговые сигналы и, в частности, таких устройств, которые содержат по меньшей мере один из перечисленных ниже элементов: /a/ относительно недорогой аналого-цифровой преобразователь для квантования сигнала с частотой, равной частоте следования символа, /b/ узел обратной перестановки, работающий по принципу цифрового вычислителя поворота систем координат (CORDIC), и /c/ цифровой узел обратной перестановки для получения цифрового сигнала, представляющего коррекцию частоты и фазы входного сигнала демодулятора в комбинации с цифровым фазовращателем, служащим для управления квантованием входного сигнала в аналого-цифровом преобразователе.

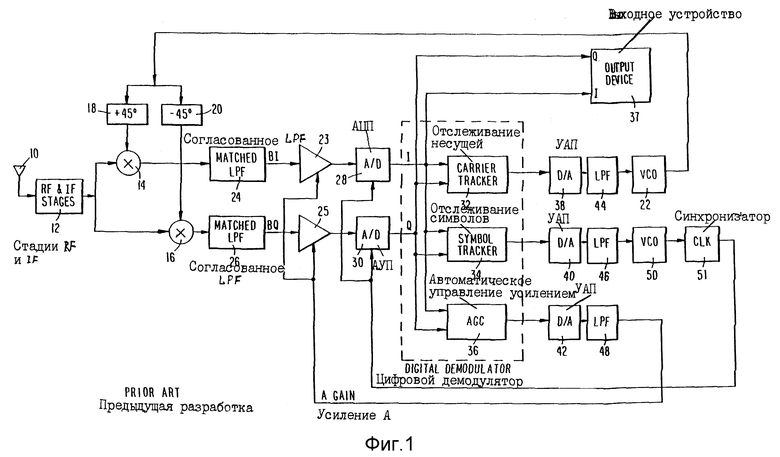

На фиг. 1 представлена блок-схема радиоприемника с фазовой подстройкой, использующая цифровую обработку данных. Приемник выделяет из фона подавленную несущую с квадратурной манипуляцией фазомодулированной электромагнитной волны, падающей на антенну 10. Эта волна, падающая на антенну 10, преобразуется в электрический сигнал, который поступает на каскады 12 усиления радио- и промежуточных частот. Волна имеет строго контролируемую частоту несущей, установленную для передатчика электромагнитных сигналов с квадратурной манипуляцией фазовым сдвигом, и включает в себя символы, имеющие заранее установленную скорость, например частоту, в частности, 20 Гц.

Выходной сигнал с каскадов 12 усиления подается одновременно на смесители 14 и 16, на которые соответственно подаются взаимно перпендикулярные волновые сигналы, подученные ±45o фазовращателями 18 и 20. Фазовращатели 18 и 20, в свою очередь, подключены к управляемому напряжением гетеродину 22 регулируемой частоты, выходная частота которого приблизительно равна частоте подавленной несущей на выходе каскадов 12. Выходные сигналы смесителей 18 и 20 подаются соответственно на согласованные (по отношению к форме сигнала передатчика) фильтры 24 и 26 низких частот (ФНЧ), формирующие переменные аналоговые модулирующие сигналы, представляющие символы, которые должны быть обработаны в информацию, представляющую выходные сигналы. Модулирующие выходные сигналы фильтров 24 и 26 обычно обозначают как канальные сигналы I и Q.

Канальные сигналы I и Q, сформированные фильтрами 24 и 26, подаются соответственно через усилители 23 и 25 с переменным усилением на АЦП 28 и 30, служащие для квантования амплитуд модулирующего сигнала I и Q на другой частоте, обычно равной приблизительно двойной частоте следования символа. Обычно коэффициенты усиления усилителей 23 и 25 регулируют для того, чтобы максимальная амплитуда аналоговых сигналов, подаваемых на преобразователи 28 и 30, находилась в оптимальном диапазоне работы последних.

В обычных режимах работы преобразователи 28 и 30 квантуют канальные сигналы I и Q, подаваемые на них, со скоростью, равной скорости следования сигнала приблизительно в центре промежутка между соседними символами. Преобразователи 28 и 30 формируют на выходе многоразрядные цифровые сигналы, представляющие величину и полярность каждой выборки, поступающей на преобразователи. Преобразователи 28 и 30, представленные отдельными интегральными микросхемами, являются довольно дорогостоящими, поскольку они должны квантовать модулирующие аналоговые канальные сигналы I и Q на частоте, приблизительно равной 40 Гц.

Цифровые сигналы I и Q на выходе преобразователей 28 и 30 подаются одновременно на систему 32 слежения за несущей, систему 34 слежения за символом и систему 36 слежения за амплитудой, каждая из которых представляет собой цифровую схему, сформированную на обычной однокристальной интегральной микросхеме. Система 32 слежения за несущей вырабатывает цифровой сигнал, несущий информацию о полярности и частоте, а также о фазовых сдвигах между выходным сигналом гетеродина 22 и сигналом подавленной несущей на выходе каскадов 12. Система 34 слежения за символом вырабатывает сигнал, несущий информацию о полярности и величине ошибки во временах квантования преобразователей 28 и 30 по отношению к установленным значениям таких времен квантования. Система 36 слежения за амплитудой сравнивает значения амплитуд выходных сигналов I и Q с опорной и оптимизирует их значения путем посылки сигнала управления на соответствующее регулирование коэффициентами усиления усилителей 23 и 25. Выходные сигналы I и Q преобразователей 28 и 30 подаются также в выходную схему 37 обработки данных. Как правило, цифровые сигналы имеют от 8 до 10 бит, в особенности для того, чтобы обеспечить требуемое разрешение для управления усилителями 23 и 25.

Цифровые сигналы, полученные на выходах систем 32, 34 и 36 слежения, подаются соответственно на цифроаналоговые преобразователи 38, 40 и 42, выходные аналоговые сигналы которых, в свою очередь, подаются на соответствующие низкочастотные фильтры 44, 46 и 48. исходной сигнал фильтра 44 управляет частотой и фазой гетеродина 22, подстраивая их к частоте и фазе сигнала подавленной несущей на выходе каскадов 12. Выходной сигнал фильтра 46 подается на управляемый напряжением перестраиваемый генератор, выходной сигнал с которого управляет фазой синхроимпульсов, полученных источником 51 синхроимпульсов. Синхроимпульсы источника 51 подаются одновременно на входы синхронизации аналого-цифровых преобразователей 28 и 30 для обеспечения управления работой этих преобразователей при квантовании аналоговых сигналов, поступающих на их входы. Синхроимпульсы, поступающие на входы синхронизации преобразователей 28 и 30, имеют частоту, приблизительно равную двойной частоте следования символов, подаваемых на преобразователи. Выходной сигнал низкочастотного фильтра 48 подается одновременно на входы управления усилением усилителей 28 и 25.

Несмотря на высокие показатели работы устройства, показанного на фиг. 1, следует отметить, что это устройство является довольно дорогостоящим для широкого использования, так как в процессе его изготовления потребуются, возможно, миллионы отдельных элементов, а наличие элементов, за которые следует заплатить даже нескольких центов, существенным образом влияет на общую стоимость. Основной причиной дороговизны устройства, показанного на фиг. 1, является необходимость двух квантований каждого символа, осуществляемых АЦП 28 и 30. Стоимость АЦП и соответствующих цифровых схем обработки существенно возрастает с увеличением скорости их работы. Необходимость трех ЦАП и связанных с ними ФНЧ также заметно увеличивает стоимость описанного устройства. И, наконец, преобразователь 46 для качественного управления усилителями 23 и 25 должен вырабатывать сигнал, имеющий по меньшей мере восемь бит.

Таким образом, целью настоящего изобретения является создание нового, усовершенствованного и относительно недорогого приемника и демодулятора для сигналов, модулированных символами, с цифровой обработкой данных.

Другой целью изобретения является создание нового и усовершенствованного приемника и демодулятора для сигналов, модулированных символами с цифровой обработкой данных, в которых на каждый символ произведено только одно квантование аналогового сигнала.

Дополнительной целью данного изобретения является создание нового и усовершенствованного приемника и демодулятора сигналов, модулированных символами, с цифровой обработкой данных, использующих только цифровую обработку данных для управления слежением за несущей и символом.

Кроме того, целью данного изобретения является создание нового и усовершенствованного приемника и демодулятора сигналов, модулированных символами, с цифровой обработкой данных, в которых для приемника использована цифровая схема источника номинально фиксированной частоты, служащая для коррекции выходного сигнала АЦП в соответствии с погрешностями частоты и фазы между действительной частотой источника и несущей модулированного сигнала.

И еще одной целью изобретения является создание нового и усовершенствованного приемника и демодулятора сигналов, модулированных символами, с цифровой обработкой данных, в которых для приемника использована схема цифровой обработки данных, а относительно недорогостоящий ЦАП использован для регулирования амплитудой модулирующих аналоговых сигналов, подаваемых на схему АЦП.

В соответствии с одним из аспектов настоящего изобретения предлагается демодулятор, принимающий символы в аналоговом модулирующем сигнале, и содержащий относительно недорогостоящий АЦП, осуществляющий квантование поступающего на него сигнала со скоростью, равной скорости следования символа. Для уменьшения стоимости АЦП не производит квантование со скоростью, равной двойной или выше скорости символа. Скорость квантования и скорость символа, а также тип АЦП выбраны такими, что стоимость сходного АЦП с возможностью квантования сигнала со скоростью, вдвое превышающей скорость символа по меньшей мере на 30%, превышает стоимость патентуемого АЦП. Увеличение стоимости на 30% является весьма определяющим фактором в случае широкого использования подобных устройств.

В одном из конкретных примеров осуществления данного изобретения, предполагающем использование скорости, равной 20 мегасимволов в секунду, стоимость АЦП, осуществляющего квантование со скоростью 20 миллионов раз в секунду, но без возможности квантования 40 миллионов раз в секунду, составляла 20% стоимости аналогичного АЦП, имеющего возможность квантования со скоростью 40 миллионов раз в секунду, при этом аналогичными преобразователями считаются такие, которые имеют одинаковые характеристики /например, разрешение и диапазон амплитуд входного сигнала/, за исключением скорости квантования. Следовательно, экономия стоимости АЦП на интегральной микросхеме, составляющая 80%, достигается квантованием со скоростью, равной скорости следования символа по сравнению с двойной скоростью квантования по отношению к скорости следования символа, что является характерным для известных коммерческих приемников.

Хотя в предшествующем уровне техники и известны преобразователи, имеющие скорость квантования, равную скорости следования символа, однако они имеют ряд недостатков, которые не позволили расширить их применение, например, при цифровом телевизионном приеме с квадратурной фазовой манипуляцией. В работе: Mueller et al IEEE Transactions on Communications, Vol. COM-24 pp. 516-531, May 1976 описан цифровой способ восстановления синхронизации символ-скорость для импульсных амплитудно-модулированных систем, в которых сложно оценить погрешность синхронизации.

Произведенная оценка определяет время прибытия каждого символа с довольно большой степенью погрешности. В другой работе Jennings et al., IEEE Transactions on Communications, Vol. COM-33, pp. 729-731, July 1985 описана система, которая обеспечивает информацию о синхронизации для одного квантования на символе, произведенного АЦП только после того, как были получены определенные последовательности данных.

В соответствии с другим аспектом изобретения демодулятор или приемник, принимающий символы аналогового сигнала и имеющий элементы вычитания для учета частотных и фазовых погрешностей между несущей, на которой промодулирован сигнал, и сигналом частотного гетеродина, содержит средство обработки аналогового сигнала, предназначенное для получения первых цифровых канальных сигналов I и Q, величины которых определяются амплитудами квантованного аналогового сигнала, включая остаточные составляющие. Средство, предназначенное для получения первых цифровых канальных сигналов I и Q, служит для получения вторых цифровых канальных сигналов I и Q, скорректированных с учетом частотной и фазовой погрешностей, а также третьего цифрового сигнала, несущего информацию о частотной и фазовой погрешностях. Вторые цифровые канальные сигналы I и Q получены комбинацией первых цифровых канальных сигналов I и Q и третьего цифрового сигнала по функции достаточно широко описанной, например, в работе Volder, IRE Transactions on Electronic Computers, pp. 330-334, September 1959.

Довольно простым путем получения вторых цифровых канальных сигналов I и Q, широко используемым для известных демодуляторов, является применение ПЗУ с табличным поиском для получения сигналов, представляющих Sin и Cos угла, указывающие частотную и фазовую погрешности. Для получения вторых цифровых сигналов I и Q величины, полученные из ПЗУ, складываются с величинами первых цифровых сигналов по двум уравнениям. Однако для такого решения, известного из предшествующего уровня техники, потребуется огромное количество полупроводниковых устройств. Использование функций CORDIC вместо табличного поиска позволяет решать уравнения, сэкономив приблизительно 50% общего количества логических элементов. Для уменьшения общей стоимости целесообразно обработку информации с использованием функции CORDIC и квантование амплитуды аналогового сигнала со скоростью, приблизительно равной скорости символа, осуществлять в одном приборе.

Демодулятор предпочтительно использовать в приемнике, содержащем /1/ частотный гетеродин, выходной сигнал с которого имеет номинальную частоту и чувствителен к отклонению от установленной величины, и /2/ средство для сложения входного сигнала, включающего символы, модулированные на частоте несущей и выходного сигнала гетеродина. Цифровые канальные сигналы I и Q имеют величины, определяемые модуляцией, а также частотами и фазами несущей и выходного сигнала гетеродина. Величины вторых канальных сигналов I и Q скомпенсированы величиной третьего цифрового сигнала. Регулируемый цифровой фазовращатель имеет первый и второй входы, предназначенные соответственно для по меньшей мере одного из цифровых сигналов и для синхроимпульсов, имеющих приблизительно целое кратное /включая один/ скорости символа для регулирования временами квантования, осуществляемого аналого-цифровым преобразователем с приблизительно такой же скоростью, что и скорость символа так, чтобы при изменении первого входного сигнала фазовращателя менялись времена квантования.

Этот путь цифрового решения регулирования временем квантования и компенсации частотной и фазовой погрешностей в сочетании с выбором одного квантования на символ устраняет необходимость использования цифроаналоговых преобразователей и сверхнизкочастотных фильтров и в то же самое время позволяет применять недорогие аналого-цифровые преобразователи. Дополнительная экономия средств обеспечивается за счет использования функции CORDIC и относительно недорогого одноразрядного сигма-дельта- модулятора, служащего для получения сигнала управления коэффициентом усиления усилителей, осуществляющего регулирование амплитуды аналогового сигнала, подаваемого на АЦП.

В предпочтительном варианте осуществления изобретения первый входной сигнал цифрового фазовращателя служит для сравнения обозначений функций величин по меньшей мере одного из цифровых сигналов для различных квантований /выборок/ (k) и (k-1), осуществляемых преобразователем. Первый входной сигнал получают как функцию

(sign Pk)Pk-1 + (-sign Pk-1)Pk

где Pk является указанием выборки, произведенной преобразователем для символа k,

Pk-1 - указание выборки, произведенной преобразователем для символа (k-1).

Управление первым входным сигналом предпочтительно осуществляют по изменениям одного или двух вторых цифровых сигналов.

Согласно еще одному важному аспекту данного изобретения приемник для модулированного входного сигнала на частоте ωi несущей содержит гетеродин с частотой ω0 , номинально равной ωi. Реакцией на входной сигнал и выходной сигнал гетеродина является появление модулирующих аналоговых канальных сигналов I и Q; модулирующие аналоговые канальные сигналы I и Q включают остаточные составляющие, обусловленные частотной и фазовой погрешностями между частотами и фазами несущей и выходного сигнала гетеродина. Первый и второй аналого-цифровые преобразователи соответственно квантуют модулирующие аналоговые канальные сигналы I и Q со скоростью символа для получения первых цифровых канальных сигналов I и Q, величины которых определяются величинами квантованных аналоговых сигналов I и Q. Узел обратного перемещения, на который поступают первые цифровые канальные сигналы I и Q, служит для получения вторых цифровых канальных сигналов I и Q, скорректированных с учетом частотной и фазовой погрешностей. Управление работой АЦП при квантовании модулирующих канальных сигналов I и Q осуществляется по меньшей мере по одному из цифровых канальных сигналов I и Q. Выходное устройство, на которое подаются вторые цифровые канальные сигналы I и Q, служит для получения информации о том, как должна быть промодулирована несущая.

В предпочтительном варианте выполнения узел обратного перемещения включает средство обратной связи, на которое поступают вторые цифровые канальные сигналы I и Q и которое служит для получения дополнительного цифрового сигнала, несущего информацию о частотной и фазовой погрешностях.

По первым цифровым канальным сигналам I и Q и дополнительному цифровому сигналу узел обратного перемещения осуществляет управление вторыми цифровыми канальными сигналами I и Q. Дополнительный цифровой сигнал получают непосредственно за счет обратной связи с тем, чтобы осуществлять управление получением вторых цифровых канальных сигналов I и Q без преобразования в аналоговый сигнал.

Указанные, а также иные цели, особенности и преимущества данного изобретения станут понятны из приведенного ниже подробного описания конкретных примеров его осуществления со ссылками на сопровождающие чертежи.

Фиг. 1 представляет, как было указано выше, блок-схему приемника с фазовой модуляцией и демодулятора, использующих цифровую обработку данных;

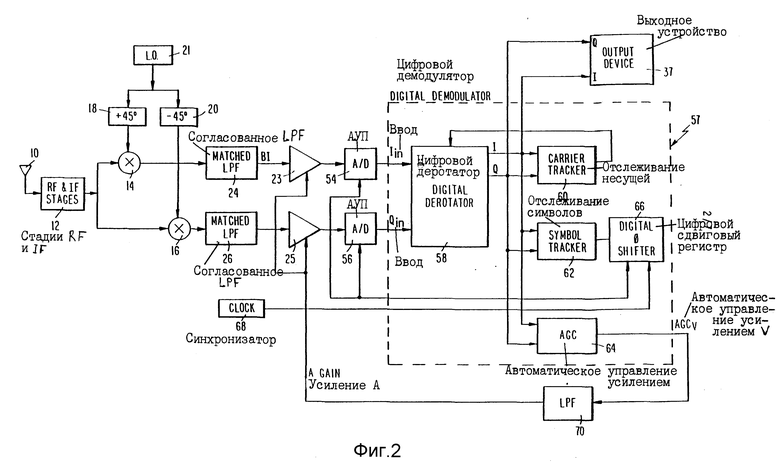

фиг. 2 - блок-схему предпочтительного примера выполнения приемника и демодулятора с цифровой обработкой данных согласно изобретению;

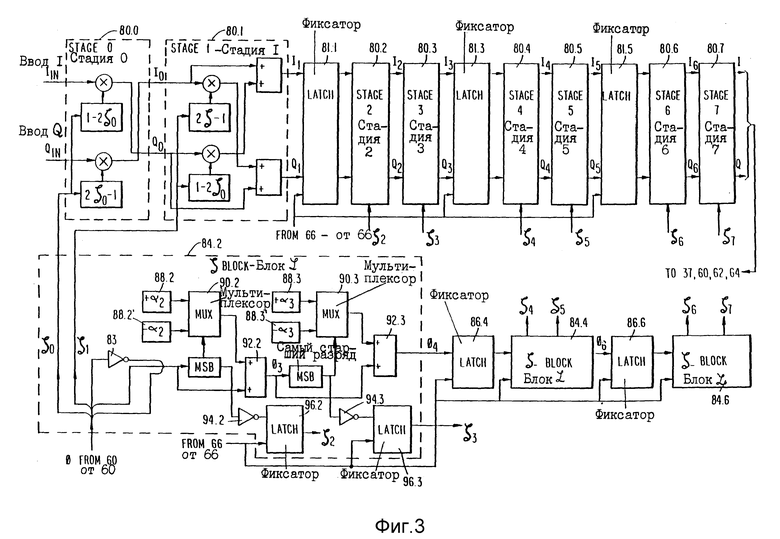

фиг. 3 - блок-схему узла обратного перемещения, показанного на фиг. 2;

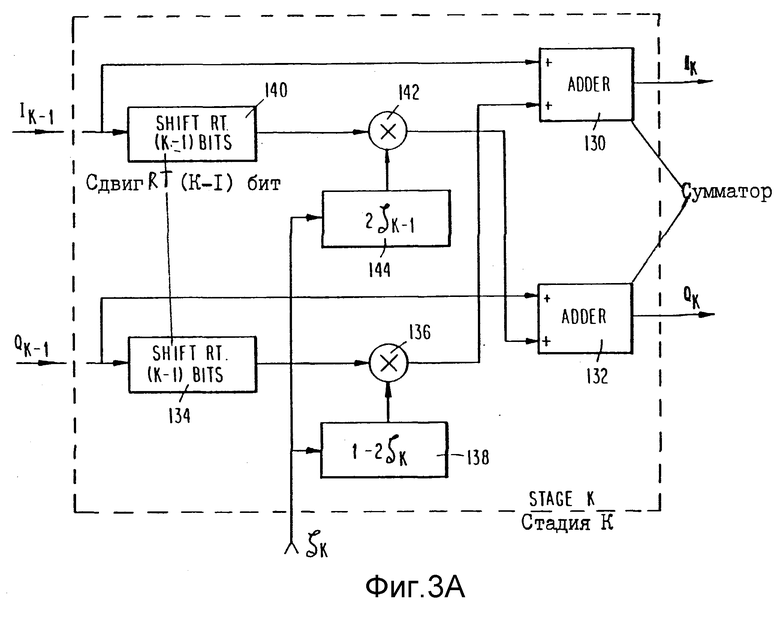

фиг. 3A - блок-схему одного каскада означенного узла на фиг. 3;

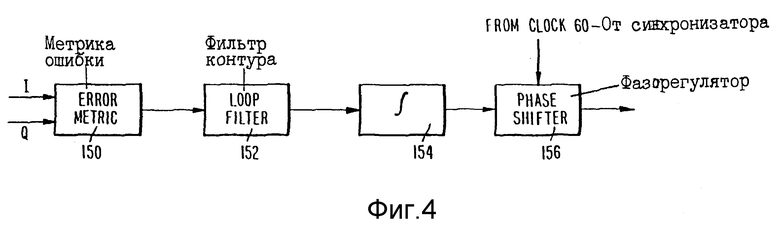

фиг. 4 - блок-схему системы слежения за символом, показанную на фиг. 2;

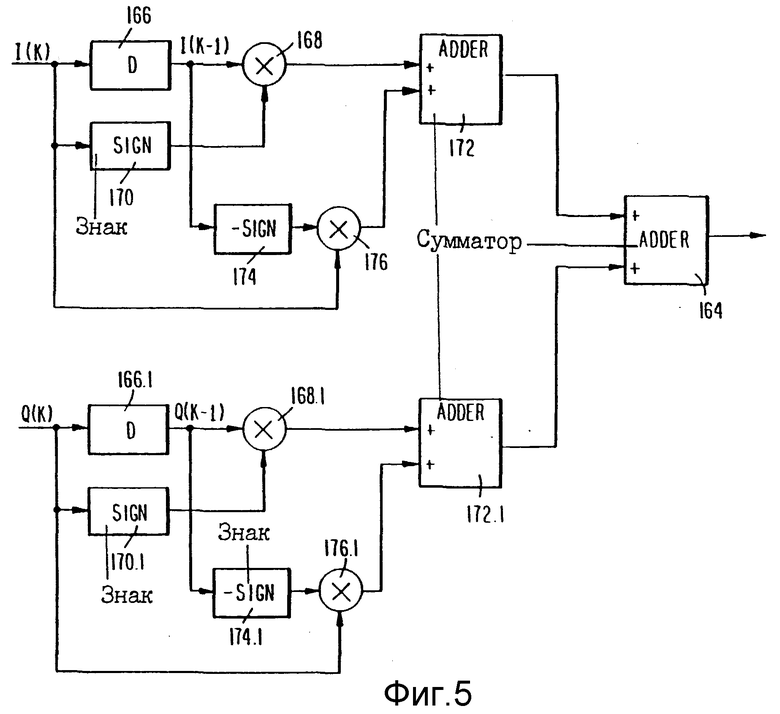

фиг. 5 - блок-схему измерительного вычислителя погрешности;

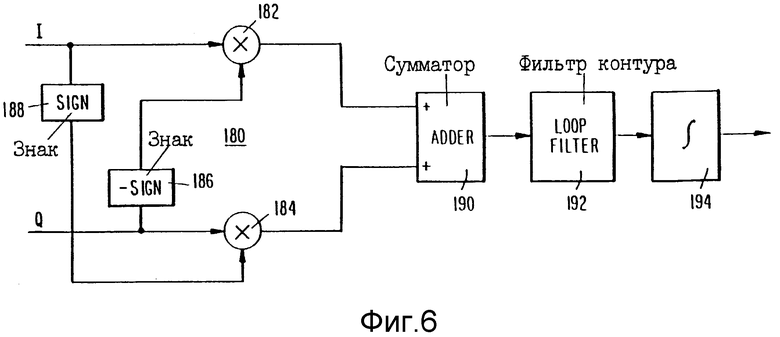

фиг. 6 - блок-схему системы слежения за несущей, показанной на фиг. 2;

фиг. 7 - блок-схему системы слежения за амплитудой, показанной на фиг. 2;

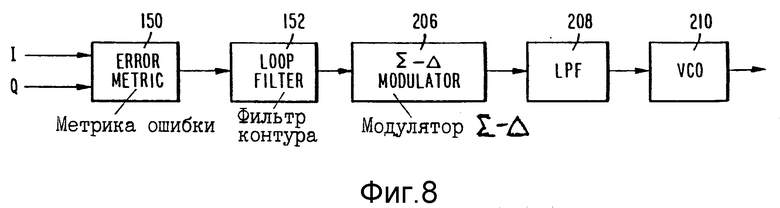

фиг. 8 - блок-схему другого варианта выполнения системы слежения за символом, показанной на фиг. 2.

Как показано на фиг. 2, входная часть приемника и демодулятора в предпочтительном варианте выполнения по существу используется такая же, что и в известном приемнике, представленном на фиг.1, а именно она содержит антенну 10, каскады 12 усиления радио- и промежуточных частот, смесители 14, +45o и -45o фазовращатели 16, согласованные ФНЧ 24 и 26 и усилители 23 и 25 с регулируемым коэффициентом усиления. Управляемый напряжением генератор 22 с регулируемой частотой заменен гетеродином 21, выходная частота которого номинально равна фиксированной частоте выходного сигнала каскадов 12, при этом у гетеродина 21 отсутствует управляемый вход. Поскольку приемник и демодулятор, показанный на фиг. 2, рассчитан на широкого потребителя, частота гетеродина не имеет четко установленного значения и при использовании имеет широкий диапазон регулирования и, кроме того, в зависимости от допусков производства этот диапазон меняется для каждого отдельного прибора.

Модулирующие аналоговые выходные канальные сигналы I и Q согласованных фильтров 24 и 26 подаются на АЦП 54 и 56 соответственно. Преобразователи 54 и 56 квантуют выходные сигналы только раз в течение каждого символа аналоговых сигналов I и Q с квадратурной манипуляцией сдвига фазы, полученных на выходах согласованных фильтров 24 и 26. С целью минимизации стоимости преобразователи 54 и 56 не имеют возможности осуществлять квантование подаваемых на них сигналов дважды на символ, как это требовалось для преобразователей 28 и 30 предшествующего уровня техники.

Следовательно, стоимость преобразователей 54 и 56, а также цифровой схемы обработки данных значительно ниже стоимости преобразователей 28 и 30 и соответствующей им цифровой схемы обработки данных. Для модулирующих символов I и Q, показанных на фиг. 2, требуется квантование со скоростью, равной скорости следования символа благодаря введению особой системы слежения за символом, которая будет описана ниже.

В одном из предпочтительных вариантов осуществления для квантования с частотой 20 мГц, каждый из преобразователей 54 и 56 может быть реализован на базе микросхемы CXD 1172 AM фирмы "Sony". Для сравнения: преобразователь D1179Q фирмы "Sony" или TRW 1175N2C40 с возможностью квантования с частотой 40 мГц стоит приблизительно на 400% больше, чем указанный выше преобразователь CXD72 AM.

Поскольку патентуемое устройство практически адаптировано для работы со скоростью 15-35 метасимволов за секунду множество существующих принципов возможно применять в других диапазонах скоростей символов.

Преобразователи 54 и 56 формируют цифровые сигналы, несущие информацию о полярности и величине квантуемых аналоговых входных сигналов. Предпочтительно каждый из преобразователей 54 и 56 формирует шестиразрядный сигнал при каждом квантовании. Для более низкого разрешения каждый из преобразователей 54 и 56 может формировать четырехразрядный сигнал при каждом квантовании.

Цифровые выходные канальные сигналы Iin и Qin преобразователей 54 и 56 имеют амплитуды, определяемые /a/ квадратурной фазомодуляцией подавленной несущей, поступающей на смесители 14 и 16, /b/ составляющими погрешности, обусловленной различиями частоты и фазы выходного сигнала гетеродина 21 по отношению к частоте и фазе подавленной несущей, поступающей на смесители 14 и 16 через каскады 12 усиления, и /c/ составляющими погрешности, обусловленной различиями скоростей символа и квантования преобразователей 54 и 56. Сигналы Iin и Qin подаются на обычную цифровую схему обработки данных на однокристальной БИС. Схема 57 включает узел обратного перемещения 58, обрабатывающий сигналы Iin и Qin, а также цифровой сигнал φ, несущий информацию о составляющей частотной и фазовой погрешностях. Цифровой узел обратного перемещения по входным сигналам формирует выходные сигналы I и Q по следующим уравнениям:

Цифровые выходные сигналы I и Q откорректированы с учетом частотных и фазовых отклонений между выходной частотой (ω0) гетеродина 21 и частотой (ω0) подавленной несущей на выходе усилителя 12. Величины I и Q рассчитываются цифровым вычислителем поворота систем координат, что значительно снижает стоимость устройства по сравнению со стоимостью известных устройств, использующих табличный поиск или принципы расчета, основанные на рядах тейлора, поскольку в предлагаемом варианте выполнения экономится приблизительно 50% логических элементов.

Выходные сигналы узла 58 одновременно подаются на выходное устройство 37, систему 60 слежения за несущей, систему 62 слежения за символом и автоматический регулятор 64 усиления, причем последние три схемы выполнены на однокристальной интегральной схеме, включающей схему 57 обработки данных. Система 60 слежения за несущей формирует выходной цифровой сигнал, разряды полярности и амплитуды которого представляют угол φ, разность между частотами и фазами гетеродина 21 и подавленной несущей на выходе каскадов 12. Цифровой сигнал подается как входной сигнал фазы на цифровой узел 58 обратного перемещения без преобразования в аналоговый сигнал, что позволяет снизить его стоимость.

Выходной цифровой сигнал системы 62 слежения за символом, полярность и амплитуды которого представляют временной сдвиг, необходимый для коррекции квантования каждого сигнала, подаваемого на АЦП 54 и 56 и является управляющим входом цифрового асинхронного фазовращателя 66, включенного в цифровую схему 57 обработки данных, выполненную на однокристальной ИС. В качестве фазовращателя 66 предпочтительно использовать, например, фазовращатель, описанный в находящейся на рассмотрении заявке, поданной 22 декабря 1992 г. Goldenberg и др. / Lowe, Price Leblanc & Bocker, N дела 1559-OO1/ под названием "Асинхронный цифровой фазовращатель". Фазовращатель 66 подключен также к источнику 68 синхросигналов, частота которых немного превышает частоту символов модулирующих канальных сигналов I и Q, поданных на АЦП 54 и 56. Соответственно, в определенных случаях, требующих работу по частоте, равной целому кратному, большему одной частоты символа, источник 68 перестраивается на частоту, приблизительно равную кратности частоты символа, при этом фазовращатель 66 имеет делитель частоты, коэффициент деления которого равен этому кратному с тем, чтобы получать сигналы выборки, подаваемые на преобразователи. На вход фазовращателя 66 поступает выходной сигнал системы 62 слежения за символом для обеспечения подачи синхросигналов источника 68 на входы синхронизации или регулирования квантования со скоростью, равной скорости следования символа.

Автоматический регулятор усиления 64, на входы которого подаются выходные сигналы I и Q узла 58, формирует сигнал управления коэффициентами усиления усилителей 23 и 25. Регулятор 64 содержит относительно недорогой сигма-дельта- модулятор предпочтительно такой, как описан Agrawal et al. в IEEE Transactions on Communications, Vol. N. 3, March, 1983, pages 360-369. В этом случае исключается требование использования для АЦП /фиг. 1/ цифрового сигнала, имеющего 8-10 разрядов. Выходные сигналы такого модулятора в регуляторе 64, имеющие регулируемую частоту, а также постоянную амплитуду и продолжительность, подаются на ФНЧ 70, выходной аналоговый сигнал с которого поступает на входы регулирования усиления усилителей 23 и 25.

На фиг. 3 представлена соответствующая блок-схема узла обратного перемещения для вычисления величин I и Q уравнений (1) и (2) по величинам Iin, Qin и φ. Простым методом вычисления этих величин является использование соответствующих таблиц или умножителей Sin и Cos для определения sinφ и cosφ в уравнениях (1) и (2). Однако такой подход потребует слишком большого количества элементов ИС. Если использовать так называемый цифровой вычислитель поворота систем координат /CORDIC/, предложенный Volder, количество элементов интегральной схемы сократится приблизительно на 50%, что, в свою очередь, снизит общую стоимость устройства.

Цифровой вычислитель поворота систем координат, показанный на фиг. 3, включает /M+I/ каскады 80.0, 80.1, 80.2....80.K.... 80.M /где M - целое нечетное число/, причем на каскад 80.0 подаются выходные сигналы Iin и Qin АЦП 54 и 56, а на последующие каскады 80.K подаются выходные сигналы Ik-1 и Qk-1 каскада 80k-1. Триггеры 81.1, ...81.p...81m-1, где p и M - целые нечетные числа, а общее количество каскадов 80 на схеме /фиг. 3/ - четное число/, подключенные между выходами каскадов с нечетными номерами и последующим по мере возрастания четным номером каскадом, работают на той же частоте, что и частота квантования преобразователей 54 и 56. Кроме того, на входы каскадов 80.0...80.K, 80.M соответственно поступают величины ξ0...ξk...ξm, полученные вычислителем 82 ξ, соответствующей выходному сигналу φ системы 60 слежения за несущей и являющемуся дополнительным кодом. На эти входы также поступают сигналы выборки, подаваемые через фазовращатель 62 на преобразователи 54 и 56. Вычислитель 82 при получении сигнала, несущего информацию о величине φ, формирует для каждого каскада 80.0 80.1, 80.2... 80.M одноразрядный сигнал величины ξ, который равен либо 0, либо 1.

При стабильной работе величины ξ рассчитываются один раз на каждое время символа аналогового сигнала, подаваемого на преобразователи 54 и 56. Для каждой последовательности Iin и Qin каскад 80.M вырабатывает последовательность сигналов I и Q, являющихся выходными сигналами узла обратного перемещения. Величина ξ является самым старшим разрядом сигнала φ, полученным на выходе системы 60 слежения за несущей. Величина ξ1, связанная с каскадом 80.1, является вторым самым старшим разрядом φ. Величины ξ2-ξm связаны каждая с величинами φ2-φm. Если величина φ2 = φ, то два самых старших разряда отбрасываются, а третий самый старший разряд реверсируется. Каждая величина ξ для каскадов 80.2 - 80.M связана с заранее установленным углом αj, например величина α2 для каскада 80.2 равна 26,5o, а величина α3 для каскада 80,3 - 14,04o и т.д., исходя из того, что αj = arctg (1/2 j-1), где j выбрана из целых чисел 2...k...M. В предпочтительном варианте выполнения M=7, а следовательно, должно быть восемь каскадов 80, а именно 80.0 - 80.7.

Входные сигналы каскадов 80.2 - 80.M суммируются после выбранного сдвига разряда и изменения полярности функции ξ, следующим образом:

Каскад 80.0 при получении Iin и Qin формирует Io и Qo согласно

а каскад 80.1 формирует I1 и Q1 в соответствии с

Поскольку (1-2ξj) и (2ξj-1) могут быть равны только +1 и -1, перемножение на (1-2ξj) и (2ξj-1) в основном представляют собой выборочное реверсирование или нереверсирование старших разрядов, входных сигналов Qk-1 и Ik-1 соответствующего каскада, несущих информацию о полярности. Эти операции могут быть выполнены полусумматорами. Умножение на 2-(k-1) также можно легко осуществить за счет сдвига разрядов вправо в регистре сдвига каскадов (k-1). Зета (ξ) - вычислитель 82 при получении величины φ из системы 60 слежения за несущей формирует одноразрядные величины ξ0, ξ1...ξk...ξm. В конкретном варианте выполнения, показанном на фиг. 3, самый старший и второй самый старший разряды  подаются на входы каскадов 80.0 и 80.1 как сигналы ξ0 и ξ1. Третий самый старший разряд /с изменением полярности, осуществленной инвертором 83/ в величине φ, а также оставшиеся разряды этой величины, полученные системой 60 слежения за несущей, подаются на ξ- блок 84.2, который формирует ξ- входы, а именно ξ2 и ξ3, для каскадов 80.2 и 80.3, а также многоразрядный сигнал φ4, величина которого определяется φ2- входом блока 84.2, а также величинами α2 и α3, записанными в блоке 84.2.

подаются на входы каскадов 80.0 и 80.1 как сигналы ξ0 и ξ1. Третий самый старший разряд /с изменением полярности, осуществленной инвертором 83/ в величине φ, а также оставшиеся разряды этой величины, полученные системой 60 слежения за несущей, подаются на ξ- блок 84.2, который формирует ξ- входы, а именно ξ2 и ξ3, для каскадов 80.2 и 80.3, а также многоразрядный сигнал φ4, величина которого определяется φ2- входом блока 84.2, а также величинами α2 и α3, записанными в блоке 84.2.

Выходной сигнал φ4ξ- блока 84.2 подается на триггер 86.4, запускаемый выходным сигналом фазовращателя 66 одновременно триггерами 81.1 - 81./M-2/. Триггер 86.4 подает в ξ- блок 84.6 зафиксированную копию выходного сигнала φ4 блока 84.2. ξ- блок 84.4 по выходному сигналу триггера 86.4, а также по записанным в нем значениям α4 и α5 формирует одноразрядные сигналы ξ4 и ξ5, подаваемые на соответствующие ξ- входы каскадов 80.4 и 80.5. Кроме того, ξ- блок 84.4 формирует многоразрядный сигнал φ6, определяемый выходным сигналом триггера 86.4 и записанными в ξ- блоке значениями α4 и α5. Многоразрядный выходной сигнал ξ- блока 84.6 подается на триггер 86.6, который по сигналам, подаваемым с фазовращателя 66, обеспечивает подачу зафиксированной копии выходного сигнала φ6 блока 84.4 в ξ- блок 84.6 ξ- блок 84.6 по выходному сигналу триггера 86.6 и записанным в нем значениям α6 и α7 формирует одноразрядные сигналы ξ6 и ξ7, которые подаются на ξ- входы каскадов 80.6 и 80.7.

Все ξ- блоки 84.2, 84.4 и 84.6 выполнены одинаково за исключением записанных в них величин α. Таким образом, приведенное описание ξ- блока 84.2 достаточно для понимания работы ξ- блоков 84.4 и 84.6.

Как показано на фиг. 3, по сигналу величины φ2 ξ- блок 84.2 вырабатывает сигналы φ4, ξ2 и ξ3. ξ- блок 84.2 включает многоразрядный цифровой регистр 88.2 и 88.3 для запоминания цифровых величин, соответствующих α2 (26,5o) и α3(14,04o). Указывающие полярность самые старшие разряды сигналов, записанные в регистрах, реверсируют для получения цифровых величин, представляющих соответственно -α2 и α3. Эти величины -α2 и -α3 записываются соответственно в регистры 88.2' и 88.3'. Сигналы, записанные в регистрах 88.2 и 88.2' подаются на входы мультиплексора 90.2, а сигналы, записанные в регистрах 88.3 и 88.3',- на входы мультиплексора 90.3. Мультиплексор 90.2 имеет управляющий вход, на который поступает информация старшего разряда φ2 для того, чтобы при изменении старшего разряда в φ2 величины α2 и -α2, поступающие на входы мультиплексора с регистров 88.2 и 88.2', выборочно подавались на многоразрядный выход мультиплексора 90.2. Многоразрядный выходной сигнал мультиплексора 90.2 и многоразрядный сигнал величины φ2, поступающий из ξ- вычислителя 84.2, складываются в цифровом сумматоре 92.2, формирующем на выходе многоразрядный сигнал  Самый старший разряд выходного сигнала φ3 подается на управляющий вход мультиплексора 88.3 для регулирования подключения одного из входов α3 и -α3 мультиплексора к его выходу. Многоразрядные выходные сигналы мультиплексора 90.3 и сумматора 92.2 суммируются цифровым сумматором 92.3, многоразрядный выходной сигнал φ4, с которого подается на вход ξ- блока 84.4.

Самый старший разряд выходного сигнала φ3 подается на управляющий вход мультиплексора 88.3 для регулирования подключения одного из входов α3 и -α3 мультиплексора к его выходу. Многоразрядные выходные сигналы мультиплексора 90.3 и сумматора 92.2 суммируются цифровым сумматором 92.3, многоразрядный выходной сигнал φ4, с которого подается на вход ξ- блока 84.4.

Самые старшие разряды сигналов φ2 и φ3, подаваемых на управляющие входы мультиплексоров 90.2 и 90.3, инвертируются соответственно инверторами 94.2 и 94.3. Таким образом, инверторы 94.2 и 94.3 формируют одноразрядные выходные сигналы, которые являются дополнительным кодом самых старших разрядов φ2 и φ3 для получения сигналов ξ2 и ξ3. Выходные сигналы инверторов 94.2 и 94.3 могут быть постоянными в течение продолжительности одного сигнала. Это достигается за счет подачи выходных сигналов инверторов 94.2 и 94.3 на триггеры 96.2 и 96.3, запускаемые теми же сигналами квантования, которые посылает фазовращатель 66 на преобразователи 54 и 56. Следовательно, триггеры 96.2 и 96.3 формируют постоянные двухразрядные величины ξ2 и ξ3 в течение интервала каждого квантования, осуществляемого преобразователями 54 и 56. Выходные сигналы триггеров 96.2 и 96.3 подаются соответственно на ξ- входы каскадов 80.2 и 80.3. Блоки 84.4 и 84.6 выполнены аналогичным образом и служат для подачи сигналов ξ4-ξ7 на ξ- входы блоков 80.4 и 80.7 соответственно.

Для решения уравнений /5/ и /6/ каскад 80.0 включает умножители 110 и 112, на которые поступают сигналы Iin и Qin, полученные с выхода преобразователей 54 и 56. На другие входы умножителей 110 и 112 поступают также сигналы (1-2ξ0) и (2ξ0-1), соответственно, значение ±1 которых получено соответствующими схемами 114 и 116, принимающими сигнал ξ0. Умножители 110 и 114 осуществляют суммирование по модулю 2 /с использованием двухразрядного полусумматора/ одноразрядных величин ξ0 и самого старшего разряда Iin, несущего информацию о полярности (многочисленные другие умножения и операции с (1-2ξk) c (2ξk-1) выполняются каскадами 80,0 - 80.M аналогичным образом). Выходные сигналы умножителей 110 и 112 подаются на соответствующие Io и Qo выходы каскада 80.0.

Для решения уравнений (7) и (8) каскад 80.1 содержит умножители 118 и 120, принимающие соответственно выходные сигналы Io и Qo каскада 80.0, подаваемые на входы каскада 80.1. Умножители 118 и 120 получают также величины ±1, рассчитанные в соответствии с (2ξ1-1) и (1-2ξ1) схемами 122 и 124, на каждую из которых поступает сигнал величины ξ1. Полученные выходные сигналы умножителей 118 и 120 подаются соответственно на один из входов сумматоров 126 и 128. На другие входы сумматоров 126 и 128 поступают соответственно сигналы Qo и Io, поступающие на каскад 80.1. Сумматоры 126 и 128 формируют соответственно выходные сигналы I1 и Q1.

Остальные каскады 80.2. ..80.k...80.1 выполнены одинаково и в основном так, как это представлено на фиг. 3A для каскада 80.K, используемого для решения уравнений (3) и (4). Каскад 80.K принимает выходные сигналы Ik-1 и Qk-1 каскада 80(k-1). Входные сигналы Ik-1 и Qk-1 подаются соответственно на один из входов сумматоров 130 и 132. Другой входной сигнал сумматора 130 получен сдвигом входного сигнала Qk-1 вправо на (k-1) разряд, осуществляемый регистром 134 сдвига, выходной сигнал с которого подается на один из входов умножителя 136. На другой вход умножителя поступает сигнал (1-2ξk), полученный схемой 138 при обработке поступающего на ее вход сигнала ξk. Выходной сигнал умножителя подается на другой вход сумматора 130.

Другой входной сигнал для сумматора 132 получен при подаче входного сигнала Ik-1 на регистр сдвига 14, осуществляющего сдвиги сигнала Ik-1 вправо на (k-1) разряд. Выходной сигнал регистра 140 сдвига умножается в умножителе 142 на сигнал (2ξk-1), полученный схемой 144 при обработке величины ξk. Выходной сигнал умножителя 142 подается на другой выход сумматора 132. Сумматоры 130 и 132 формируют соответственно выходные сигналы, представляющие Ik и Qk.

Хотя устройство, показанное на фиг. 3, имеет (M+1) отдельных каскадов 80.0 - 80.14, понятно, что в конкретном варианте выполнения необязательно использовать (M+1) каскад. Для минимизации аппаратурных средств можно использовать лишь некоторое количество каскадов, а выходные сигналы "последнего" возвращать обратно на предыдущий каскад.

На фиг. 4 представлена блок-схема системы 62 слежения за символом, на входы которой поступает один или два выходных сигнала I и Q узла 58 обратного перемещения и которая служит для формирования управляющего сигнала фазовращателя 66, принимающего также синхроимпульсы источника 68. Фазовращатель 66 управляет подачей сигналов квантования на АЦП 54 и 56. В предпочтительном варианте выполнения выходные сигналы I и Q подаются на вычислитель 150 показателя погрешности, который в основном сравнивает амплитуды соседних выборок, произведенных АЦП 54 и 56 аналоговых модулирующих сигналов I и Q. По соседним квантованным величинам производится оценка приблизительного отклонения соседних сигналов от нулевой линии. В идеальном случае каждый импульс выборки, подаваемый на преобразователи 54 и 56, находится в центре каждого сигнала, поступающего в преобразователь. Временная погрешность сигнала оценивается следующим образом:

(sign Ik)Ik-1 + (-sign Ik-1)Ik + (sign Qk)Qk-1 + (-sign Qk-1)Qk, (9)

где Ik - величина I для коэффициента k1;

Ik-1 - величина I для коэффициента (k-1);

Qk - величина Q для коэффициента k;

Qk-1 - величина Q для коэффициента (k-1).

Сигнал временной погрешности символа для двух соседних разрядов, полученный вычислителем 150 показателя погрешности, подается на цифровой фильтр 152 нижних частот синхронного детектора, в основном ФНЧ с частотой среза, представляющей долю процента частоты источника 68. Выходной сигнал фильтра 152 подается на интегратор 154, складывающий отфильтрованные величины временной погрешности и служащий для получения сигнала, представляющего действительную величину фазового сдвига для коррекции сигналов источника 68, чтобы сигналы выборки подавались на АЦП 54, 56 с частотой символа приблизительно в центре каждого символа. Выходной цифровой сигнал интегратора 154 подается на цифровой фазовращатель 156 преимущественно такого типа, который описан в ранее поданной заявке Goldenberg и др. / Lowe, Price, LeBlas & Becker, N 1559-001/. Импульсы источника 68, подаваемые на фазовращатель 156, имеют частоту, намного превышающую частоту символов, подаваемых на преобразователи 54 и 56. В основном фазовращатель 156 при получении цифрового управляющего сигнала с выхода интегратора 154 обеспечивает задержку выбранных сигналов источника 68 для того, чтобы сигналы выборки поступали на АЦП в требуемое время.

На фиг. 5 показан один из лучших вариантов выполнения вычислителя 150 показателя временной погрешности символа, имеющего каналы 160 и 162 вычисления временной погрешности сигнала I и Q. Произведенные в каналах 160 и 162 соответствующие вычисления временной погрешности складываются в сумматоре 164 для получения выходного сигнала составной временной погрешности. Поскольку каналы 160 и 162 идентичны, ограничимся описанием канала вычисления временной погрешности только для сигнала I. Соответствующие элементы канала Q обозначены такими же позициями, что и для канала I, за исключением того, что они имеют дополнительное обозначение "k".

На вход канала 160 вычисления подается выходной сигнал I вычислителя 58 узла обратного перемещения для выборки k, произведенной АЦП 54, поэтому этот входной сигнал обозначен как Ik. Элемент 166 задержки обеспечивает задержку входного сигнала Ik на временной интервал между символами модулирующего сигнала, подаваемого на преобразователь. Элемент 166 задержки формирует выходной сигнал Ik-1, амплитуда которого является функцией выборки, произведенной АЦП для символа (k-1). Выходной сигнал Ik-1 элемента 166 задержки подается на один из входов умножителя 168, на второй вход которого подается сигнал, представляющий знак Ik, т.е. самый высокий разряд символа Ik, несущий информацию о полярности и полученный с выхода детектора 170 знака. Выходной сигнал умножителя 168 подается на один из входов сумматора 172 согласно sign (Ik)Ik-1.

Другой входной сигнал сумматора представляет собой сигнал, равный -sign (Ik-1)Ik. Самый старший разряд выходного сигнала Ik-1 элемента 166 инвертируется элементом 174. Инвертированный выходной сигнал, в свою очередь, подается на один из входов мультиплексора 176, на второй вход которого поступает сигнал Ik. Сигнал, полученный в результате перемножения умножителем 176, подается на второй вход сумматора 172, который осуществляет суммирование в соответствии

sign IkIk-1 + (-sign Ik-1)Ik. /10/

В канале 162, на который поступает цифровой сигнал Qk, аналогичным образом получают выходной сигнал в соответствии

sign QkQk-1 + (-sign Qk-1)Qk. /11/

Полученные выходные сигналы каналов 160 и 162 I и Q соответственно суммируются в сумматоре 164, выходной сигнал с которого представляет собой временную погрешность символа для пары соседних символов в соответствии с ранее приведенным уравнением /9/.

Следует отметить, что необязательно для всех случаев использовать каналы I и Q. В некоторых случаях для получения сигнала коррекции погрешности символа возможно использование только одного из каналов. Хотя предпочтительно подавать выходные сигналы узла 58 обратного перемещения на систему 62 слежения за символом, однако возможно подавать выходные сигналы преобразователей 54 и 56 непосредственно на систему слежения за символом с меньшим разрешением для сигнала, полученного на выходе выходного устройства 37.

На фиг. 6 представлена блок-схема системы 60 слежения за несущей, принимающей выходные сигналы I и Q узла 58 обратного перемещения и служащей для получения сигнала, несущего информацию о частотной и фазовой погрешностях между частотой и фазой гетеродина 21 и частотой и фазой подавленной несущей радиосигнала, подаваемого на смесители 14 и 16. Схема на фиг. 6 включает измерительный вычислитель 180 погрешности, который, как правило, сравнивает амплитуды выходных сигналов I и Q, узла 58 для получения сигнала в соответствии

(-sign Q)(I) + (sign I)Q. (12)

Измерительный вычислитель 180 фазовой погрешности имеет мультиплексоры 182 и 184, на первые входы которых поступают соответствующие выходные сигналы I и Q узла 58. На второй вход мультиплексора 182 поступает сигнал -sign Q, полученный на выходе детектора 186, а на второй вход мультиплексора 184 - сигнал sign I, полученный на выходе детектора 188. Выходные сигналы мультиплексоров 182 и 184 складываются цифровым сумматором 190, выходной сигнал с которого получен в соответствии с приведенным выше уравнением (12). Выходной сигнал сумматора 190, таким образом, несет информацию об общей фазовой погрешности между выходным сигналом гетеродина и сигналом несущей, подаваемым на смесители 14 и 16.

Выходной сигнал измерительного вычислителя 180 фазовой погрешности подается на фильтр нижних частот синхронного детектора, предельная частота которого находится в диапазоне долей процента и нескольких процентов частоты сигнала источника 68. Выходной сигнал фильтра 192 интегрируется интегратором 194, выходной сигнал с которого представляет фазовую коррекцию φ, которая должна поступить на узел 58.

На фиг. 7 представлен автоматический регулятор 68 усиления усилителей 23 и 25, служащий для регулирования амплитудами модулирующего сигнала, подаваемого на ЦАП 54 и 58. В основном схема, показанная на фиг. 7, определяет амплитуду сигнала I и Q, имеющего наибольшую величину, сравнивает ее с опорной и формирует сглаживающий сигнал погрешности на одноразрядный сигма-дельта-модулятор, описанный как было указано выше, Agrawal. Сигма-дельта-модулятор формирует серии импульсов фиксированного времени следования и переменной частоты, которые усредняются ФНЧ для получения выходного аналогового сигнала, подаваемого на усилители 23 и 25 как сигнал управления усилением. Использование одноразрядного сигма-дельта-модулятора для ЦАП позволяет одновременно со снижением стоимости достичь приблизительно такого же разрешения, что и при использовании 8-10 разрядного ЦАП 42, что несомненно является важным преимуществом данного изобретения.

И, наконец, сигналы I и Q, полученные на выходе узла 58 или на выходах Iin и Qin преобразователей 54 и 56, подаются на соответствующие схемы 196 и 198 определения абсолютной величины, в представленном варианте выполнения на схемы определения абсолютной величины подаются выходные сигналы узла обратного перемещения. Схемы 196 и 198 отделяют самые старшие разряды, представляющие полярность, от сигналов I и Q. Эти сигналы затем подают на компаратор 200. Компаратор 200 выделяет сигнал I и Q с наибольшей амплитудой и вычитает ее из установленной величины (A) для максимальной амплитуды входных аналоговых сигналов, поступающих на цифровые преобразователи 54 и 56. Полученный цифровой сигнал погрешности подается на фильтр 202 нижних частот синхронного детектора, предельная частота которого составляет несколько процентов частоты источника 68. Выходной сигнал фильтра 202 подается на одноразрядный сигма-дельта-модулятор 204, выполненный в интегральном исполнении со схемами 58, 60 и 62. Сигма-дельта-модулятор 204 формирует серии импульсов с постоянной амплитудой переменной частоты, которые преобразуются ФНЧ 70 в аналоговый сигнал переменной амплитуды, подаваемый на усилители 23 и 25 как сигнал управления усилением.

Еще один вариант регулирования временными импульсами, подаваемыми на АЦП 54 и 56, показан на фиг. 8. Схема, показанная на фиг. 8, аналогична схеме на фиг. 4, так как обе эти схемы имеют измерительный вычислитель 150 ошибки символа, а также схеме на фиг. 5, имеющей фильтр 152 нижних частот синхронного детектора. Однако в схеме на фиг. 8 отсутствует источник 68 синхросигналов и цифровой фазовращатель 66. Вместо этих элементов выходной сигнал фильтра 152 подается на одноразрядный сигма-дельта-модулятор 206, изготовленный в интегральном исполнении на том же чипе, что и схемы 58, 60 и 62. Модулятор 206 формирует серии импульсов переменной частоты с постоянной амплитудой, подаваемые на ФНЧ 208, выходной аналоговый сигнал которого, в свою очередь, подается на вход регулирования частоты генератора 210, управляемого напряжением. Выходной сигнал этого генератора имеет частоту, приблизительно равную частоте следования символов, поступающих на АЦП 54 и 56. Указанный выходной сигнал подается на вход синхронизации преобразователей 54 и 56, обуславливая квантование поступающих на него символов модулирующих аналоговых сигналов со скоростью, равной скорости следования символов, преимущественно в центре каждого символа.

Хотя в настоящем описании представлено множество конкретных примеров осуществления данного изобретения, понятно, что в него могут быть внесены различные дополнения и изменения, без затрагивания сущности этого изобретения и объема притязаний, ограниченных заявленной формулой.

| название | год | авторы | номер документа |

|---|---|---|---|

| СПОСОБ СДВИГА ФАЗЫ И УСТРОЙСТВО ДЛЯ ЕГО ОСУЩЕСТВЛЕНИЯ | 1993 |

|

RU2141165C1 |

| ПРИЕМНАЯ И ПЕРЕДАЮЩАЯ АППАРАТУРА И СПОСОБ, ВКЛЮЧАЮЩИЙ ПУНКТУРИРОВАННОЕ СВЕРТОЧНОЕ КОДИРОВАНИЕ И ДЕКОДИРОВАНИЕ | 1994 |

|

RU2117390C1 |

| Кодек блочных кодов | 1987 |

|

SU1473088A1 |

| ПРИЕМНАЯ СИСТЕМА AMPS, ИСПОЛЬЗУЮЩАЯ АРХИТЕКТУРУ НУЛЕВОЙ ПРОМЕЖУТОЧНОЙ ЧАСТОТЫ | 2003 |

|

RU2308804C2 |

| ДЕМОДУЛЯТОР ФАЗОМАНИПУЛИРОВАННЫХ СИГНАЛОВ | 2008 |

|

RU2393641C1 |

| РАДИОМОДЕМ | 2024 |

|

RU2830959C1 |

| МНОГОРЕЖИМНОЕ УСТРОЙСТВО РАДИОСВЯЗИ И МНОГОРЕЖИМНЫЙ СОТОВЫЙ РАДИОТЕЛЕФОН | 1993 |

|

RU2128886C1 |

| АРХИТЕКТУРА КОММУНИКАЦИОННОЙ СИСТЕМЫ С РАСПРЕДЕЛЕННЫМИ ПРИЕМНИКАМИ С МНОГИМИ ПОЛЬЗОВАТЕЛЯМИ | 1996 |

|

RU2156033C2 |

| ДЕМОДУЛЯТОР ДВУХПОЗИЦИОННЫХ ФАЗОМАНИПУЛИРОВАННЫХ СИГНАЛОВ | 2018 |

|

RU2699066C1 |

| ДЕКОДЕР ЦИФРОВОГО ТЕЛЕВИЗИОННОГО СИГНАЛА С НЕСКОЛЬКИМИ НЕСУЩИМИ | 1994 |

|

RU2125346C1 |

Демодулятор, принимающий символ, содержащий аналоговый сигнал, имеет два относительно недорогих аналого-цифровых преобразователя для квантования канальных сигналов I и Q со скоростью, равной скорости следования символа. Узел обратного перемещения, принимающий выходные сигналы преобразователей и цифровой сигнал, представляющий коррекции частоты и фазы входного сигнала демодулятора, работает как цифровой вычислитель поворота системы координат с целью получения канальных цифровых сигналов I и Q, скомпенсированных коррекциями. Цифровой фазовращатель, на который поступает по меньшей мере один из цифровых сигналов I и Q, управляет процессом квантования входного сигнала, осуществляемого преобразователем. Технический результат заключается в создании нового усовершенствованного демодулятора и приемника. 4 с. и 18 з. п.ф-лы, 9 ил.

Q, для получения вторых цифровых канальных сигналов I и Q, имеющих величины, скорректированные с учетом частотных и фазовых погрешностей, а средство для приема по меньшей мере одного из канальных цифровых сигналов I и Q выполнено с возможностью регулирования процесса квантования канальных модулированных сигналов I и Q в аналого-цифровом преобразователе.

(Sign PkPk-1) + (-Sign Pk-1)Pk,

где Pk является величиной указания выборки, сделанной преобразователем для символа k;

Pk-1 - величина указания выборки, сделанной преобразователем для символа (k - 1).

(Sign Ik)Ik-1 + (-Sin Ik-1)Ik + (Sign Qk)Qk-1 + (-Sign Qk-1)Qk,

где Ik является величиной указания I для символа k;

Ik-1 - величина указания I для символа (k - 1);

Qk - величина указания Q для символа k;

Qk-1 - величина указания Q для символа (k - 1).

| Окунев Ю.Б | |||

| Цифровая передача информации фазомодулированными сигналами | |||

| - М.: Радио и связь, 1991, с.95 - 106 | |||

| Конвейерная кокильная машина | 1973 |

|

SU503632A1 |

| US 4583048 A, 15.04.86 | |||

| ВОЗДУХОЗАБОРНИК ДЛЯ СИСТЕМЫ КОНДИЦИОНИРОВАНИЯ | 1999 |

|

RU2153635C1 |

| БУРОВОЙ РАСТВОР | 2001 |

|

RU2203303C2 |

| Устройство для приема псевдослучайных сигналов | 1988 |

|

SU1596482A1 |

Авторы

Даты

1999-03-27—Публикация

1993-12-29—Подача