фиг.1

114

Изобретение относится к автоматике и вычислительной технике и может использоваться в системах считывания, преобразования и передачи информации.

Цель изобретения - расширение Функциональных возможностей за счет выделения тактового сигнала и повышения помехоустойчивости при нестабильном периоде повторения входного сиг- нала.

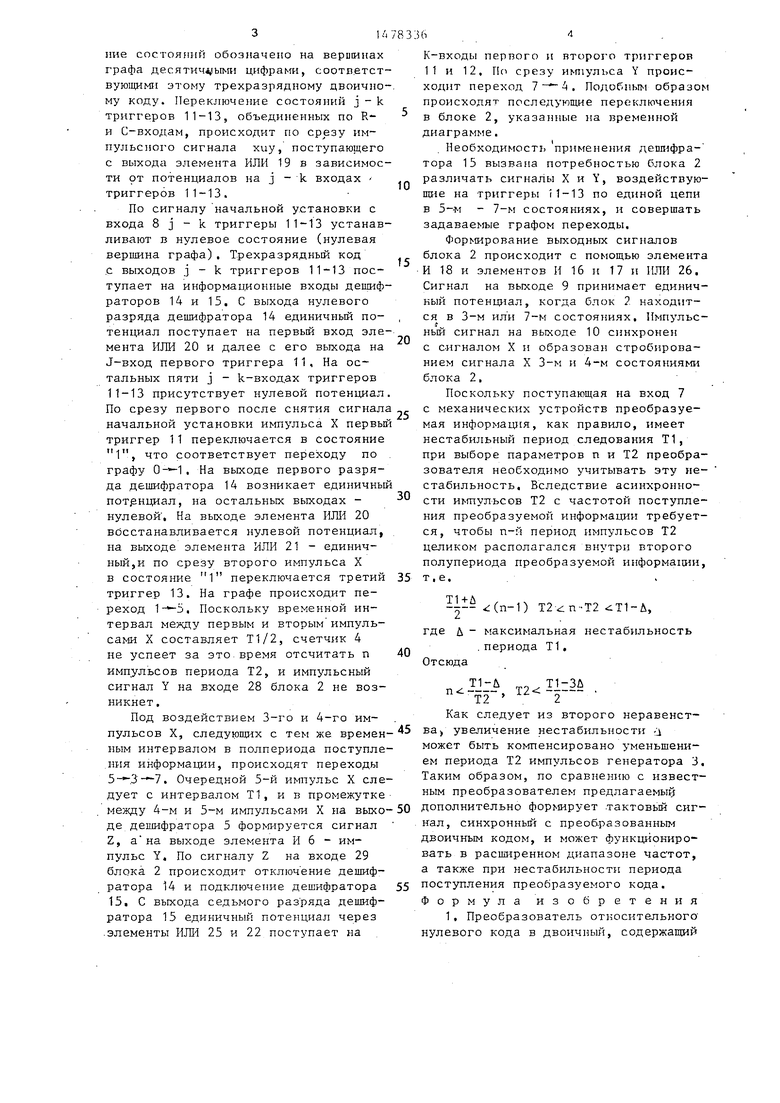

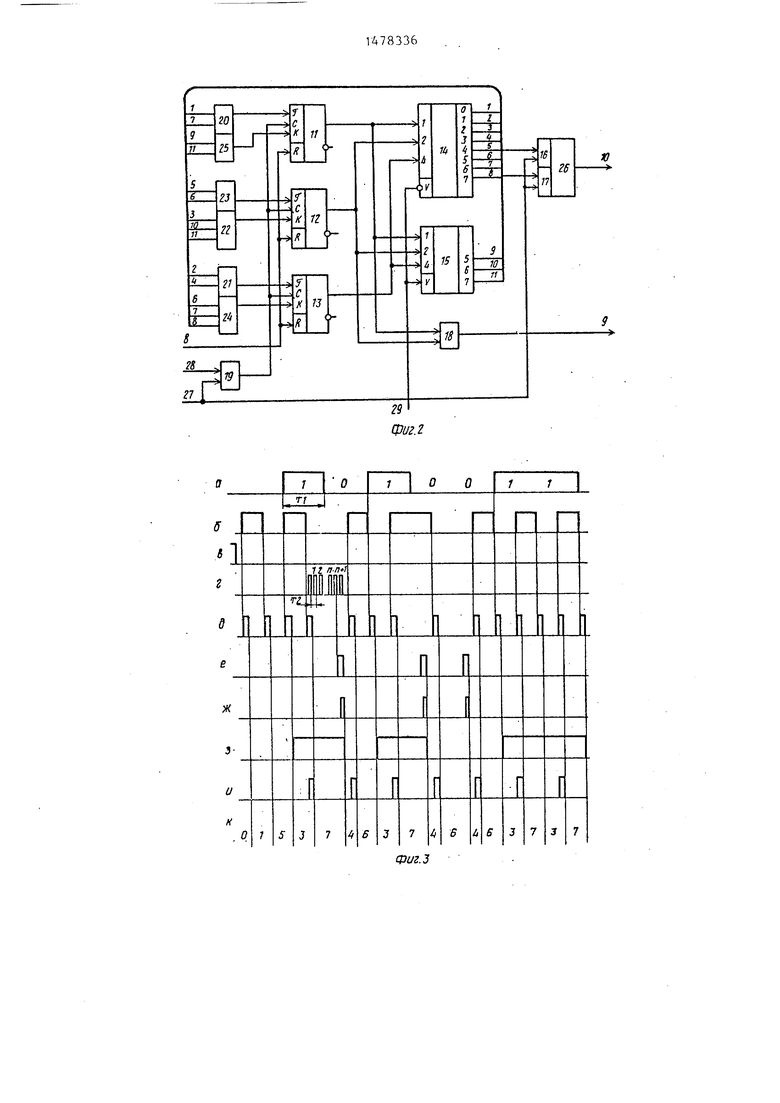

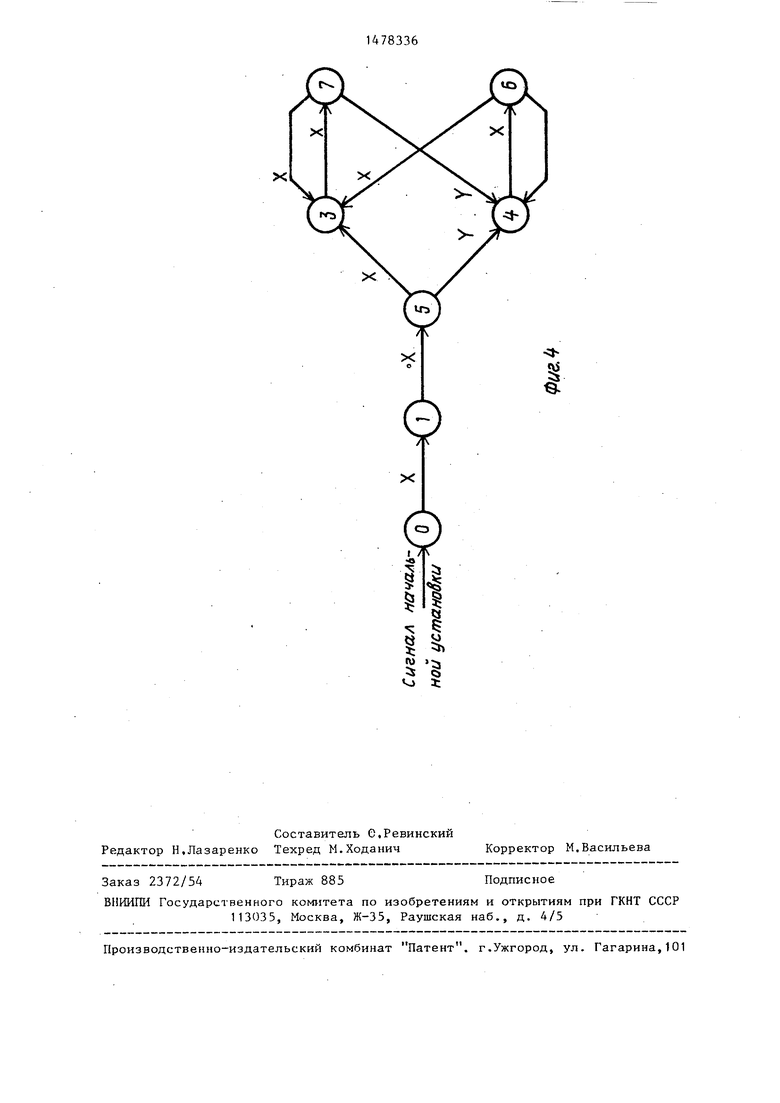

На фиг.1 представлена функциональная схема преобразователя; на фиг,2 - блок формирования выходных сигналов; на фиг.З - временные диаграммы сигна- лов; на фиг.4 - граф работы блока формирования выходных сигналов.

Преобразователь содержит (фиг.1) блок 1 выделения фронтов, блок 2 формирования выходных сигналов, генера- тор 3 импульсов, счетчик 4, дешифратор 5 и элемент И 6, На фиг,1 обозначены информационный вход 7, вход 8 начальной установки, информационный и тактовый выходы 9 и 10,

Блок 1 выделения фронтов служит для формирования импульсов, совпадающих с фронтами входного сигнала. Он может быть выполнен в виде соединенных последовательно дифференцирующего элемента и формирователя положительных импульсов.

Елок 2 формирования выходных сигналов содержит (фиг,2) первый - третий триггеры 11-13, первый и второй дешифраторы 14 и 15, первый - третий элементы И 16-18 и первый - восьмой элементы ИЛИ 19-26. На фиг,2 обозначены первый и второй информационные входы 27 и 28 и управляющий вход 29,

Преобразователь с таким выполнением блока 2 обеспечивает преобразование кода Манчестер I в код без возврата к нулю (ЬВН), В случае преобразования кода Манчестер II в код LBH к входам элемента И 18 надо вместо указанных подключить прямой выход триггера 13 и инверсный выход триггера 11 .

На фиг.З обозначены диаграммы: а - преобразуемой информации (код БВН); б - относительного нулевого кода (ОНК), в данном случае Манчестер I; в - сигнала на входе 8; г - сигнала на выходе генератора 3; д - сигнала X на входе 27 блока 2; е - сигнала Z на входе 29 блока 2; ж - сигнала Y на входе 28 блока 2; з - сигнала на выходе 9; и - сигнала

Q

g

0 5

о

п

0 5

5

362

на выходе 10; к - номера состояний блока 2 на графе фиг,4.

Преобразователь ОНК в двоичный код работает следующим образом,

ОНК, несущий двоичную информацию, например 1010011, поступает на вход 7 преобразователя,

Для определенности представим принцип кодирования двоичной информации в ОНК таким, что символу 1 соответствует повторение предыдущего элемента кодирования, а символу О - смека элемента кодирования на противоположный. Элемент кодирования определяется тем, в какую из половин периода Т1 следования информации передается единичный (нулевой) уровень,

С выхода блока 1 последовательность положительных импульсов, синхронных с фронтами и срезами ОНК, поступает на вход 27 блока 2, Тем самым формируется сигнал X, поступающий и на R-вход счетчика 4,

Генератор 3 вырабатывает последовательность положительных импульсов с периодом Т2, которые поступают на С-вход счетчика 4 и один из входов элемента И 6. Группа выходов счетчика 4 подключена к информационным входам дешифратора 5, п-й выход (пЈ2 -1 , где k - разрядность счетчика 4) дешифратора 5 подключен к второму входу элемента И 6 и управляющему входу 29 блока 2, Если счетчик 4 в промежутке между двумя соседними импульсами на его R-входе успеет сосчитать п импульсов периодом Т2, то на выходе дешифратора 5 появится сигнал разрешения для пропуска (п+1)-го импульса с периодом Т2 от генератора 3 элементом И 6, Таким образом, на выходе элемента И 6 формируется сигнал Y, представляющий собой каждый (п+1)-й импульс с периодом Т2 после возникновения последнего импульса на входе 27 блока 2 и на R-входе счетчика 4,

Елок 2 управления (фиг,2) работает в соответствии с графом (фиг,4) и формирует потенциальный двоичный последовательный код на выходе 9 и такты преобразования на выходе 10, Состояния j - k триггеров 11-13 рассматривается как трехразрядный параллельный двоичный код, у которого младший первый разряд реализуется первым j - k триггером 11, второй разряд - вторым j - k триггером 12 и старший третий - третьим j - k триггером 13. Кодирова

ние состояний обозначено на вериинах графа десятичными цифрами, соответствующими этому трехразрядному двоичному коду. Переключение состояний j - k триггеров 11-13, объединенных по R- и С-входам, происходит по срезу импульсного сигнала хиу, поступающего с выхода элемента ИЛИ 19 в зависимости от потенциалов на j - k входах триггеров 11-13.

По сигналу начальной установки с входа 8 j - k триггеры 11-13 устанавливают в нулевое состояние (нулевая вершина графа), Трехразрядный код с выходов j - k триггеров 11-13 поступает на информационные входы дешифраторов 14 и 15. С выхода нулевого разряда дешифратора 14 единичный по- тенциал поступает на первый вход элемента ИЛИ 20 и далее с его выхода на J-вход первого триггера 11, На остальных пяти j - k-входах триггеров 11-13 присутствует нулевой потенциал. По срезу первого после снятия сигнала начальной установки импульса X первый триггер 11 переключается в состояние 1, что соответствует переходу по графу . На выходе первого разряда дешифратора 14 возникает единичный потенциал, на остальных выходах - нулевой. На выходе элемента ИЛИ 20 восстанавливается нулевой потенциал, на выходе элемента ИЛИ 21 - единичный по срезу второго импульса X в состояние 1 переключается третий триггер 13. На графе происходит переход 1 . Поскольку временной интервал между первым и вторым импульсами X составляет Т1/2, счетчик 4 не успеет за это время отсчитать п импульсов периода Т2, и импульсный сигнал Y на входе 28 блока 2 не возникнет .

Под воздействием 3-го и 4-го импульсов X, следующих с тем же времен- ным интервалом в полпериода поступления информации, происходят переходы , Очередной 5-й импульс X следует с интервалом Т1, и в промежутке между 4-м и 5-м импульсами X на выхо- де дешифратора 5 формируется сигнал Z, а на выходе элемента И 6 - импульс Y, По сигналу Z на входе 29 блока 2 происходит отключение дешифратора 14 и подключение дешифратора 15, С выхода седьмого разряда дешифратора 15 единичный потенциал через элементы ИЛИ 25 и 22 поступает на

0

5

0

. 5 0

0 5

0

К-входы первого и второго триггеров 11 и 12, По срезу импульса Y происходит переход 7 4 . Подобным образом происходят последующие переключения в блоке 2, указанные на временной диаграмме.

Необходимость применения дешифратора 15 вызвана потребностью блока 2 различать сигналы X и Y, воздействующие на триггеры 11-13 по единой цепи в 5-м - 7-м состояниях, и совершать задаваемые графом переходы.

Формирование выходных сигналов блока 2 происходит с помощью элемента И 18 и элементов И 16 п 17 и ИЛИ 26. Сигнал на выходе 9 принимает единичный потенциал, когда блок 2 находится в 3-м или 7-м состояниях. Импульсный сигнал на выходе 10 синхронен с сигналом X и образован стробирова- нием сигнала X 3-м и 4-м состояниями блока 2,

Поскольку поступающая на вход 7 с механических устройств преобразуемая информация, как правило, имеет нестабильный период следования Т1, при выборе параметров п и Т2 преобразователя необходимо учитывать эту нестабильность. Вследствие асинхронно- сти импульсов Т2 с частотой поступления преобразуемой информации требуется, чтобы п-п период импульсов Т2 целиком располагался внутри второго полупериода преобразуемой информации, т.е.

(n-1) iT1-A,

где д - максимальная нестабильность

периода Т1, Отсюда

„.- , .

Как следует из второго неравенства увеличение нестабильности -л может быть компенсировано уменьшением периода Т2 импульсов генератора 3. Таким образом, по сравнению с известным преобразователем предлагаемый дополнительно формирует тактовый сигнал, синхронный с преобразованным двоичным кодом, и может функционировать в расширенном диапазоне частот, а также при нестабильности периода поступления преобразуемого кода. Формула изобретения

1, Преобразователь относительного нулевого кода в двоичный, содержащий

блок выделения фронтов, счетчик и элемент И, отличающийся тем, что, с целью расширения функциональный возможностей за счет выделе- кия тактового сигнала и повышения помехоустойчивости при нестабильном - периоде повторения входного сигнала, в преобразователь введены блок формирования выходных сигналов, дешифратор и генератор импульсов, выход которого подключен к первому входу элемента И и счетному входу счетчика, выходы которого соединены с входами дешифратора, выход которого подключен к второму входу элемента К и управляющему входу блока формирования выходных сигналов, вход начальной установки которого является одноименным входом преобразователя, вход блока выделения фронтов является информационным входом преобразователя, выход блока выделения фронтов соединен с первым информационным входом блока формирования выходных сигналов и входом обнуления счетчика, выход элемента И подключен к второму информационному входу блока формирования выходных сигналов, первый и второй выходы которого являются соответственно информационным и тактовым выходами преобразователя.

2. Преобразователь по п,1, отличающийся тем, что блок формирования выходных сигналов со10

15

вого триггера соединен с ш-рвымп вхо дами первого и второго дешифраторов и третьего элемента И, выход второго триггера подключен к вторым входам первого и второго дешифраторов и третьего элемента И, выход которого является первым выходом блока, выход третьего триггера подключен к третьи входам дешифратора, выходы нулевого второго разрядов первого дешифратора соединены с пер-выми входами соответственно второго - четвертого элемен- тов ИЛИ, выход третьего разряда первого дешифратора подключен к вторым входам первого элемента И и третьего элемента ИЛИ, выход четвертого разря да первого дешифратора подключен к второму входу второго элемента И и первому входу пятого элемента ИЛИ, выход пятого разряда первого дешифратора соединен с вторым входом пято го и первым входом шестого элементов ИЛИ, выход шестого разряда первого 25 дешифратора подключен к вторым входа второго и шестого элементов ИЛИ, выход седьмого разряда первого дешифра тора и пятого и шестого разрядов второго дешифратора соединены соответственно с третьим входом шестого, первым входом седьмого и вторым входом четвертого элементов ИЛИ, выход седьмого разряда второго дешифратора подключен к третьему входу четвертог и второму входу седьмого элементов

20

30

держит триггеры, дешифраторы, элемен- 35 ИЛИ, выходы второго и седьмого, пя10

15

83366

вого триггера соединен с ш-рвымп входами первого и второго дешифраторов и третьего элемента И, выход второго триггера подключен к вторым входам первого и второго дешифраторов и третьего элемента И, выход которого является первым выходом блока, выход третьего триггера подключен к третьим входам дешифратора, выходы нулевого - второго разрядов первого дешифратора соединены с пер-выми входами соответственно второго - четвертого элемен- тов ИЛИ, выход третьего разряда первого дешифратора подключен к вторым входам первого элемента И и третьего элемента ИЛИ, выход четвертого разряда первого дешифратора подключен к второму входу второго элемента И и первому входу пятого элемента ИЛИ, выход пятого разряда первого дешифратора соединен с вторым входом пятого и первым входом шестого элементов ИЛИ, выход шестого разряда первого 25 дешифратора подключен к вторым входам второго и шестого элементов ИЛИ, выход седьмого разряда первого дешифратора и пятого и шестого разрядов второго дешифратора соединены соответственно с третьим входом шестого, первым входом седьмого и вторым входом четвертого элементов ИЛИ, выход седьмого разряда второго дешифратора подключен к третьему входу четвертого и второму входу седьмого элементов

20

30

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для формирования адресов операндов процессора быстрого преобразования Фурье | 1987 |

|

SU1444814A1 |

| Частотный аналого-цифровой преобразователь | 1989 |

|

SU1702528A1 |

| Устройство для приема и передачи информации | 1988 |

|

SU1536422A1 |

| Аналого-цифровой преобразователь знакопеременных сигналов | 1987 |

|

SU1483641A1 |

| Устройство для контроля дефектов фотошаблона | 1989 |

|

SU1698712A1 |

| Устройство для разбиения графа на подграф | 1985 |

|

SU1305703A1 |

| Цифроаналоговый генератор телевизионного сигнала | 1989 |

|

SU1654978A1 |

| Устройство для определения кратчайшего пути на графе | 1983 |

|

SU1134944A1 |

| Устройство для цифровой записи-воспроизведения речевой информации | 1987 |

|

SU1490691A1 |

| Устройство для разбиения графа на подграфы | 1984 |

|

SU1273941A1 |

Изобретение относится к автоматике и вычислительной технике. Его использование в системах считывания, преобразования и передачи информации позволяет расширить функциональные возможности за счет выделения тактового сигнала и повысить помехоустойчивость при нестабильном периоде повторения входного сигнала. Преобразователь содержит блок 1 выделения фронтов, счетчик 4 и элемент И6. Благодаря введению генератора 3, дешифратора 5 и блока 2 формирования выходных сигналов с соответствующим выполнением в преобразователе обеспечивается стабильная работа. 1 з.п. ф-лы, 4 ил.

ты И и элементы ИЛИ, первый вход первого элемента ИЛИ объединен с первыми входами первого и второго элементов И и является первым информационным входом блока, второй вход первого элемента ИЛИ является вторым информационным входом блока, выход первого элемента ИЛИ подключен к ОБХОДам первого - третьего триггеров, R-входы которых объединены и являются входом начальной установки блока, выход пер

того и четвертого, третьего и шестого элементов ИЛИ подключены соответственно к J- и К-входам первого - третьего триггеров, инверсный управляющий вход первого и прямой управляющий вход второго дешифратора объединены и являются управляющим входом . блока, выходы первого и второго элементов И соединены с входами восьмого элемента ИЛИ, выход которого является вторым выходом блока,

Составитель С.Ревинский Редактор Н.Лазаренко Техред М.Ходанич

Заказ 2372/54

Тираж 885

ВНИИПИ Государственного комитета по изобретениям и открытиям при ГКНТ СССР 113035, Москва, Ж-35, Раушская наб., д. 4/5

Производственно-издательский комбинат Патент. г.Ужгород, ул. Гагарина,101

Корректор М.Васильева

Подписное

| Преобразователь биимпульсного двоичного сигнала в бинарный сигнал | 1983 |

|

SU1200426A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Электроника, 1982, т | |||

| Устройство двукратного усилителя с катодными лампами | 1920 |

|

SU55A1 |

| Аппарат, предназначенный для летания | 0 |

|

SU76A1 |

| Устройство для приема биимпульсного сигнала | 1972 |

|

SU467483A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1989-05-07—Публикация

1987-04-13—Подача