Изобретение относится к импульсной технике, в частности к преобразователям напряжения в цифровой код с промежуточным преобразованием в частоту импульсов.

Цель изобретения - повышение точности преобразования.

На фиг. 1 изображена блок-схема АЦП; на фиг. 2 - блок-схема блока удвоения числа импульсов; на фиг.З - схема блока коррекции; на фиг. 4 - схема блока управления; на фиг. 5 - блок-схема преобразователя кодов; на фиг. 6 - временная диаграмма работы АЦП.

АЦП содержит шины входного 1 и нулевого 2 напряжений, шину 3 запуска в работу, шину 4 напряжения сети питания, шину 5 сигнала окончания преоб- разования, выходную шину 6, преобразователь 7 напряжения в частоту (ПНЧ), цифроаналоговый преобразователь (ЦАП) 8 с дополнительным младшим разрядом и токовым выходным сигналом, источник 9 тока смещения, первый 10 и второй 11 переключатели, каждый из которых имеет два входа и резистор на выходе, который при наличии сигнала на управляющем входе подключен к первому входу, а при его

4

00 00

о

4

отсутствии - к второму входу, третий переключатель 12, имеющий один вход, который при наличии сигнала на управляющем входе подключен к первому выходу, а при его отсутствии - к второму выходу, реверсивные счетчики 13 и 14, имеющие знаковые старшие разряды с весом N0, входы для установки О кода и управления режимом вычитания, преобразователь 15 кодов, который в зависимости от сигналов на управляющих входах передает на выходы прямой или инверсный код с дополнительным младшим разрядом или на всех выходах выдает 1 код, элементы И 16-21, элементы ИЛИ 22, 23, блок 24 удвоения числа импульсов, блок 25 коррекции, блок 26 управления.

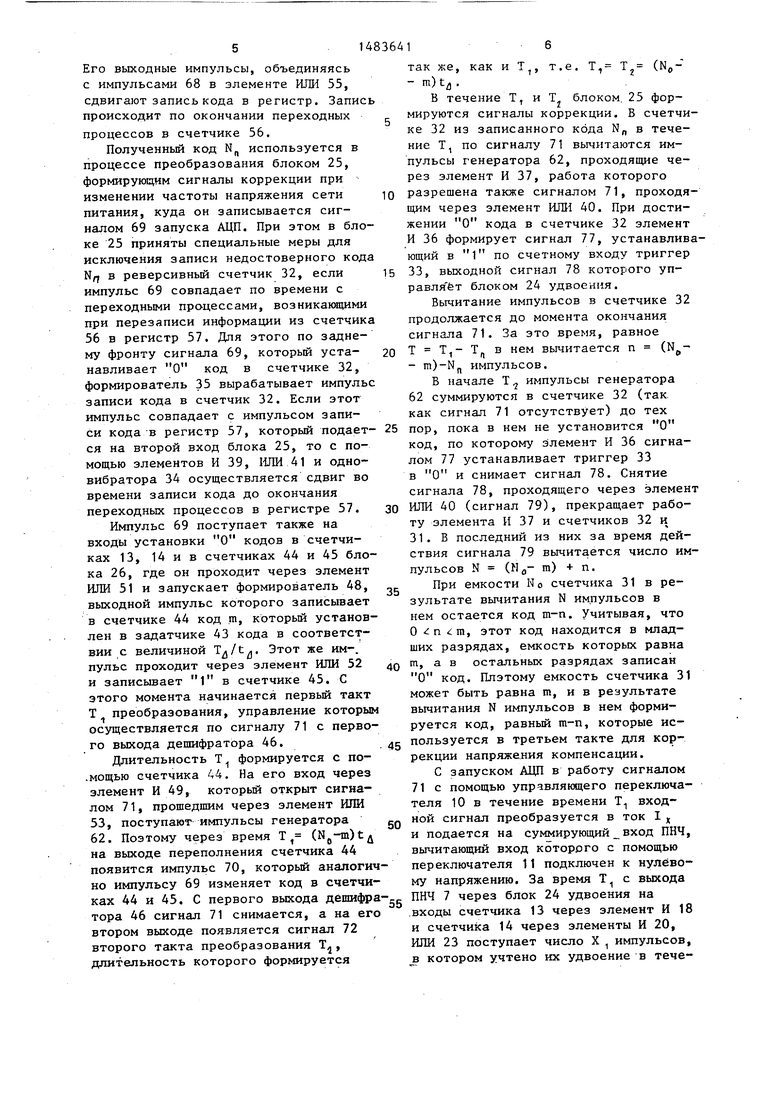

Блок удвоения 24 (фиг. 2) содержит формирователи 27 и 28 импульсов, элемент И 29 и элемент ИЛИ 30, блок 25 коррекции (фиг. 3) содержит счетчик 31, работающий на вычитание и имеющий емкость М0 и вход для устано ки О кода, реверсивный счетчик 32, имеющий емкость т, входы для записи и разряды кода и управления режимом вычитания, триггер 33, одновибратор 34, формирователь 35 импульсов, элементы И 36, 37, группу элементов И 38, элемент И 39, элементы ИЛИ 40, 41, группу элементов ИЛИ 42.

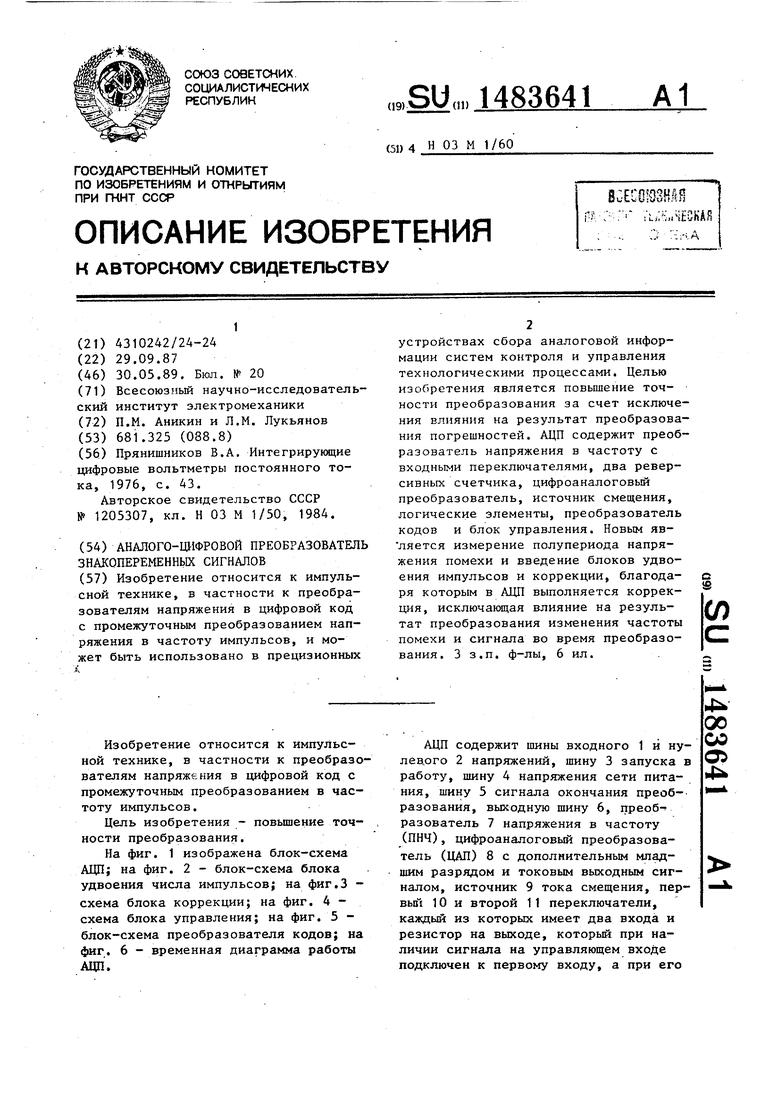

Блок 26 управления (фиг. 4) содержит задатчик 43 кода, который может быть выполнен, например, для каждого разряда в виде перемычки, подсоединеной к шине питания для 1 кода или к нулевой шине для О кода, первьй счетчик 44, имеющий емкость N0, входы для установки О кода, записи кода, входы разрядов и выход переполнения, счетчик 45, дешифратор 46 на четыре выхода, формирователи 47 и 48 импульсов, элементы И 49, 50, элементы ИЛИ 51-55, счетчик 56 с емкостью NO, регистр 57, формирователь 58 импульсов, одновибратор 59, элемент И 60, формирователь 61 импульсов при прохождении напряжения сети питания через нуль, генератор 62 импульсов. Блоки 55-61 являются узлом измерения полупериода помехи сети питания.

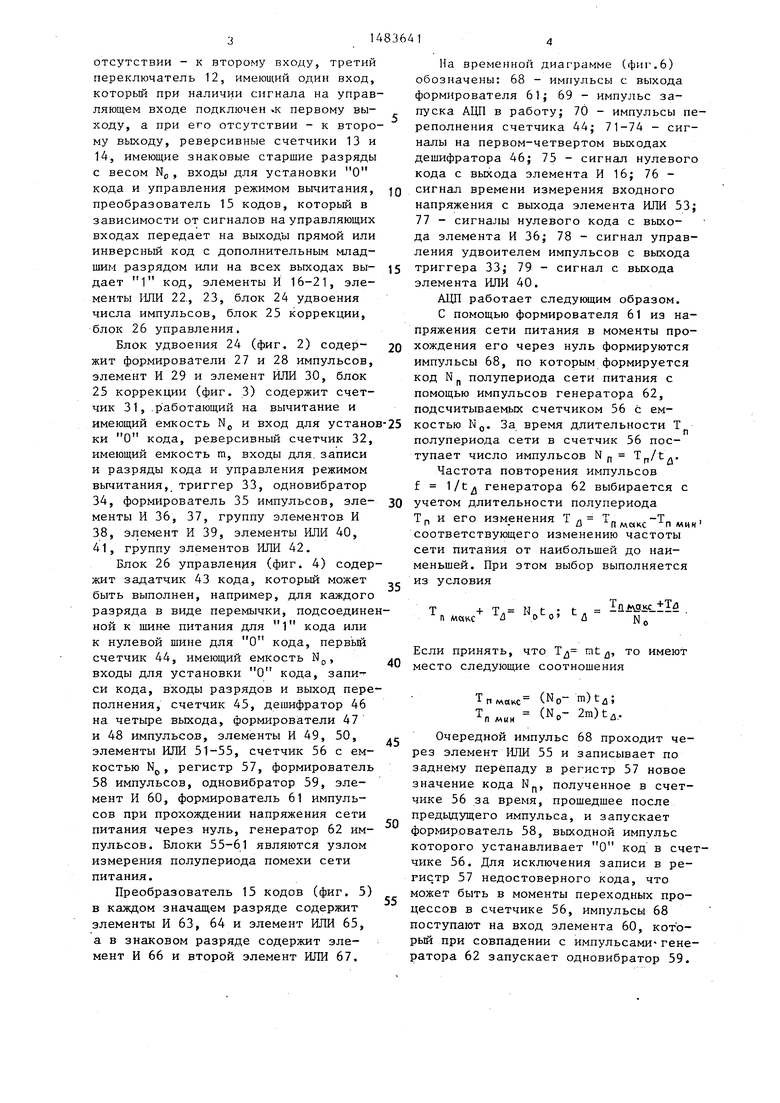

Преобразователь 15 кодов (фиг. 5) в каждом значащем разряде содержит элементы И 63, 64 и элемент ИЛИ 65, а в знаковом разряде содержит элемент И 66 и второй элемент ИЛИ 67.

0

5

0

5

0

5

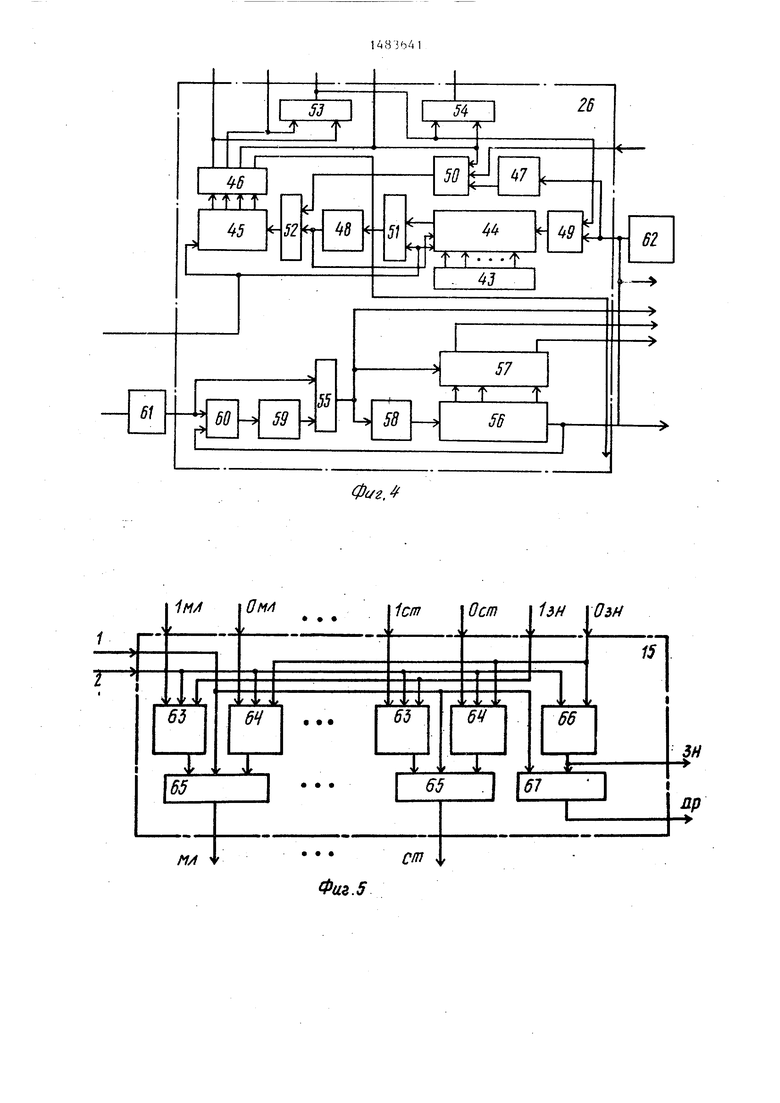

На временной диаграмме (фиг.6) обозначены: 68 - импульсы с выхода формирователя 61; 69 - импульс запуска АЦП в работу; 70 - импульсы переполнения счетчика 44; 71-74 - сигналы на первом-четвертом выходах дешифратора 46; 75 - сигнал нулевого кода с выхода элемента И 16; 76 - сигнал времени измерения входного напряжения с выхода элемента ИЛИ 53; 77 - сигналы нулевого кода с выхода элемента И 36; 78 - сигнал управления удвоителем импульсов с выхода триггера 33; 79 - сигнал с выхода элемента ИЛИ 40.

АЦП работает следующим образом.

С помощью формирователя 61 из напряжения сети питания в моменты прохождения его через нуль формируются импульсы 68, по которым формируется код Nn полупериода сети питания с помощью импульсов генератора 62, подсчитываемых счетчиком 56 с емкостью N0. За время длительности Т полупериода сети в счетчик 56 поступает число импульсов N п Tn/tд.

Частота повторения импульсов f 1/t генератора 62 выбирается с учетом длительности полупериода Тп и его изменения Тд Тп макс-Тп ми„, соответствующего изменению частоты сети питания от наибольшей до наименьшей. При этом выбор выполняется из условия

Т п м«кс+ ТД Н оL°

Jujftgjsc j;Td

N.

Если принять, что Тд nta, то имеют место следующие соотношения

тпм«кс (NO m)td;

п мни

(No- 2m)tй.

Очередной импульс 68 проходит через элемент ИЛИ 55 и записывает по заднему перепаду в регистр 57 новое значение кода Nn, полученное в счетчике 56 за время, прошедшее после предыдущего импульса, и запускает формирователь 58, выходной импульс которого устанавливает О код в счетчике 56. Для исключения записи в регистр 57 недостоверного кода, что может быть в моменты переходных процессов в счетчике 56, импульсы 68 поступают на вход элемента 60, который при совпадении с импульсами- генератора 62 запускает одновибратор 59.

51483641

Его выходные импульсы, объединяясь с импульсами 68 в элементе ИЛИ 55, сдвигают запись кода в регистр. Запись происходит по окончании переходных процессов в счетчике 56.

Полученный код Nn используется в процессе преобразования блоком 25, формирующим сигналы коррекции при изменении частоты напряжения сети ю питания, куда он записывается сигналом 69 запуска АЦП. При этом в блоке 25 приняты специальные меры для исключения записи недостоверного кода Nfl в реверсивный счетчик 32, если 15 импульс 69 совпадает по времени с переходными процессами, возникающими при перезаписи информации из счетчика 56 в регистр 57. Для этого по заднему фронту сигнала 69, который устанавливает О код в счетчике 32, формирователь 35 вырабатывает импульс записи кода в счетчик 32. Если этот импульс совпадает с импульсом записи кода в регистр 57, который подается на второй вход блока 25, то с помощью элементов И 39, ИЛИ 41 и одно- вибратора 34 осуществляется сдвиг во времени записи кода до окончания переходных процессов в регистре 57.

Импульс 69 поступает также на входы установки О кодов в счетчиках 13, 14 и в счетчиках 44 и 45 блока 26, где он проходит через элемент ИЛИ 51 и запускает формирователь 48, выходной импульс которого записывает в счетчике 44 код га, который установлен в задатчике 43 кода в соответствии с величиной . Этот же им-. пульс проходит через элемент ИЛИ 52 и записывает 1 в счетчике 45. С этого момента начинается первый такт

так же, как и Т7,

т.е.

- m)td.

В течение Т,

Т,

Т2 (Neи Т блоком 25 формируются сигналы коррекции. В счетчи ке 32 из записанного кода Nn в течение Т, по сигналу 71 вычитаются импульсы генератора 62, проходящие через элемент И 37, работа которого разрешена также сигналом 71, проходя щим через элемент ИЛИ 40. При достижении О кода в счетчике 32 элемент И 36 формирует сигнал 77, устанавлива ющий в 1 по счетному входу триггер 33, выходной сигнал 78 которого уп- равля ёт блоком 24 удвоения.

Вычитание импульсов в счетчике 32 продолжается до момента окончания сигнала 71. За это время, равное

(N,20 Т Т.,- Тп в нем вычитается п - m)-Nn импульсов.

В начале Т 7 импульсы генератора 62 суммируются в счетчике 32 (так как сигнал 71 отсутствует) до тех

25 пор, пока в нем не установится О код, по которому элемент И 36 сигналом 77 устанавливает триггер 33 в О и снимает сигнал 78. Снятие сигнала 78, проходящего через элемент

30 ИЛИ 40 (сигнал 79), прекращает работу элемента И 37 и счетчиков 32 и 31. В последний из них за время действия сигнала 79 вычитается число импульсов N (М0- га) + п.

35

40

45

При емкости No счетчика 31 в результате вычитания N импульсов в нем остается код m-n. Учитывая, что О п :га, этот код находится в младших разрядах, емкость которых равна т, а в остальных разрядах записан О код. Плэтому емкость счетчика 31 может быть равна т, и в результате вычитания N импульсов в нем формируется код, равный m-n, которые используется в третьем такте для коррекции напряжения компенсации.

С запуском АЦП в работу сигналом 71 с помощью управляющего переключателя 10 в течение времени Т., входной сигнал преобразуется в ток I „ и подается на суммирующий вход ПНЧ, вычитающий вход которого с помощью переключателя 11 подключен к нулево- но импульсу 69 изменяет код в счетчи- му напряжению. За время Т1 с выхода ках 44 и 45. С первого выхода дешифра- 5 ПНЧ 7 через блок 24 удвоения на тора 46 сигнал 71 снимается, а на его входы счетчика 13 через элемент И 18 втором выходе появляется сигнал 72 и счетчика 14 через элементы И 20, второго такта преобразования Т, длительность которого формируется

Т преобразования, управление которым осуществляется по сигналу 71 с первого выхода дешифратора 46.

Длительность Т1 формируется с по- .мощью счетчика 44. На его вход через элемент И 49, который открыт сигналом 71, прошедшим через элемент ИЛИ 53, поступают импульсы генератора 62. Поэтому через время Т , (N8-m)tЈ на выходе переполнения счетчика 44 появится импульс 70, который аналогич50

ИЛИ 23 поступает число X импульсов,

в котором учтено их удвоение в тече

т.е.

Т,

Т2 (NeТ блоком 25 формируются сигналы коррекции. В счетчике 32 из записанного кода Nn в течение Т, по сигналу 71 вычитаются импульсы генератора 62, проходящие через элемент И 37, работа которого разрешена также сигналом 71, проходящим через элемент ИЛИ 40. При достижении О кода в счетчике 32 элемент И 36 формирует сигнал 77, устанавливающий в 1 по счетному входу триггер 33, выходной сигнал 78 которого уп- равля ёт блоком 24 удвоения.

Вычитание импульсов в счетчике 32 продолжается до момента окончания сигнала 71. За это время, равное

(N,Т Т.,- Тп в нем вычитается п - m)-Nn импульсов.

В начале Т 7 импульсы генератора 62 суммируются в счетчике 32 (так как сигнал 71 отсутствует) до тех

пор, пока в нем не установится О код, по которому элемент И 36 сигналом 77 устанавливает триггер 33 в О и снимает сигнал 78. Снятие сигнала 78, проходящего через элемент

ИЛИ 40 (сигнал 79), прекращает работу элемента И 37 и счетчиков 32 и 31. В последний из них за время действия сигнала 79 вычитается число импульсов N (М0- га) + п.

С запуском АЦП в работу сигналом 71 с помощью управляющего переключателя 10 в течение времени Т., входной сигнал преобразуется в ток I „ и подается на суммирующий вход ПНЧ, вычитающий вход которого с помощью переключателя 11 подключен к нулево- му напряжению. За время Т1 с выхода ПНЧ 7 через блок 24 удвоения на входы счетчика 13 через элемент И 18 и счетчика 14 через элементы И 20,

ИЛИ 23 поступает число X импульсов,

С запуском АЦП в работу сигналом 71 с помощью управляющего переключателя 10 в течение времени Т., входной сигнал преобразуется в ток I „ и подается на суммирующий вход ПНЧ, вычитающий вход которого с помощью переключателя 11 подключен к нулево- му напряжению. За время Т1 с выхода ПНЧ 7 через блок 24 удвоения на входы счетчика 13 через элемент И 18 и счетчика 14 через элементы И 20,

в котором учтено их удвоение в тече

т,-т ние времени Т: Х2 k j (Ic+ lx)dt +

Г + 2k J (1,.+ IJoft.

V

Удвоение импульсов осуществляется блоком 24 по сигналу 78, разрешающему работу элемента И 29. Поэтому каждый входной импульс при наличии сигнала 79 запускает цепочку из двух последовательно соединенных формирователей 27 и 28. Импульс последнего из них проходит через элемент ИЛИ 30 на выход блока 24.

Получаемый промежуточный результа X, передается в ЦАП 8 через преобразователь 15 кодов, в котором сигнал 72 поступает на второй управляю- i

щий вход и разрешает работу элементов И 63, 64 значащих разрядов и элемента И 66 знакового разряда. В зависимости от 1 или О входного кода в знаковом разряде на выход через элементы И 65 передается соответственно прямой или инверсный код значащих разрядов, а также выходной единичный код в знаковом и дрполнитель- ном разрядах (соответственно с выходов элементов И 66, ИЛИ 67).

В ЦДЛ 8 выходной код преобразователя 15 кодов преобразуется в токовый сигнал I к, 2idXl5 который имеет отрицательную полярность (втекающий ток). Этот ток с помощью пе- теключателя 12 в зависимости от 1м или О в знаковом разряде преобразователя 15 подключается к суммирующему или вычитающему входу ПНЧ 7. К этому же входу через резистор переключателя 10 и 11 (в последнем по сиг налу 72) подается нулевое или входное напряжение.

За время Т с учетом удвоения в начале такта в течение Т с выхода ПНЧ 7 на вход счетчика 13 поступает

X ч импульсов VT

Хг 2k (1С+ 21ДХ,- Ix)Jt +

VT;

+ k

i«.

т.+т

+ 21ДХ,- Ix)oft.

В течение Тг счетчик 13 работает на вычитание, так как сигнал 72, ( проходя через элемент ИЛИ 22,включает этот режим. Поэтому к концу Та в нем остается число X .. X - Х„. По окон1 xiчании Т т. второй импульс 70 изменяет

0

5

5

5

5

0

0

0

5

в счетчике 45 код на 3 и на третьем выходе дешифратора 46 появляется сш нал 73 третьего такта работы Тэ. С выхода элемента ИЛИ 53 сигнал 76 снимается и выключается источник 9 смещения. Сигнал 73 в зависимости от знака Хп включает в работу элемент И 19 или 17, управляющий режимом вычитания в счетчике 13 или 14. Сигнал 73 поступает также на первый управляющий вход преобразователя 15, где он проходит через элементы ИЛИ 65 и 67, формируя 1 код во всех разрядах. Этот же сигнал разрешает работу элемента И 21, через который и через элемент ИЛИ 23 импульсы генератора 62 поступают на вход счетчика 14. В течение Т3 сигналы 71 и 72 отсутствуют и входы ПНЧ 7 через резисторы переключателей 10 и 11 подсоединены к нулевому напряжению. Поэтому преобразуется только один выходной токовый сигнал I К2 ЦДЛ 8, подключенный к вычитающему входу ПНЧ 7, так как на выходе элемента И 66 знакового разряда преобразователя 15 - О код.

Величина Ik/i образуется в результате преобразования ЦАП 8 выходного кода преобразователя 15, группа младших разрядов которого корректируется блоком 25 по коду m-n, сформированному счетчиком 31. В блоке 25 эта группа младших разрядов, старший из которых имеет вес т, поступает на входы элементов И 38. Вторые входы этих элементов через элементы ИЛИ 42 подсоединены к соответствующим О выходам разрядов счетчика 31. На вторые входы всех элементов ИЛИ 42 поступает сигнал 72, так что в течение Т 2 код с выхода преобразователя 15 в этих разрядах передается в ЦАП 8 без изменения. В течение Т блок 25 с помощью единичного кода во всех разрядах этой группы от преобразователя 15 формирует код с инверсным значением m-n, так как он снимается с О выходов счетчика 31. Этот код с учетом 1 в младшем дополнительном разряде, передаваемом от преобразователя 15 без коррекции, в ЦАП 8 преобразуется в компенсирующий ток

n - IM 2i4(N0- m + n) .

В результате преобразования Т К1 импульсы с выхода ПНЧ 7 поступают на вход счетчика 13 через элемент И 18, работу которого разрешает сигнал с выхода элемента ИЛИ 54. В счетчике 13 код Xfi компенсируется до нуля этими импульсами, и в этот момент элемент И 16 вырабатывает сигнал 75, по которому заканчивается Т3. Сигналы 75 и 73 разрешают работу элемента И 50, через который про- ходит импульс от формирователя 47 на счетный выход счетчика 45, устанавливая в нем О код. По этому коду дешифратор 46 формирует сигнал 74 готовности результата преобразования на шинах 6 и сигнал окончания преобразования, передаваемый на шину 5.

В случае Xf2 О сигнал 74 формируется сразу после окончания Т.

В течение Т 3 импульсы генератора 62 поступают через элемент И 21, открытый сигналом 73, и через элемент ИЛИ 23 на вход счетчика 14, где они изменяют код X1, увеличивая или уменьшая его в зависимости от знака X .

Число импульсов, поступающих за Т3 в счетчик 13, равно X п к-1ц4-Тэ k-2i(N0- m + n)T3 , а в счетчик 14 Хэ . В счетчике 14 формируется окончательный результат преобразова- ния

X Х,+ Х3 X,

X ,г

2ki/j(N0-m+n)t:/

При преобразовании входного сиг- 35 нала Ix(t) I0+ Vt (где V - скорость изменения входного сигнала) величина X fl X ,- X,; равна

т,-тт,

Xn k (Ic+I0+Vt)dt + 2k (Ic+40

DTVTТ,-Т

+I0+Vt)dt - 2k J (It+2i X1-I0-Vt)dt - TVT2т,

- k (Ie+2i/,X1-Ie-Vt)dt.

VT45

С учетом Т, T.i Т u (N0-m)td, Т , получим

Xfl 2k(I0-idXi+VTH)(N0-m+n)t0,

результат преобразования

1,-iiXt+VTM 1

д - ТД

50

+ i ikЈi±YTM 1 1 +ути)-х.,.

1л - LA

Полученный результат преобразования X представляет собой среднее значение входного сигнала Хср за фиксированное время измерения 2Тц. В этом

JQ 15

20 25

30

35

0

5

0

5

результате нет погрешностей, присущих прототипу и обусловленных изменением периода помехи от сети питания, а также необходимостью синхронизации выполнения тактов преобразования от сети питания для подавления помех. В предлагаемом АЦП преобразование начинается сразу по приходе сигнала запуска его в работу, т.е. без потерь времени на синхронизацию. В процессе преобразования при изменении частоты сети питания выполняется коррекция, благодаря которой гогрешнос- ти, вызываемые этим изменением и изменением входного сигнала за время измерения, полностью устраняются.

Формула изобретения

1. Аналого-цифровой преобразователь знакопеременных сигналов, содержащий первый и второй переключатели, первые информационные входы которых объединены и являются входной шиной, вторые информационные входы объединены, подключены к первому выходу цифроаналогового преобразователя и являются шиной нулевого напряжения, второй выход цифроаналогового преобразователя соединен с информационным входом третьего переключателя, первый выход которого объединен с выходом источника тока смещения и подключен к суммирующему входу преобразователя напряжения в частоту, вычитающий вход которого подключен к выходу второго и второму выходу третьего переключателей, управляющий вход источника тока смещения соединен с первым вы- ходом блока управления, первый вход которого является шиной запуска и объединен с входами установки нулевого кода первого и второго реверсивных счетчиков, единичные выходы разрядов последнего являются выходной шиной и соединены совместно с нулевыми выходами разрядов с соответствующими информационными входами преобра-г зователя кодов, выход знакового разряда которого соединен с управляющим входом третьего переключателя, выходы группы старших разрядов и дополнительного разряда - с соответствующими одноименными входами цифроаналогового преобразователя, при этом второй вход блока управления является шиной напряжения сети питания, второй вы- .ход - шиной сигнала окончания преобразования, третий выход соединен с первыми входами первого, второго и третьего элементов И и первым управляющим входом преобразователя кодов, четвертый выход - с управляющим входом первого переключателя и первым входом четвертого элемента И, выход которого соединен с первым входом первого элемента ИЛИ, второй вход ко торого подключен к выходу первого элемента И, второй вход которого соединен с пятым выходом блока управления, шестой выход которого соединен с управляющим входом второго пе- реключателя, с вторым управляющим входом преобразователя кодов и первым входом второго элемента ИЛИ, второй вход которого соединен с выходом второго элемента И, второй вход которо- го объединен с первым входом пятого элемента И и подключен к нулевому выходу знакового разряда второго реверсивного счетчика, вход управления вычитанием которого соединен с выхо- дом второго элемента ИЛИ, а выходы нулевых разрядов, кроме знакового - с остальными входами пятого элемента И, выход которого соединен с третим входом блока управления, выход первого элемента ИЛИ соединен со счетным входом первого реверсивного счетчика, вход управления вычитанием которого соединен с выходом третьего элемента И, второй вход которого соединен с единичным выходом знакового разряда второго реверсивного счетчика,-шестой элемент И, первый вход которого объединен с вторым входом четвертого элемента И, второй вход подключен к седьмому выходу блока управления, а выход соединен со счетным входом второго реверсивного счетчика, отличающийся тем, что, с целью повышения точности преобразования, в него введены блок удвоения числа импульсов и блок коррекции, первый вход которого соедине с пятым выходом блока управления, восьмой выход и группа выходов кото- рого подключены соответственно к второму входу и первой группе входов блока коррекции, вторая группа входов которого подключена соответственно к группе входов младших разрядов преобразователя кодов, а группа выходов соединена с входами соответствующих младших разрядов цифроаналого вого преобразователя, третий и четвертый входы блока коррекции подключены соответственно к четвертому и шестому выходам блока управления, пятый вход является шиной запуска, а выход соединен с управляющим входом блока удвоения числа импульсов, информационный вход которого соединен с выходом преобразователя напряжения в частоту, а выход - с первым входом шестого элемента И.

2.Преобразователь по п.1, о т - личающийся тем, что блок удвоения числа импульсов выполнен на элементах И, ИЛИ и двух формирователях импульсов, вход первого из которых соединен с выходом элемента И, а выход через второй формировател импульсов подключен к первому входу элемента ИЛИ, выход которого является выходом блока, а второй вход является информационным входом блока и объединен с первым входом элемента

И, второй вход которого является управляющим входом.

3.Преобразователь по п. 1, отличающийся тем, что блок коррекции выполнен на реверсивном счетчике, триггере, одновибраторе, формирователе импульсов, счетчике, группе элементов ИЛИ, группе элементов И, элементах И, ИЛИ, причем информационные входы реверсивного счетчика являются первой группой входов блока, нулевые выходы разрядов соединены с соответствующими входами первого элемента И, выход которого соединен со счетным входом триггера, вход управления вычитанием реверсивного счетчика является третьим входо блока и объединен с первым входом первого элемента ИЛИ, второй вход которого подключен к выходу триггера и является выходом блока, вход записи реверсивного счетчика соединен

с выходом второго элемента ИЛИ, а вход установки нулевого кода является пятым входом блока и объединен с входом формирователя импульсов, входом сброса триггера и входом установки нулевого кода счетчика, счетный вход которого объединей со счетным входом реверсивного счетчика и подключен к выходу второго элемента И, первый вход которого является первым входом блока, а второй вход соединен с выходом первого элемента ИЛИ второй группой входов блока являются

первые входы группы элементов И, вторые входы которых соединены с соответствующими выходами группы элементов ИЛИ, первые входы которых объединены и являются четвертым входом блока, а вторые входы подключены к нулевым выходам разрядов счетчика, выходы группы элементов И являются группой выходов блока, вторым входом которого является первый вход третьего элемента И, второй вход которого объединен с первым входом второго элемента ИЛИ и подключен к выходу формирователя импульсов, второй вход второго элемента ИЛИ соединен через одновибратор с выходом третьего элемента И.

4. Преобразователь по п. 1, о т- личающийся тем, что блок управления выполнен на трех счетчиках, четырех формирователях импульсов, одновибраторе,дешифраторе, за- датчике кода, генераторе импульсов, регистре, элементах И, ИЛИ, причем входы установки нулевого кода первого и второго счетчиков объединены с первым входом первого элемента ИЛИ и являются первым входом блока, вто- рой вход которого через первый формирователь импульсов соединен с первыми входами второго элемента ИЛИ и первого элемента И, второй вход которого объединен со счетным входом третьего счетчика, входом второго формирователя импульсов и первым входом второго элемента И, является пятым выходом блока и подключен к выходу генератора импульсов, второй вход второго элемента И объединен с первым входом третьего элемента ИЛИ, подключен к выходу четвертого элемента ИЛИ и является первым выходом

блока, третьим входом которого является первый вход третьего элемента И, второй вход которого соединен с выходом второго формирователя импульсов, выход - с первым входом пятого элемента ИЛИ, выход которого подключен к счетному входу второго счетчика, выходы которого подключены к соответствующим входам дешифратора, первый и второй выходы которого соединены соответственно с первым и вторым входами четвертого элемента ИЛИ и являются соответственно четвертым и шестым выходами блока, третьим выходом которого является третий выход дешифратора, подключенный к второму входу третьего элемента ИЛИ и третьему входу второго элемента И, четвертый выход дешифратора является вторым выходом блока, седьмым выходом которого является выход третьего элемента ИЛИ, выход переполнения первого счетчика соединен с вторым входом первого элемента ИЛИ, выход которого через третий формирователь импульсов подключен к второму входу пятого элемента ИЛИ и входу записи кода первого счетчика, информационные входы которого соединены с соответствующими выходами задатчика кода, а выход первого элемента И через одновибратор соединен с вторым входом второго элемента ИЛИ, выход которого является восьмым выходом блока, и к входу записи кода регистра непосредственно, а к входу установки нулевого кода третьего счетчика - через четвертый формирователь импульсов, выходы счетчика соединены с соответствующими входами регистра, выходы которого являются группой выходов блока, выход второго элемента И соединен со счетным входом первого счетчика.

Фиг. 5

| название | год | авторы | номер документа |

|---|---|---|---|

| Аналого-цифровой частотный преобразователь | 1986 |

|

SU1359911A1 |

| Цифровой многоточечный измерительный мост | 1980 |

|

SU938164A1 |

| Способ аналого-цифрового преобразования и устройство для его осуществления | 1990 |

|

SU1837395A1 |

| Аналого-цифровой преобразователь с промежуточным преобразованием напряжения в частоту импульсов | 1985 |

|

SU1305856A1 |

| Аналого-цифровой преобразователь с частотным преобразованием | 1990 |

|

SU1725396A1 |

| Аналого-цифровой преобразователь | 1988 |

|

SU1504789A1 |

| Аналого-цифровой преобразователь | 1984 |

|

SU1229958A1 |

| Аналого-цифровой преобразователь с преобразованием напряжения в частоту | 1989 |

|

SU1651381A1 |

| Аналого-цифровой преобразователь | 1990 |

|

SU1730722A2 |

| АНАЛОГО-ЦИФРОВОЙ ПРЕОБРАЗОВАТЕЛЬ С ПРОМЕЖУТОЧНЫМ ПРЕОБРАЗОВАНИЕМ В ЧАСТОТУ | 1990 |

|

RU2007029C1 |

Изобретение относится к импульсной технике , в частности к преобразователям напряжения в цифровой код с промежуточным преобразованием напряжения в частоту импульсов, и может быть использовано в прецизионных устройствах сбора аналоговой информации систем контроля и управления технологическими процессами. Целью изобретения является повышение точности преобразования за счет исключения влияния на результат преобразования погрешностей. АЦП содержит преобразователь напряжения в частоту с входными переключателями, два реверсивных счетчика, цифроаналоговый преобразователь, источник смещения, логические элементы, преобразователь кодов и блок управления. Новым является измерение полупериода напряжения помехи и введение блоков удвоения импульсов и коррекции, благодаря которым в АЦП выполняется коррекция, исключающая влияние на результат преобразования изменения частоты помехи и сигнала во время преобразования. 3 з.п. ф-лы, 6 ил.

| Прянишников В.А | |||

| Интегрирующие цифровые вольтметры постоянного тока, 1976, с | |||

| Зубчатое колесо со сменным зубчатым ободом | 1922 |

|

SU43A1 |

| Аналого-цифровой преобразователь знакопеременных напряжений | 1984 |

|

SU1205307A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1989-05-30—Публикация

1987-09-29—Подача