Изобретение относится к электрО связи и может быть использовано в системах передачи информации для защиты от ошибок.

Цель изобретения - повышение достоверности передаваемых сообщений и упрощение структуры устройства.

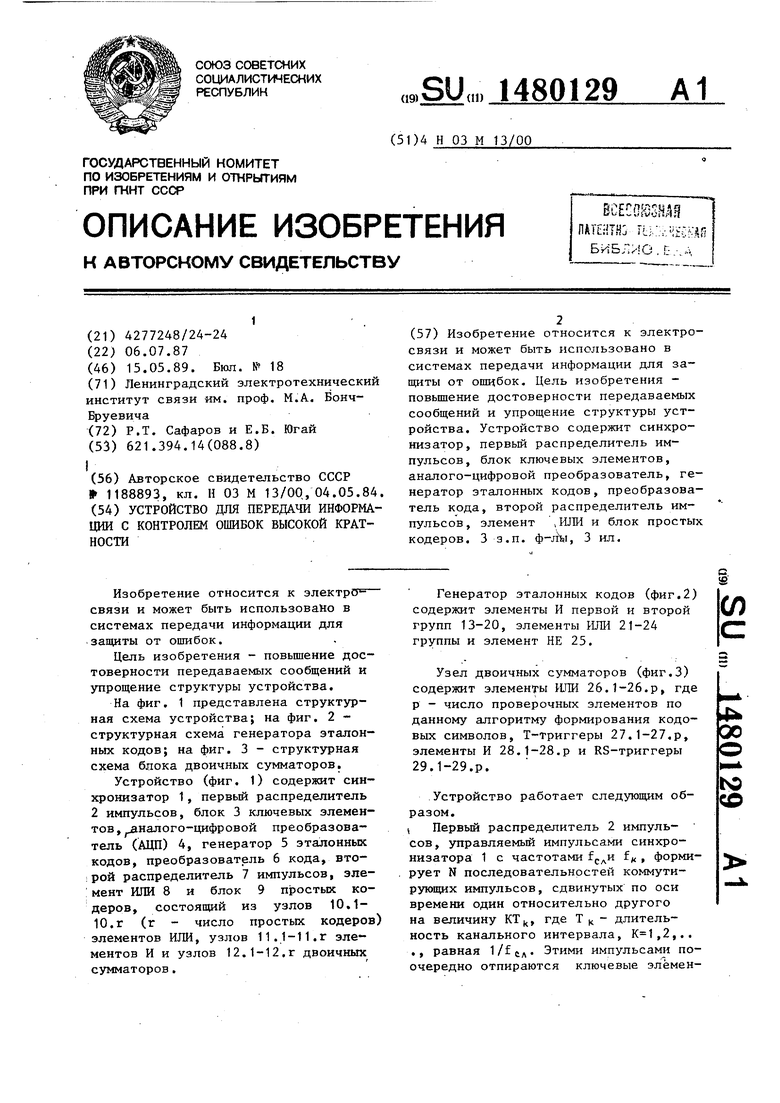

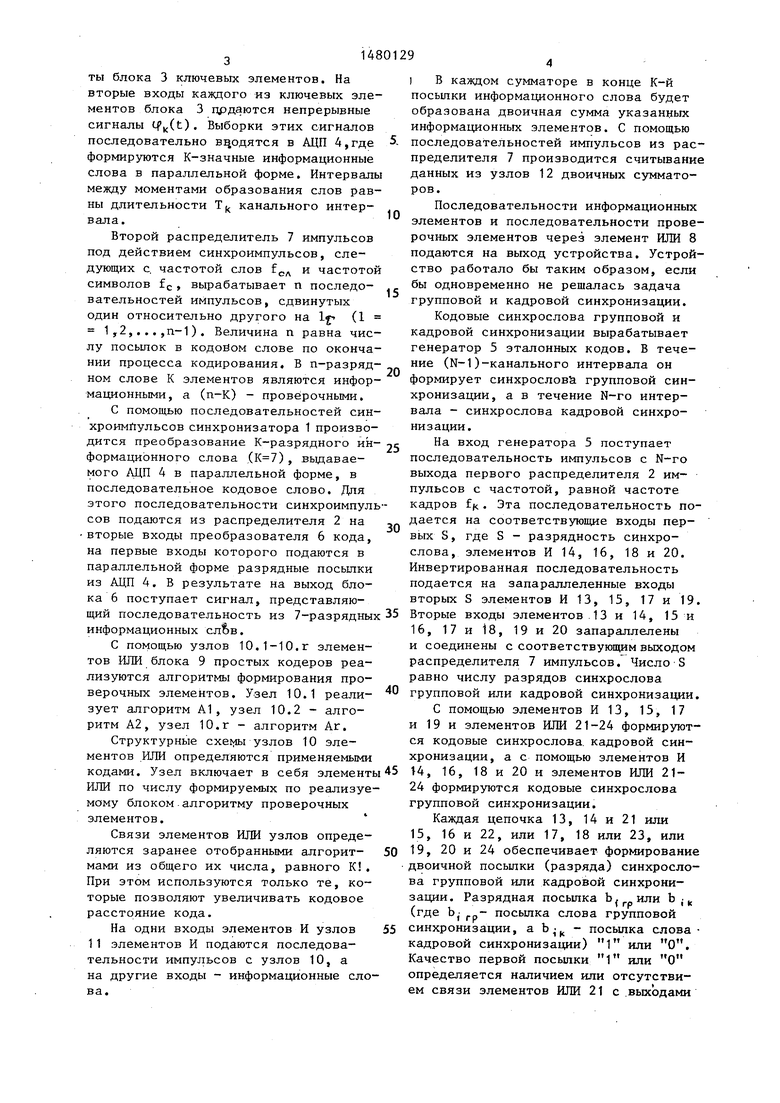

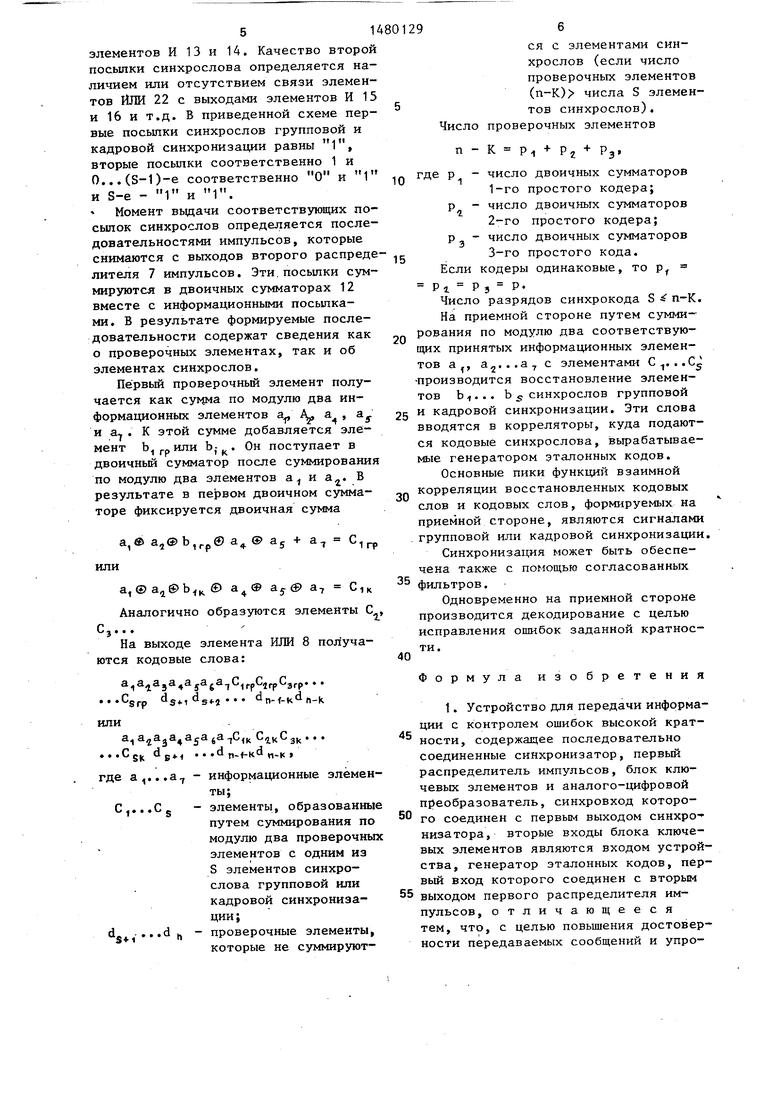

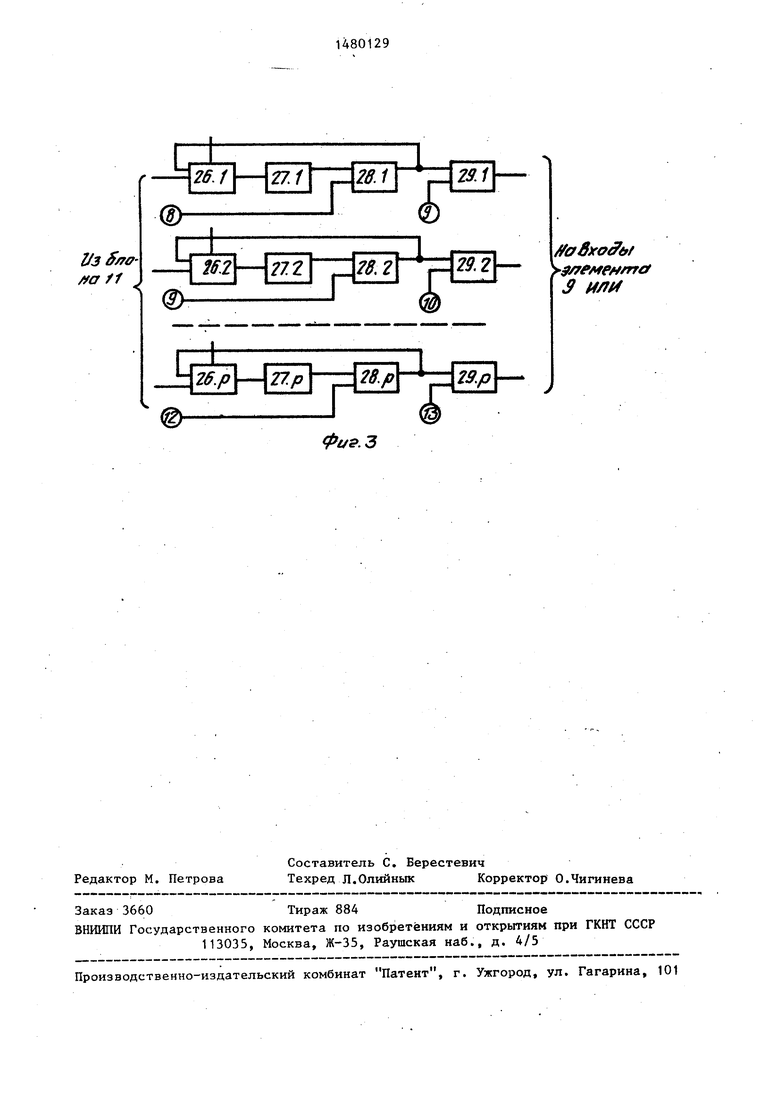

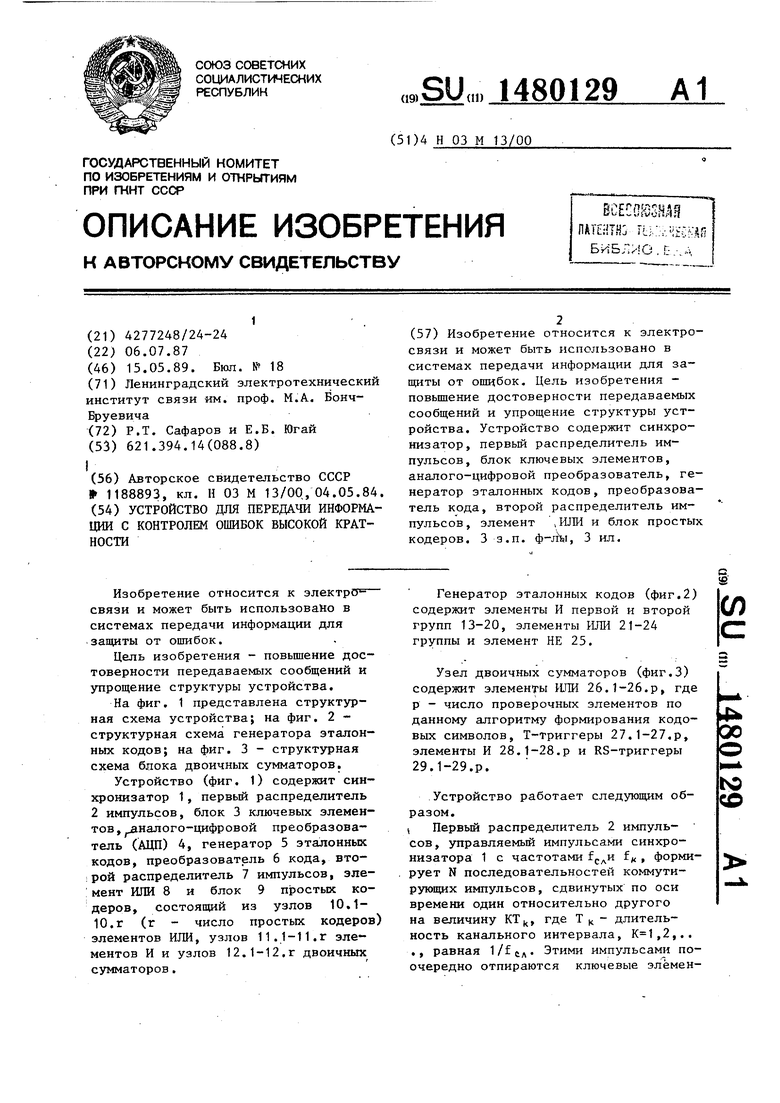

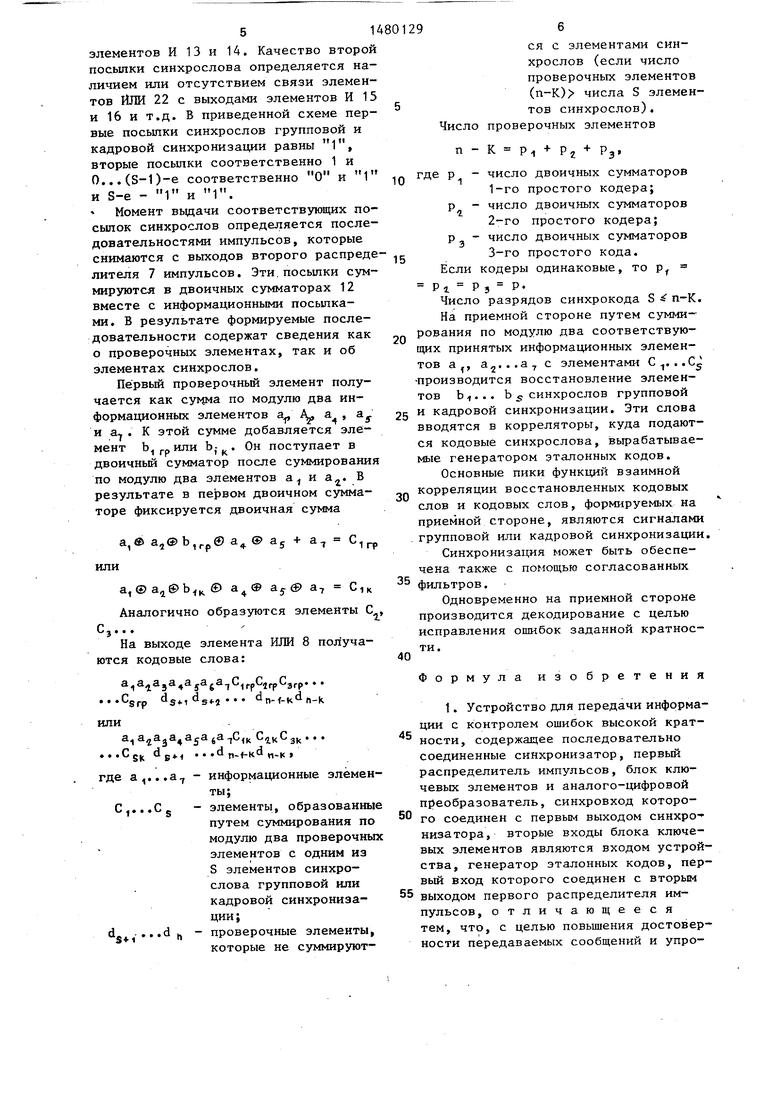

На фиг. 1 представлена структурная схема устройства; на фиг. 2 - структурная схема генератора эталонных кодов; на фиг. 3 - структурная схема блока двоичных сумматоров.

Устройство (фиг. 1) содержит синхронизатор 1, первый распределитель 2 импульсов, блок 3 ключевых элементов, аналого-цифровой преобразователь (АЦП) 4, генератор 5 эталонных кодов, преобразователь 6 кода, второй распределитель 7 импульсов, элемент ИЛИ 8 и блок 9 простых кодеров, состоящий из узлов 10.1- 10.г (г - число простых кодеров) элементов ИЛИ, узлов 11.1-11.г элементов И и узлов 12.1-12.г двоичных сумматоров.

Генератор эталонных кодов (фиг.2) содержит элементы И первой и второй групп 13-20, элементы ИЛИ 21-24 группы и элемент НЕ 25.

Узел двоичных сумматоров (фиг.З) содержит элементы ИЛИ 26.1-26.р, где р - число проверочных элементов по данному алгоритму формирования кодовых символов, Т-триггеры 27.1-27.р, элементы И 28.1-28.р и RS-триггеры 29.1-29.р.

Устройство работает следующим образом.

i Первый распределитель 2 импуль- сов, управляемый импульсами синхронизатора 1 с частотами ЈСли f«, формирует N последовательностей коммутирующих импульсов, сдвинутых по оси времени один относительно другого на величину KTk, где Тк - длительность канального интервала, ,2,.. ., равная 1/f ед. Этими импульсами поочередно отпираются ключевые элёменс 58

(Л

ь

00

1C

СО

10

15

20

ты блока 3 ключевых элементов. На вторые входы каждого из ключевых элементов блока 3 додаются непрерывные сигналы Ч х(ь). Выборки этих сигналов последовательно вводятся в АЦП 4,где формируются К-значные информационные слова в параллельной форме. Интервалы между моментами образования слов равны длительности Tk канального интервала.

Второй распределитель 7 импульсов под действием синхроимпульсов, следующих с частотой слов fCA и частотой символов fс, вырабатывает п последовательностей импульсов, сдвинутых один относительно другого на 1р (1 1 ,2,...,п-1). Величина п равна числу посылок в кодобом слове по окончании процесса кодирования. В п-разряд- ном слове К элементов являются информационными, а (п-К) - проверочными.

С помощью последовательностей синхроимпульсов синхронизатора 1 производится преобразование К-разрядного ин- 25 формационного слова (), выдаваемого АЦП 4 в параллельной форме, в последовательное кодовое слово. Для этого последовательности синхроимпульсов подаются из распределителя 2 на вторые входы преобразователя 6 кода, на первые входы которого подаются в параллельной форме разрядные посыпки из АЦП 4. В результате на выход блока 6 поступает сигнал, представляющийинформационных слов.

С помощью узлов 10.1-10.г элементов ИЛИ блока 9 простых кодеров реализуются алгоритмы формирования проверочных элементов. Узел 10.1 реализует алгоритм А1, узел 10.2 - алгоритм А2, узел 10.г - алгоритм Аг.

Структурные схемы узлов 10 элементов ИЛИ определяются применяемыми

1 В каждом сумматоре в конце К-й посылки информационного слова будет образована двоичная сумма указанных информационных элементов. С помощью 5. последовательностей импульсов из распределителя 7 производится считывание данных из узлов 12 двоичных сумматоров.

Последовательности информационных элементов и последовательности проверочных элементов через элемент ИЛИ 8 подаются на выход устройства. Устройство работало бы таким образом, если бы одновременно не решалась задача групповой и кадровой синхронизации.

Кодовые синхрослова групповой и кадровой синхронизации вырабатывает генератор 5 эталонных кодов. В течение (N-1)-канального интервала он формирует синхрослова групповой синхронизации, а в течение N-го интервала - синхрослова кадровой синхронизации.

На вход генератора 5 поступает последовательность импульсов с N-ro выхода первого распределителя 2 импульсов с частотой, равной частоте кадров f«. Эта последовательность подается на соответствующие входы первых S, где S - разрядность синхрослова, элементов И 14, 16, 18 и 20. Инвертированная последовательность подается на запараллелейные входы вторых S элементов И 13, 15, 17 и 19.

последовательность из 7-разрядных35 Вторые входы элементов 13 и 14, 15 и

16, 17 и 18, 19 и 20 запараллелены и соединены с соответствующим выходом распределителя 7 импульсов. Число S равно числу разрядов синхрослова групповой или кадровой синхронизации.

С помощью элементов И 13, 15, 17 и 19 и элементов ИЛИ 21-24 формируются кодовые синхрослова кадровой синхронизации, а с помощью элементов И

30

40

кодами. Узел включает в себя элементы 45 14, 16, 18 и 20 и элементов ИЛИ 21ИЛИ по числу формируемых по реализуемому блоком алгоритму проверочных элементов.

Связи элементов ИЛИ узлов определяются заранее отобранными алгоритмами из общего их числа, равного К. При этом используются только те, которые позволяют увеличивать кодовое расстояние кода.

На одни входы элементов И узлов 11 элементов И подаются последовательности импульсов с узлов 10, а на другие входы - информационные слова.

24 формируются кодовые синхрослова групповой синхронизации.

Каждая цепочка 13, 14 и 21 или 15, 16 и 22, или 17, 18 или 23, или

19, 20 и 24 обеспечивает формирование двоичной посылки (разряда) синхрослова групповой или кадровой синхронизации. Разрядная посылка Ь( или Ъ (. „ (где bf - посылка слова групповой

синхронизации, а - посыпка слова- кадровой синхронизации) 1 или О. Качество первой посылки 1 или О определяется наличием или отсутствием связи элементов ИЛИ 21 с выходами

51

элементов И 13 и 14. Качество второй посыпки синхрослова определяется наличием или отсутствием связи элементов ИЛИ 22 с выходами элементов И 15 и 16 и т.д. В приведенной схеме первые посыпки синхрослов групповой и кадровой синхронизации равны 1, вторые посылки соответственно 1 и 0...(S-1)-e соответственно О и 1 и S-e - 1 и 1.

Момент выдачи соответствующих посылок синхрослов определяется последовательностями импульсов, которые снимаются с выходов второго распреде лителя 7 импульсов. Эти посылки суммируются в двоичных сумматорах 12 вместе с информационными посыпками. В результате формируемые последовательности содержат сведения как о проверочных элементах, так и об элементах синхрослов.

Первый проверочный элемент получается как сумма по модулю два информационных элементов а, Ар а , af

и а. К этой сумме добавляется элемент Ь1Грили Ь-к. Он поступает в двоичный сумматор после суммирования по модулю два элементов а1 и а„. В результате в первом двоичном сумматоре фиксируется двоичная сумма

а,® а7©Ь1Гр© а5 + а., С1гр

или

а, © . € а4© ау ® а-, С1к

Аналогично образуются элементы С С,...

На выходе элемента ИЛИ 8 получаются кодовые слова:

ся с элементами синхрослов (если число проверочных элементов (п-К) числа S элементов синхрослов). проверочных элементов

К р1 + р2 + р ,

где р - число двоичных сумматоров

1-го простого кодера; р - число двоичных сумматоров

2-го простого кодера; р 3 - число двоичных сумматоров

3-го простого кода. Если кодеры одинаковые, то pf

PI Р э Р

Число разрядов синхрокода S п-К.

На приемной стороне путем суммирования по модулю два соответствующих принятых информационных элементов af, аг...а7 с элементами С1. ..С производится восстановление элементов b.,. .. b s синхрослов групповой и кадровой синхронизации. Эти слова вводятся в корреляторы, куда подаются кодовые синхрослова, вырабатываемые генератором эталонных кодов.

Основные пики функций взаимной корреляции восстановленных кодовых слов и кодовых слов, формируемых на приемной стороне, являются сигналами групповой или кадровой синхронизации.

Синхронизация может быть обеспечена также с помощью согласованных фильтров.

Одновременно на приемной стороне производится декодирование с целью исправления ошибок заданной кратности.

Изобретение относится к области электросвязи и может использоваться в системах передачи информации для защиты от ошибок. Цель изобретения - повышение достоверности передаваемых сообщений и упрощение структуры устройства. Устройство содержит синхронизатор, первый распределитель импульсов, блок ключевых элементов, аналого-цифровой преобразователь, генератор эталонных кодов, преобразователь кода, второй распределитель импульсов, элемент ИЛИ и блок простых кодеров. 3 з.п. ф-лы, 3 ил.

L

aialaSa4a5atai irp lrp - 3rp

srp

dn-f-kdn-K

ИЛИ

aia«a3a«a5a a Ј

. ,CSK d B44 де a 1...a 7

t i . - e

к C1KC3(C .

d n-f-K i H-K

информационные элементы;

элементы, образованные путем суммирования по модулю два проверочных элементов с одним из S элементов синхрослова групповой или кадровой синхронизации;

проверочные элементы, которые не суммируют5

0

5

Формула изобретения

0

5

0

5

0

5

0

5

являются первым входом генератора эталонных кодов, вторые входы одноименных элементов И обеих групп со- s ответственно объединены и являются вторыми входами генератора эталонных кодов, выходы элементов ИЛИ- являются выходами генератора эталонных кодов.

с соответствующими третьими входами одноименных узлов двоичных сумматоров, выходы которых являются выходами блока простых кодеров, входы узлов элементов ИЛИ являются третьими входами блока двоичных сумматоров.

©-M 25 A

0фиеЛ

22

фаг.2

й

Tj-|БТ| ЖТрр ш -

Уз faff- #а f1 .

Фиг.З

#o6xo&t t &7еме тс( S ИМ

Авторы

Даты

1989-05-15—Публикация

1987-07-06—Подача