Изобретение относится к электросвязи и может быть использовано в те- . леметрии и при передаче данных.

Цель изобретения - повышение быстродействия системы путем сокращения избыточности кода и повышение надежности системы путем упрощения ее структуры.

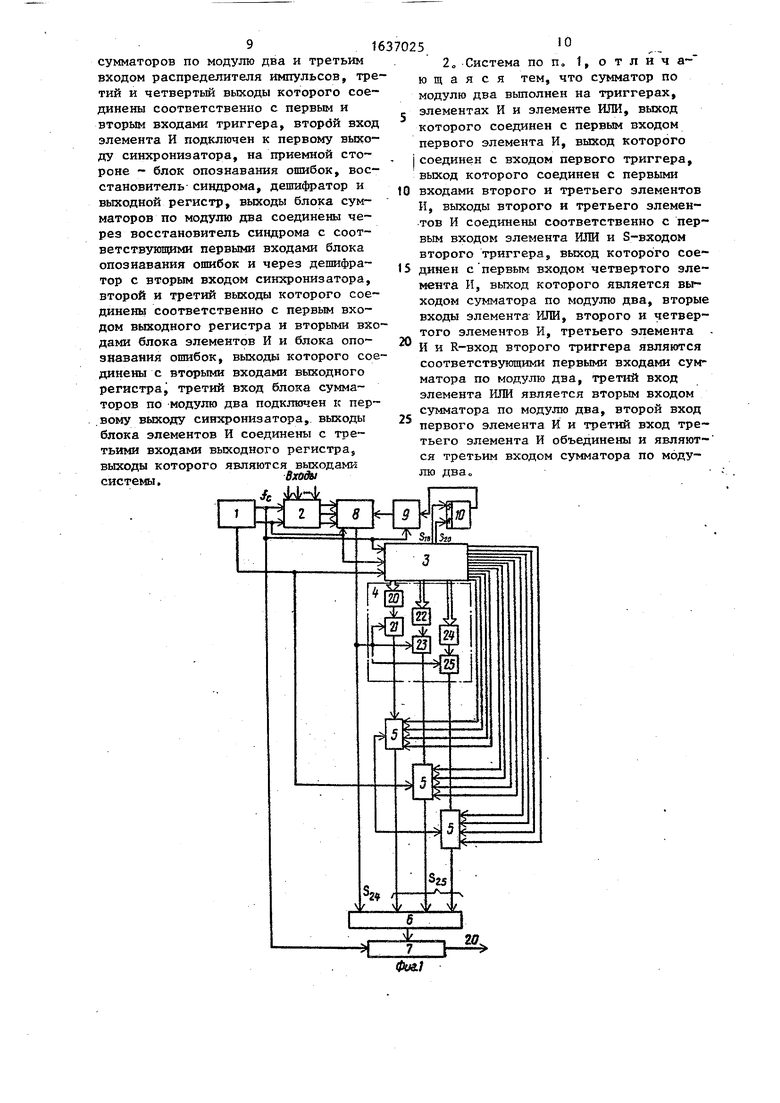

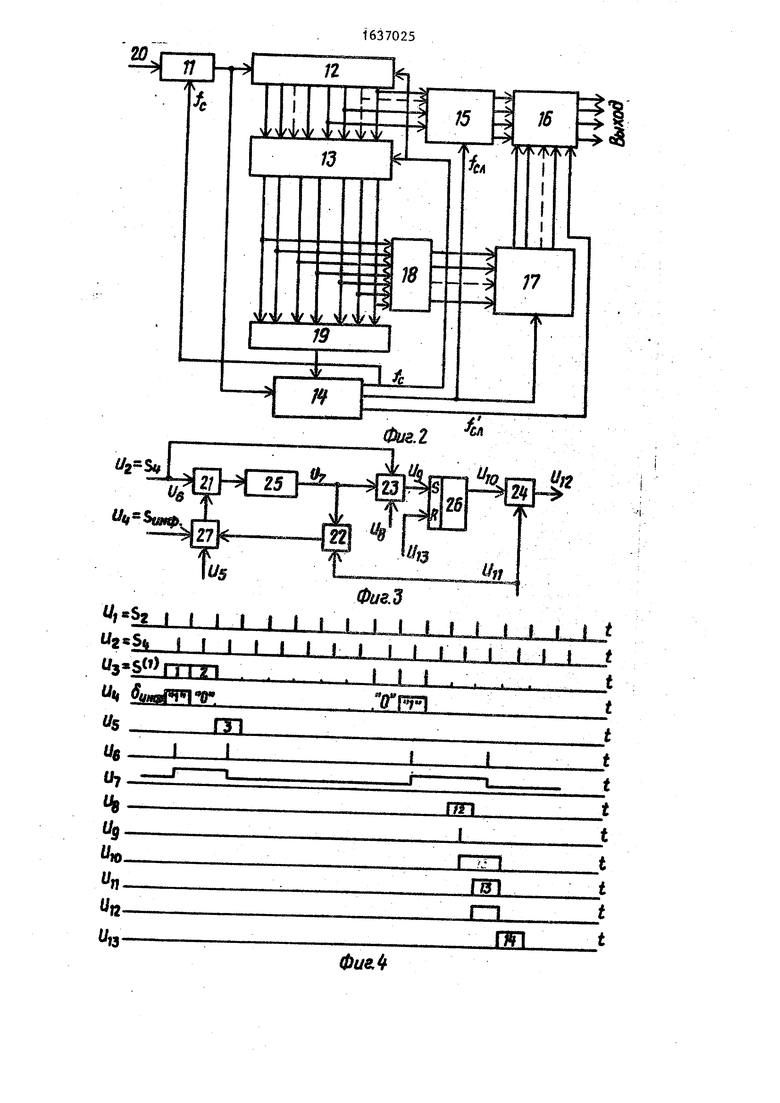

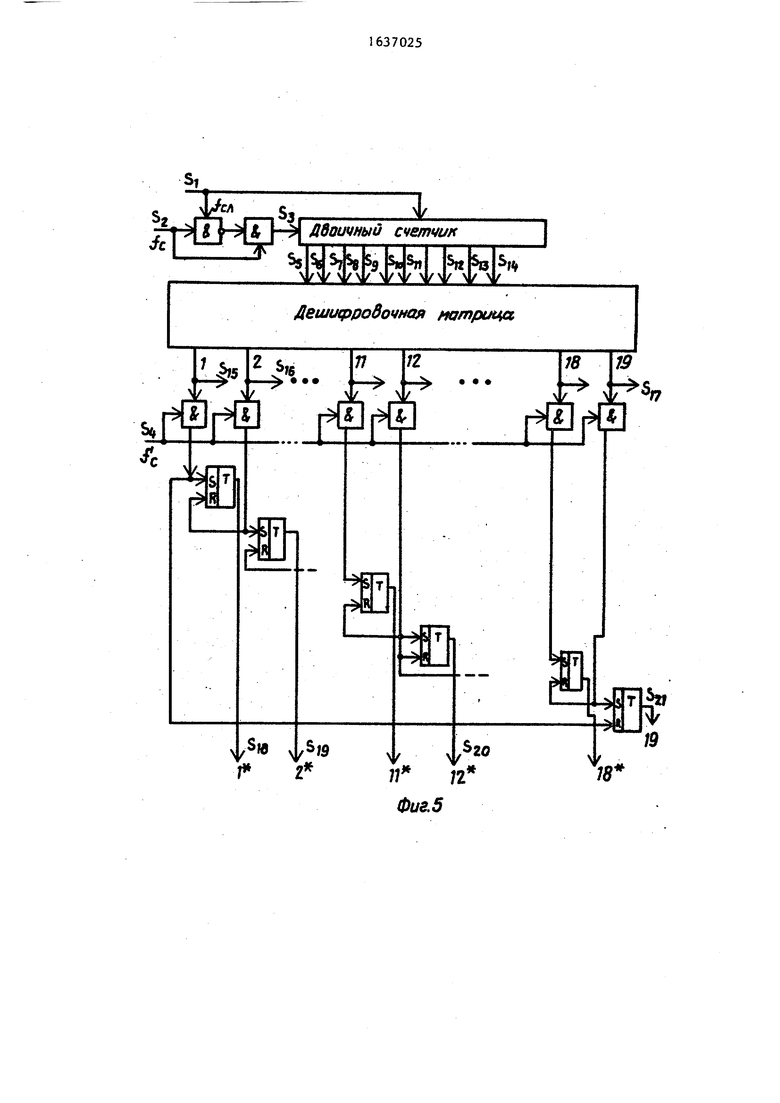

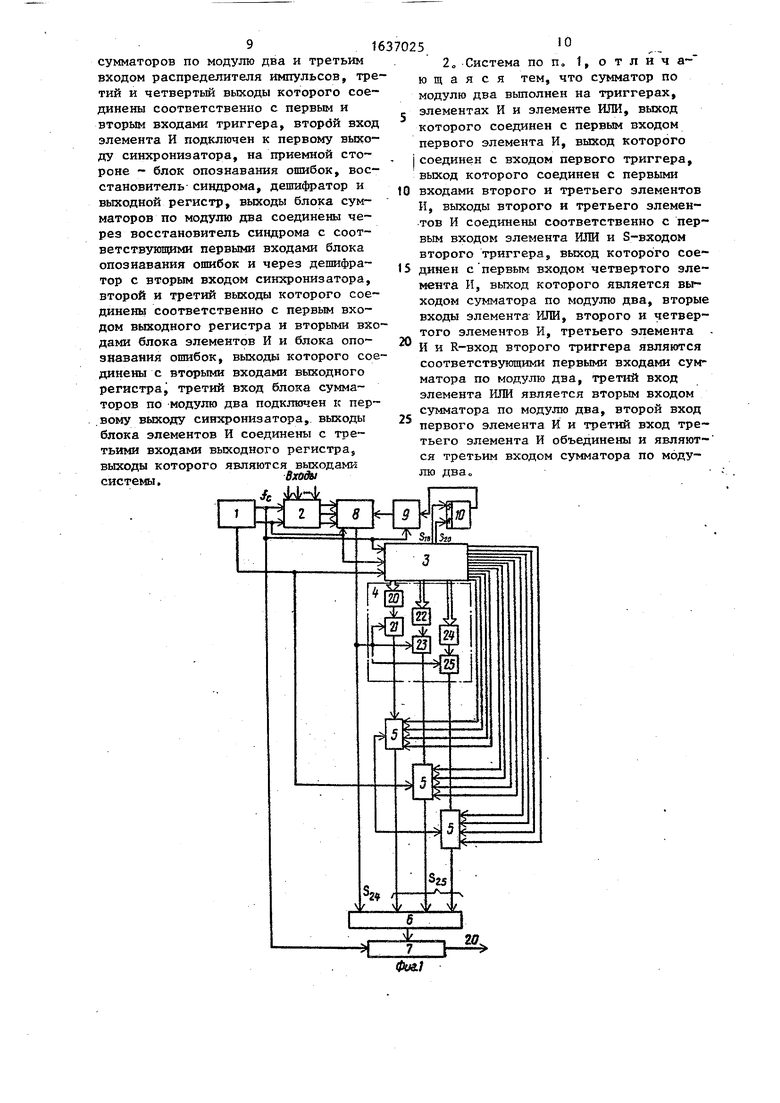

На фит. 1 приведена структурная схема передающей стороны системы; на фиг. 2 - структурная схема приемной стороны системы; на фиг. 3 - структурная схема сумматора по модулю два редающей стороны системы; на фиг,4 - временны диаграммы сигналов в этом

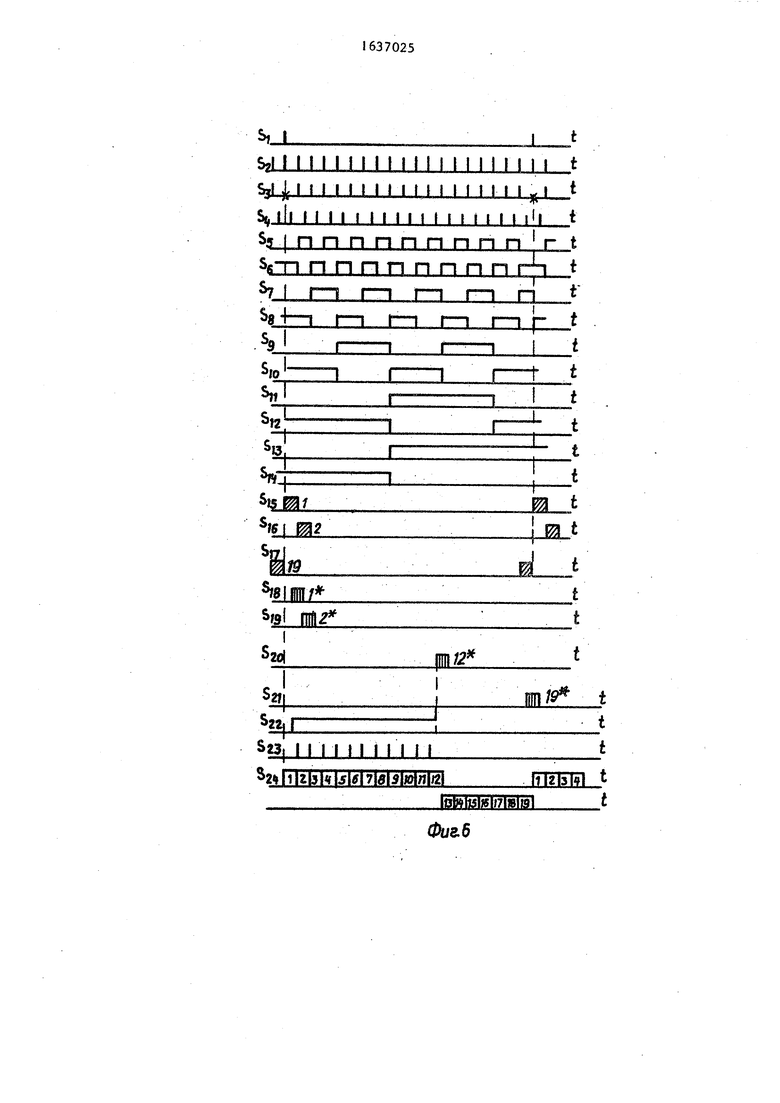

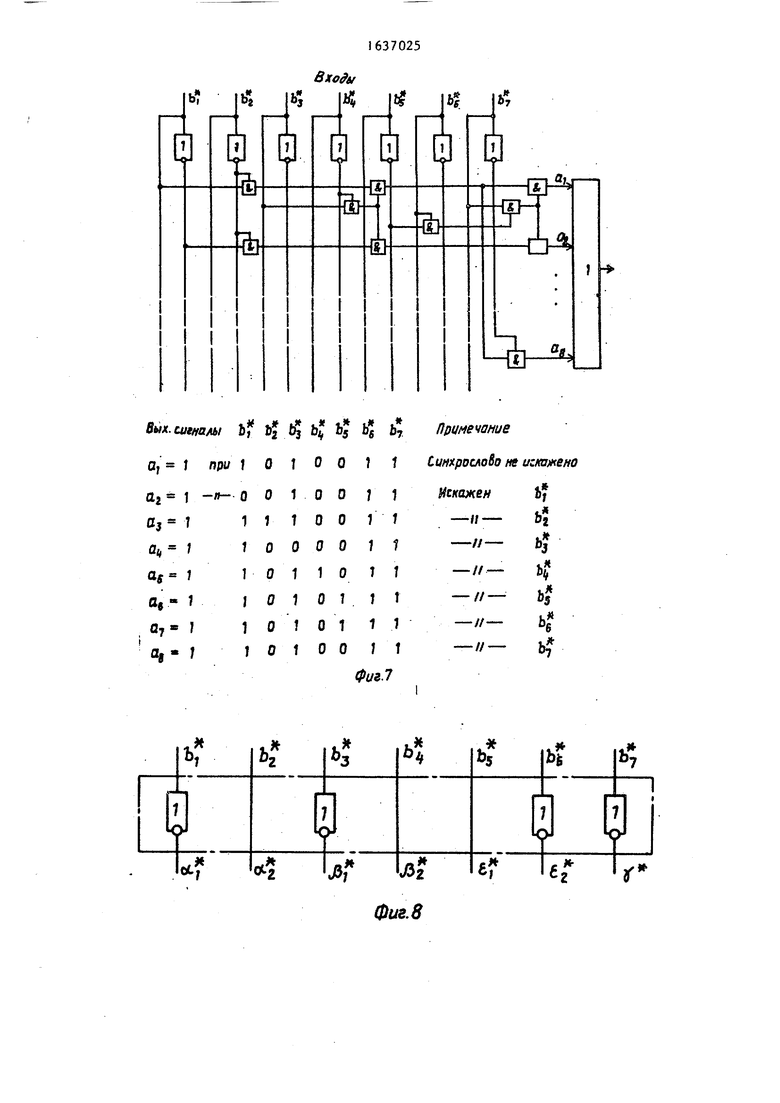

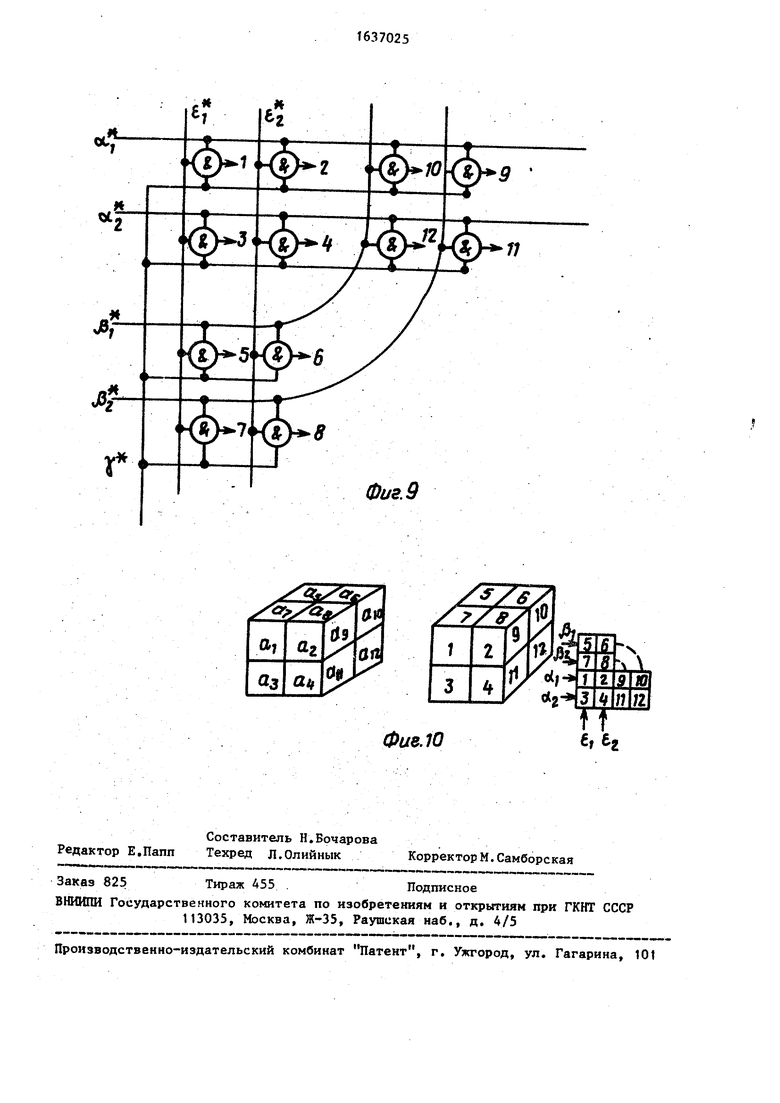

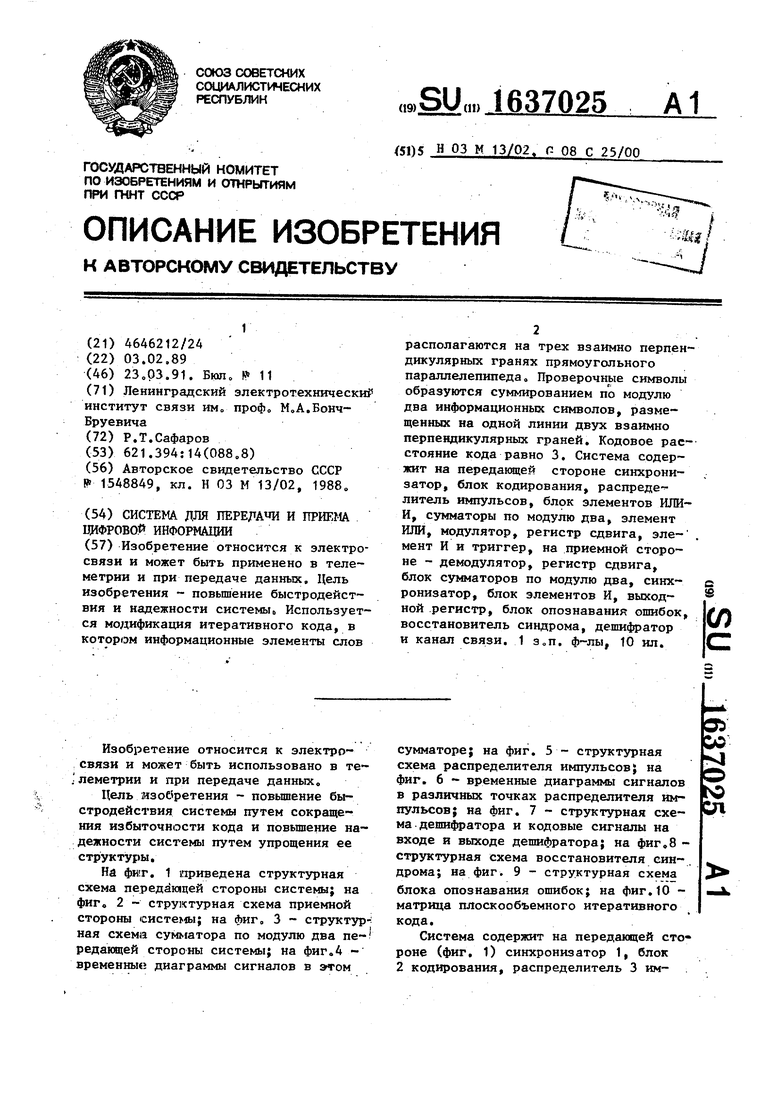

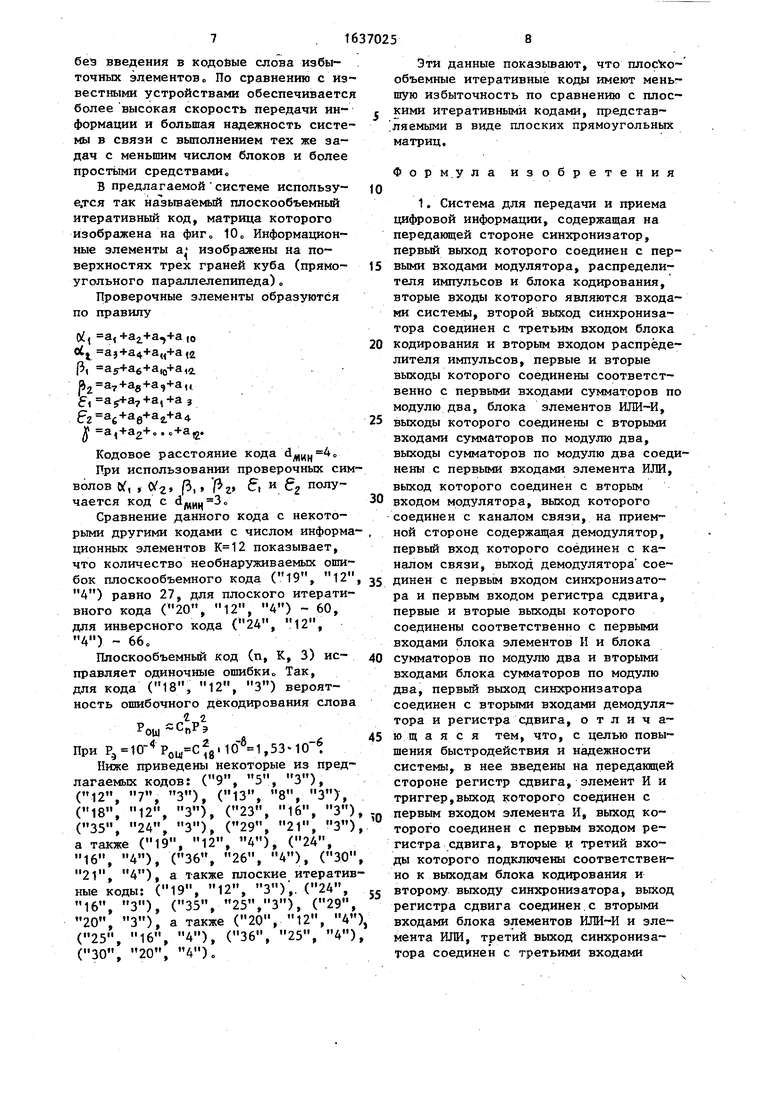

сумматоре; на фиг. 5 - структурная схема распределителя импульсов; на фиг. 6 - временные диаграммы сигналов в различных точках распределителя импульсов; на фиг. 7 - структурная схема дешифратора и кодовые сигналы на входе и выходе дешифратора; на фиг.8 - структурная схема восстановителя син-. дрома; на фиг. 9 - структурная схема блока опознавания ошибок; на фиг.10 - матрица плоскообъемного итеративного кода.

Система содержит на передающей стороне (фиг. 1) синхронизатор 1, блок 2 кодирования, распределитель 3 импульсов, блок 4 элементов ИЛИ-И, сумматоры 5 по модулю два по числу проверочных элементов кода, элемент 6 ИЛИ, модулятор 7, регистр 8 сдвига, элемент И 9„ триггер 10, на приемной стороне (фиг. 2) - демодулятор 11, регистр 12 сдвига, блок 13 сумматоров по модулю два, синхронизатор 14, блок 15 элементов И, выходной регистр 16, блок 17 опознавания ошибок, восстановитель 18 синдрома, дешифратор 19, канал 20 связи. Сумматор 5 по модулю два содержит (фиг. 3) первый-четвертый элементы И 21-24, первый и второй триггеры 25 и 26, элемент ИЛИ 27.

Система для передачи и приема цифровой информации работает следующим образом

Блок 2 кодирования преобразует дискретные входные сигналы (сообщения) в К-разрядные слова двоичного кода. Кодовые слова считываются в моменты времени, определяемые импульсами синхронизатора 1, частота следования которых fCA fc/19. Кодовые слова в эти моменты времени вводятся в регистр 8 сдвига, из которого они считаются импульсами, следующими с частотой f., которые пачками поступают с выхода элемента И 9 (фиг. 1 и 6, сигнал Sg). Кодовое К разрядное слово в последовательной форме (фиго 6, сигнал 82ф) поступает на входы блока 4 элементов ИЛИ-И и элемента ИЛИ 6

Распределитель 3 импульсов, управляемый сигналами S , S и S 5 (фиг о 6), поступающими из синхронизатора 1, вырабатывает различные коммутирующие и управляющие сигналы (Аиг. 6, сигналы S,Ј,...,847 S|g,...,S2).

В соответствии с алгоритмом образования проверочных элементов эти сигналы подаются на входы блока 4 элементов ИЛИ-И. Например, для предлагаемого плоско-объемного итеративного кода на вход первого элемента ИЛИ-И поступают сигналы, соответствующие позициям 1, 2, 9 и 10 кодового слова, на вход второго элемента - сигналы, соответствующие по- зициям 3, 4, 11 и 12, на вход третьего элемента - сигналы, соответствующие позициям 3, 1, 7 и 5, на вход четвертого элемента - сигналы с номерами 4, 2, 8 и 6

0

5

0

5

0

5

0

5

0

5

на вход пятого - сигналы с номерами 5, 6, 10 и 12, на вход шестого - сигналы с номерами 7, 8, 9 и 11, а на вход седьмого элемента ИЛИ-И - коммутирующие сигналы, соответствующие позициям 1, 2,..,, 12 кодового слова

На выходе первого элемента ИЛИ-И будут , , и элементы информационной части кодового словао При этом символам 1 будут соответствовать сигналы высокого уровня длительностью равной С (Ј- длительность элемента кодового слова)с На выходе последнего элемента ИЛИ-И будет последовательность сигналов высокого уровня (символы 1) и низкого уровня (символы О)„ Эти сигналы подаются на входы соответствующих сумматоров 5 по модулю два Каждый сумматор имеет шесть входов. На вход поступают импульсы с частотой fe (фиг. 4, сигнал U или сигнал S, фиг. 6), сдвинутые относительно основной последовательности импульсов той же частоты (сигнал U) На второй вход подается указанная выше последовательность U4 , (фиг о 4) информационных элементов, определяемая алгоритмом образования проверочных символов кодового слова,, На третий вход подается (или не подается) сигнал типа U g- (фиг. 4) в течение интервала времени, не совпадающего с поступлением информационных посылок, Сигнал типа Ug- присутствует, если соответствующий элемент синхрослова, используемого для групповой синхронизации, равен 1 „Если этот символ равен нулю, то сигнала типа Ug- нет (вход сигнала отсутствует). На четвертый вход сумматора подается сигнал Uц (фиг„ 4), на пятый вход - сигнал Ug, на шестой вход - сигнал U (3 . Если сумма по модулю два информационных элементов, поступающих на вход U4. с добавлением сигнала U равна 1, то Т триггер 25 находится в состоянии Если сумма равна нулю, то триггер 25 находится в состоянии О о

Сигнал Uj служит для считывания состояния Т-триггера 25 и записи этой информации (О или 1) в RS-триггер 26. Сигнал U f предназначен для считывания состояния сумматора (RS-триг- гера 26) и возвращения Т триггера 25 в нулевое состояние Сигнал Up возвращает в нулевое состояние RS-триг- гер 26 (фиг„ 3).

Таким образом, на вход элемента ИЛИ 6 (фиг„ 1) поступают информационные элементы .1, „.12 из регистра 8 сдвига и проверочные элементы , несущие также сведения о синхрослове из сумматоров 5 по модулю два. Эта последовательность двоичных сигналов поступает в модулятор 7 (фиг. 1) и далее идет в канал 20 связи.

Принятые сигналы вводятся в демодулятор 11 (фиг„ 2) „ Продетектирован ные видеосигналы в виде последовательности двоичных элементов вводятс в регистр 12 сдвига.

Выходы соответствующих ячеек регистра сдвига связаны с входами сумматоров по модулю два блока 13 сумматоров по модулю два. В каждом из г сумматоров (г - число проверочных элементов, равное числу разрядов синхрослова) вычисляется сумма по модулю два части принятых и одного из проверочных символов. Например, для рассматриваемого поверхностно- объемного итеративного кода (19, 12, 4) в первом сумматоре суммируются , , , и элементы, т0е. определяется величина

Ь аЧа г+аЧа +с,

где C(j а(+аг+а9+а|0+Ь1 (получается на передающей стороне).

В результате суммирования имеем

b,a{+a +a9+aJ0 +at+a2+a9+a,0 +Ъ, Ъ(

(если без искажения приняты символы

ai az а аю и ciy л

Таким образом, через интервалы с,

равные длительности двоичного элемента, определяются величины Ь,,

b,...,bЈ. При правильном фазировани все элементы совпадают с элементами

СИНХрОСЛрВа,,;

ь В дешифратор 19 поступают сигналы b( , ..., Те из них, которые в синхрослове должны быть равны О, проходят на входы элементов И (фиго 7) через инверторы, а элементы, которые должны быть равны 1 - без инвертирования , На выходе а (фиг. 7) при отсутствии искажений выделяется сигнал совпадения символов Ь,...,bj-, соответствующий пику функции взаийно$ корреляции кодовых

, ,ЬТ и Ъ,..,,Ъ. Сиг- (фиг„ 7) соответству

5

сигналов uj,о.о, налы а,.о о,3g ют случаю, когда при образовании восстановленного синхрослова искажен один из его элементов. В результате дешифратор 19 выдает в соответствующий момент сигнал групповой синхронизации, которым фазируется синхронизатор 14.

Для исправления ошибок необходим синдром

K x- lfiplЈ e zx

представляющий слово, состоящее из проверок вида , i . i . ( . i . ..I

5

0/ а +а2+а а 0+( ; & а}+а4+а ,( рТ-а +аЈ+аЈ,+а«+в;;

Р1 ат+а8+а9+а +fa Ј а +а;+а +а +е;;

ЈЈ-ai+ai+afc+aЈ+ei; Jf«-a +ai+...+a,l2+fl ;

где штрих над символом показывает, что это принятый элемент,

Для восстановления синдрома сигналы с выходов сумматоров по модулю

два блока 13 сумматоров по модулю два пропускают через восстановитель 18 синдрома (фиг, 8).

Восстановленный синдром вводится в блок 17 опознавания ошибок, который обнаруживает место ошибки, т.е. определяет номер искаженного информационного элемента при наличии -однократной ошибки. Блок 17 опознавания ошибок (фиг. 9)

содержит 12 элементов И, соединенных своими входами с соответствующими семью входными шинами, на которые подаются сигналы в виде элементов синдрома К

При выделении пика синхросигнала синхронизатор 14 выдает сигнал считывания информационной части слова (символы 11.1.. .12) из регистра 12 сдвига и записи этих сигналов в вы-

ходной регистр 16, куда подаются

(при однократной ошибке) сигналы для инвертирования соответствующих сим- волово После этого по сигналу синхронизатора 14 исправленное кодовое

слово выдается на выход системы.

Таким образом, в системе обеспечивается передача цифровых сигналов с исправлением однократных ошибок с надежной групповой синхронизацией

без введения в кодовые слова избыточных элементов По сравнению с известными устройствами обеспечивается более высокая скорость передачи информации и большая надежность системы в связи с выполнением тех же задач с меньшим числом блоков и более простыми средствами.

В предлагаемой системе использу- е.тся так называемый плоскообъемный итеративный код, матрица которого изображена на фиг„ 10„ Информационные элементы а- изображены на поверхностях трех граней куба (прямо- угольного параллелепипеда)„

Проверочные элементы образуются по правилу

tf, а«+аг+а,+а ,о

ott aj+a4+aH+a,2

3, as+a6+a,.

рг-а7+а8+а,+а,4

Ј ,а5+а7+а,+а3

P2 a6+a6-fai+a4

# а,+а2+„. +а,2.

Кодовое расстояние кода

При использовании проверочных символов tf, , Уг, (3,, Рг 6i и бг получается код с dw(

Сравнение данного кода с некоторыми другими кодами с числом информа- ционных элементов показывает, что количество необнаруживаемых ошибок плоскообъемного кода (19, 12, 4) равно 27, для плоского итеративного кода (20, 12, 4) -60, для инверсного кода (24, 12, 4) - 66,

Плоскообъемный код (п, К, 3) ис- правляет одиночные ошибки0 Так, для кода (18, 12, 3) вероятность ошибочного декодирования слова

г г РОЫ ССЛР

При POU(cf8. ,

Ниже приведены некоторые из предлагаемых кодов: (9, 5, 3), (12, 7, 3), (13, 8, 3), (18, 12, 3), (23, 16, 3), (35, 24, 3), (29, 21, 3), а также (19, 12, 4), (24, 16, 4), (36, 26, 4), (30, 21, 4), а также плоские итеративные коды: (19, 12, 3),. (24, 16, 3), (35, 25,3), (29, 20, 3), а также (20, 12, 4) (25, 16, 4), (36, 25, 4), (30, 20, 4)о

5

0

5

0

5

0

п

5

Эти данные показывают, что плоско- объемные итеративные коды имеют меньшую избыточность по сравнению с плоскими итеративными кодами, представляемыми в виде плоских прямоугольных матриц.

Формула изобретения

1. Система для передачи и приема цифровой информации, содержащая на передающей стороне синхронизатор, первый выход которого соединен с первыми входами модулятора, распределителя импульсов и блока кодирования, вторые входы которого являются входами системы, второй выход синхронизатора соединен с третьим входом блока кодирования и вторым входом распределителя импульсов, первые и вторые выходы которого соединены соответственно с первым входами сумматоров по модулю два, блока элементов ИЛИ-И, выходы которого соединены с вторыми входами сумматоров по модулю два, выходы сумматоров по модулю два соединены с первыми входами элемента ИЛИ, выход которого соединен с вторым входом модулятора, выход которого соединен с каналом связи, на приемной стороне содержащая демодулятор, первый вход которого соединен с каналом связи, выход демодулятора соединен с первым входом синхронизатора и первым входом регистра сдвига, первые и вторые выходы которого соединены соответственно с первыми входами блока элементов И и блока сумматоров по модулю два и вторыми входами блока сумматоров по модулю два, первый выход синхронизатора соединен с вторыми входами демодулятора и регистра сдвига, отличающаяся тем, что, с целью повышения быстродействия и надежности системы, в нее введены на передающей стороне регистр сдвига, элемент И и триггер,выход которого соединен с первым входом элемента И, выход которого соединен с первым входом регистра сдвига, вторые и третий входы которого подключены соответственно к выходам блока кодирования и второму выходу синхронизатора, выход регистра сдвига соединен с вторыми входами блока элементов ИЛИ-И и элемента ИЛИ, третий выход синхронизатора соединен с третьими входами

91

сумматоров по модулю два и третьим

входом распределителя импульсов, третий и четвертый выходы которого соединены соответственно с первым и вторым входами триггера, вторбй вход элемента И подключен к первому выходу синхронизатора, на приемной стороне блок опознавания ошибок, восстановитель синдрома, дешифратор и выходной регистр, выходы блока сумматоров по модулю два соединены через восстановитель синдрома с соответствующими первыми входами блока опознавания ошибок и через дешифратор с вторым входом синхронизатора, второй и третий выходы которого соединены соответственно с первым входом выходного регистра и вторыми входами блока элементов И и блока опознавания ошибок, выходы которого соединены с вторыми входами выходного регистра третий вход блока сумматоров по модулю два подключен к первому выходу синхронизатора, выходы блока элементов И соединены с третьими входами выходного регистра,

выходы которого являются выходами системы.Дхвйм

0

025

10

2„ Система по п 1, о т л и ч а- ю щ а я с я тем, что сумматор по модулю два выполнен на триггерах, элементах И и элементе ИЛИ, выход которого соединен с первым входом первого элемента И, выход которого соединен с входом первого триггера, выход которого соединен с первыми входами второго и третьего элементов И.

, выходы второго и третьего элементов И соединены соответственно с первым входом элемента ИЛИ и S-входом второго триггера, выход которого сое- 5 динен с первым входом четвертого элемента И, выход которого является выходом сумматора по модулю два, вторые входы элемента ИЛИ, второго и четвертого элементов И, третьего элемента И и R-вход второго триггера являются соответствующими первыми входами сумматора по модулю два, третий вход элемента ИЛИ является вторым входом сумматора по модулю два, второй вход первого элемента И и третий вход третьего элемента И объединены и являют- ся третьим входом сумматора по модулю два„

0

5

Фиа.1

ФМ.1

Jtli

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для передачи информации с защитой от ошибок | 1989 |

|

SU1669080A1 |

| Устройство для передачи информации с контролем ошибок высокой кратности | 1987 |

|

SU1480129A1 |

| Устройство для передачи информации с защитой от ошибок | 1987 |

|

SU1490713A1 |

| СПОСОБ КОДИРОВАНИЯ И ДЕКОДИРОВАНИЯ ДАННЫХ ДЛЯ СИСТЕМЫ ПЕРСОНАЛЬНОГО РАДИОВЫЗОВА И ДЕКОДЕР ДЛЯ СИСТЕМЫ ПЕРСОНАЛЬНОГО РАДИОВЫЗОВА | 1994 |

|

RU2108667C1 |

| Кодек квазициклического кода | 1986 |

|

SU1349010A1 |

| Декодер | 1978 |

|

SU896614A1 |

| УСТРОЙСТВО УПРАВЛЕНИЯ ПЕРЕДАЧЕЙ ДАННЫХ В КАНАЛЕ МНОЖЕСТВЕННОГО ДОСТУПА | 2002 |

|

RU2233038C1 |

| Кодек самоортогонального квазициклического кода | 1986 |

|

SU1376247A1 |

| Устройство передачи сообщений | 1985 |

|

SU1506555A1 |

| Многоканальная цифровая телеметрическая система | 1989 |

|

SU1672498A2 |

Изобретение относится к электросвязи и может быть применено в телеметрии и при передаче данных. Цель изобретения - повышение быстродействия и надежности системы Используется модификация итеративного кода, в котором информационные элементы слов располагаются на трех взаимно перпендикулярных гранях прямоугольного параллелепипеда. Проверочные символы образуются суммированием по модулю два информационных символов, размещенных на одной линии двух взаимно перпендикулярных граней. Кодовое расстояние кода равно 3. Система содержит на передающей стороне синхронизатор, блок кодирования, распределитель импульсов, блок элементов ИЛИ- И, сумматоры по модулю два, элемент ИЛИ, модулятор, регистр сдвига, эле- , мент И и триггер, на приемной стороне - демодулятор, регистр сдвига, блок сумматоров по модулю два, синхронизатор, блок элементов И, выходной регистр, блок опознавания ошибок, восстановитель синдрома, дешифратор и канал связи. 1 э,п. ф-лы, 10 ил. (Л

U2rS

li/5

I 1 I L-LLLJLJ.. J J

УЙ- WwФие.З

П

фиа.Ь

Двоичный счетчик

7%

%

V W (( {( (

s«

Дешифровочная матрица

П

RP1Ж Ж

TlrWIlr lr l

,

S|fl

2

%

(( {( (

s«

П

/2

;ff

7

ЖЈ

Ж «

S/7

V

Я /21 Фиг. 5

S2o

Фиг. б

Вых. сигналы bf toj t bj Ъ bj b Примечание

npy I

i -я- о /

1

J

У

о t о о t 0100 1

Синхрослобо не искажено Искажен Ь

-//-

и-// -

. . it

-// -

Фиг. 8

ОС

ОС

Фив. 9

Фив. 10

/

г

fT ЬЧ

| Разборный с внутренней печью кипятильник | 1922 |

|

SU9A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1991-03-23—Публикация

1989-02-03—Подача