Г «««Н k ММЦ 1

. Ж,

|сжз

Фиг.1

Изобретение относится к автоматике и вычислительной технике и может быть использовано в системах передачи информации.

Цель изобретения - повышение помехоустойчивости кодека при использовании восьмифазной модуляции.

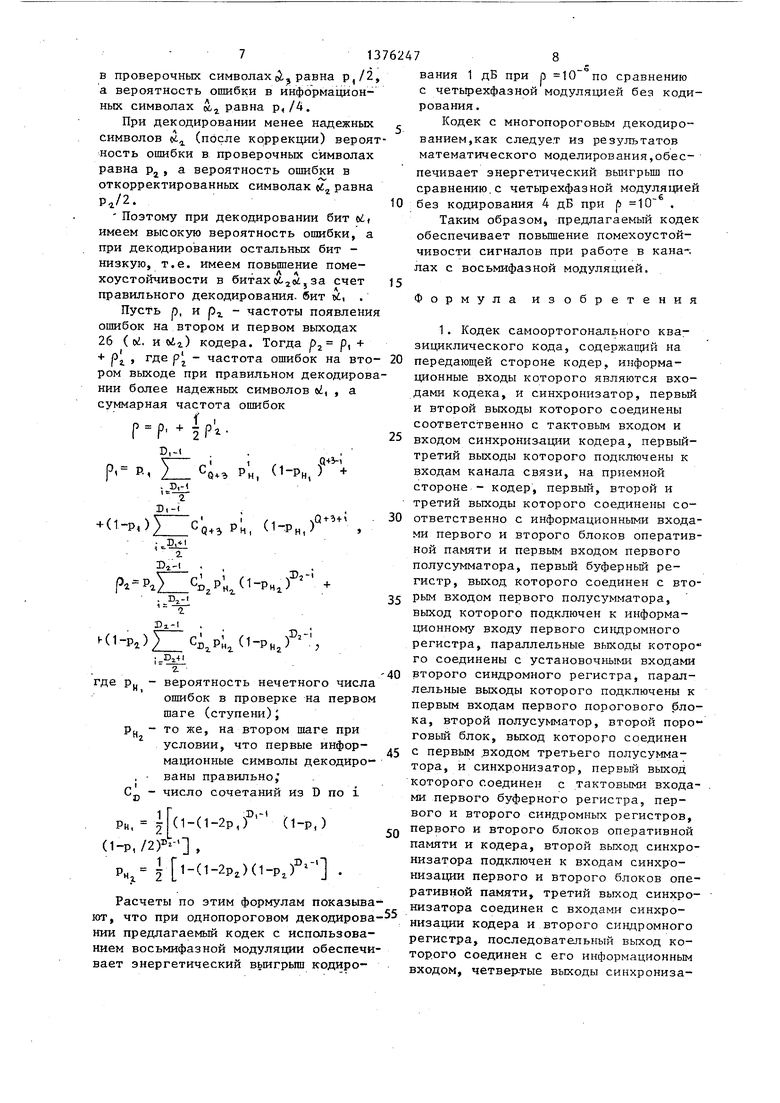

На фиг.1 представлена блок-схема кодека самоортогонального квазициклического кода ,на фиг.2-4 - функциональные схемы соответственно кодера, корректора и канала связи; на фиг.5- фазовая диаграмма сигналов; на фиг.6- временная структура сигналов в характерных точках схемы кодека.

Кодек самоортогонального квазициклического кйда состоит из (фиг.1) передающей стороны 1, канала 2 связи и приемной стороны 3. Передающая сторона 1 кодека содержит кодер 4 и синхронизатор 5. Приемная сторона 3 - включает в себя кодер 6, первый 7 и второй 8 буферные регистры, первый- четвертьй блоки 9-12 оперативной па- мяти, корректор 13, первый-третий полусумматоры 14-16, первый-четвертый синдромные регистры 17-20, первый 21 и втйрой 22 пороговые блоки и синхронизатор 23. На фиг.1 обозначены входы 24 кодека, вход 25 синхронизации приемной стороны 3 и выходы 26 кодека.

Кодер 4 на передающей стороне и кодер 6 на приемной стороне кодека выполнены одинаково (фиг.2); на пер- вом-четвертом регистрах 27-30 сдвига и полусумматоре 31. На фиг.2 обозначены информационные 32 и тактовый 33 входы, вход 34 синхронизации и выхо- ды 35.

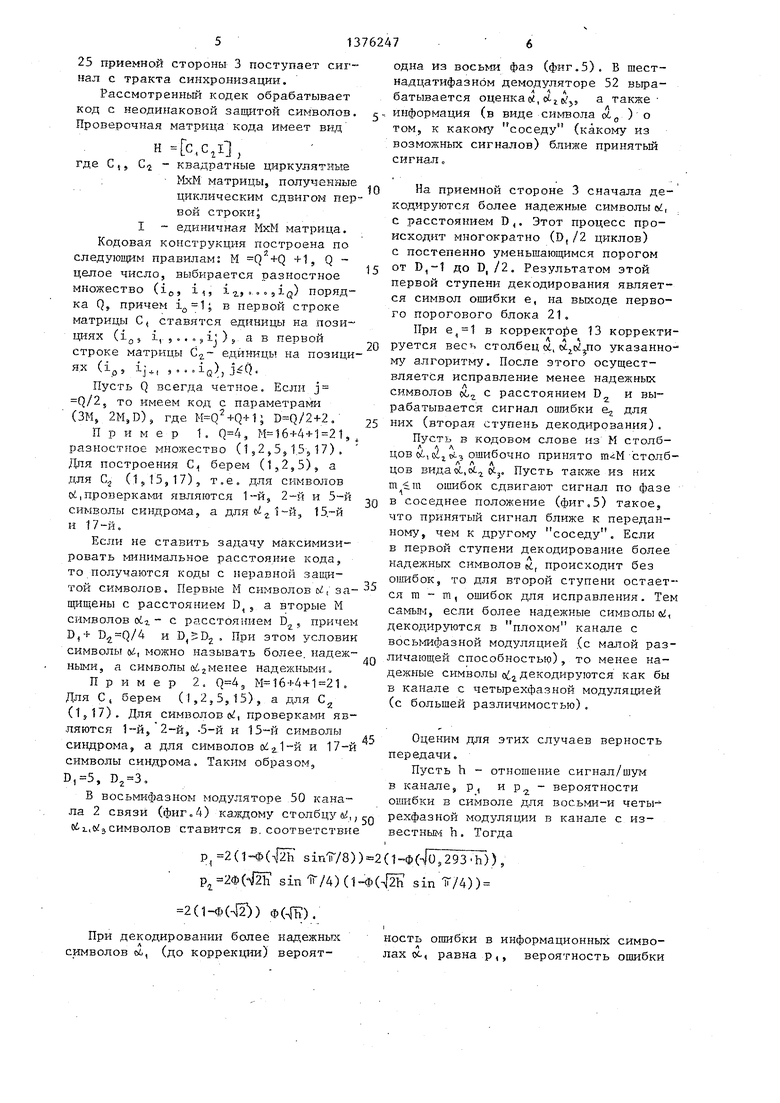

Корректор 13 выполнен (фиг.3) на элементе НЕ 36, элементе ИЛИ 37, трех элементах И- 38 и сумматоре 39. На фиг.З обозначены входы 40 и выходы 4 Т

Пороговый блок 21 или 22 представляет собой сумматор, входы которого являются первыми входами блока, выходы подключены к первым входам элемента сравнения, вторые входы и вькод которого являются вторыми входами и выходом порогового блока.

Синхронизатор 23 приемной стороны включает в себя (фиг.1) первый 42 и -второй 43 умножители частоты, первый 44 и второй 45 делители Частоты, первый 46 и второй 47 вычитающие счет - чики и генератор 48 тактовых импульсов. Соединения синхронизатора 23 с

О 5

0 5 0

0

0

соответствующими блоками приемной стороны 3 обозначены буквами F,F, , 45 Ф Н, и Hj. На соединениях, выполненных шинами, указана их кратность.

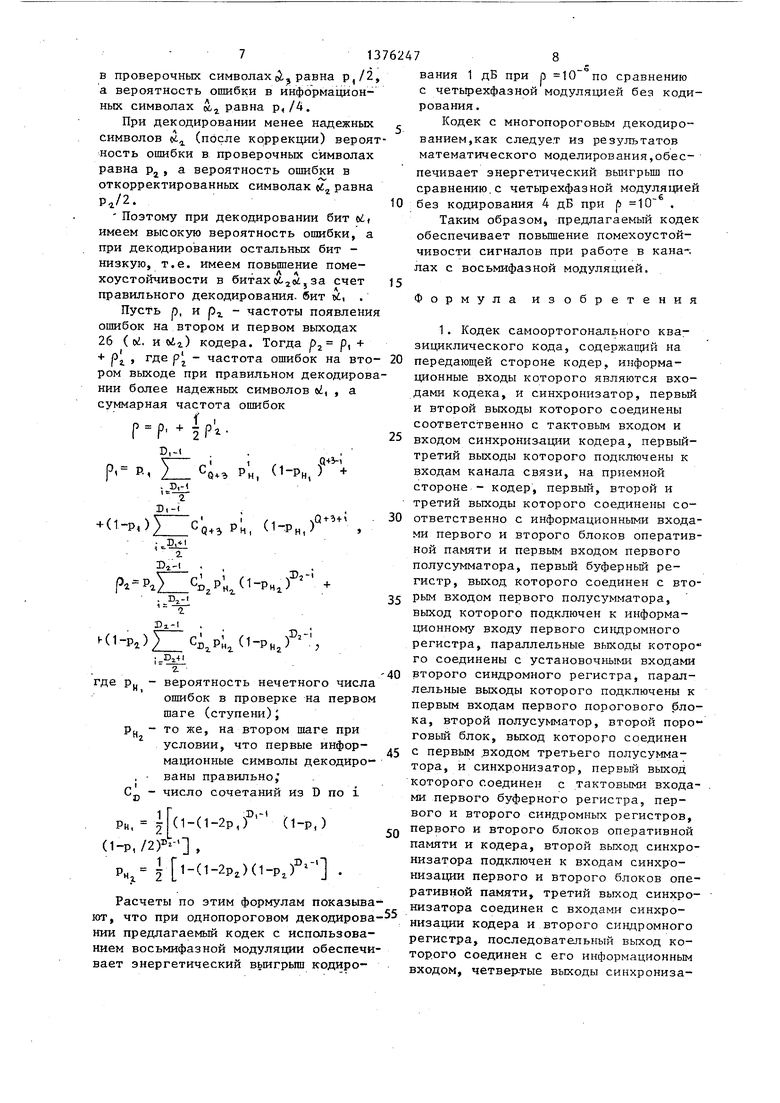

Канал 2 связи представляет собой (фиг.4) соединенные последовательно первый преобразователь 49 кода, вось- мифазный фазовый модулятор 50, линию 51 связи, шестнадцатифазный фазовый демодулятор 52 и второй, преобразователь 53 кода. Преобразователи 49 и 53 обеспечивают соответственно преобразование двоичного кода в восьми-, ричный и шестнадцатиричного кода в двоичньй.

Регистры 7,17-20, 27-30, а также блоки 9-12 имеют емкость М бит, где М - длина ко.пового слова циклического кода, из которого построен используемый квазициклический (N,K,D)- код, где - общее число символов в кодовом слове;К 2М - число информационных символов; D - расстояние Хэмминга используемого кода.- Регистр В имеет емкость 2М бит.

Частоты сигналов синхронизатора 23 имеют следующие значения: на первом выходе F, на втором и пятом выхо FDi „ FDa дах F, --- , F г- на третьем

F выходе Ф - , на четвертых и шестых

F F

выходах Н - и Н- -. Кратность М М

последних из указанных выходов ; )log2(D;-1)r; ,2vl l ближайшее меньшее целое число.

Кодек самоортогонального квазициклического кода работает следующим образом.

Исходная информация с входов 24 в двоичной форме Двумя импульсными потоками поступает на входы 32 кодера 4. При этом символы oi, и cij поступают соответственно на регистры 27 и 28. После их заполнения по сигналу на входе 34 (сигнал цикловой метки, фиг.6) информация переписывается в параллельном виде в регистры 29 и 30 и подвергается циклическим сдвигам по тактовым импульсам на входе 33. В результате на выходе полусумматора 31 формируются проверочные символы oij, которые вместе с информационными символами ot, и ciг подаются на соответствующие выходы 35. Таким образом.

в кодере 4 осуществляется кодирование информации путем перемножения информационного слова на порождающую матрицу самоортогонального квазицикли- ческого кода.

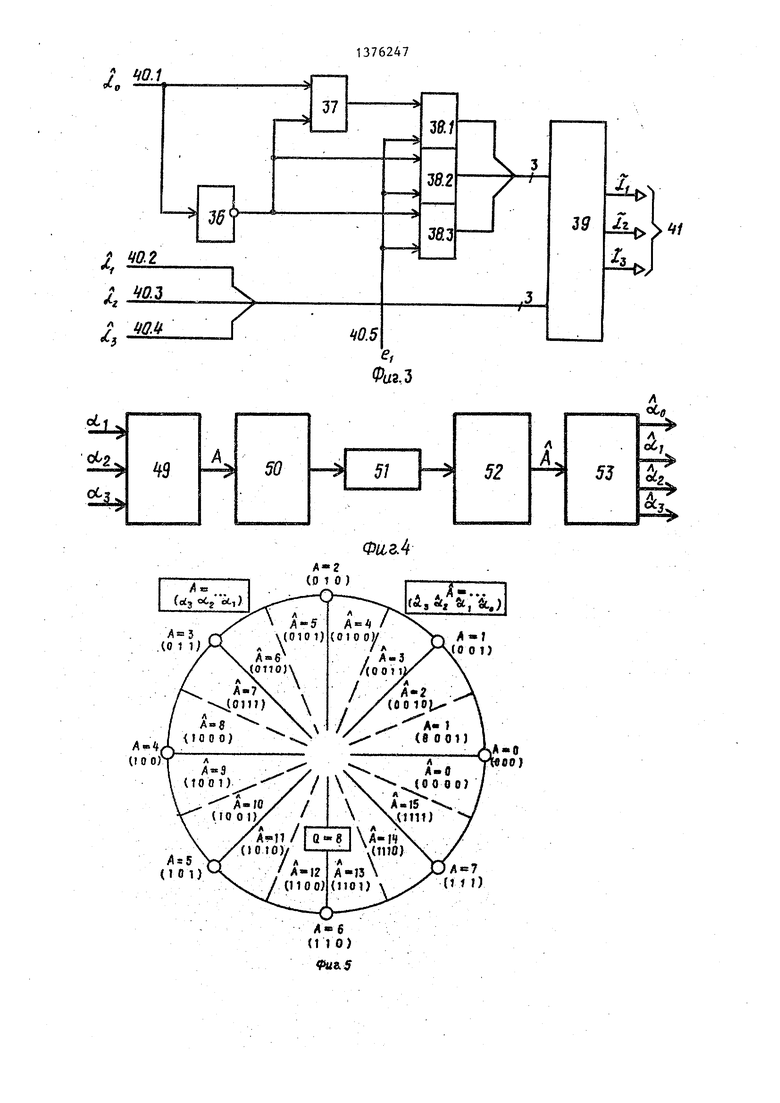

С выходов кодера 4 каждая двоичная последовательность &;, ci е зпопадает в канал 2 связи, где она преобразуется в цифровой сигнал со значениями от О до 7 (преобразователь 49,фиг.4), по которому в модуляторе 50 образуется сигнал несущей частоты с одним из восьми значений фазы (фиг.5). В линии 51 связи этот сигнал искажается под действием шумов и помех. В демодуляторе 52 искаженный сигнал оценивается так, что его фазе ставится в соответствие ближайшая из оценок, имеющих значения от О до 15. Эта оценка преобразуется в двоичный сигнал (преобразователь 53), причем СИМВОЛЫ к ода оценки od, , oil , поступают на пер-- вьш-третий выходы канала 2 связи, а символ oi-o (младший разряд полученно- го кода) - на четвертьй выход канала 2 ..

л л

Далее оценку информационных «i,, oi проверочных Ы/, и вспомогательных oio символов параллельно поступают на входы приемной стороны 3. Информационные символы oi, ,ii,j кодируются в кодере 6 аналогично тому, как это делается в кодере 4, т.е. на третьем выхода кодера 6 вырабатываются проверочные символы od,. Проверочные и

А , А

вспомогательные символы oij и ot запоминаются в регистрах 7 и 8. В полусумматоре 14 соответствующие символы «23 и обJскладываются по модулю два, образуя синдром, который запоминается в регистре 17. Одновременно символы (2,, , oi и oi.3 запоминаются в блоках 9-11 оперативной памяти.

По сигналу цикловой метки с выхода старшего разряда вычитающего счетчика 46 синхронизатора 23 информация из регистра 17 переписывается в регистр 18, где начинаются циклические сдвиги информации и D,/2 циклов для последующего исправления. При этом исправляются только символы к, и nor следующие проверки в первом пороговом блоке 2,1 относятся тоже только к символу cd, .

Результаты исправлений символа об« в виде параллельного кода подаются на вход первого порогового блока 21 с изменяемым порогом, который устанавливается на его вторых ,входах (Н,). Если на выходе блока 21 символ е, 1, то по обратной связи он исправляет те символы во втором синдромном регистре 18, которые соответствуют проверкам. Если е,0, то исправление не производится.

Задержанные во втором буферном регистре 8 и в блоках 9-11 символый- oL символ е, с выхода первого порогового блока 21 поступают на входы корректора 13, алгоритм функционирования которого имеет вид

если , то 2.,2iOij &i,ciiOi, © е, J

0, TooZ,S6iS.j-, ф 7е,, где все ( принимают двоичные значени О либо 1;

ф - сумма по модулю восемь;

запись oi, ei2 Ы5 имеет смысл целого числа от О до 7 в двоичной системе исчисления,

е, - символ ошибки на пятом входе корректора 13.

Согласно этому алгоритму все символы oi, oi 1 (х J сигнала корректируются только в том случае, если е, 1, при этом, если то к фазе сигнала

прибавляется т з. еслиобд и, то вычитается Т/4 (фиг.5). В этом процессе ct, корректируется всегда, а половине случаев.

После коррекции символы :, поступают на второй выход 26.2 кодека, символы 6 Jзaпo шнaютcя в четвертом блоке 12, а символы oi-, вместе с некор ректнрованными символами eJi, складываются во втором полусумматоре 15 и результат используется для исправления синдрома, поступающего с выхода второго синдромного регистра 18 на один из входов второго полусумматора

Если корректор 13 исправляет проверочный символ (т.е. ; (stj) , то вторьтм полусумматором 15 осуществля ется коррекция соответствующего символа синдрома, поступающего на один из входов полусумматора 15.

Аналогично в процессе обработки в третьем 19 и четвертом 20 синдром- ных регистрах, втором пороговом блоке 22 с другим изменяемым порогом и третьем полусумматоре 16 производится коррекция символа S , в результате которой формируется сигнал на первом выходе-26.1 кодека. На вход

25 приемной стороны 3 поступает сигнал с тракта синхронизации.

Рассмотренный кодек обрабатывает

одна из фаз (фиг.5). В шест- надцатифазном демодуляторе 52 вьфа- батывается оценка ci, , э такжекод с неодинаковой защитой символов, с-, информация (в виде символа oig ) о Проверочная матрица кода имеет вид

н Гс,с,

том, к какому соседу (какому из возможных сигналов) ближе принятый сигнал о

10

где С,5 С - квадратные циркулятяые : МхМ матрицы, полученные циклическим сдвигом первой строки,

I - единичная МхМ матрица. Кодовая конструкция построена по

следующим правилам М +1, Q р /2. Результатом этой целое число, выбирается разностное ступени декодирования являет- множество (1„, 1,, I,.,.,IQ) поряд- , g вькоде первоНа приемной стороне 3 сначала декодируются более надежные символы 6, с расстоянием D,. Этот процесс происходит многократно (D,/2 циклов) с постепенно уменьшающимся порогом

ка Q, причем в первой строке матрицы С, ставятся единицы на пози циях (i,.,, i, 5o..,i:)j а в первой строке матрицы С единицы на позици ях (ij,, ij, , , . .ifj), .

Пусть Q всегда четное. Если j Q/2, то имеем код с параметрами (ЗМ, 2м,D), где M Q +Q-M; D Q/2+2,

Пример 1. , )-4 + , разностное множество (1,2 ,5j 1,5j 17) , Для построения С берем (1,2,5), а для С (1515,17), т.е. для символов Ы,проверками являются 1--й, 2-й и 5-й символы , а для 1 Ч- i,, 15.й и 17-й,

Если не ставить задачу максимизировать г-мнимальное расстояние кода, то получаются коды с неравной защиго порогового блока 21,

При е,1 в корректоре 13 корректи20 руется весь столбец oi, указанному алгоритму. После этого осуществляется исправление менее надежных символов об. с расстоянием D, и вырабатывается сигнал оишбки е для

25 них (вторая ступень декодирования).

Пусть в кодовом слове из М столбцов 5-, (гЫ-з ошибочно принято столбцов видаоб.о. oij. Пусть также из них m m ошибок сдвигают сигнал по фазе

30 в соседнее положение (фиг.5) такое, что принятый сигнал ближе к переданному, чем к другом соседу. Если в первой ступени декодирование более надежных символов (я1, происходит без оиибок, то для второй ступени остаетТ /- VX J-LCi . а i V-f /,Oi Л и i -f JJ К I. - -iyil llH,

той символов. Первые М символов сг, ся га - m, ошибок для исправления. Тем

40

щнщены с расстоянием D,, а вторые М символов сх.г - с расстоянием D , причем D,-b и , При этом условии символь о/., можно называть более, надежными, а символы ai2 менее надежньв- и.

Пример 2, M 16-i-4 + . Для С, берем (1,2,5,15), а для С, (1,17). Для символов проверками являются 1--Й, 2-й, 5-й и 15-й символы синдрома, а для символов и 17-й символы синдрома. Таким образом, D,5, D,,3,

В восьмифазном модуляторе 50 канала 2 связи (фиГо4) ка: кдому столбцу f,, г oii,; символов ставится в, соответствие

. 45

самьи, если более надежные символы ai, декодируются в плохом канале с восьмифазной модуляцией (с малой различающей способностью), то менее надежные символы cij декодируются как бы в канале с четырехфазной модуляцией (с большей различимостью).

Оценим для этих случаев верность передачи.

Пусть h - отношение сигнал/шум в канале, р, и р,, - вероятности ошибки в символе для вocь -IИ-и четырехфазной мод шяции в канале с известным h. Тогда

одна из фаз (фиг.5). В шест- надцатифазном демодуляторе 52 вьфа- батывается оценка ci, , э такжеинформация (в виде символа oig ) о

информация (в виде символа oig ) о

том, к какому соседу (какому из возможных сигналов) ближе принятый сигнал о

р /2. Результатом этой ступени декодирования являет- , g вькоде первоНа приемной стороне 3 сначала декодируются более надежные символы 6, с расстоянием D,. Этот процесс происходит многократно (D,/2 циклов) с постепенно уменьшающимся порогом

го порогового блока 21,

При е,1 в корректоре 13 корректи20 руется весь столбец oi, указанному алгоритму. После этого осуществляется исправление менее надежных символов об. с расстоянием D, и вырабатывается сигнал оишбки е для

25 них (вторая ступень декодирования).

Пусть в кодовом слове из М столбцов 5-, (гЫ-з ошибочно принято столбцов видаоб.о. oij. Пусть также из них m m ошибок сдвигают сигнал по фазе

30 в соседнее положение (фиг.5) такое, что принятый сигнал ближе к переданному, чем к другом соседу. Если в первой ступени декодирование более надежных символов (я1, происходит без оиибок, то для второй ступени остаетТ /- VX J-LCi . а i V-f /,Oi Л и i -f JJ К I. - -iyil llH,

ся га - m, ошибок для исправления. Тем

самьи, если более надежные символы ai, декодируются в плохом канале с восьмифазной модуляцией (с малой различающей способностью), то менее надежные символы cij декодируются как бы в канале с четырехфазной модуляцией (с большей различимостью).

Оценим для этих случаев верность передачи.

Пусть h - отношение сигнал/шум в канале, р, и р,, - вероятности ошибки в символе для вocь -IИ-и четырехфазной мод шяции в канале с известным h. Тогда

| название | год | авторы | номер документа |

|---|---|---|---|

| Кодек квазициклического кода | 1986 |

|

SU1349010A1 |

| Сверточный кодек с алгоритмом порогового декодирования | 1985 |

|

SU1327296A1 |

| Пороговый декодер сверточного кода | 1982 |

|

SU1078654A1 |

| Декодер сверточного кода | 1985 |

|

SU1320904A1 |

| Способ декодирования информации с использованием свёрточных кодов | 2016 |

|

RU2637487C1 |

| Кодек несистематического сверточного кода | 1990 |

|

SU1714812A1 |

| Пороговый декодер сверточного кода | 1991 |

|

SU1781825A1 |

| Устройство для кодирования и декодирования двоичной информации сверточными кодами | 1982 |

|

SU1035819A1 |

| Кодер несистематического сверточного кода | 1990 |

|

SU1695516A1 |

| Пороговый декодер сверточного кода | 1984 |

|

SU1185629A1 |

Изобретение относится к автоматике и вычислительной технике и позволяет повысить помехоустойчивость кодека при использовании восьмифаз- ной модуляции. Кодек самоортогонального квазициклического кода содержит канал 2 связи, на передающей стороне 1 - кодер 4 и синхронизатор 5, на приемной стороне 3 - кодер 6, буферный регистр 7, блоки 9,10 оператив- г ной памяти, полусумматоры 14-16., синдромные регистры 17,18, пороговые блоки 21,22 и синхронизатор 23. Введение на приемной стороне 3 буферного регистра 8, блоков 11,12 оперативной памяти, синдромных регистров 19,20 и корректора 13 обеспечивает многопороговое декодирование, дающее энергетический вьигрыш по сравнению с известным устройством. 4 з.п.ф-лы, 6 ил. S (Л

р, 2(1HE(if2h 51пТ/8))2(1-Ф(4о,293 Ь)), (-42Ь sin 1/4)((- sin Т/4))(1-Ф(-42)) Ф(-4Ь ).

При декодировании более надежньсс символов ы., (до коррекции) вероятность ошибки в информационных символ

лах (:.( равна р,, вероятность ошибки

в проверочных символахli, равна р,/2, вания 1 дБ при р 10 °по сравнению а вероятность ошибки в информацион- ных символах i, равна .

с четырехфазной модуляцией без коди рования .

Кодек с многопороговым декодированием, как следует из результатов математического моделирования,обес печивает энергетический вьшгрьшд по сравнению.с четьфехфазной модуляцие без кодирования 4 дБ при |Ь 10 .

При декодировании менее надежных с символов (после коррекции) вероятность ошибки в проверочных символах равна PJ, а вероятность ошибки в откорректированных символах ог равна .10

Поэтому при декодировании бит Ы., имеем высокую вероятность ошибки, а при декодировании остальных бит - низкую, т.е. имеем повьшение помехоустойчивости в битахб. счет 15 правильного декодирования, бит ., .

Пусть р, и рг - частоты появления ошибок на втором и первом выходах 26 (oi, и 6ii) кодера. Тогда 0 р, +

Кодек с многопороговым декодированием, как следует из результатов математического моделирования,обеспечивает энергетический вьшгрьшд по сравнению.с четьфехфазной модуляцие без кодирования 4 дБ при |Ь 10 .

Таким образом, предлагаемый коде обеспечивает повышение помехоустойчивости сигналов при работе в каналах с восьмифазной модуляцией.

Формула изобретени

+ PJ , где р - частота ошибок на вто- 20 передающей стороне кодер, информа- ром выходе при правильном декодировании более надежных символов ei, , а суммарная частота ошибок f ,

р р,

+ орг

25

ционные входы которого являются вхо дами кодека, и синхронизатор, первы и второй выходы которого соединены соответственно с тактовым входом и входом синхронизации кодера, первый третий выходы которого подключены к входам канала связи, на приемной стороне - кодер, первый, второй и третий вьпсоды которого соединены со ответственно с информационными вход ми первого и второго блоков операти ной памяти и первым входом первого полусумматора, первый буферный регистр, выход которого соединен с вт рым входом первого полусумматора, выход которого подключен к информационному входу первого синдромного регистра, параллельные выходы котор го соединены с установочными входам второго синдромного регистра, парал лельные выходы которого подключены первым входам первого порогового бл ка, второй полусумматор, второй пор говый блок, выход которого соединен

D,-(

Р- И

Q + Э

,, .Q+i(1-Рн, ) +

+ (1-р,)

Q + 3 Н,

(1-.р„,)

п±ъ+

.3)7р.-р.,(1-ри.) ;.в

i-p,).(i-pH,).S

г.

де Рц - вероятность нечетного числа ошибок в проверке на первом шаге (ступени),

РЦ - то же, на втором шаге при условии, что первые инфор- мат онные символы декодиро- , ваны правильно,

число сочетаний из D по i

Cj.1

Рн, 2

D.-t

(1-(1-2р,) (1-р,)

(1-р,/2)-4,

Р„ I l-(1-2p,)(1-p,) .

Расчеты по этим формулам показывают, что при однопороговом декодирова НИИ предлагаемый кодек с использованием восьмифазной модуляции обеспечивает энергетический вьшгрыш кодирования 1 дБ при р 10 °по сравнению

с четырехфазной модуляцией без кодирования .

Кодек с многопороговым декодированием, как следует из результатов математического моделирования,обеспечивает энергетический вьшгрьшд по сравнению.с четьфехфазной модуляцией без кодирования 4 дБ при |Ь 10 .

Таким образом, предлагаемый кодек обеспечивает повышение помехоустойчивости сигналов при работе в кана. лах с восьмифазной модуляцией.

Формула изобретения

передающей стороне кодер, информа-

ционные входы которого являются входами кодека, и синхронизатор, первый и второй выходы которого соединены соответственно с тактовым входом и входом синхронизации кодера, первый- третий выходы которого подключены к входам канала связи, на приемной стороне - кодер, первый, второй и третий вьпсоды которого соединены соответственно с информационными входами первого и второго блоков оперативной памяти и первым входом первого полусумматора, первый буферный регистр, выход которого соединен с вторым входом первого полусумматора, выход которого подключен к информационному входу первого синдромного регистра, параллельные выходы которого соединены с установочными входами второго синдромного регистра, параллельные выходы которого подключены к первым входам первого порогового блока, второй полусумматор, второй поро говый блок, выход которого соединен

45

с первым .входом третьего полусумматора, и синхронизатор, первый выход которого соединен с тактовыми входами первого буферного регистра, первого и второго синдромных регистров, д первого и второго блоков оперативной памяти и кодера, второй выход синхронизатора подключен к входам синхронизации первого и второго блоков оперативной памяти, третий выход синхронизатора соединен с входами синхронизации кодера и второго синдромного регистра, последовательный выход которого соединен с его информационным входом, четвер-тые выходы синхрониза55

9137

тора подключены к вторым входам первого порогового блока, вьгкод которого соединен с управляющим входом второго синдромного регистра, первый и второй инфopмaIJ7ioнныe входы кодера и информационный вход первого буферного регистра подключены соответственно к первому - третьему выходам каналам

связи, выход третьего полусумматора является первым выходом кодека, о т л и ч а ю щ и и с я тем, что, с целью повышения помехоустойчивости кодека при использовании восьмифаз- ной модуляции, на приемной стороне кодека введены корректор, третий и четвертый блоки оперативной памяти, третий и четвертый синдромные регистры и второй буферный регистр, выход которого соединен с первым входом корректора, выходы первого и второго блоков оперативной памяти соединены соответственно с вторым и третьим входами корректора, первый и второй выходы которого соединены соответственно с информационным входом четвертого блока оперативной памяти и с первым входом второго полусумматора, выходы которых подключены соответственно к второму входу третьего полусумматора и к информационному входу третьего синдромного регистра, информационный вход третьего блока оперативной памяти подключен к выходу первого буферного регистра, выход третьего блока оперативной памяти соединен с вторым входом второго полусумматора и четвертым входом корректора, пятый вход которого подключен к выходу первого порогового блока, третий вход второго полусумматора подключен к последовательному выходу второго синдромного регистра, параллельные выходы третьего синдромного регистра соединены с установочными входами четвертого синдромного регистра, параллельные выходы которого соединены с установочными входами второго порогового блока, тактовые входы второго буферного регистра, третьего блока оперативной памяти, третьего и четвертого синдромных регистров подключены к первому выходу синхрони- .затора, вход синхронизации третьего блока оперативной памяти и тактовый вход четвертого блока оперативной памяти подключены к второму выходу синхронизатора, вход синхронизации четвертого синдромного регистра

5

0

ключен к третьему выходу синхронизатора, пятьш и шестой выходы которого соединены соответственно с входом .

синхронизации четвертого блока оперативной памяти и вторыми входами второго порогового блока, последовательный выход четвертого синдромного регистра соединен с его информацион0 ным входом, информационный вход второго буферного регистра подключен к четвертому выходу канала связи, вход синхронизатора является входом синхронизации кодека, третий выход корректора является вторым выходом кодека.

2,Кодек ПОП.1, отличающийся тем, что кодер передающей и приемной стороны выполнен на регистрах сдвига и полусумматоре, параллельные выходы первого и второго регистров сдвига соединены с установочными входами соответственно третьего

и четвертого регистров сдвига, параллельные выходы которых подключены соответственно к первым и вторым входам полусумматора, последовательные выходы третьего и четвертого регистров сдвига соединены со своими информационными входами, информационные входы первого и второго регистров сдвига являются соответственно первым и вторы1 1 информационными входами кодера, тактовые входы всех регистров сдвига объединены и являются тактовым входом кодера, входы синхронизации третьего и четвертого регистров сдвига объединены и являются входом синхронизации кодера, последовательные выходы первого и второго регистров сдвига и выход полусумматора являются соответственно первым - третьим выходами кодерл.

3,Кодек ПОП.1, отличаю5

0

5

0

щ и и с я тем, что корректор выполг н ен на элементах И, элементе НЕ, сумматоре и элементе ИЛИ, выход которого соединен с первым входом первого элемента И, выход элемента НЕ подключен к первому входу элемента ИЛИ и первым входам второго и третьего элементов И, выходы первого-третьего элементов И соединены с соответствую- Е;ИМИ первыми входами сумматора, второй вход элемента ИЛИ и вход элемента НЕ объединены и являются первым входом корректора, вторые входы сумматора являются вторым - четвертым входами корректора, вторые входы

10

11137624712

всех элементов И объединены и являются пятым входом корректора, выходы сумматора являются соответствующими выходами корректора.

4, Кодек поп,1, отличающийся тем, что синхронизатор приемной стороны выполнен на умножителях частоты, делителях частоты, вычитающих счетчиках и генераторе тактовых импульсов, выход которого подключен к входам умножителей частоты и является первым выходом синхронизатора, выходы первого и второго умножителей частоты через одноименные делители частоты подключены к входам одноименных вычитающих счетчиков, вход генератора тактовых импульсов является входом синхронизатора, выход первого умножителя частоты, 20 ды второго преобразователя кода яв- выход старшего разряда первого вычи- ляются одноименными вьЕКодаот-г канала тающего счетчика, выходы всех разря- связи.

дов первого вычитающего счетчика, выход второго умножителя частоты и выходы разрядов второго вьгчитаюш;его счетчика являются соответственно вторым, третьим, четвертыми, пятым и шестыми выходами синхронизатора,

(1

/

32

Ф ч/ у U 29 Г

2

33 3

ды второго преобразователя кода яв- ляются одноименными вьЕКодаот-г канала связи.

дов первого вычитающего счетчика, выход второго умножителя частоты и выходы разрядов второго вьгчитаюш;его счетчика являются соответственно вторым, третьим, четвертыми, пятым и шестыми выходами синхронизатора,

28

}

35

30

3f

f

Фиг2

об2

ПК

Л 5

(IOU

л

06tf

,

л.

&.

ФагА

Am

А А л в

(Аз &, , &J

.(001)

00}

мт

мт

Вх.

(П

(2)

их. декодера

Запись б 03а

апись 8 син.рег.

Петка переписи Ш рабление ouiuS.c расст. Dj

Коррекция

Запись в син. рег.

Мел Йспраблениё

Метка пере

oujuS. с

мт мт мт .

I I I

I

-U,U)(/(. метки

fiwx.(J)

oC/2

3

в син. рег.

Мел ениё

Метка переписи if.

oujuS. с paccm.Dj 8wx(2)

/ 2 M

Фиг, 6

| Труды НИИР, 1983, № 1, с.89-99 | |||

| IEEE Transact ion s.on Communications, 1978, V | |||

| Прибор для получения стереоскопических впечатлений от двух изображений различного масштаба | 1917 |

|

SU26A1 |

| переводов/Под ред.Э.М.Блоха - М.: Мир, 1970, с.36-67, рис.2,4. | |||

Авторы

Даты

1988-02-23—Публикация

1986-06-04—Подача