1

Изобретение предназначено для использования в нелинейных аналоге-1 цифровых преобразователях, в устройствах амплитудной селекции, а также в трактах усиления для сжатия их ди-- намического диапазона.

Цель изобретения - повышение быстродействия и точности каскада.

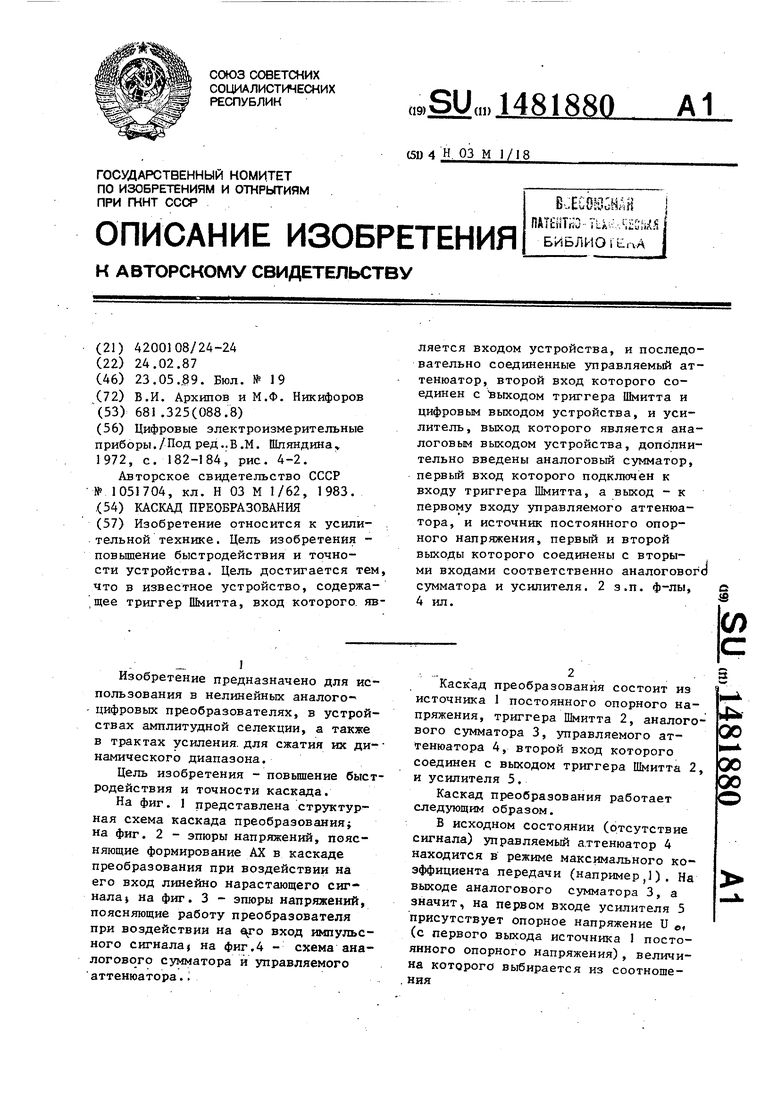

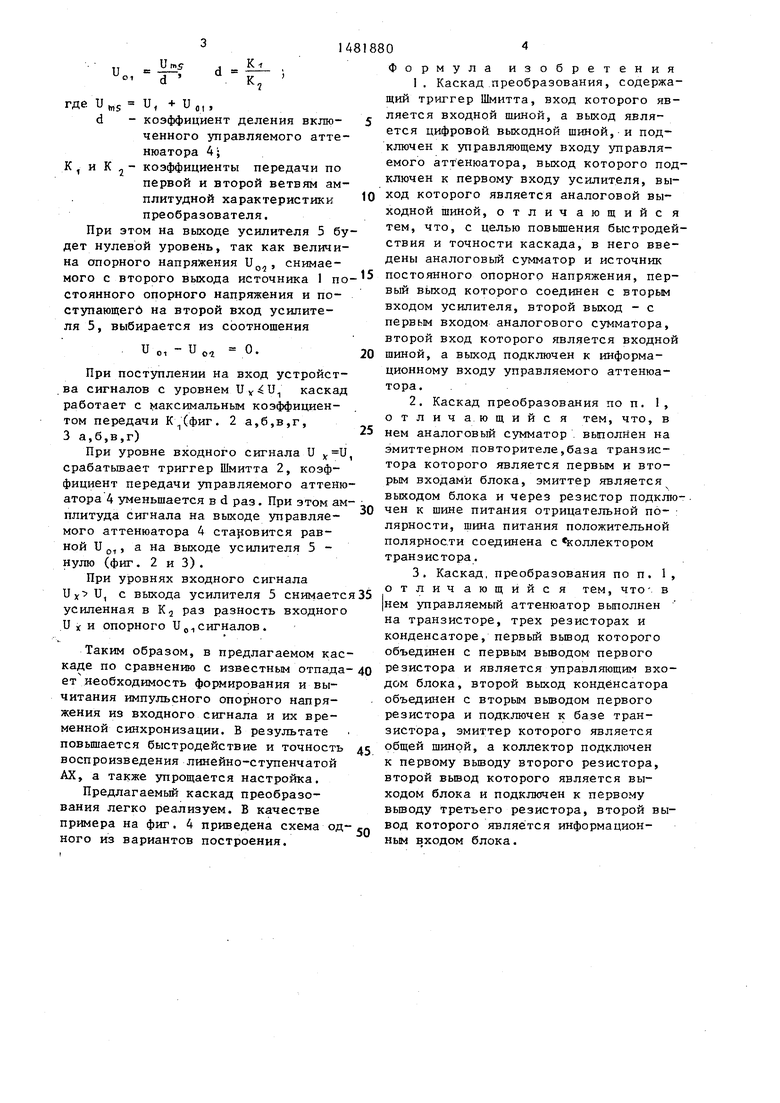

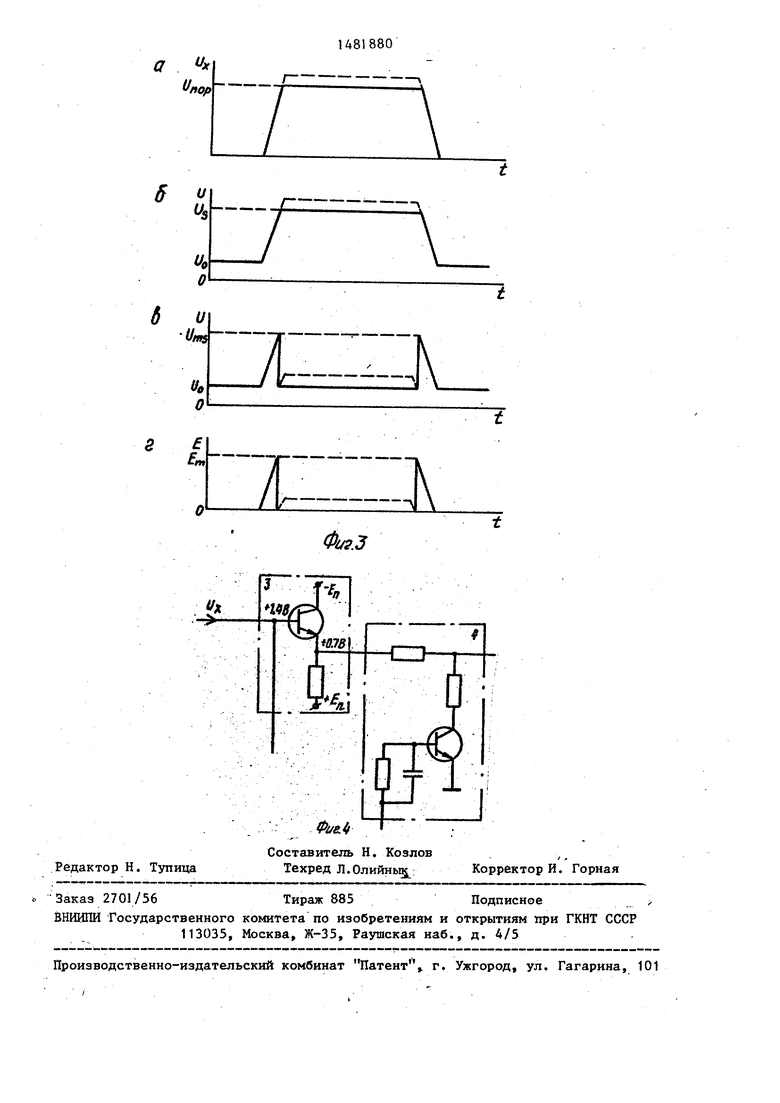

На фиг. 1 представлена структурная схема каскада преобразования$ на фиг. 2 - эпюры напряжений, поясняющие формирование АХ в каскаде преобразования при воздействии на его вход линейно нарастающего сигнала на фиг. 3 - эпюры напряжений, поясняющие работу преобразователя при воздействии на цго вход импульсного сигнала, на фиг,4 - схема аналогового сумматора и управляемого аттенюатора..

Каскад преобразования состоит из источника 1 постоянного опорного напряжения, триггера Шмитта 2, аналогового сумматора 3, управляемого аттенюатора 4, второй вход которого соединен с выходом триггера Шмитта 2, и усилителя 5.

Каскад преобразования работает следующим образом.

В исходном состоянии (отсутствие сигнала) управляемый аттенюатор 4 находится в режиме максимального коэффициента передачи (например 1). На выходе аналогового сумматора 3, а значит, на первом входе усилителя 5 присутствует опорное напряжение U ef (с первого выхода источника 1 постоянного опорного напряжения), величина которого выбирается из соотношения

42

00

00 00

и.

Urns d

d

К

К,

14818804

Формула изобретения

1 . Каскад преобразования, содержащий триггер Шмитта, вход которого является входной шиной, а выход является цифровой выходной шиной, и подключен к управляющему входу управляемого аттенюатора, выход которого подключен к первому входу усилителя, вы- Ю ход которого является аналоговой выходной шиной, отличающийся тем, что, с целью повышения быстродействия и точности каскада, в него введены аналоговый сумматор и источник

где UMS Uf + U,t,

d - коэффициент деления включенного управляемого аттенюатора 4;

К t и К ,j - коэффициенты передачи по первой и второй ветвям амплитудной характеристики преобразователя,

При этом на выходе усилителя 5 будет нулевой уровень, так как величина опорного напряжения U , снимаемого с второго выхода источника 1 по-15 постоянного опорного напряжения, первый выход которого соединен с вторым

стоянного опорного напряжения и по- ступающегб на второй вход усилителя 5, выбирается из соотношения

0.

U

от U ог

входом усилителя, второй выход - с первым входом аналогового сумматора, второй вход которого является входной

20 шиной, а выход подключен к информационному входу управляемого аттенюатора.

При поступлении на вход устройства сигналов с уровнем UX4U1 каскад работает с максимальным коэффициентом передачи . 2 а,б,в,г, 3 а,б,в,г)

При уровне входного сигнала U , срабатывает триггер Шмитта 2, коэффициент передачи управляемого аттенюатора 4 уменьшается в d раз. При этом амплитуда сигнала на выходе управляемого аттенюатора 4 становится равной U 01, а на выходе усилителя 5 - нулю (фиг. 2 и 3).

При уровнях входного сигнала Ux U, с выхода усилителя 5 снимается усиленная в К2 раз разность входного Оки опорного U 01 сигналов .

на транзисторе, трех резисторах и конденсаторе, первый вьюод которого объединен с первым выводом первого

Таким образом, в предлагаемом каскаде по сравнению с известным отпада- 40 Резистора и является управляющим вхо- ет необходимость формирования и вы-Д м блока, второй выход конденсатора

объединен с вторым выводом первого резистора и подключен к базе транчитания импульсного опорного напряжения из входного сигнала и их временной синхронизации. В результате

зистора, эмиттер которого является

входом усилителя, второй выход - с первым входом аналогового сумматора, второй вход которого является входной

шиной, а выход подключен к информационному входу управляемого аттенюатора.

2. Каскад преобразования по п. I, отличающийс я тем, что, в

нем аналоговый сумматор выполнен на эмиттерном повторителе,база транзистора которого является первым и вторым входами блока, эмиттер является выходом блока и через резистор подключен к шине питания отрицательной полярности, шина питания положительной полярности соединена с Коллектором транзистора.

3. Каскад, преобразования по п. I , отлич ающийс я тем, что- в нем управляемый аттенюатор выполнен

на транзисторе, трех резисторах и конденсаторе, первый вьюод которого объединен с первым выводом первого

Резистора и является управляющим вхо блока, второй выход конденсатора

зистора, эмиттер которого является

| название | год | авторы | номер документа |

|---|---|---|---|

| Логарифмический преобразователь напряжения в двоичный код | 1989 |

|

SU1709523A1 |

| Импульсный стабилизатор постоянного напряжения | 1991 |

|

SU1820944A3 |

| Функциональный преобразователь напряжения в двоичный код | 1982 |

|

SU1051704A1 |

| Логарифмический преобразователь | 1979 |

|

SU801002A1 |

| Программный генератор | 1982 |

|

SU1062858A2 |

| Устройство для определения частоты основного резонанса головки громкоговорителя | 1985 |

|

SU1415471A1 |

| Устройство широкодиапазонного логарифмического аналого-цифрового преобразования | 1988 |

|

SU1571763A1 |

| Программный генератор | 1983 |

|

SU1190484A1 |

| Програмный генератор | 1979 |

|

SU873388A1 |

| Программный генератор периодических сигналов и постоянных напряжений а.и.кантера | 1978 |

|

SU790154A1 |

Изобретение относится к усилительной технике. Цель изобретения - повышение быстродействия и точности устройства. Цель достигается тем, что в известное устройство, содержащее триггер Шмитта, вход которого является входом устройства, и последовательно соединенные управляемый аттенюатор, второй вход которого соединен с выходом триггера Шмитта и цифровым выходом устройства, и усилитель, выход которого является аналоговым выходом устройства, дополнительно введены аналоговый сумматор, первый вход которого подключен к входу триггера Шмитта, а выход - к первому входу управляемого аттенюатора, и источник постоянного опорного напряжения, первый и второй выходы которого соединены с вторыми входами соответственно аналогового сумматора и усилителя. 2 з.п. ф-лы, 4 ил.

повышается быстродействие и точностьAS °бЩЈй шиной, а коллектор подключен воспроизведения линейно-ступенчатойк первому вьюоду второго резистора,

АХ, а также упрощается настройка.второй вывод которого является выПредлагаемый каскад преобразо-ходом блока и подключен к первому

вания легко реализуем. В качествевьюоду третьего резистора, второй выпримера на фиг. 4 приведена схема одного из вариантов построения.

50

вод которого является информационным входом блока.

- - -- --

дыход „Цифра

Фиг.1

Фи&2

иг их

Ј(/

О,

О

и

ч

Ui

I

/

с/

/ L i;Л

Фю.З

Фие.Ь

| Цифровые электроизмерительные приборы./Под ред.,В.М | |||

| Контрольный висячий замок в разъемном футляре | 1922 |

|

SU1972A1 |

| Затвор для дверей холодильных камер | 1920 |

|

SU182A1 |

| Очаг для массовой варки пищи, выпечки хлеба и кипячения воды | 1921 |

|

SU4A1 |

| Функциональный преобразователь напряжения в двоичный код | 1982 |

|

SU1051704A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1989-05-23—Публикация

1987-02-24—Подача