Ј

оо оо

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для цифровой фильтрации | 1983 |

|

SU1095357A1 |

| Цифровой фильтр | 1987 |

|

SU1390784A1 |

| Многочастотный цифровой фильтр | 1987 |

|

SU1474827A1 |

| Цифровой фильтр | 1980 |

|

SU904201A1 |

| Цифровой фильтр | 1988 |

|

SU1566469A1 |

| СИНТЕЗАТОР ЧАСТОТ | 1997 |

|

RU2137287C1 |

| Способ обнаружения и оценивания характеристик широкополосных сигналов и устройство для его реализации | 2023 |

|

RU2814220C1 |

| Специализированный процессор для цифровой фильтрации | 1989 |

|

SU1631558A1 |

| МНОГОКАНАЛЬНЫЙ ПЕРЕПРОГРАММИРУЕМЫЙ ЦИФРОВОЙ ПРИЕМНЫЙ ТРАКТ | 2004 |

|

RU2289202C2 |

| Цифровой нерекурсивный фильтр | 1985 |

|

SU1270876A1 |

Изобретение относится к вычислительной технике. Цель изобретения - повышение быстродействия. Устройство содержит фильтр 1 нижних частот, АЦП 2, коммутаторы 3 и 7, блок памяти 4, умножитель 5, накапливающий сумматор 6 , блок синхронизации 8, блок постоянной памяти 9 и мультиплексор 10. В устройстве осуществляется октавный частотный анализ с постоянной относительной шириной диапазонов и значениями среднегеометрических частот и границ соседних частотных диапазонов, отличающихся в два раза. Использован метод прореживания входных отсчетов по времени со смещением. Цель достигается введением мультиплексора 10, определяющего с какого блока коммутируется исходная информация: с выхода блока памяти 4 или с выхода умножителя 5. При этом умножитель 5 и сумматор 6 по сигналам блока синхронизации 8 выполняют обработку в соответствии со структурой, выбранной прямой формы нерекурсивного полосового фильтра. Даны ил. выполнения коммутатора 3, блока синхронизации 8 и мультиплексора 10. 5 ил.

го

Изобретение относится к вычислительной технике и предназначено для использования в устройствах многодиапазонного частотного анализа сигналов с постоянной относительной шириной полос пропускания и является усовершенствованием изобретения по авт. св. № 1095357.

Цель изобретения - повышение бы- стродействия (при использовании в полосовых фильтрах передаточной функци с симметричными весовыми коэффициентами) .

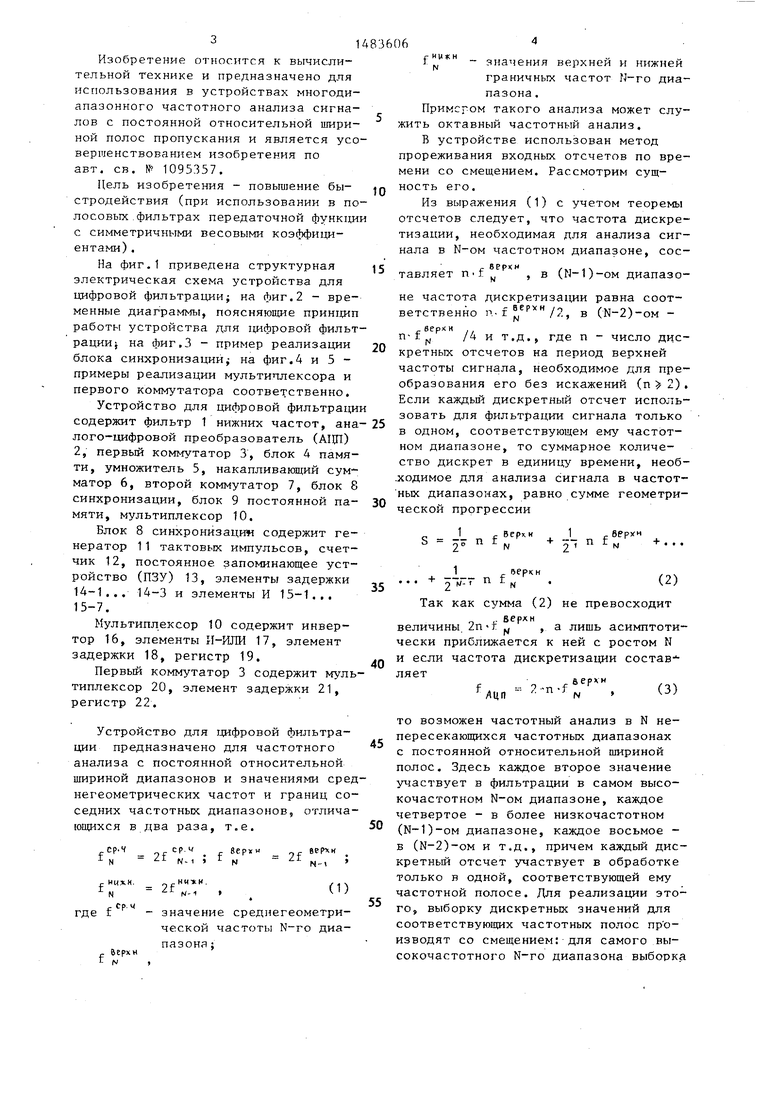

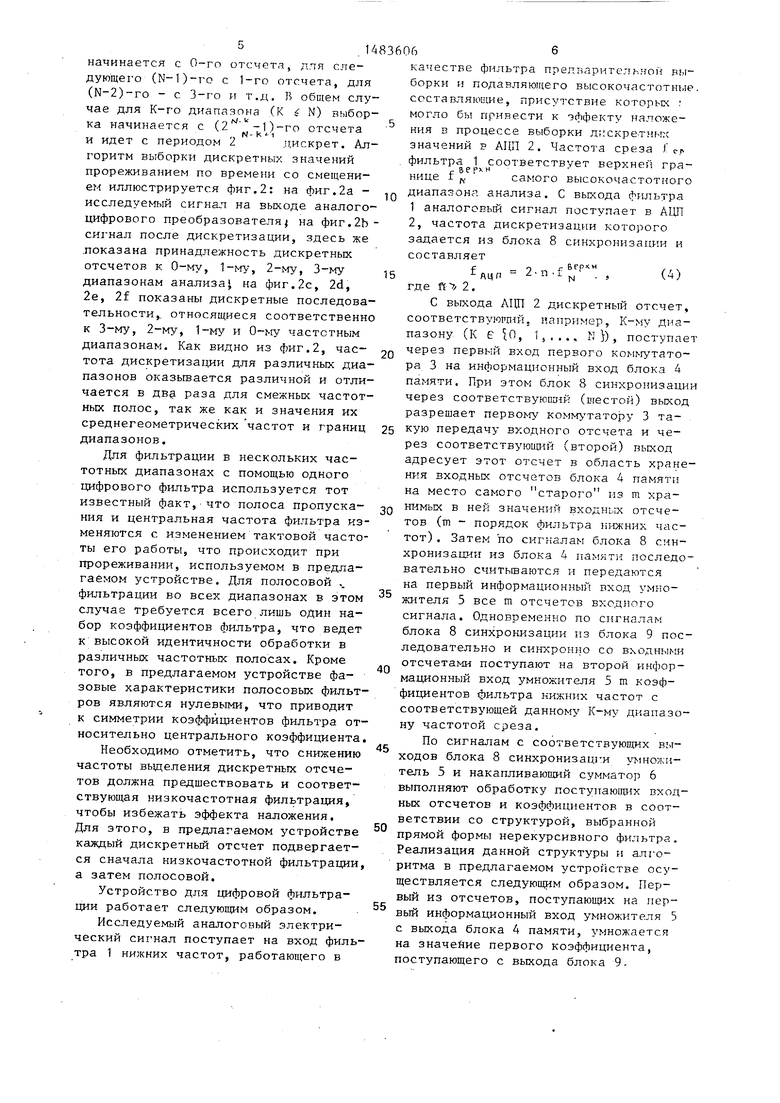

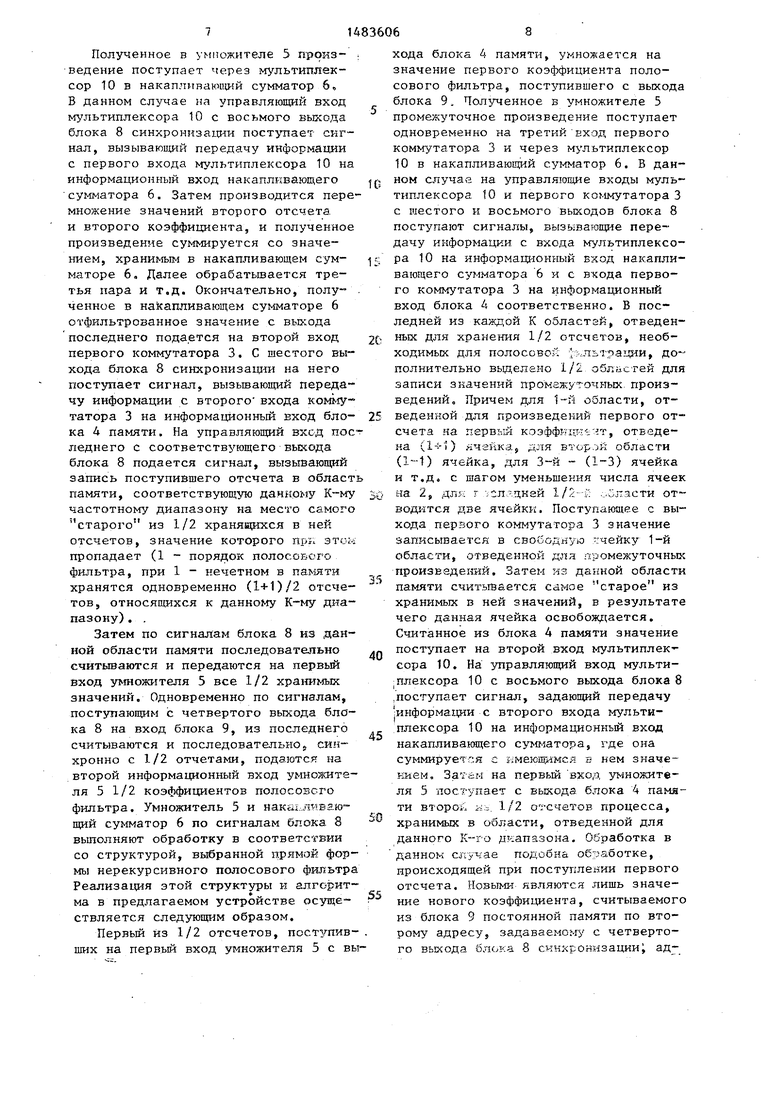

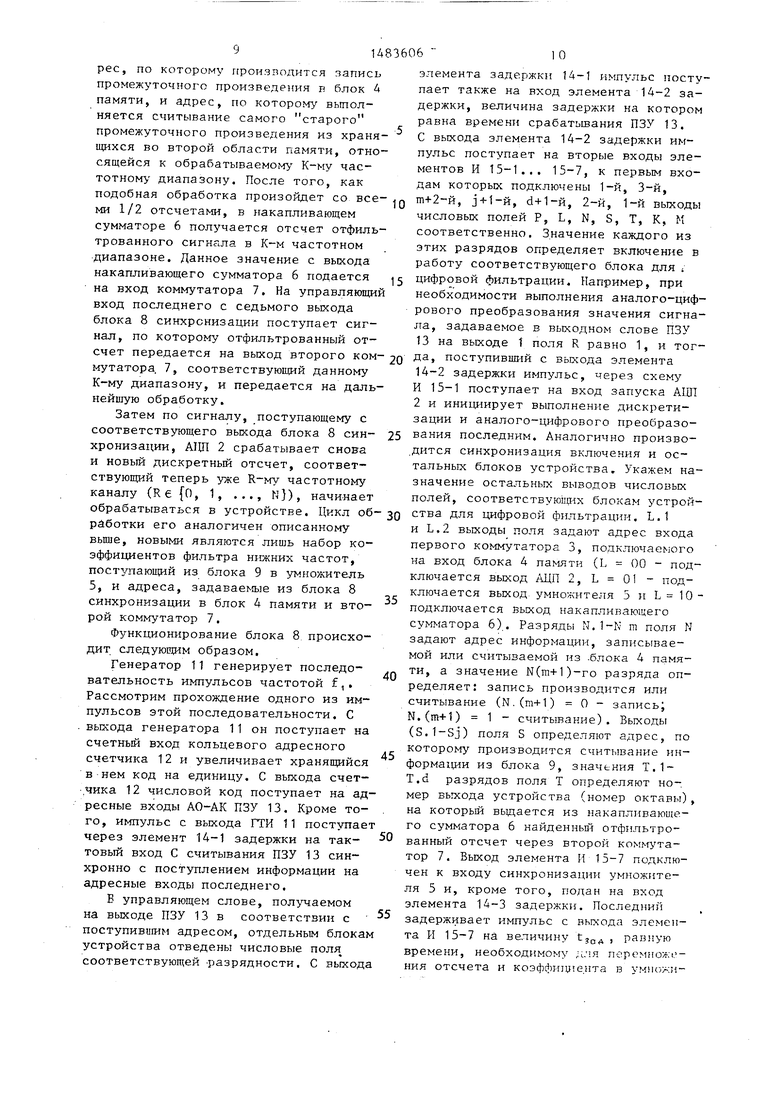

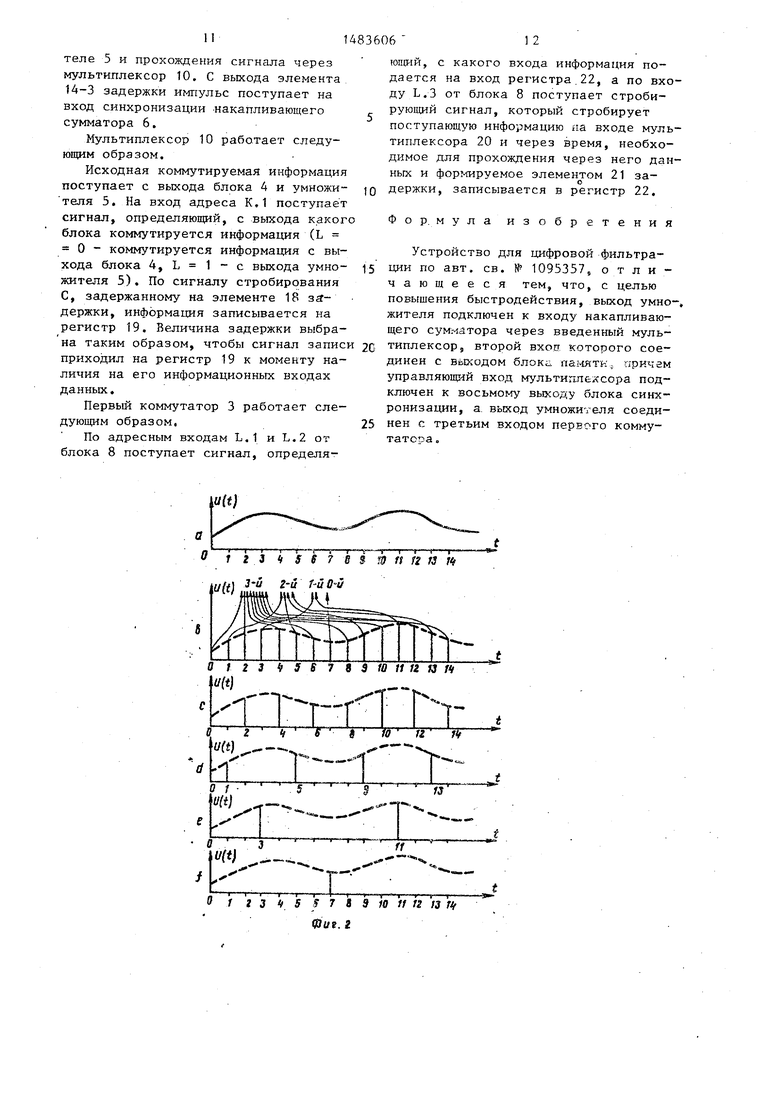

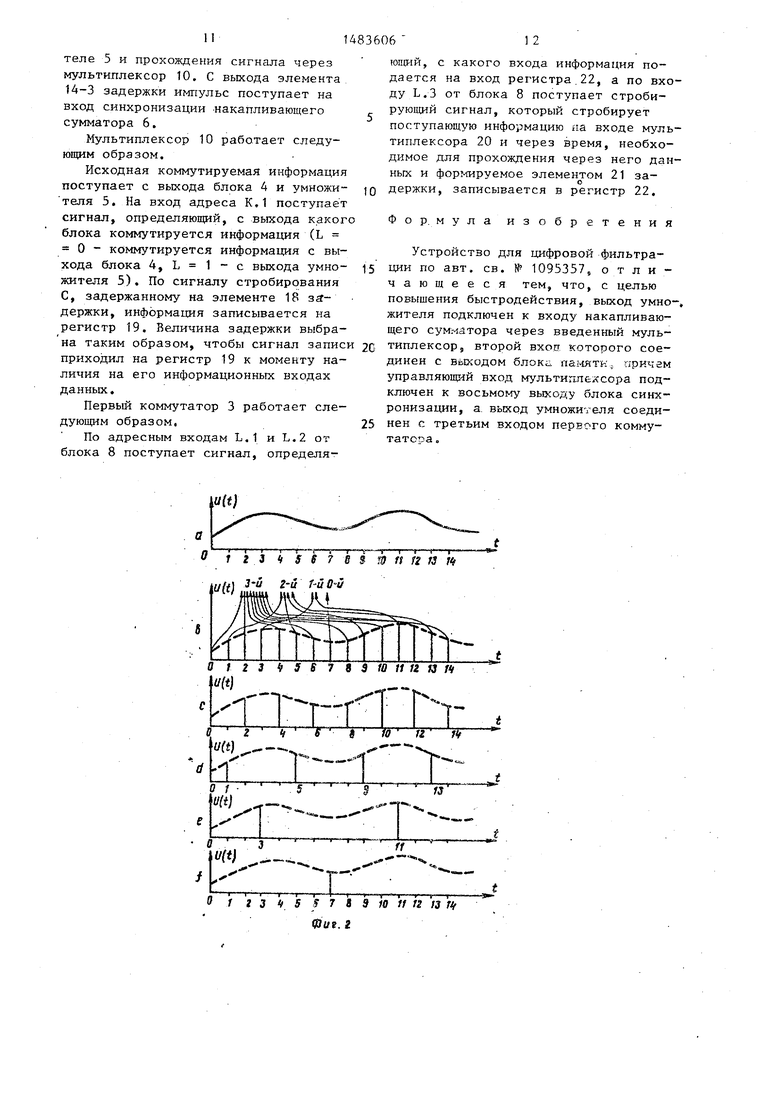

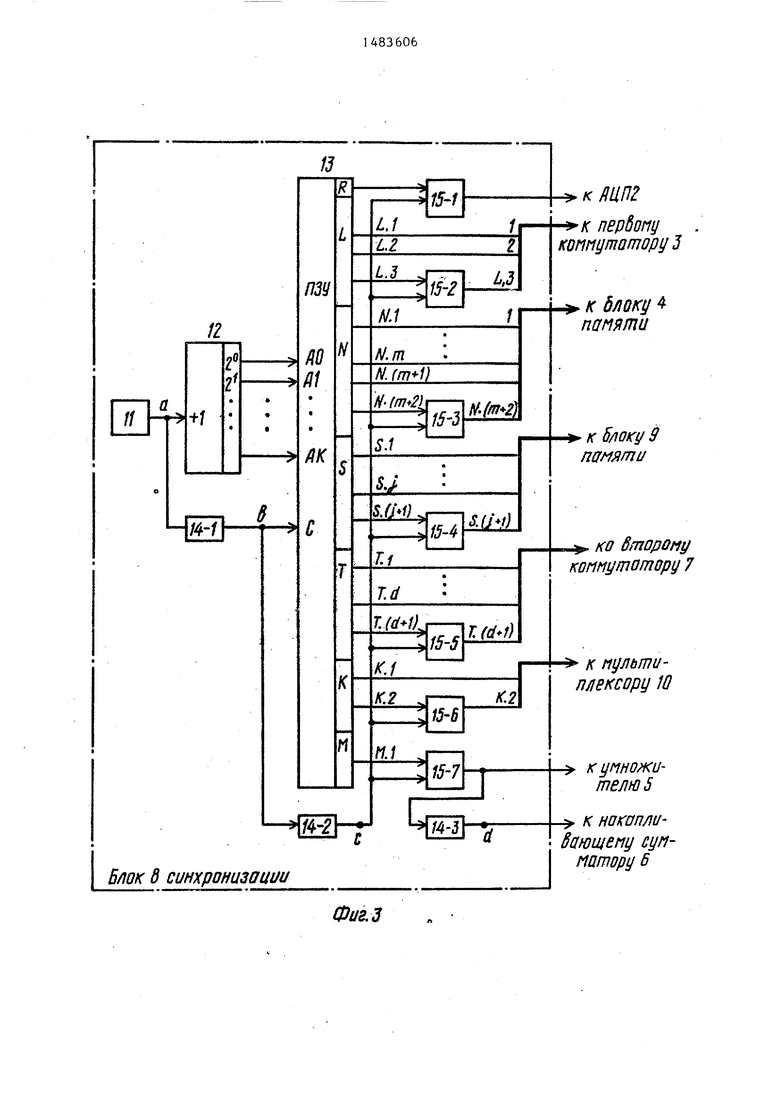

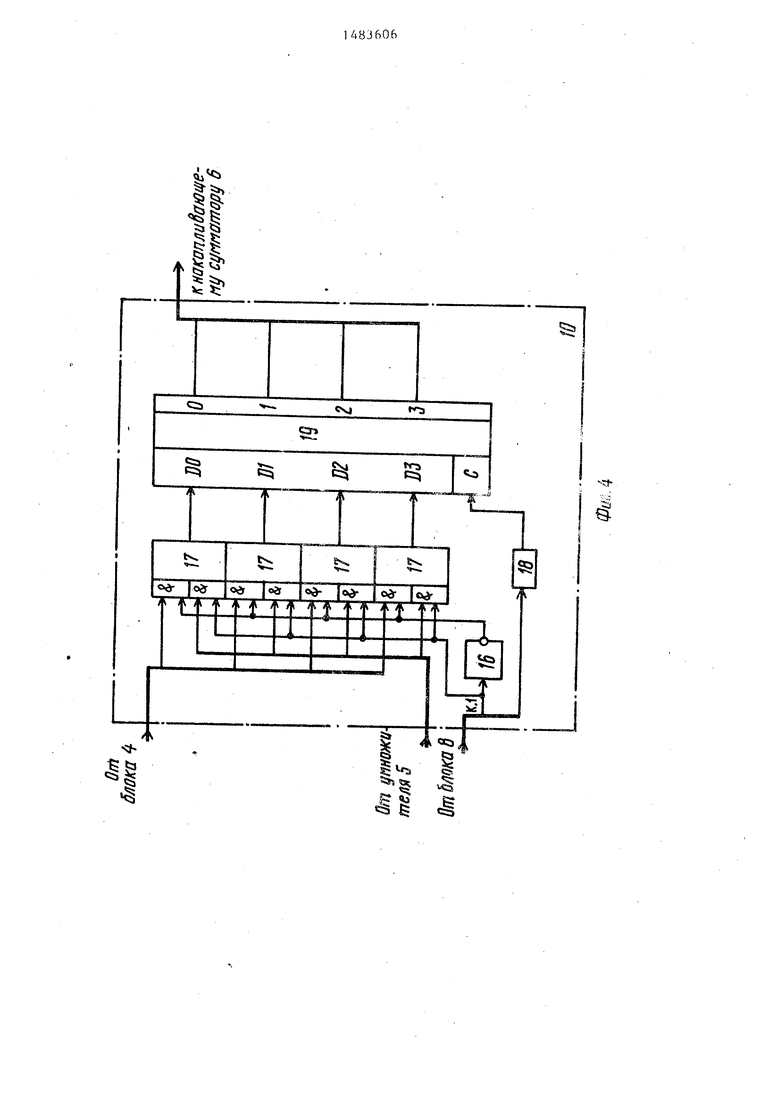

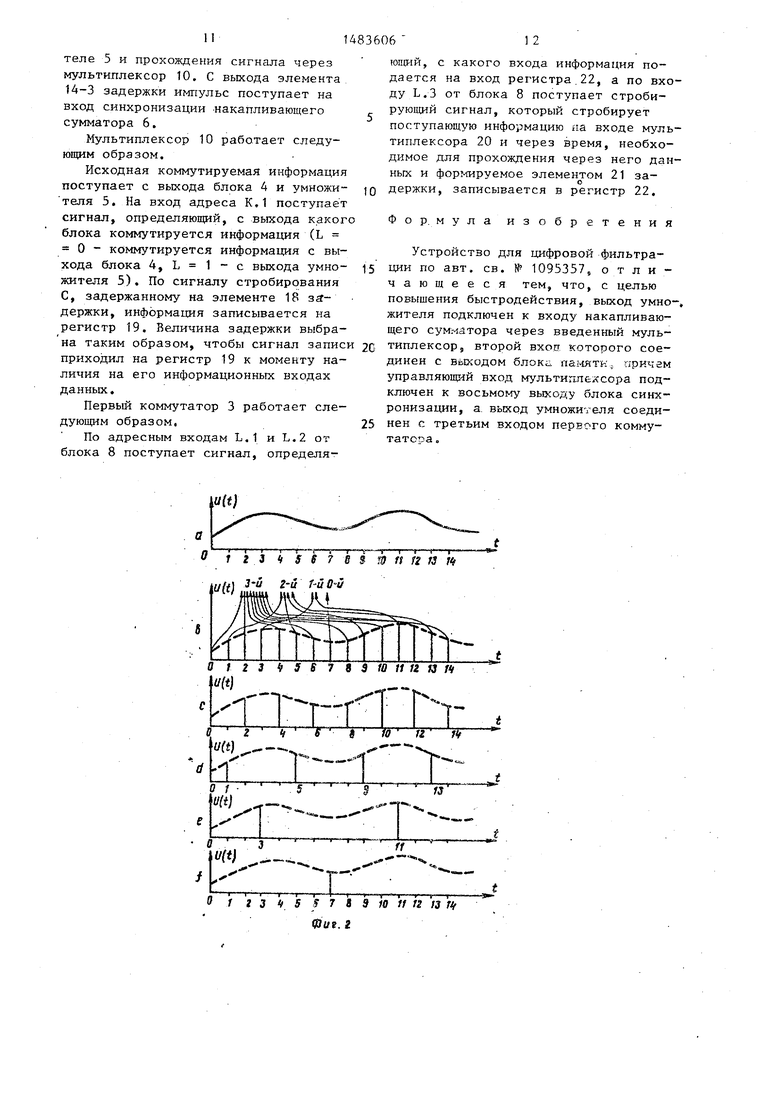

На фиг.1 приведена структурная электрическая схема устройства для цифровой фильтрации; на фиг.2 - временные диаграммы, поясняющие принцип работы устройства для цифровой фильт рацш-ц на фиг.З - пример реализации блока синхронизации; на фиг.4 и 5 - примеры реализации мультиплексора и первого коммутатора соответственно.

Устройство для цифровой фильтраци содержит фильтр 1 нижних частот, ана лого-цифровой преобразователь (А1Щ) 2, первый коммутатор 3, блок 4 памяти, умножитель 5, накапливающий сумматор 6, второй коммутатор 7, блок 8 синхронизации, блок 9 постоянной па- мяти, мультиплексор 10.

Блок 8 синхронизации содержит генератор 11 тактовых импульсов, счетчик 12, постоянное запоминающее устройство (ПЗУ) 13, элементы задержки 14-1... 14-3 и элементы И 15-1... 15-7.

Мультиплексор 10 содержит инвертор 16, элементы И-ИЛИ 17, элемент задержки 18, регистр 19.

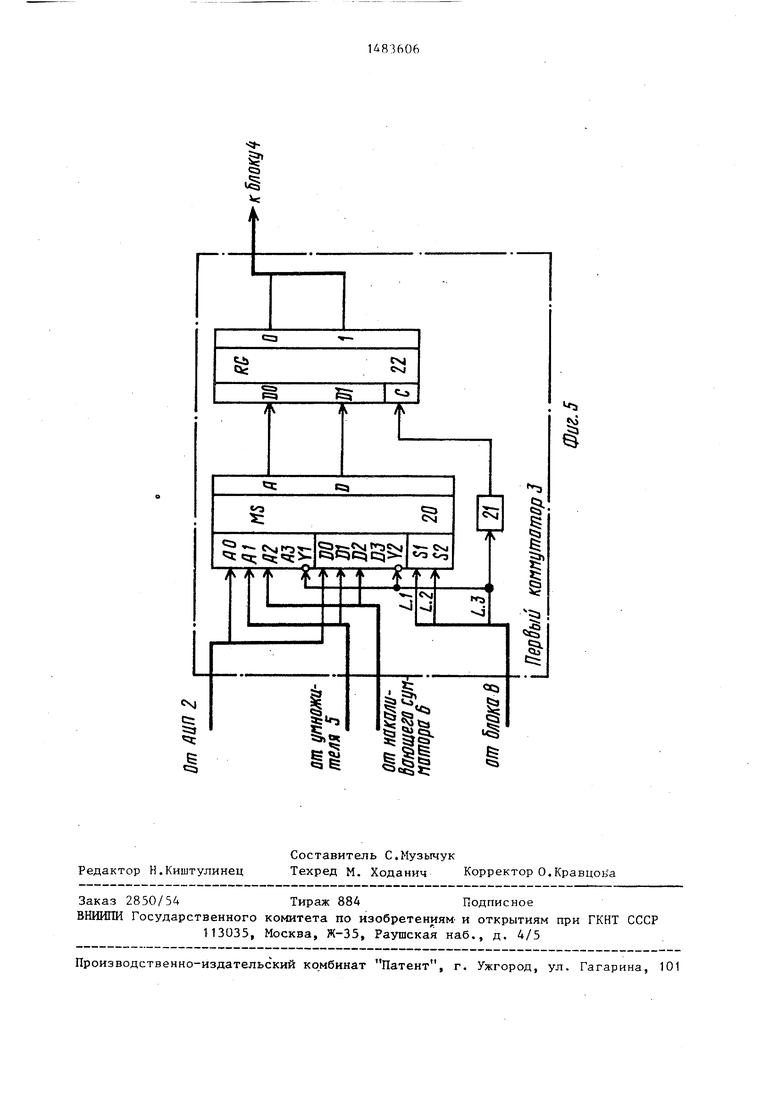

Первый коммутатор 3 содержит мультиплексор 20, элемент задержки 21, регистр 22.

45

Устройство для цифровой фильтрации предназначено для частотного анализа с постоянной относительной шириной диапазонов и значениями среднегеометрических частот и границ соседних частотных диапазонов, отличающихся в два раза, т.е.50

fCf-ч 9ггсРч . г вер 94г верхи „

1 N Zt N-I Т N- ZI м,

N-1

г ННХН г, с. НИХН

NN-1

. Ср Ч

(1)

где ч - значение среднегеометрической частоты N-ГО диапазона ; , берхн г N ,

с,,ачения верхней и нижней граничных частот N-ro диапазона .

Примером такого анализа может служить октавный частотный анализ.

В устройстве использован метод прореживания входных отсчетов по времени со смещением. Рассмотрим сущность его.

Из выражения (1) с учетом теоремы отсчетов следует, что частота дискретизации, необходимая для анализа сигнала в N-OM частотном диапазоне, сосверхн

тавляет n f

N

, в (N-I)-OM диапазоне частота дискретизации равна соответственно n.f ерхн/2, в (Ы-2)-ом n-f

верхи

N /4 и т.д., где п - число дискретных отсчетов на период верхней частоты сигнала, необходимое для преобразования его без искажений (п 2). Если каждый дискретный отсчет использовать для фильтрации сигнала только в одном, соответствующем ему частотном диапазоне, то суммарное количество дискрет в единицу времени, необходимое для анализа сигнала в частотных диапазонах, равно сумме геометрической прогрессии

S-jVnfJ + +..

1

+ JIT- n fн

веркн

(2)

0

5

0

5

Так как сумма (2) не превосходит

верхи

величины /п-г , а лишь асимптотически приближается к ней с ростом N и если частота дискретизации состав-1ляет

fо „

ДЦП n f (3)

то возможен частотный анализ в N непересекающихся частотных диапазонах с постоянной относительной шириной полос. Здесь каждое второе значение участвует в фильтрации в самом высокочастотном N-OM диапазоне, каждое четвертое - в более низкочастотном (N-1)-oM диапазоне, каждое восьмое - Б (Ы-2)-ом и т.д., причем каждый дискретный отсчет участвует в обработке только в одной, соответствующей ему частотной полосе. Для реализации этого, выборку дискретных значений для соответствующих частотных полос производят со смещением: для самого высокочастотного N-ro диапазона выборка

начинается с 0-го ОТСЧРТЛ, дчя следующего (N-l)-ro с 1-го отсчета, для (М-2)го - с 3-го и т.д. В общем случае для К-го диапазона (К & N) выборка начинается с (2м -П-го отсчета и идет с периодом 2 дискрет. Алгоритм выборки дискретных значений прореживанием по времени со смещением иллюстрируется фиг.2: на фиг.2а - исследуемый сигнал на выходе аналого- цифрового преобразователяj на фиг.2Ь- сигнал после дискретизации, здесь же показана принадлежность дискретных отсчетов к 0-му, 1-му, 2-му, 3-му диапазонам анализа на фиг.2с, 2d, 2е, 2f показаны дискретные последовательности, относящиеся соответственно к 3-му, 2-му, 1-му и 0-му частотным диапазонам. Как видно из фиг.2, частота дискретизации для различных диапазонов оказывается различной и отличается в два раза для смежных частотных полос, так же как и значения их среднегеометрических частот и границ диапазонов.

Для фильтрации в нескольких частотных диапазонах с помощью одного цифрового фильтра используется тот известный факт, что полоса пропускания и центральная частота фильтра изменяются с изменением тактовой частоты его работы, что происходит при прореживании, используемом в предлагаемом устройстве. Для полосовой ,. фильтрации во всех диапазонах в этом случае требуется всего лишь один набор коэффициентов фильтра, что ведет к высокой идентичности обработки в различных частотных полосах. Кроме того, в предлагаемом устройстве фазовые характеристики полосовых фильтров являются нулевыми, что приводит к симметрии коэффициентов фильтра относительно центрального коэффициента.

Необходимо отметить, что снижению частоты выделения дискретных отсчетов должна предшествовать и соответствующая низкочастотная фильтрация, чтобы избежать эффекта наложения. Для этого, в предлагаемом устройстве каждый дискретный отсчет подвергается сначала низкочастотной фильтрации, а затем полосовой.

Устройство для цифровой фильтрации работает следующим образом.

Исследуемый аналоговый электрический сигнал поступает на вход фильтра 1 нижних частот, работающего в

0

5

0

5

0

5

0

5

0

5

качестве фильтра предварительной выборки и подавляющего высокочастотные, составляющие, присутствие которых могло бы привести к эффекту наложения в процессе выборки д::скретны;с значений р АЦП 2. Частота среза fсс

фильтра 1 соответствует верхней граснице г самого высокочастотного

диапазона анализа. С выхода фильтра 1 аналоговый сигнал поступает в АЦП 2, частота дискретизации которого задается из блока 8 синхронизации и составляет

f- 9 ,-, ,

Г АЦП - Z n N J{+)

где 2.

С выхода АЦП 2 дискретный отсчет, соответствующий, например, К-му Диапазону (К е (}, 1,..., N }) , поступает через первый вход первого коммутатора 3 на информационный вход блока 4 памяти. При этом блок 8 синхронизации через соответствующий (шестой) выход разрешает первому коммутатору 3 такую передачу входного отсчета и через соответствующий (второй) выход адресует этот отсчет в область хранения входных отсчетов блока 4 памяти на место самого старого из m хранимых в ней значений входных отсчетов (т - порядок фильтра нижних частот) . Затем по сигналам блока 8 синхронизации из блока 4 памяти последовательно считываются и передаются на первый информационный вход умножителя 5 все m отсчетов входного сигнала. Одновременно по сигналам блока 8 синхронизации из блока 9 последовательно и синхронно со входными отсчетами поступают на второй информационный вход умножителя 5 m коэффициентов фильтра нижних частот с соответствующей данному К-му диапазону частотой среза.

По сигналам с соответствующих выходов блока 8 синхронизацги умножитель 5 и накапливающий сумматор 6 выполняют обработку поступающих входных отсчетов и коэффициентов в соответствии со структурой, выбранной прямой формы нерекурсивного фильтра. Реализация данной структуры и алгоритма в предлагаемом устройстве осуществляется следующим образом. Первый из отсчетов, поступающих на первый информационный вход умножителя 5 с выхода блока 4 памяти, умножается на значение первого коэффициента, поступающего с выхода блока 9Полученное в умножителе 5 произведение поступает через мультиплексор 10 в накапливающий сумматор 6, В данном случае на управляющий вход мультиплексора 10 с восьмого выхода блока 8 синхронизации поступает сигнал, вызывающий передачу информации с первого входа мультиплексора 10 на информационный вход накапливающего сумматора 6. Затем производится перемножение значений второго отсчета и второго коэффициента, и полученное произведение суммируется со значением, хранимым в накапливающем сумматоре 6, Далее обрабатывается третья пара и т.д. Окончательно, полу™ ченное в накапливающем сумматоре 6 отфильтрованное значение с выхода последнего подается на второй вход первого коммутатора 3. С шестого выхода блока 8 синхронизации на него поступает сигнал, вызывающий передачу информации с второго входа коммутатора 3 на информационный вход блока 4 памяти. На управляющий вхсд последнего с соответствующего выхода блока 8 подается сигнал, вызывающий запись поступившего отсчета в област памяти, соответствующую дачному К-му частотному диапазону на место самого старого из 1/2 хранящихся в ней отсчетов, значение которого пр. зтс;-. пропадает (1 - порядок полосового фильтра, при 1 - нечетном в памяти хранятся одновременно (1-4-1)72 отсчетов, относящихся к данному К-му диапазону) . .

Затем по сигналам блока 8 из данной области памяти последовательно считываются и передаются на первый вход умножителя 5 все 1/2 хранимых значений. Одновременно по сигналам, поступающим с четвертого выхода блока 8 на вход блока 9, из последнего считываются и последовательно,, синхронно с 1 /2 отчетами, подаются на второй информационный вход умножителя 5 1/2 коэффициентов полосовсго фильтра. Умножитель 5 и накс -Л вакг- щий сумматор 6 по сигналам блока 8 выполняют обработку в соответствии со структурой, выбранной прямо формы нерекурсивного полосового фильтра Реализация этой структуры и алгоритма в предлагаемом устройстве осуществляется следующим образом.

Первый из 1/2 отсчетов, поступив- ших на первый вход умножителя 5 с выС

:0

5

5

0

5

5

хода блока 4 памяти, умножается на значение первого коэффициента полосового фильтра, поступившего с выхода блока 9. Полученное в умножителе 5 промежуточное произведение поступает одновременно на третий вход первого коммутатора 3 и через мультиплексор 10 в накапливающий сумматор 6. В данном случае на управляющие входы мультиплексора 10 и первого коммутатора 3 с шестого и восьмого выходов блока 8 поступают сигналы, вызь.ва -ощие передачу информации с входа мультиплексора 10 на информационный вход накапливающего сумматора бис входа первого коммутатора 3 на информационный вход блока 4 соответственно. В последней из каждой К областей, отведенных для хранения 1/2 отсчетов, необходимых для полоссвс,. , до полнительно выделано 1/2 областей для записи значений промежуточных произведений. Причем для 1-й области, отведенной для произведений первого отсчета на первой кэзфф -.цг- гг, отведена (1--1) «чгикз, ля в op JK области (1-1) ячейка, для 3-й - (1-3) ячейка и т.д. с шагом уменьшения числа ячеек на 2, цл - ел т;кай 1/1 ,г1сти отводится две ячейки. Поступающее с выхода первого коммутатора 3 значение записывается в своСодн.о ™чейку 1-й области, отведенной для ; - омежуточных произведений. Затем -г данной области памяти считывается самое старое из хранимых в ней значений, в результате чего данная ячейка освобождается. Считанное из блока 4 памяти значение поступает на второй вход мультиплексора 10. На управляющий вход мультиплексора 10с восьмого выхода блока 8 поступает сигнал, задающий передачу информации с второго входа мультиплексора 10 на информационный вход накапливающего сумматора, где она суммирует я с имеющимся в ьем значением. на первый вхол умножителя 5 лос - пает с выхода блока 4 памяти вторе, „ . 1/2 о .-счетор процесса, хранимых в области, отведенной для данного Кто диапазона. Обработка в данном случае подобна об З.ботке, происходящей при поступлении первого отсчета. Новыми являются лишь значение нового коэффициента, считываемого из блока 9 постоянной памяти по второму адресу, задаваемому с четвертого выхода 8 скчхроьлзации; ад

pec, no которому производится запись промежуточного произведения н блок 4 памяти, и адрес, по которому выполняется считывание самого старого промежуточного произведения из хранящихся во второй области памяти, относящейся к обрабатываемому К-му частотному диапазону. После того, как подобная обработка произойдет со всеми 1/2 отсчетами, в накапливающем сумматоре 6 получается отсчет отфильтрованного сигнала в К-м частотном диапазоне. Данное значение с выхода накапливающего сумматора 6 подается на вход коммутатора 7. На управляющий вход последнего с седьмого выхода блока 8 синхронизации поступает сиг15 цифровой фильтрации. Например, при необходимости выполнения аналого-ци рового преобразования значения сигн ла, задаваемое в выходном слове ПЗУ 13 на выходе 1 поля R равно 1, и то

нал, по которому отфильтрованный отсчет передается на выход второго ком- 2Q Да поступивший с выхода элемента мутатора 7, соответствующий данному 14-2 задержки импульс, через схему К-му диапазону, и передается на дальнейшую обработку.

Затем по сигналу, поступающему с соответствующего выхода блока 8 син- 25 хронизации, А1Щ 2 срабатывает снова

И 15-1 поступает на вход запуска АЦ 2 и инициирует выполнение дискрети зации и аналого-цифрового преобразо вания последним. Аналогично произво дится синхронизация включения и остальных блоков устройства. Укажем н значение остальных выводов числовых полей, соответствующих блокам устро

и новый дискретный отсчет, соответствующий теперь уже R-му частотному каналу (Re (0, 1, ..., N}), начинает

35

40

обрабатываться в устройстве. Цикл 06-30 ства для цифровой фильтрации. L.1 работки его аналогичен описанному выше, новыми являются лишь набор коэффициентов фильтра нижних частот, поступающий из блока 9 в умножитель 5, и адреса, задаваемые из блока 8 синхронизации в блок 4 памяти и второй коммутатор 7.

Функционирование блока 8 происходит следующим образом.

Генератор 11 генерирует последовательность импульсов частотой f,. Рассмотрим прохождение одного из импульсов этой последовательности. С выхода генератора 11 он поступает на счетньй вход кольцевого адресного счетчика 12 и увеличивает хранящийся в нем код на единицу. С выхода счетчика 12 числовой код поступает на адресные входы АО-АК ПЗУ 13. Кроме того, импульс с выхода ГТИ 11 поступает через элемент 14-1 задержки на тактовый вход С считывания ПЗУ 13 синхронно с поступлением информации на адресные входы последнего,

В управляющем слове, получаемом на выходе ПЗУ 13 в соответствии с поступившим адресом, отдельным блокам устройства отведены числовые поля соответствующей -разрядности. С выхода

45

50

55

и L.2 выходы поля задают адрес вхо первого коммутатора 3, подключаемо на вход блока 4 памяти (L 00 - п ключается выход АЦП 2, L 01 - по ключается выход умножителя 5 и L подключается выход накапливающего сумматора 6). Разряды N.1-N m поля задают адрес информации, записывае мой или считываемой из .блока 4 пам ти, а значение N(m+1)-ro разряда о ределяет: запись производится или считывание (N.(m+1) 0 - запись; N.(т+1) 1 - считывание). Выходы (S.1-SJ) поля S определяют адрес, которому производится считывание и формации из блока 9, значения Т.1- T.d разрядов поля Т определяют но мер выхода устройства (номер октав на который выдается из накапливающ го сумматора 6 найденный отфильтро ванный отсчет через второй коммута тор 7. Выход элемента И 15-7 подкл чен к входу синхронизации умножите ля 5 и, кроме того, подан на вход элемента 14-3 задержки. Последний задерживает импульс с выхода элеме

та И 15-7 на величину времени, необходимому

tjo , равную

|.ля перемнож ния отсчета и коэффициента в умнох

606 -1 О

элемента задержки 14-1 импульс поступает также на вход элемента 14-2 задержки, величина задержки на котором равна времени срабатывания ПЗУ 13. С выхода элемента 14-2 задержки импульс поступает на вторые входы элементов И 15-1... 15-7, к первым входам которых подключены 1-й, 3-й,

JQ m+2-й, j-H-й, d+1-й, 2-й, 1-й выходы числовых полей Р, L, N, S, Т, К, М соответственно. Значение каждого из этих разрядов определяет включение в работу соответствующего блока для ,

15 цифровой фильтрации. Например, при необходимости выполнения аналого-цифрового преобразования значения сигнала, задаваемое в выходном слове ПЗУ 13 на выходе 1 поля R равно 1, и тогQ Да поступивший с выхода элемента 14-2 задержки импульс, через схему Да поступивший с выхода элемента 14-2 задержки импульс, через схему

И 15-1 поступает на вход запуска АЦП 2 и инициирует выполнение дискретизации и аналого-цифрового преобразования последним. Аналогично производится синхронизация включения и остальных блоков устройства. Укажем назначение остальных выводов числовых полей, соответствующих блокам устрой-

ства для цифровой фильтрации. L.1

и L.2 выходы поля задают адрес входа первого коммутатора 3, подключаемого на вход блока 4 памяти (L 00 - подключается выход АЦП 2, L 01 - подключается выход умножителя 5 и L 10- подключается выход накапливающего сумматора 6). Разряды N.1-N m поля N задают адрес информации, записываемой или считываемой из .блока 4 памяти, а значение N(m+1)-ro разряда определяет: запись производится или считывание (N.(m+1) 0 - запись; N.(т+1) 1 - считывание). Выходы (S.1-SJ) поля S определяют адрес, по которому производится считывание информации из блока 9, значения Т.1- T.d разрядов поля Т определяют номер выхода устройства (номер октавы), на который выдается из накапливающего сумматора 6 найденный отфильтрованный отсчет через второй коммутатор 7. Выход элемента И 15-7 подключен к входу синхронизации умножителя 5 и, кроме того, подан на вход элемента 14-3 задержки. Последний задерживает импульс с выхода элемента И 15-7 на величину времени, необходимому

tjo , равную

|.ля перемножения отсчета и коэффициента в умнохнтеле 5 и прохождения сигнала через мультиплексор 10. С выхода элемента 14-3 задержки импульс поступает на вход синхронизации накапливающего сумматора 6.

Мультиплексор 10 работает следующим образом.

Исходная коммутируемая информация

юший, с какого входа информация подается на вход регистра 22, а по входу L.3 от блока 8 поступает строби- рующий сигнал, который стробирует поступающую информацию аа входе мультиплексора 20 и через время, необходимое для прохождения через него данных и формируемое элементом 21 заО

поступает с выхода блока 4 и умножи- JQ держки, записывается в регистр 22. теля 5. На вход адреса К.1 поступает

сигнал, определяющий, с выхода какого Формула изобретения блока коммутируется информация (L

0 - коммутируется информация с вы- Устройство для цифровой фильтра- хода блока 4, L 1 - с выхода умно- )§ Ц™ по авт. св. № 1095357s о т л и - жителя 5). По сигналу стробирования чающееся тем, что, с целью С, задержанному на элементе 18 держки, информация записывается на

регистр 19. Величина задержки выбраповышения быстродействия, выход умно-, жителя подключен к входу накапливающего сумматора через введенный муль- на таким образом, чтобы сигнал записи 2С типлексор, второй вхоп KOTODoro coe- приходил на регистр 19 к моменту на- динен с выходом блок,- памяти „ причем

управляющий вход мультиплексора подключен к восьмому выходу блока синхронизации, а выход умножителя соеди- 25 нен с третьим входом первого комму- татстза.

личия на его информационных входах данных.

Первый коммутатор 3 работает следующим образом,

По адресным входам L.1 и L.2 от блока 8 поступает сигнал, определя-т-ет-г

О 1 2 3 Ц S S 7 § S W ft Гг 13 № им 3-й 1-й 1-UQ-U

6

о I г з s в 7 в а ю и гг a n

Угг-гп .

.-, J- Ј-, J-, JP Jj, fi,.,

т

fj

п

ft

.- -«ч..

I т |т f i

5 $ 7 i 9 ю н гг 13 т# УЗие.2

юший, с какого входа информация подается на вход регистра 22, а по входу L.3 от блока 8 поступает строби- рующий сигнал, который стробирует поступающую информацию аа входе мультиплексора 20 и через время, необходимое для прохождения через него дан-т-ет-г

§ S W ft

т

fj

ft

.- -«ч..

Влок д синхронизации

Фиг.3

КЛШ

к nepforty ко fin у та тор i/3

К 5ЛОК1/ 4

памяти

к а/югу 9 памяти

ко Второму копну то тору 7

к пдльти- ллексору 10

купножи- телюЗ

к покапли- Вающепу сун- пагпору б

Qm днножи- те т 5

Qm блокад

Фи 4

CNJ

I

a

I

| Устройство для цифровой фильтрации | 1983 |

|

SU1095357A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1989-05-30—Публикация

1987-07-06—Подача