ел

о о

4

О5 СО

Изобретение относится к радиотехнике и вычислительной технике и может быть использовано в устройствах многоканальной связи с цифровой обработкой сигналов.

Цель изобретения - повышение качества фильтрации за счет разделения групповых сигналов частотно-уплотненных каналов.

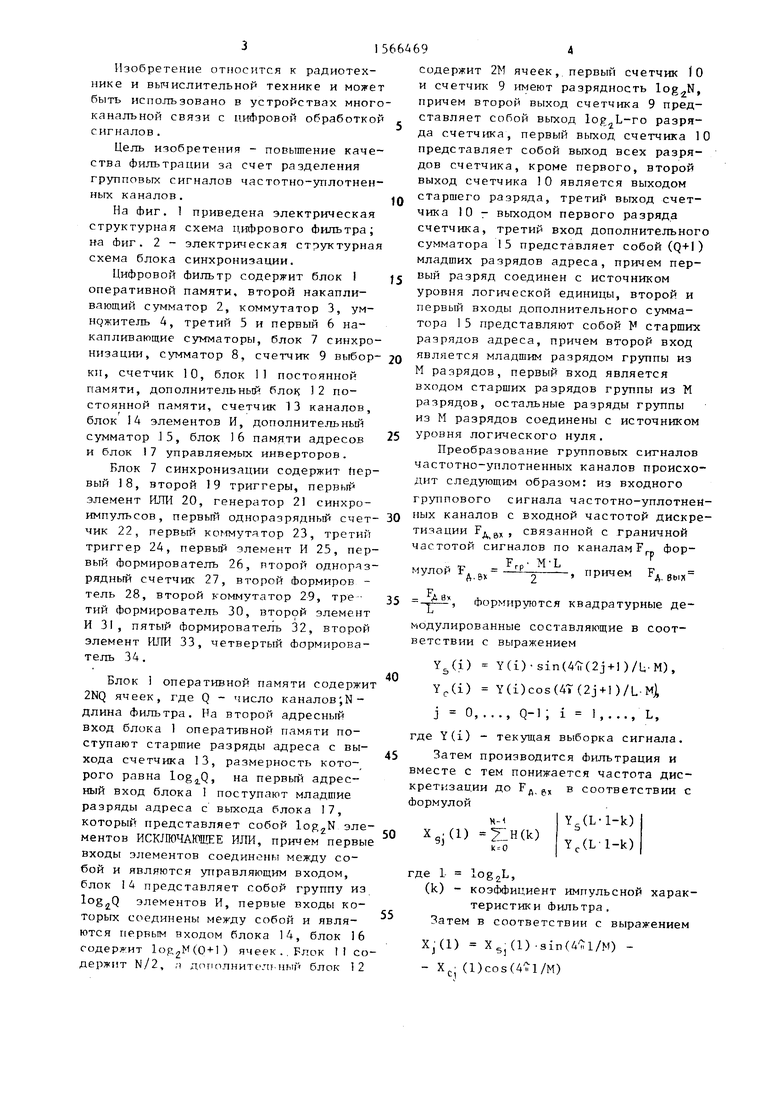

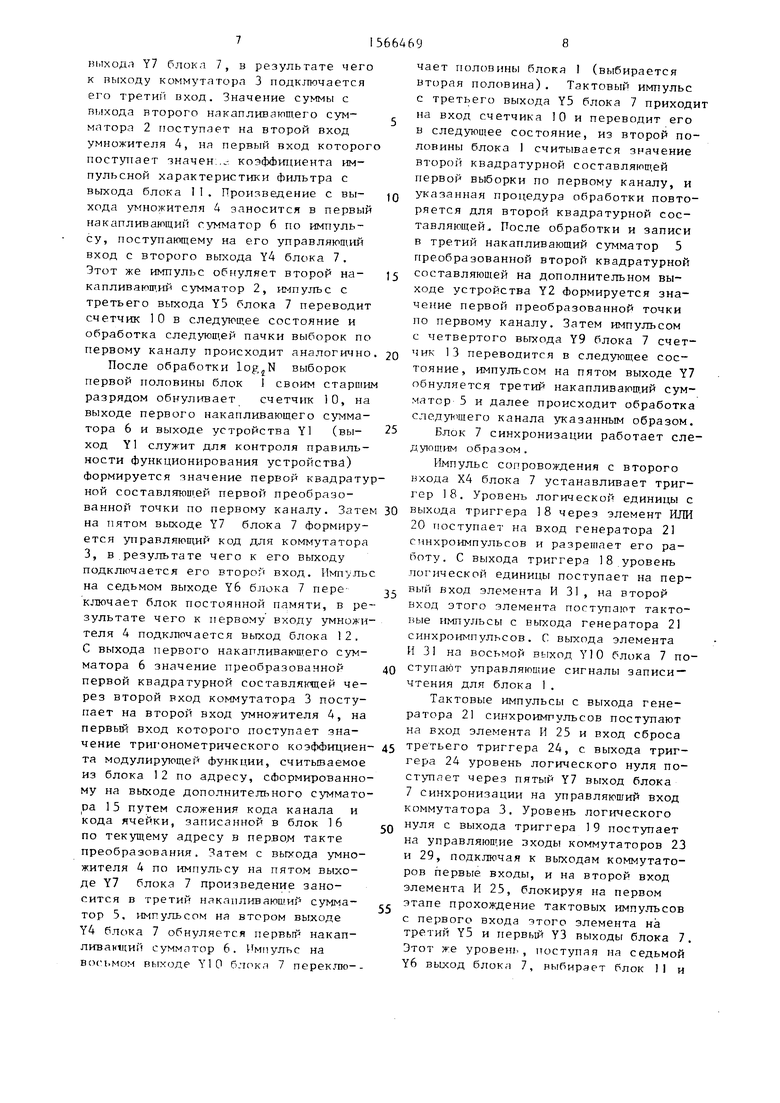

На фиг. 1 приведена электрическая структурная схема цифрового Фильтра; на Фиг. 2 - электрическая структурная схема блока синхронизации.

Цифровой фильтр содержит блок 1 оперативной памяти, второй накапливающий сумматор 2, коммутатор 3, ум- нджитель 4, третий 5 и первый 6 накапливающие сумматоры, блок 7 синхронизации, сумматор 8. счетчик 9 выбор- кп, счетчик 10, блок 11 постоянной памяти, дополнительный блок, 1 2 постоянной памяти, счетчик 13 каналов, блок 14 элементов И, дополнителъньй сумматор J5, блок 16 памяти адресов и блок 17 управляемых инверторов.

Блок 7 синхронизации содержит первый 18, второй 19 триггеры, первый элемент ИЛИ 20, генератор 21 синхроимпульсов, первый одноразрядный счет- чик 22, первый ког тмутатор 23, третий триггер 24, первый элемент И 25, первый формирователь 26, второй одноразрядный счетчик 27, второй Формиров - тель 28, второй коммутатор 29, тре тий формирователь 30, второй элемент И 31, пятый формирователь 32, второй элемент ИЛИ 33, четвертый Формирователь 34.

Блок 1 оперативной памяти содержит 2NQ ячеек, где Q - число каналов;N- длина фильтра. На второй адресный вход блока 1 оперативной памяти поступают старшие разряды адреса с выхода счетчика 13, размерность которого равна , на первый адресный вход блока 1 поступают младшие разряды адреса с выхода блока 17, который представляет собой log2N элементов ИСКЛЮЧАЮЩЕЕ ИЛИ, причем первые входы элементов соединены между собой и являются управляющим входом, блок 14 представляет собой группу из l°gЈQ элементов И, первые входы которых соединены между собой и являются первым входом блока 14, блок 16 содержит logzM(0-H) ячеек. Блок 11 содержит N/2, а дополнителтный блок 12

Q

5 0

0 5

5

содержит 2М ячеек, первый счетчик 10 и счетчик 9 имеют разрядность , причем второй выход счетчика 9 представляет собой выход log L-ro разряда счетчика, первый выход счетчика 10 представляет собой выход всех разрядов счетчика, кроме первого, второй выход счетчика 10 является выходом старшего разряда, третий выход счетчика 10 - выходом первого разряда счетчика, третий вход дополнительного сумматора 15 представляет собой (Q+1 ) младших разрядов адреса, причем первый разряд соединен с источником уровня логической единицы, второй и первый входы дополнительного сумматора 15 представляют собой V старших разрядов адреса, причем второй вход является младшим разрядом группы из М разрядов, первый вход является входом старших разрядов группы из М разрядов, остальные разряды группы из М разрядов соединены с источником уровня логического нуля.

Преобразование групповых сигналов частотно-уплотненных каналов происходит следующим образом: из входного группового сигнала частотно-уплотненных каналов с входной частотой дискретизации Рд вх, связанной с граничной частотой сигналов по каналам форf

FrP M-L

причем

д.вх 2 А-выл формируются квадратурные де

модулированные составляющие в соответствии с выражением

Y5(i) Y(i)-sin(4/n(2j + l)/U-M), Yc(i) Y(i)cos(47(2j + I)/L-M| j 0, ..., Q-l ; i 1,. ... L,

где Y(i) - текущая выборка сигнала.

Затем производится Фильтрация и вместе с тем понижается частота дискретизации до Гд Ј„ в соответствии с Формулой

9)

(1) ZlH(k) k 0

Y3(L-l-k) Yc(L l-k)

где 1 log2L,

(k) - коэффициент импульсной характеристики фильтра. Затем в соответствии с выражением

Xj(l) XS(1) ) - - Xcj (l)cos()

производится восстановление исходного сигнала для каждого канала. На вход цифрового фильтра поступает групповой сигнал частотно-уплотненных каналов, где содержится информация по каналам, каждый из которых находится на своей несущей частоте.

Цифровой фильтр работает следующим образом.

В исходном состоянии счетчики 9, 10,13, блок 16 и дополнительный сумматор 15 обнулены. На вход устройства XI поступает групповой сигнал частотно-уплотненных каналов, который сопровождается импульсами сопровождения на управляющем входе устройства Х2. Импульс сопровождения на управляющем входе X 2 переводит в следуюшее состояние счетчик 9 и поступает на второй вход Х4 блока 7, который начинает вырабатывать управляющие импульсы первого этапа отработки. На управляющий вход коммутатора 3 с пятого выхода Y7 блока 7 поступает управляющий код, в результате чего вход устройства X подключается к второму входу умножителя 4, первый вход которого подключен к выходу блока 12, в котором хранятся значения тригонометрических множителей модулирующей Функции. Результат умножения значения входной выборки на значение первой тригонометрической составляющей по импульсам, поступающим с восьмого выхода Y10 блока 7, заносится в первую половину блока 1 по адресу, сформированному на втором адресном входе счетчиком J3 и первом адресном входе сумматором 8 (адрес на выходе сумматора 8 равен адресу на первом выходе счетчика 9). Затем импульс с седьмого выхода Y6 блока 7 поступает на управляющий вход блока 12, в результате чего из указанного блока считывается значение второй тригонометрической составляющей, которое поступает на первый вход умножителя 4, с выхода которого произведение входной выборки на вторую тригонометрическую составляющую модулирующей функции заносится во вторую половину блока 1 по импульсам, поступающим с восьмого выхода YIO блока 7. Импульсы с шестого выхода Y8 блока 7 поступают на управляющие входы дополнительного сумматора 15, блока 16 и первый (инверсный вход) блока 14, открывая его. С первого выхода счетчика 13 код номера

0

0

5

обрабатываемого канала через второй вход блока 14 поступает на третий вход дополнительного сумматора 15, суммируется с содержанием блока 16 и заносится в блок 16 по тому же адресу (соответствует адресу считываемого из блока 12 значению тригонометрического коэффициента модулирующей функции, который используется для формирования квадратурных составляющих по данному каналу).

Затем тактовый импульс с четвертого выхода Y9 блока 7 переводит в сле- 5 дующее состояние счетчик 13 и обработка выборки по следующему каналу происходит аналогично.

После записи в блок 1 по Q каналам импульс с второго выхода счетчика 13 поступает на третий вход Х6 блока 7 и переводит устройство в режим ожидания до прихода следующего пмпулъсл сопровождения на управляющий вход Х2 устройства. По следующему импульсу сопровождения на этом входе уклчан ная процедура повторяется для следующей выборки по всем каналам. После обработки log2L выборок на втором выходе счетчика 9 формируется импульс, который поступает на четвертый вход Х5 блока 7 и переводит его в режим формирования управлявших сигналов второго этапа обработки. Счетчики 13 и 9 сбрасываются по заднему фронту своего старшего разряда.

На втором этапе обработки с третьего выхода Y5 блока 7 на вход счетчика 10 поступают тактовые импульсы, с выхода которого формируемые коды поступают на первый вход сумматора 8 и адресный вход блока 11. Те же тактовые импульсы с первого выхода Y3 блока 7 поступают на управляющий вход второго накапливающего сумматора 2. 5 Из первой половины блока 1 по адресу, сформированному на выходе сумматора 8, считывается значение первого операнда и заносится во второй накапливающий сумматор 2, затем на управляющий вход блока 17 приходит 1гмпульс с третьего выхода счетчика 10, в результате чего значение следующего операнда считывается из блока 1 по прообразованному блоком 17 коду (это связано с тем, что импульсная характеристика Фильтра симметрична) , и снова заносится во второй накапливающий сумматор 2. На управляющий вход коммутатора 3 поступает код с пятого

0

5

0

0

5

выхода Y7 блока 7, в результате чего к выходу коммутатора 3 подключается его третий вход. Значение суммы с выхода второго накапливающего сум- маторл 2 поступает на второй вход умножителя 4, на первый вход которого поступает значен коэффициента импульсной характеристики фильтра с выхода блока 11. Произведение с вы- хода умножителя 4 заносится в первый накапливающий сумматор 6 по импульсу, поступающему на его управляющий вход с второго выхода Y4 блока 7. Этот же импульс обнуляет второй на- капливающий сумматор 2, импульс с третьего выхода Y5 блока 7 переводит счетчик 10 в следующее состояние и обработка следующей пачки выборок по первому каналу происходит аналогично.

После обработки logjN выборок первой половины блок 1 своим старшим разрядом обнуливает счетчик 10, на выходе первого накапливающего сумматора 6 и выходе устройства Y1 (вы- ход Y1 служит для контроля правильности функционирования устройства) Формируется значение первой квадратурной составляющей первой преобразованной точки по первому каналу. Затем на пятом выходе Y7 блока 7 формируется управляющий код для коммутатора 3, в результате чего к его выходу подключается его второй вход. Импульс на седьмом выходе Y6 блока 7 пере ключает блок постоянной памяти, в результате чего к первому входу умножителя 4 подключается выход блока 12. С выхода первого накапливающего сумматора 6 значение преобразованной первой квадратурной составляющей через второй вход коммутатора 3 поступает на второй вход умножителя 4, на первый вход которого поступает значение тригонометрического коэффициен- та модулирующей функции, считываемое из блока 12 по адресу, сформированному на выходе дополнительного сумматора 15 путем сложения кода канала и кода ячейки, записанной в блок 16 по текущему адресу в первом такте преобразования. Затем с выхода умножителя 4 по импульсу на пятом выходе Y7 блока 7 произведение заносится в третий накапливающий сумматор 5. имгульсом на втором выходе Y4 блока 7 обнуляется первый накап- ливантций сумматор 6. Импульс на восьмом выходе Y10 блока 7 переклю-

0

5 0 5 0 5 Q

5

чает половины блока 1 (выбирается вторая половина). Тактовый импульс с третьего выхода Y5 блока 7 приходит на вход счетчика 10 и переводит его в следующее состояние, из второй половины блока 1 считывается значение второй квадратурной составляющей первой выборки по первому каналу, и указанная процедура обработки повторяется для второй квадратурной составляющей. После обработки и записи в третий накапливающий сумматор 5 преобразованной второй квадратурной составляющей на дополнительном выходе устройства Y2 формируется значение первой преобразованной точки по первому каналу. Затем импульсом с четвертого выхода Y9 блока 7 счетчик 13 переводится в следующее состояние, импульсом на пятом выходе Y7 обнуляется третий накапливающий сумматор 5 и далее происходит обработка следующего канала указанным образом.

Блок 7 синхронизации работает следующим образом.

Импульс сопровождения с второго входа Х4 блока 7 устанавливает триггер 18. Уровень логической единицы с выхода триггера 18 через элемент ИЛИ 20 поступает на вход генератора 21 синхроимпульсов и разрешает его работу. С выхода триггера 18 уровень логической единицы поступает на первый вход элемента И 31, на второй вход этого элемента поступают тактовые импульсы с выхода генератора 21 синхроимпульсов. С выхода элемента И 31 на восьмой выход Y10 блока 7 поступают управляющие сигналы записи чтения для блока 1.

Тактовые импульсы с выхода генератора 21 синхроимпульсов поступают на вход элемента И 25 и вход сброса третьего триггера 24, с выхода триггера 24 уровень логического нуля поступает через пятый Y7 выход блока 7 синхронизации на управляющий вход коммутатора 3. Уровень логического нуля с выхода триггера 19 поступает на управляющие зходы коммутаторов 23 и 29, подключая к выходам коммутаторов первые входы, и на второй вход элемента И 25, блокируя на первом этапе прохождение тактовых импульсов с первого входа этого элемента на третий Y5 и первый Y3 выходы блока 7. Этот же уровень, поступая на седьмой Y6 выход блока 7, выбирает блок 11 и

91

поступает через пятый Y7 выход блок 7 на управляющий вход коммутатора 3 (при комбинации 00 к выходу коммутатора 3 подключен первый вход, 10 - третий вход, 01 - второй вход). с выхода генератора 21 синхроимпульсов тактовые импульсы поступают на вход одноразрядного счетчика 22, с выхода которого импульсы поступают на первы входы коммутаторов 23 и 29 ч вход фомирователя 30. На его выходе Формируются короткие импульсы, которые поступают на первый Y3 выход блока 7 и являются импульсами обнуления второг накапливающего сумматора 2, и, поступая на второй выход блока 7 синхронизации, являются импульсами записи в первый накапливающий сумматор 6.

С выхода первого коммутатора 23 тактовые импульсы через седьмой выход блока 7 поступают на вход счетчика 13, а через четвертый выход - на управляющий вход дополнительного блока 12, где управляют считыванием первой или второй квадратурной компоненты модулирующей функции. С выхода второго коммутатора 29 тактовые импульсы через восьмой выход блока 7 синхронизации поступает на вход упра ления блока 1, где управляют выбором первой или второй половины блока 1. Эти же импульсы формируют на выходе формирователя 34 короткие импульсы, которые поступают на шестой выход блока 7 и управляют записью в блок 16. После считывания выборки по всем каналам импульс на третьем входе блока 7 сбрасывает триггер 18. Уровень логического нуля с выхода триггера 18 через элемент ИЛИ 20 поступает на вход генератора 21 синхроимпульсов и блокирует его. С приходом следующего импульса сопровожде

10

Q 5

0

0

5

5

0

формируется сигнал, который поступает на вход генератора 21 синхроимпульсов и разрешает его работу, с выхода генератора 21 тактовые импульсы поступают на второй вход элемента И 25. Уровень логической единицы в инверсном выходе триггера 24 также поступает на третий вход элемента И 25, на выходе которого формируются тактовые импульсы, которые через первый Y3 и третий Y5 выходы блока 7 синхронизации поступают на входы счетчика 10 и второго накапливающего сум- Mafopa 2. Уровень логической единицы с выхода триггера 19 поступает на седьмой выход Y6 блока 7. Этот же сигнал поступает через пятый выход Y7 блока 7 на управляющий вход коммутатора 3 .

После формирования N импульсов на третьем выходе Y5 блока 7 импульс на первом входе ХЗ блока 7 устанавливает триггер 24. Уровень логической единицы с выхода триггера 24 поступает на вход одноразрядного счетчика 27, через пятый выход Y7 блока 7 - на управляющий вход коммутатора 3, через шестой выход блока 7 - на управляющий вход блока 16. С помошью Формирователя 32 формируется на выходе элемента ИЛИ 33 и втором выходе блока 7 импульс обнуления первого накапливающего сумматора 6. С выхода одноразрядного счетчика 27 сигналы поступают на вторые входы коммутаторов 23 и 29. На выходе первого коммутатора 23 через четвертый выход Y9 блока 7 формируется тактовый импульс для счетчика 13 и через седьмой выход Y6 блока 7 поступает на вход блока 11. На выходе второго коммутатора 29 через восьмой выход Y10 блока 7 формируется управляющий сигнал для

| название | год | авторы | номер документа |

|---|---|---|---|

| Многоканальный цифровой интерполирующий фильтр для частотного уплотнения каналов | 1987 |

|

SU1525716A1 |

| Устройство для цифровой обработки сигналов | 1988 |

|

SU1575203A1 |

| Многоканальный перестраиваемый цифровой фильтр | 1988 |

|

SU1569955A1 |

| Устройство для реализации быстрого преобразования Фурье | 1988 |

|

SU1672468A1 |

| Устройство для реализации быстрого преобразования Фурье | 1989 |

|

SU1672469A1 |

| Устройство для спектрального анализа с постоянным относительным разрешением | 1982 |

|

SU1109760A1 |

| Цифровой генератор периодической функции | 1987 |

|

SU1432491A1 |

| Цифровой анализатор спектра | 1985 |

|

SU1256044A1 |

| Устройство для обработки данных при формировании диаграммы направленности антенной решетки | 1987 |

|

SU1462351A1 |

| Устройство для обработки многотоновых изображений | 1988 |

|

SU1608699A1 |

Изобретение относится к радиотехнике и позволяет повысить качество фильтрации. Цифровой фильтр содержит блок 1 оперативной памяти, накапливающие сумматоры 2, 5 и 6, коммутатор 3, умножитель 4, блок 7 синхронизации, сумматоры 8 и 15, счетчик 9 выборки, счетчик 10, блоки 11 и 12 постоянной памяти, счетчик 13 каналов, блок 14 элементов И, блок 16 памяти адресов и блок 17 управляемых инверторов. Преобразование групповых сигналов частотно-уплотненных каналов происходит следующим образом. Из входного группового сигнала частотно-уплотненных каналов с входной частотой дискретизации, связанной с граничной частотой сигналов по каналам, формируются квадратурные демодулированные составляющие. Затем производится фильтрация и вместе с тем понижается частота дискретизации. Далее осуществляется восстановление исходного сигнала для каждого канала. Цель достигается за счет обеспечения разделения группового сигнала частотно-уплотненных каналов, что позволяет выделить из него информацию по каждому из каналов. 2 ил.

ния на второй Х4 вход блок 7 работает д5 блока 7, а также для блока 1 и через

указанным образом.

На втором этапе обработки импульс на четвертом входе блока 7 Формирует на выходе формирователя 26 короткий импульс, который устанавливает триггер 19, на выходе элемента ИЛИ 33 (второй Y4 выход блока 7) формирует импульс обнуления первого накапливающего сумматора 6. Уровень логической единицы с выхода триггера 19 поступает на управляющие входы коммутаторов 23 и 29, первый вход элемента И 25 и второй вход элемента ИЛИ 20. На выходе элемента ИЛИ 20

0

5

формирователь 34 на шестом выходе Y8 блока 7 формируется импульс записи в блок 16. На пятый выход Y7 блока 7 поступают с выхода одноразрядного счетчика 27 сигналы управления для третьего накапливающего сумматора 5 и по заднему фронту этих сигналов на выходе формирователя 28 формируются короткие импульсы, обнуляющие третий накапливающий сумматор 5.

Предлагаемый Фильтр позволяет разделить групповой сигнал частотно- уплотненных канатов и выделить из него информацию по из каналов.

Формул а изобретения

Цифровой фильтр, содержащий последовательно соединенные умножитель и первый накапливающий сумматор, выход которого является выходом цифрового Фильтра, послелогательно соединенные блок оперативной памяти и второй накапливающий сумматор, последовательно соединенные счетчик, сумматор и блок управляемых инверторов, выход которого соединен с первым адресным входом блока оперативной памяти, счетчик выборки, первый выход которого соединен с вторым входом сумматора, счетчик каналов, первый выход которого соединен с вторым адресным входом блока оперативной памяти, блок постоянной памяти, выход которого соединен с пер вым входом умнозгителя, а адресный вход блока постоянной памяти соединен с первым выходом счетчика, и блок синхронизации, первый вход которого соединен с вторым выходом счетчика, третий выход которого подключен к второму входу блока управляемых инверторов, второй вход блока синхронизации является управляющим входом цифрового Фильтра и соединен с входом счетчика выборки, а третий вход блока синхронизации соединен с вторым выходом счетчика каналов, причем первый, второй, третий и четвертый выходы блока синхронизации соединены с управляющими входами вторрго и первого накапливающих сумматоров и входами счетчика и счетчика каналов соответственно, отличающийся тем, что, с целью повышения качества фильтрации за счет разделения групповых сигналов частотно-уплотненных каналов, введены коммутатор, первый вход которого является входом цифрового Фильтра, второй и третий входы соединены с выходами первого и второго накапливающих сумматоров соответственно, а выход коммутатора подключен к второму входу умножителя, третий накапливающий сумматор, вход которого соединен с входом блока оперативной памяти и выходом умножителя, а выход третьего накапливающего сумматора является дополнительным выходом цифрового фильтра, и последовательно соединенные блок элементов И, блок памяти адресов, дополнительный сумматор и дополнительный блок постоянной памяти, выход которого соединен с первым входом умножителя, причем управляющие входы третьего накапливающего сумматора и коммутатора соединены с пятым выходом блока синхронизации, шестой выход которого соединен с управляющими входами блока памяти адресов и дополнительного сумматора, вторым входом дополнительного сумматора и первым входом блока элементов И, второй вход которого соединен с первым выходом счетчика каналов, второй выход счетчика выборки соединен с четвертым входом блока синхронизации, седьмой и восьмой выходы которого соединены с управляющими входами блоков постоянной памяти и блока оперативной памяти соответственно, а выход блока элементов И соединен с третьим входом дополнительного сумматора.

| Многоканальный цифровой интерполирующий фильтр | 1986 |

|

SU1401480A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1990-05-23—Публикация

1988-02-01—Подача