фиеА

Изобретение относится к вычислительной технике и может быть использовано в системах цифровой обработки сигналов.

Целью изобретения является расширение функциональных возможностей за счет выполнения рекурсивной фильтрации.

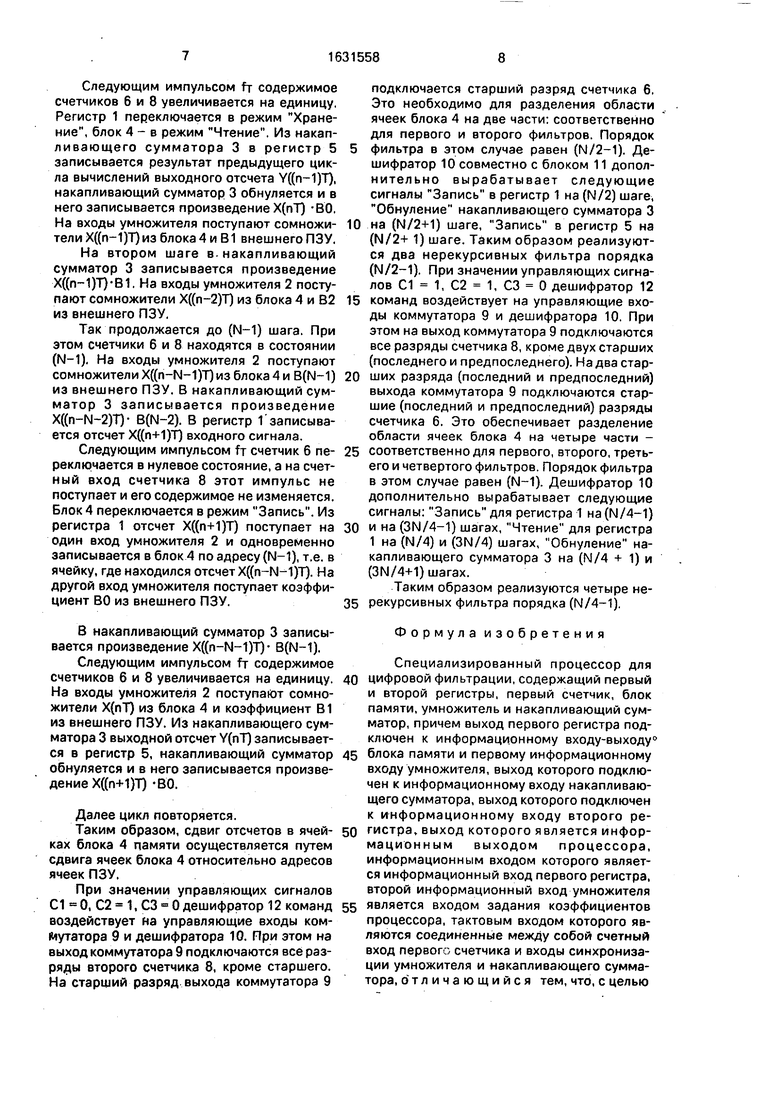

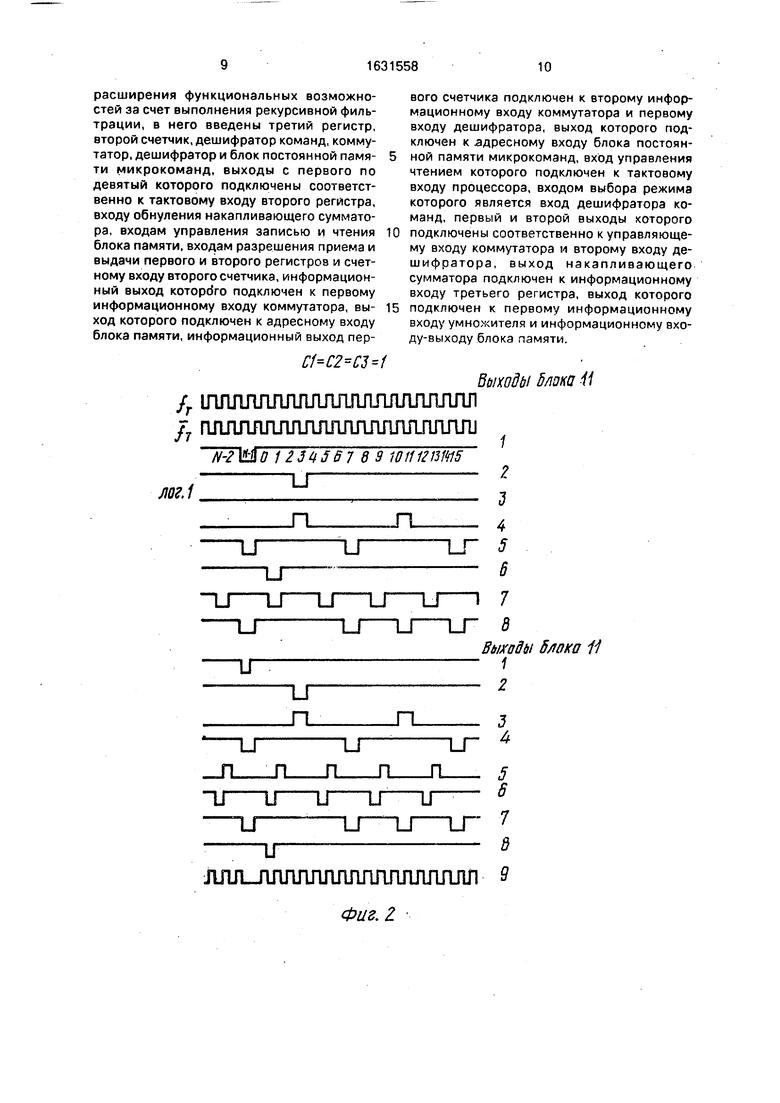

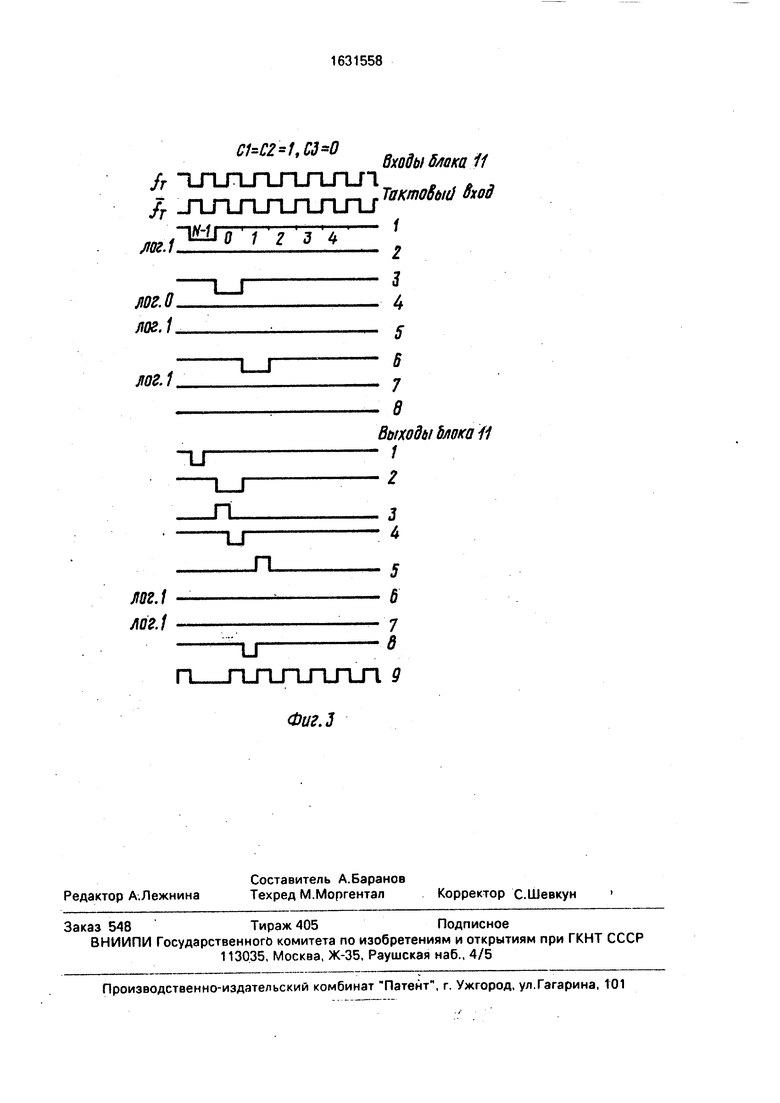

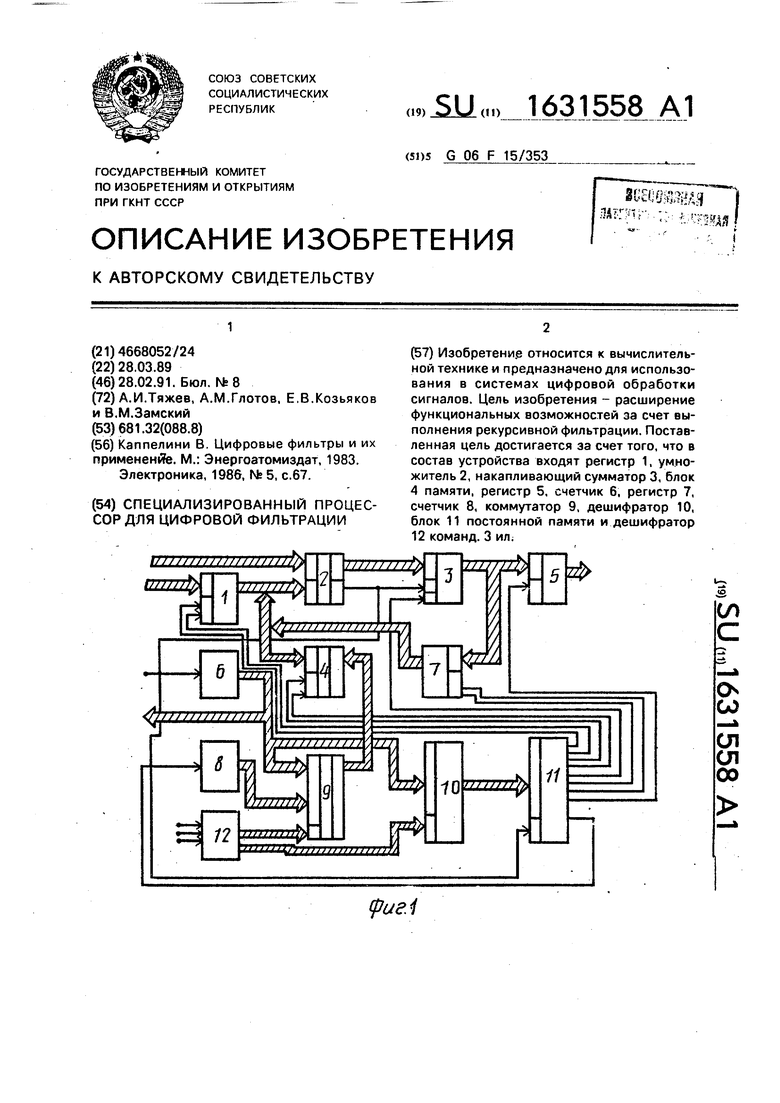

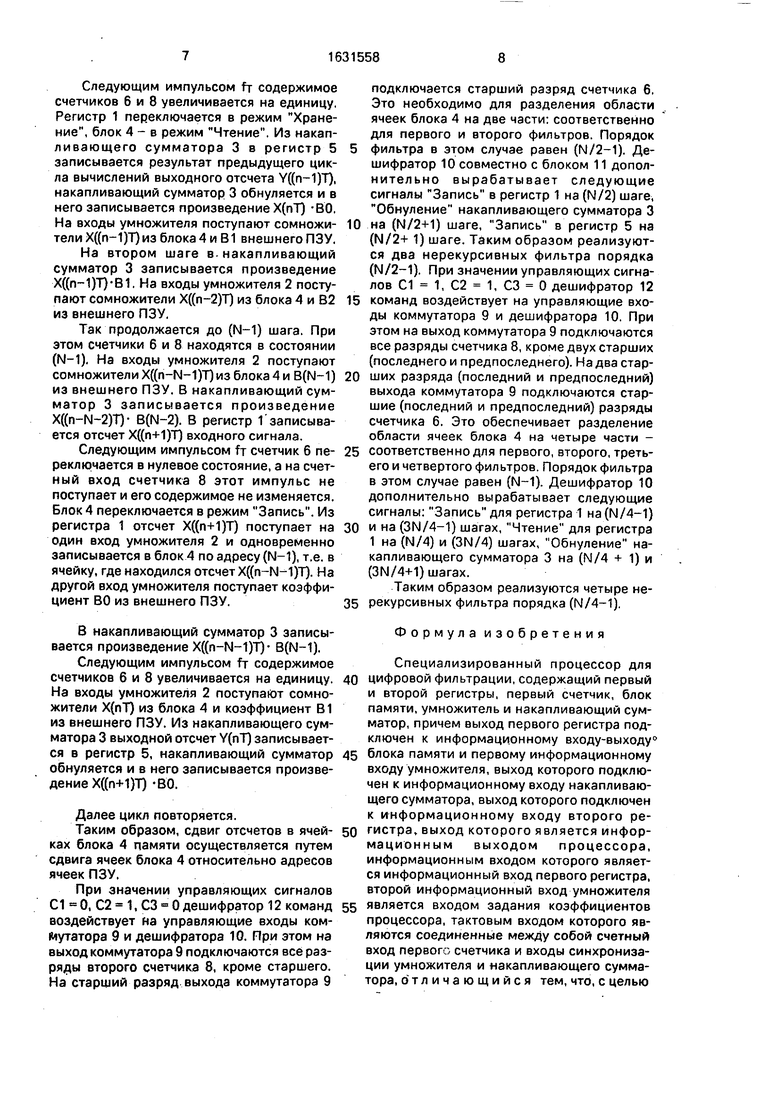

На фиг.1 изображена функциональная схема специализированного процесса; на фиг,2 и 3 - временные диаграммы его работы.

Специализированный процессор содержит регистр 1, умножитель, накапливающий сумматор 3, блок 4 памяти, регистр 5, счетчик 6, регистр 7, счетчик 8, коммутатор 9, дешифратор 10, блок 11 постоянной па- мяти (микрокоманд) и дешифратор 12 команд.

Специализированный процессор работает следующим образом.

На первый вход процессора поступают цифровые отсчеты входного сигнала X(nT), a на второй вход - весовые коэффициенты из внешнего ПЗУ. Адресная шина внешнего ПЗУ подключается к второму выходу процессора. На тактовый вход поступают такто- вые импульсы частотой Тт. Коэффициенты пересчета счетчиков б и 8 одинаковы и равны N. На первый выход специализированного процессора поступают цифровые отсчеты выходного сигнала Y(nT). Режим ра- боты устройства определяется логическими уровнями на управляющих входах устройства.

Амплитудно-частотная характеристика фильтра, построенного на основе специали- зированного процесса, определяется значениями весовых коэффициентов.

Рассмотрим работу специализированного процессора в режиме рекурсивного цифрового фильтра, состоящего из каскад- но соединенных рекурсивных звеньев второго порядка. При этом число звеньев L N/a, где а - количество периодов тактовой частоты, необходимое для обработки одного звена. В этом режиме состояние управля- ющих входов следующее: С1 1; С2 1; СЗ 1.

На выход коммутатора 9 подключается счетчик 6 таким образом, что с адресным входом блока 4 соединяются все разряды счетчика 6, кроме первого и третьего. Это обеспечивает повторение ячеек блока 4 памяти в процессе вычислений.

Значение выходного отсчета Y(nT) вычисляется по формулам:

V(nT) М - Х(пТ) + А1 V((n-1)T) +

+ A2-V((n-2)T);(1)

Y(nT) - ВО -V(nT) + В1 V((n-1)T) + -

+ В2 -V((n-2)T),(2)

где n - номер входного отсчета;

Х(пТ) - значение входного отсчета;

V(nT(, V((n-1)T), V((n-2)T) - значение выходного отсчета рекурсивной части звена в настоящем и двух предыдущих циклах вычислений;

ВО,В1,В2,А1,А2 - весовые коэффициенты фильтра;

М - масштабирующий коэффициент.

Максимальный коэффициент передачи рекурсивной части звена Кмакс 1, поэтому на входе фильтра предусмотрен масштабирующий коэффициент М, величина которого выбирается из условия М 1/Кмакс.

Коэффициенты А1 иВ1 могут принимать значения от 2 до -2, поэтому, чтобы избежать переполнения в умножителе, следует использовать половинные значения коэффициентов, значения которых по модулю не превышают единицу.

С учетом этого в формуле (1) вместо произведения А1 V((n-1)T) следует записать 0,5 А1 -V((n-1)T) + 0,5- А1 -V((n-1)T). Аналогичные изменения в формуле (2).

На нулевом шаге, т.е. при нулевом состоянии счетчика 6, регистр 1 находится в режиме Хранение, блок 4 памяти - в режиме Чтение, регистр 7 - в режиме Хранение, регистр 5 - в режиме Чтение.

На входы умножителя 2 подаются сомножители V((n-1)T) из блока 4 и 0,5- А1 из внешнего ПЗУ. В накапливающий сумматор 3 записывается результат предыдущего умножения.

Следующим импульсом fr содержимое счетчика 6 увеличивается на единицу. Из накапливающего сумматора 3 в регистр 5 записывается результат вычислений Y((n- 1)Т) предыдущего цикла. Импульсом с выхода блока 11 накапливающий сумматор 3 обнуляется и в него записывается произведение 0,5- А1 V((n-1)T). На вход умножителя поступают сомножители V((n-1)T) из блока 4 и 0,5- А1 из внешнего ПЗУ.

На втором шаге результат умножения записывается в накапливающий сумматор 3, в умножитель 2 поступают сомножители V((n-2)T) из блока 4 и коэффициент А2 из внешнего ПЗУ. В регистр 1 записывается входной отсчет Х(пТ) на шаге N-1.

На третьем шаге блок 4 переключается в режим Хранение, в накапливающий сумматор 3 записывается произведение V((n-2)T)-A2. На входы умножителя поступают входной отсчет Х(пТ) с выхода регистра 1 и масштабирующий коэффициент М из внешнего ПЗУ.

На четвертом шаге регистр 1 переключается в режим Хранение. На входы умножителя 2 поступают сомножители V((n-1)T) из блока 4 и 0,5-81 из внешнего ПЗУ. В

накапливающий сумматор 3 записывается произведение Х(пТ) -M.

На пятом шаге из накапливающего сумматора 3 в регистр 7 записывается выходной отсчет рекурсивной части звена V(nT). На входы умножителя 2 поступают сомножители V((n-1)T) из блока 4 и 0,5 -В1 из внешнего ПЗУ. Накапливающий сумматор 3 обнуляется и в него записывается произведение V((n-1)T) -0,5; В1.

На шестом шаге в накапливающий сумматор 3 записывается произведение V((n-1)T)-0,5 B1, а на вход умножителя поступают сомножители V((n-2)T) из блока 4 и коэффициент В2 из внешнего ПЗУ.

На седьмом шаге блок 4 памяти переключается в режим Запись и s него по адресу, где находился отсчет V((n-2)T), записывается из регистра 7 значение отсчета V(nT), которое одновременно поступает на один вход умножителя 2, в то время как на другой вход умножителя 2 из внешнего ПЗУ поступает коэффициент ВО. В накапливающий сумматор 3 . записывается произведен е V((n-2)T) -В2.

На восьмом шаге заканчивается вычисление входного отсчета Y (nT) первого-звена, который записывается в регистр 7. Значение Y(nT) является входным отсчетом для второго звена. Накапливающий сум- матор 3 обнуляется и в него записывается произведение V ((n-1)T)-0,5 -A1. На входы умножителя 2 поступают сомножители V ((n-1)T) из блока 4 и 0,5- А1 из внешнего ПЗУ.

Далее процесс вычислений повторяется. Выходной отсчет очередного звена является входным для последующего.

Таким образом, на вычисление выходного отсчета затрачивается восемь перио- дов частоты fr, отсюда количество звеньев L N/8.

Выходной отсчет Y(nT) рекурсивного фильтра записывается во второй регистр 5 на первом шаге второго цикла вычислений. После каждого цикла вычислений второй разряд адреса блока 4 инвертируется в коммутаторе 9, т.е. старший и младший элементы задержки меняются местами, что эквивалентно сдвигу отсчетов в элементах задержки.

При значении управляющих входов С1 О, С2 1, С3 1 дешифратор 12 команд формирует управляющие сигналы, под воздействием которых дзшифратор 10 совмест- но с блоком 11 дополнительно формирует сигналы записи на (N/2-1) шаге и чтения на (N/2+ 3) шаге для регистра 1, на (N/2+ 1) шаге - сигнал записи для регистра 5. Кроме того, регистр 7 переключается в режим

Хранение на (N/2+3) шаге, чтобы исключить передачу выходного отсчета первого фильтра на вход второго.

Таким образом реализуются два рекурсивных цифровых фильтра (РЦФ) из N/16 рекурсивных звеньев второго порядка.

При значении управляющих входов С1 О, С2 0, СЗ 1 дешифратор 12 команд формирует управляющие сигналы, под воздействием которых дешифратор 10 совместно с блоком 11 дополнительно формирует сигналы записи на (N/4-1), (N/2-1) и (3N/4-1) шагах и чтения на (N/4+3), (N/2+3) и (3N/4+3) шагах для регистра 1, Ha(N/4+1), (N/2+1), (3N/4+1) шагах - сигнал записи для регистра 5. Кроме того, регистр 7 переключается в режим Хранение на (N/4+ 3), (N/2+3) и (3N/4-.3) шагах, чтобы исключить передачу выходного отсчета одного фильтра на вход другого. Так реализуются четыре РЦФ из N/32 звеньев.

Рассмотрим работу специализированного процессора в режиме нерекурсивного цифрового фильтра. Порядок фильтра определяется коэффициентом пересчета счетчиков б и 8 и равен Г 1. Входы управления режимом работы в этом с;г чае подключены к нулевому потенциалу, т.е С1 С2 СЗ 0.

Выходной отсчет Y(nT нерекурсивного цифрового филырэ определяется по формуле

Y(nT) S1X((n-l)T)-B, (3)

I о

На первый вход устройства поступают отсчеты входного сигнала Х(пТ), а на второй вход- коэффициенты фильтра из внешнего ПЗУ, адресный вход которого соединяется с вторым выходом специализированного процессора. На тактовый вход поступают тактовые импульсы с частотой тт, на выход - выходные отсчеты Y(nT).

На выход коммутатора 9 переключен выход счетчика 8, который и определяет адрес блока 4. На счетный вход счетчика 8 поступают тактовые импульсы с выхода блока 11, Регистр 7 в работе не участвует и переключен в режим Хранение. На нулевом шаге, когда счетчики 6 и 8 находятся в нулевом состоянии, из внешнего ПЗУ на один вход умножителя 2 поступает коэффициент ВО, на другой вход с выхода регистра 1 - отсчет входного сигнала Х (пТ), записан- ,ный на предыдущем шаге. Одновременно блок 4 переключается в режим Запись и по нулевому адресу происходит запись отсчета Х(пТ) входного сигнала. В накапливающий сумматор 3 записывается произведение Х((п-1)Т) -ВО.

Следующим импульсом fr содержимое счетчиков 6 и 8 увеличивается на единицу, Регистр 1 переключается в режим Хранение, блок 4 - в режим Чтение. Из накапливающего сумматора 3 в регистр 5 записывается результат предыдущего цикла вычислений выходного отсчета Y((n-1)T), накапливающий сумматор 3 обнуляется и в него записывается произведение Х(пТ) -ВО, На входы умножителя поступают сомножители Х((п-1)Т)из блока 4 и В1 внешнего ПЗУ.

На втором шаге в. накапливающий сумматор 3 записывается произведение Х((п-1)Т) В1. На входы умножителя 2 поступают сомножители Х((п-2)Т) из блока 4 и В2 из внешнего ПЗУ.

Так продолжается до (N-1) шага. При этом счетчики 6 и 8 находятся в состоянии (N-1). На входы умножителя 2 поступают сомножители X((n-N-1)T) из блока 4 и B(N-1) из внешнего ПЗУ. В накапливающий сумматор 3 записывается произведение X((n-N-2)T)- B(N-2). В регистр 1 записывается отсчет Х((п+1)Т) входного сигнала.

Следующим импульсом fr счетчик 6 переключается в нулевое состояние, а на счетный вход счетчика 8 этот импульс не поступает и его содержимое не изменяется. Блок 4 переключается в режим Запись. Из регистра 1 отсчет Х((л+1)Т) поступает на один вход умножителя 2 и одновременно записывается в блок 4 по адресу (N-1), т.е. в ячейку, где находился отсчет X((n-N-1)T). На другой вход умножителя поступает коэффициент ВО из внешнего ПЗУ.

В накапливающий сумматор 3 записывается произведение X((n-N-1)T) B(N-1).

Следующим импульсом fr содержимое счетчиков 6 и 8 увеличивается на единицу. На входы умножителя 2 поступают сомножители Х(пТ) из блока 4 и коэффициент В1 из внешнего ПЗУ. Из накапливающего сумматора 3 выходной отсчет Y(nT) записывается в регистр 5, накапливающий сумматор обнуляется и в него записывается произведение Х((п+1)Т) -ВО.

Далее цикл повторяется.

Таким образом, сдвиг отсчетов в ячейках блока 4 памяти осуществляется путем сдвига ячеек блока 4 относительно адресов ячеек ПЗУ.

При значении управляющих сигналов С1 О, С2 1, СЗ 0 дешифратор 12 команд воздействует на управляющие входы коммутатора 9 и дешифратора 10. При этом на выход коммутатора 9 подключаются все разряды второго счетчика 8, кроме старшего. На старший разряд выхода коммутатора 9

подключается старший разряд счетчика 6. Это необходимо для разделения области ячеек блока 4 на две части: соответственно для первого и второго фильтров. Порядок

5 фильтра в этом случае равен (N/2-1). Дешифратор 10 совместно с блоком 11 дополнительно вырабатывает следующие сигналы Запись в регистр 1 на (N/2) шаге, Обнуление накапливающего сумматора 3

10 на (N/2+1) шаге, Запись в регистр 5 на (N/2+ 1) шаге. Таким образом реализуются два нерекурсивных фильтра порядка (N/2-1). При значении управляющих сигналов С1 1, С2 1, СЗ 0 дешифратор 12

15 команд воздействует на управляющие входы коммутатора 9 и дешифратора 10. При этом на выход коммутатора 9 подключаются все разряды счетчика 8, кроме двух старших (последнего и предпоследнего). На два стар20 ших разряда (последний и предпоследний) выхода коммутатора 9 подключаются старшие (последний и предпоследний) разряды счетчика 6. Это обеспечивает разделение области ячеек блока 4 на четыре части 25 соответственно для первого, второго, третьего и четвертого фильтров. Порядок фильтра в этом случае равен (N-1). Дешифратор 10 дополнительно вырабатывает следующие сигналы: Запись для регистра 1 Ha(N/4-1)

30 и на (3N/4-1) шагах, Чтение для регистра 1 на (N/4) и (3N/4) шагах, Обнуление накапливающего сумматора 3 на (N/4 + 1) и (3N/4+1) шагах.

Таким образом реализуются четыре не35 рекурсивных фильтра порядка (N/4-1).

Формула изобретения

Специализированный процессор для

40 цифровой фильтрации, содержащий первый и второй регистры, первый счетчик, блок памяти, умножитель и накапливающий сумматор, причем выход первого регистра подключен к информационному входу-выходу

45 блока памяти и первому информационному входу умножителя, выход которого подключен к информационному входу накапливающего сумматора, выход которого подключен к информационному входу второго ре50 гистра, выход которого является информационным выходом процессора, информационным входом которого является информационный вход первого регистра, второй информационный вход умножителя

55 является входом задания коэффициентов процессора, тактовым входом которого являются соединенные между собой счетный вход первого счетчика и входы синхронизации умножителя и накапливающего сумматора, отличающийся тем, что, с целью

расширения функциональных возможностей за счет выполнения рекурсивной фильтрации, в него введены третий регистр, второй счетчик, дешифратор команд, коммутатор, дешифратор и блок постоянной памяти микрокоманд, выходы с первого по девятый которого подключены соответственно к тактовому входу второго регистра, входу обнуления накапливающего сумматора, входам управления записью и чтения блока памяти, входам разрешения приема и выдачи первого и второго регистров и счетному входу второго счетчика, информационный выход KOTOpdro подключен к первому информационному входу коммутатора, выход которого подключен к адресному входу блока памяти, информационный выход пер0

вого счетчика подключен к второму информационному входу коммутатора и первому входу дешифратора, выход которого подключен к адресному входу блока постоянной памяти микрокоманд, вход управления чтением которого подключен к тактовому входу процессора, входом выбора режима которого является вход дешифратора команд, первый и второй выходы которого подключены соответственно к управляющему входу коммутатора и второму входу дешифратора, выход накапливающего сумматора подключен к информационному входу третьего регистра, выход которого подключен к первому информационному входу умножителя и информационному входу-выходу блока памяти.

| название | год | авторы | номер документа |

|---|---|---|---|

| Нерекурсивный цифровой фильтр нижних частот | 1986 |

|

SU1418750A1 |

| Цифровой анализатор спектра | 1985 |

|

SU1256044A1 |

| Цифровой нерекурсивный фильтр | 1990 |

|

SU1786638A1 |

| Адаптивный корректор межсимвольной интерференции | 1987 |

|

SU1540009A1 |

| Нерекурсивный цифровой фильтр | 1983 |

|

SU1171994A1 |

| Цифровой коррелятор | 1976 |

|

SU636619A1 |

| Устройство для вычисления скользящего спектра | 1988 |

|

SU1527642A1 |

| Многоканальный цифровой фильтр | 1990 |

|

SU1751781A1 |

| Цифровой генератор функций | 1989 |

|

SU1656511A1 |

| Дельта-кодер | 1989 |

|

SU1612375A1 |

Изобретение относится к вычислительной технике и предназначено для использования в системах цифровой обработки сигналов. Цель изобретения - расширение функциональных возможностей за счет выполнения рекурсивной фильтрации. Поставленная цель достигается за счет того, что в состав устройства входят регистр 1, умножитель 2, накапливающий сумматор 3, блок 4 памяти, регистр 5, счетчик 6, регистр 7, счетчик 8, коммутатор 9, дешифратор 10, блок 11 постоянной памяти и дешифратор 12 команд. 3 ил.

Выходы 5лока И

/г 1гггии1ллллллллллллпллпл /7 гшлгиишшглядллпяплгшл

лf

о.1

1234587 8 9 WIHinWS TJ

г

3

гт

и

и

и

ллллшпяпллп тллж1шш в

Фиг. 2

WIHinWS

п

LT

--

б/tока 11

Входы блока 11

,

/г 1JTJTJTJTJT-TLTI

/г JIJOJIJOTIJIJIJ7 Ы

ri JTJTJnjnj-U l 9

Фиг.З

Входы блока 11

| Каппелини В | |||

| Цифровые фильтры и их применение | |||

| М.: Энергоатомиздат, 1983 | |||

| Электроника, 1986, № 5, с.67. |

Авторы

Даты

1991-02-28—Публикация

1989-03-28—Подача