Изобретение относится к технике связи, в частности к системам импульсной радиосвязи, и может быть использовано в каналах служебной связи с дельта-модуля1Д1ей для передачи по каналу низкоскоростной цифровой информации.

Цель изобретения - уменьшение уровня искажений передаваемого дель- та-модулированного сигнала.

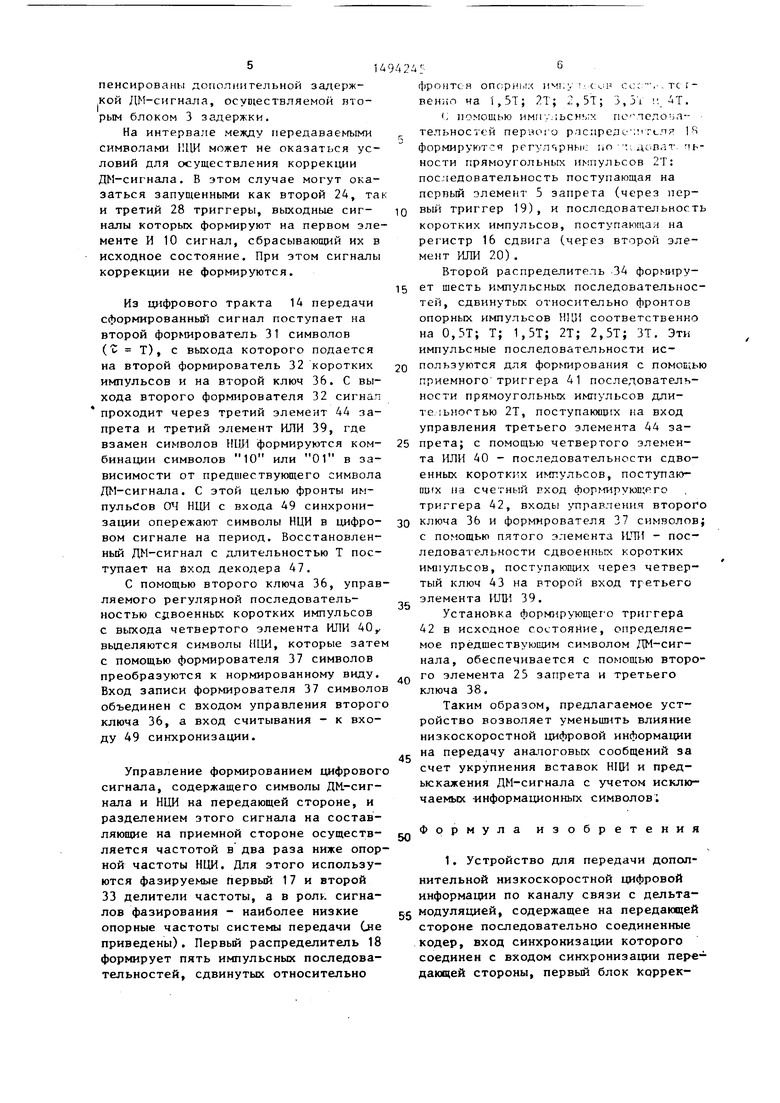

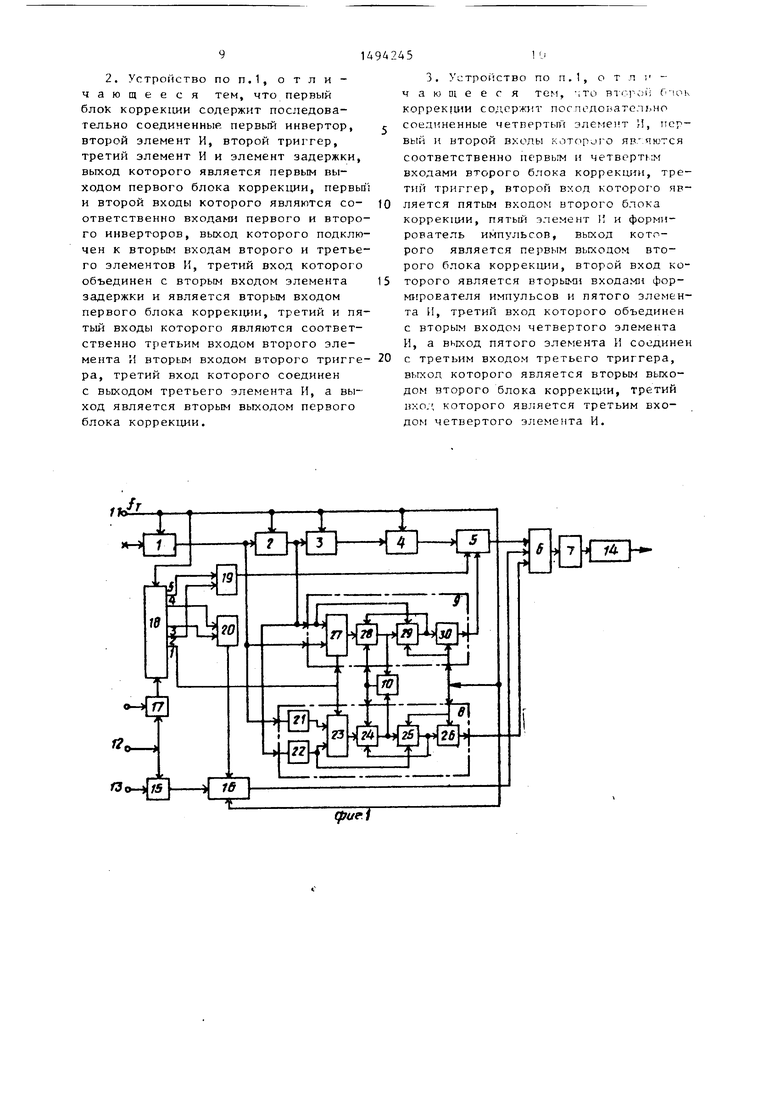

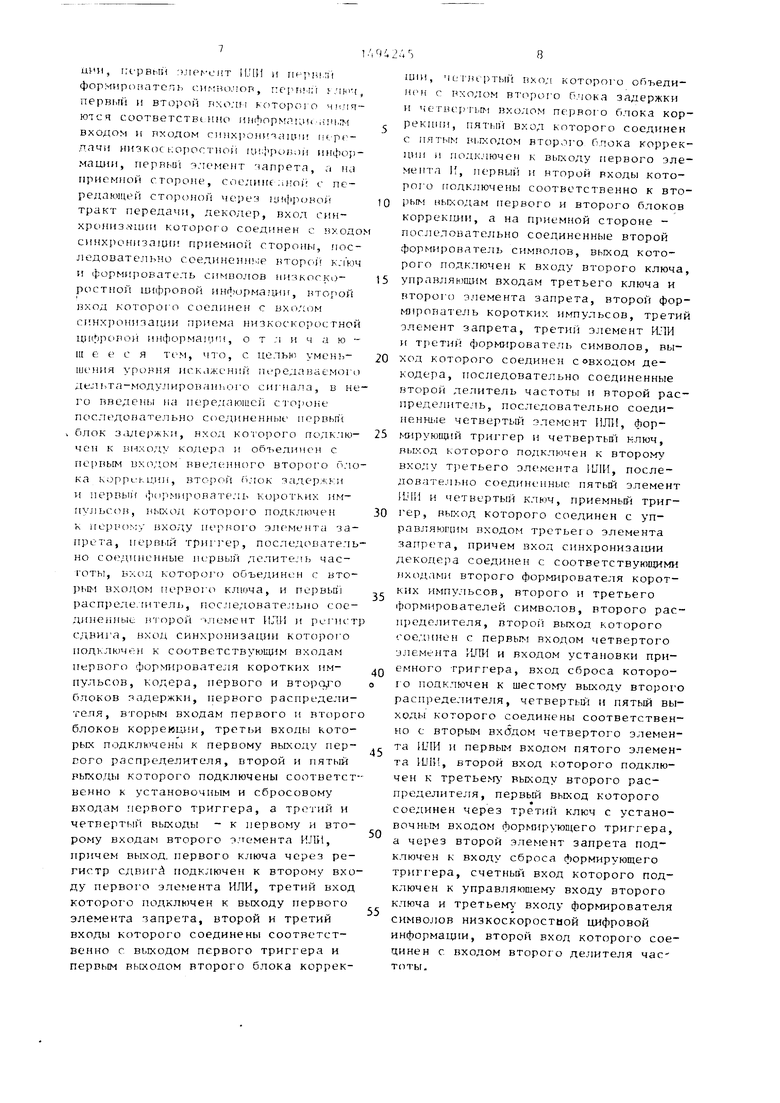

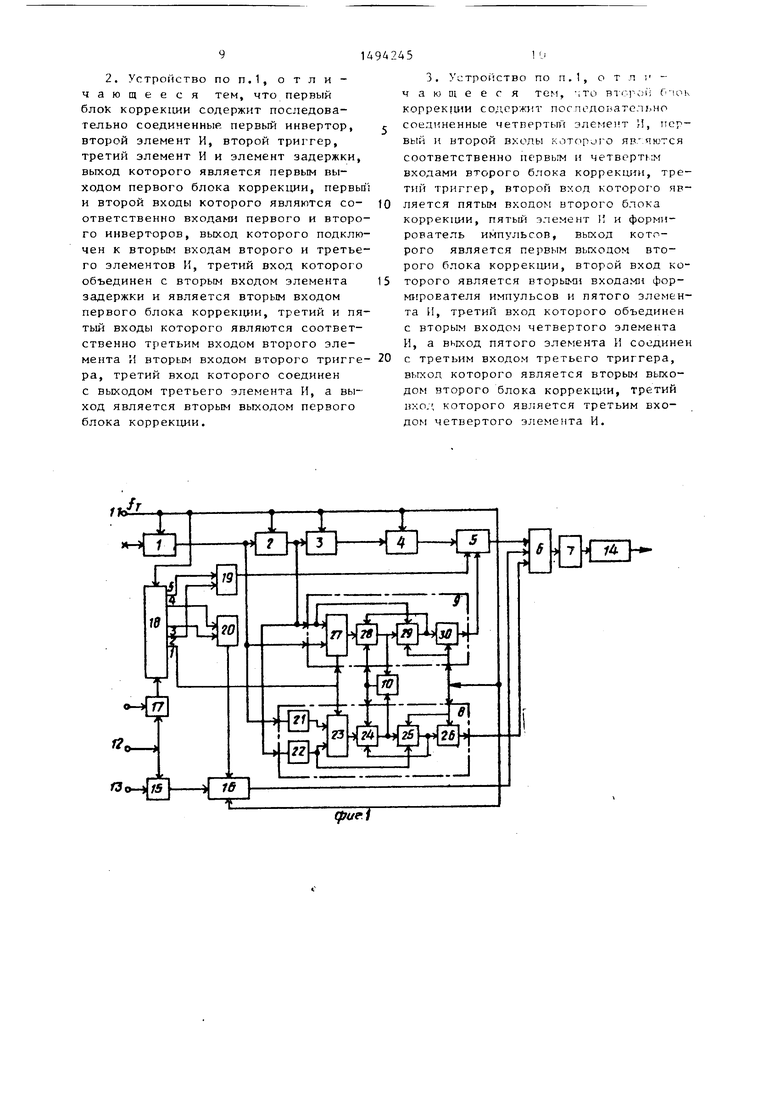

На фиг.1 приведена структурная схема передающей стороны предлагаемого устройства; на фиг.2 - структурная схема приемной стороны.

Передающая сторона устройства (фиг.1) содержит кодер 1, первый 2 и второй 3 блок 4 задержки, первый

формирователь 4 коротких импульсов, первый элемент 5 запрета, первый элемент ИЛИ 6, первый формирователь 7 символов, первый 8 и второй 9 блоки коррекции, первый элемент И 10 вход 11 синхронизации передающей стороны, вход 12 синхронизации передачи низкоскоростной цифровой информации, информационный вход 13, цифровой тракт 14 передачи, первый ключ 15, регистр 16 сдвига, первый делитель 17 частоты, первый распределитель 18, первый триггер 19, второй элемент ИЛИ 20, первый 21 и второй 22 инверторы, второй элемент И 23, второй триггер 24, третий элемент И 25, элемент.26 за- держки, четвертый элемент И 27, тре

314

rufi триггер 2o, пятый элемент И 29 и формирователь 30 и fIIyльcoв,

Приемная сторона устройства (фнг.2) содержит второй формировател 31 символов, второй формирователь 32 коротких импульсов, второй делитель 33 частоты, второй распределитель 34 второй элемент 35 запрета, второй ключ 36, формирователь 37 символов низкоскоростной Щ1ФРОБОЙ информации, третий ключ 38, третий элемент ШШ 39 четвертый элемент ILTTi 40, приемный триггер 41, форьшрующий триггер 42, четвертьй ключ 43, третий элемент 44 запрета, пятый элемент {ПИ 45, трети форьшрователь 46-символов, декодер 47, вход 48 синхронизации приемной стороны и вход 49 синхронизащ{и низкоскоростной цдтфровой информации.

Устройство работает следую1цим образом.

Двоичный дсльта-модулированный сигнал (ЛМ), формируемый кодером 1, с тактовой частотой f, численно рав ной скорости следования символов в Щ1ФРОВОМ тракте 14 передачи, проходит пос.ледовательно через первый 2 и B l Qpuii 3 блоки задержки, первый форьпсрователь 4, первый элемент 5 запрета, первый элемент ИЛИ 6 и пер- ;-,ын фор№1рователь 7 символов.

Регулярно с частотой, которая в два раза ниже опорной частоты низкоскоростной цифровой информации (04 НЩ1) , поступающей с входа, 12 синхронизации, и равна , в первом элементе 5 запрета блокируются 2- элемснтные комбинации символов, язаме} которых с помощью первого эле мента Ю1 6 вводятся 2-эдементные комби11ации символов НИИ. Таким образом, в Щ1фровой тракт 14 передачи поступает чередующаяся последовательность 2- лементных комбинаций симво- лов fim; и (N-2)-элементных отрезков 71М-сигнала с учетом осуществляемого предыска |.ения.

Предыскажение соответствушпи1Х символов Л 1-сигнала осуществляется следующим образом.

Комбинации символов ДМ-сигнала, соответствующие паузным последовательностям, не изменяются (комбинации 01 и 10). Символы изменения уровня 11 и 00 корректируются соответствуюо1ей заменой символа О на символ 1 и наоборот. При этом фронты импульсов 04 НЦИ на передаю

Q 5 0

5 0

г Q

щей стороне опережают подменяемые симво.-ты цифровог о сигнала на два периода тактовой частоты. На приемной стороне осуществляется стробирование принятого сигнала, задержка его во времени и формирование символов НЦИ по длительности.

Восстановление ДМ-сигнала осуществляется заменой пар принятых символов Н1Ш паузными комбинациями символов .

Такая интерпретация ДМ-сигнала как последовательности 2-элементных комбинаций эквивалента переходу от двоичной к троичной дельта-модуляции.

Данный алгоритм коррекции структуры ДМ-сигнала реализуется с помощью первого 8 и второго 9 блоков коррекции и первого 2 и второй 3 блоков задержки.

Исходньп ДМ-сигнал и задержанньй на такт поступают соответственно на первьш и четвертьй входы первого 8 и второго 9 блоков коррекции, на третьи рходы которых подается последовательность коротких импульсов, сдвинутая относительно фронтов опорных импульсов НЦИ на 1,5Т (где Т - период следования символов НЦИ). Кс- ли символы подменяют в ДМ-сигнале комбина11;ии символов 01 или 10, то на выходах второго 23 и четвертого 27 элe eнтoв И импульсы отсутствуют , а следовательно, нет сигналов коррек1щи на выходах первого 8 и второго 9 блоков коррекции. При комбинации символов ДМ-сигнала типа 11, форкпфуется импульс }ia вькоде четвертого элемента И 27, который запускает третий триггер 28, выходной сигнал которого подготавливает пятьй элемент И 29 к формированию сигнала коррекции в момент поступления в ДМ-сигнале ближайшего по времени символа 1, при поступлении которого формируется

импульс длительностью

Т на выхо

де второго блока 9 коррекции, который с помощью первого элемента 5 запрета запрещает в ДМ-сигнале соответствующий символ. Аналогично работает первый блок 8 коррек1щи, где при комбинации символов 00 формируется сигнал Koppexipin в виде импульса, поступающего на первый вход первого элемента ИЛИ 6.

Bpe ieHHbie задержки сигналов при формировании сигналов коррекции скомпенсированы дополнительной задержкой ДМ-сигнала, осуществляемой вторым блоком 3 задержки.

На интервале между передаваемыми символами ШЩ может не оказаться условий для осуществления коррек1Ц1и ДМ-сигнала. Б этом случае могут оказаться запущенными как второй 24, та и третий 28 триггеры, выходные сиг- налы которых формируют на первом элементе И 10 сигнал, сбрасывающий их в исходное состояние. При этом сигналы коррекции не формируются.

Из цифрового тракта 14 передачи сформированный сигнал поступает на второй формирователь 31 символов (и Т), с выхода которого подается на второй формирователь 32 коротких импульсов и на второй ключ 36. С выхода второго формирователя 32 сигнал проходит через третий элемент 44 запрета и третий элемент ИЛИ 39, где взамен символов НиЛ формируются ком- бинации символов 10 или 01 в зависимости от предшествующего символа ДМ-сигнала. С этой целью фронты им- пульСов ОЧ НЦИ с входа 49 синхронизации опережают символы НЦИ в цифро- вом сигнале на период. Восстановленный ДМ-сигнал с длительностью Т поступает на Вход декодера 47.

С помощью второго ключа 36, управляемого регулярной последовательностью сдвоенных коротких импульсов с выхода четвертого элемента ИЛИ 40,, вьщеляются символы НЦИ, которые зате с помощью формирователя 37 символов преобразуются к нормированному виду. Вход записи формирователя 37 символо объединен с входом управления второг ключа 36, а вход считывания - к входу 49 синхронизации.

Управление формированием цифровог

сигнала, содержащего символы ДМ.-сиг- нала и НЦИ на передающей стороне, и разделением этого сигнала на составляющие на приемной стороне осуществ- ляется частотой в два раза ниже опорной частоты НЦИ. Для этого используются фазируемые Первый 17 и второй 33 делители частоты, а в ролк сигналов фазирования - наиболее низкие опорные частоты системы передачи Сне приведены), Первьй распределитель 18 формирует пять импульсных последовательностей, сдвинутых относительно

5 О

5

Q g

5

фронтон опсфных nMi:y 1л c:iji i ссс:-.-, тс г- венно ча 1,5Т; 2Т; 2,5Т; 3,j i :.. 4Т.

; помощью им1г/: ьснь;х г1С тсдоьл- тельностей первого р/зсиреде ; 18 формируются рггулчрньи; lio --:;. доват. пь- ности прямоугольных импульсов 2Т: последовательность поступающая на первый элемент 5 запрета (через пср- вьй триггер 19), и последовательность коротких импульсов, поступающа;- на регистр 16 сдвига (через второй элемент ИЛИ 20) .

Второй распределитель -34 формирует шесть импульсных последовательностей, сдвинутых относительно фронтов опорных импульсов ИЦИ соответственно на 0,5Т; Т; 1,5Т; 2Т; 2,5Т; ЗТ. Эти импульсные последовательности используются для формирования с помощью приемного триггера 41 последовательности прямоугольных импульсов длительностью 2т, поступакнщгх на вход управления третьего элемента 44 запрета; с помощью четвертого элемента ИЛИ 40 - последовательности сдвоенных коротких импульсов, поступаю- пцтх на счетный вход формируюп;рго триггера 42, входы управления второго ключа 36 и формирователя 37 символов; с помощью пятого элемента ШТИ - последовательности сдвоенных коротких импульсов, поступающих через четвертый ключ 43 на второй вход третьего элемента ИЩ1 39.

Установка формирующег о триггера 42 в исходное состояние, определяемое предшествующим символом ДМ-сигнала, обеспечивается с помощью второго элемента 25 запрета и третьего ключа 38.

Таким образом, предлагаемое устройство возволяет уменьшить влияние низкоскоростной цифровой информации на передачу анапоговых сообщений за счет укрупнения вставок НЦИ и пред- ьюкажения ДМ-сигнала с учетом исключаемых -информационных символов;

Формула изобретения

1. Устройство для передачи дополнительной низкоскоростной цифровой информации по каналу связи с дельта- модуляцией, содержащее на передающей стороне последовательно соединенные кодер, вход синхронизации которого соединен с входом синхронизации передающей стороны, первый блок коррекиии, rirpBhiii :)Jipr-(jnT ИЛИ и riei Hi.n i

фОрМНрСШаТСЛ}-) .OГI , r C pFi Jli }.

nepBi.rfi и второй лхолм которого миля- юте л соответственно .,i;UiW

входом и ЛХОДОМ С1П ХрОНИЧаЦ11И 1(рГ - ДЛЧЛ низкоскоростной IUl;| p)fii)H ИНформащ1И, нервьц 1 элемент чапрета, а на приемной стороне, coe;inHf .ifmi с передающей стороной через цифровой тракт передачи, декодер, вход син- хронизлчцп кото{)ого соединен с входо синхрон11за1Ц1и приемной стороны, последовательно соединенн.1е второГг к:Гюч и формирователь символов низкоск о- рс стной Ш1фровой ин(|)орма;1,ии, второй вход которого соединен с вхсхчом синх11ониза1и1и приема низкоскоростной цисГ)рС1ВО}1 информации, о т л и ч а ю - III е е с я тем, что, с целью умен},- шения уровня искажений передаваемого дельта-модулирован1,ого сигнала, в него введет,1 на иередяюшсй сто1)оне пос.ледовательно соединенные первьпЧ бдок 3издержки, вход которого подключен к кодера и объединен с rie)BbtM входом введенного второг о блока коррекции, второй п.лсж задержки и первый (}и1рмирояате:1ь коротких импульсов, выход которого подключен к nopBoNiv входу первого элемента запрета, первой , последовательно соединенные первый делите„ ть час- готы, вход которотл) объедиН1;н с вто- ръв- входом I epBoi o ключа, и первьц расп1)еделитель, последовательно соединенные B j-орой элемент ИЛИ и регис т сдвига, вход синхро})иза:1,ии KoTopoi o подключен к соответствующим входам первого фор гирователя коротких импульсов, кодера, первого и второго блоков задержки, первого распределителя, вторым входам первого и второг блоков корреир1и, третьи входы которых подключены к первому выходу пер- Doro распределителя, второй и пятый выходы которого подключены соответственно к установочным и сбросовому входам первого триггера, а третий и четвертый выходы - к первому и второму входам второго э. темента ИЛИ, причем выход, первого ключа через регистр сдвиги подключен к второму входу первого элемента ИЛИ, третий вход которого подключен к выходу первого эдемента запрета, второй и третий входы которого соединены соответственно с выходом первого триггера и первым вьиодом второго блока коррек0

5

0

5

0

5

0

5

0

5

ш:и, чспчнртьи вход которого объединен с входом второго блока задержки и четвергым вхо;юм первого блока кор- рекпии, пятый вход которого соединен с iiHTiiiM в1-с-;одом второго блока коррекции и подключен к выходу первого элемента И, первый и второй входы которого ггодключены соответственно к вто- рьм ныходам первого и второго блоков коррекпли, а на приемной стороне - последовательно соединенные второй формирователь символов, выход которого подключен к входу второго ключа, управляющим входам третьего ключа и BTopoi tj элемента запрета, второй фор- м)фователь коротких импульсов, третий элемент запрета, третиГ элемент H lH и трети формирователь символов, выход которого соединен с«входом декодера, последовательно соединенные второй делитель частоты и второй распределитель, последовательно соеди- HBHHi.ie четвертый элемент ИЛИ, фор- olpyю Щ й триггер и четвертый ключ, вььчод которого подключен к второмл входу третьего элемента ИЛИ, последовательно соединенные пятый элемент ИМИ и четвертый ключ, приемный триг- 1-ер, нъкод которого соединен с уп- равляю1Ц 1м входом третьего элемента запрета, причем вход синхронизагши декодера соединен с соответствуюощми входами второго формирователя коротких импульсов, второго и третьего ||)ормирователей символов, второго распределителя, ОТОРО выход, которого

гое.линен с первым входом четвертого элемента ИЛИ и входом установки приемного триггера, вход сброса которого подключен к шecтo fy выходу второго распреде;и1теля, четверты и пятый выходы которого соединены соответственно с вторым входом четвертого элемента iUIH и первым входом пятого эдемента ИЛИ., второй вход которого подключен к третьем вьсчоду второго распределителя, первый выход которого соединен через третий ключ с установочным входом формирующего триггера, а через второй элемент запрета под- ключ ен к входу сброса формирующего тригг ера, счетный вход которого подключен к управляющему входу второго ключа и третьему- входу формирователя символов низкоскоростиой цифровой информации, второй вход которого сое- цинен с входом второго делителя час тоты.

2. Устройство по П.1, отличающееся тем, что первый блок коррек:1ии содержит последовательно соединенные первьй инвертор, второй элемент И, второй триггер, третий элемент И и элемент задержки, выход которого является первым выходом первого блока коррекции, первьш и второй входы которого являются со- ответственно входаю первого и второго инверторов, выход которого подключен к вторым входам второго и третьего элементов И, третий вход которого объединен с вторым входом элемента задержки и является вторым входом первого блока коррек1Ц и, третий и пятый входы которого являются соответственно третьим входом второго элемента И вторым входом второго тригге- ра, третий вход которого соединен с выходом третьего элемента И, а выход является вторым выходом первого блока коррекции.

3. VcTpoi icTBO по П.1, о т л -и - чающееся тем, то BTCJ-CH ; коррек и1И содержит последо1 атс:1}..но соединенные четверть элемент И, первый и второй вхолы которого яв..яются соответственно пефвым и четвертин входами второго блока коррекции, третий триггер, второй вход которог О является пятым входом второго блока коррекции, пятый элемент И и формирователь импульсов, выход которого является первым выходом второго блока коррекции, второй вход которого является вторыьо входами фор- М1 рователя импульсов и пятого элемента И, третий вход которого объединен с вторым входом четвертого элемента И, а вьгход пятого элемента И соединен с третьим входом третьего триггера, вьгход которого является вторым выходом второго блока коррекции, третий lixo; , которого является третьим входом четвертого элемента И.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для одновременной передачи аналогового сигнала методом дельтамодуляции и двоичного сигнала низкоскоростной дискретной информации | 1976 |

|

SU604181A1 |

| Устройство для одновременной передачи дельта-модулированного сигнала и двоичного сигнала низкоскоростной дискретной информации | 1982 |

|

SU1077060A1 |

| Устройство для асинхронного переприема дельта-модулированного сигнала | 1989 |

|

SU1665516A1 |

| Устройство для отображения символов на экране электронно-лучевой трубки | 1981 |

|

SU970435A1 |

| Устройство для формирования изображений на экране электронно-лучевой трубки | 1982 |

|

SU1164776A1 |

| Устройство для отображения символов на экране электронно-лучевой трубки | 1985 |

|

SU1247919A1 |

| УСТРОЙСТВО ДЛЯ ТРЕНИРОВКИ ОПЕРАТОРОВ | 1991 |

|

RU2020599C1 |

| Адаптивное устройство для обучения языкам | 1987 |

|

SU1441445A1 |

| Устройство для отображения информации | 1986 |

|

SU1446642A1 |

| Устройство для формирования изображения на экране электронно-лучевой трубки | 1982 |

|

SU1070600A1 |

Изобретение относится к технике связи. Цель изобретения - уменьшение уровня искажений передаваемого дельта-модулированного (ДМ) сигнала. Устройство содержит передающую и приемную стороны. На передающей стороне формируется чередующаяся последовательность 2-элементных комбинаций символов низкоскоростной цифровой информации (НЦИ) и (N -2)-элементных отрезков ДМ-сигнала с учетом осуществляемого предыскажения. Этот сформированный сигнал из цифрового тракта передачи поступает на приемную сторону, где происходит его разделение на составляющие. При этом осуществляется восстановление ДМ-сигнала и преобразование символов НЦИ к нормированному виду. Устройство позволяет уменьшить влияние НЦИ на передачу аналоговых сообщений за счет укрупнения вставок НЦИ и предыскажения ДМ-сигнала с учетом исключаемых информационных символов. 2 з.п. ф-лы, 2 ил.

cpup2

| Устройство для одновременной передачи аналогового сигнала методом дельтамодуляции и двоичного сигнала низкоскоростной дискретной информации | 1976 |

|

SU604181A1 |

| Очаг для массовой варки пищи, выпечки хлеба и кипячения воды | 1921 |

|

SU4A1 |

Авторы

Даты

1989-07-15—Публикация

1987-10-02—Подача