(54) УСТРОЙСТВО ДЛЯ ОДНОВРЕМЕННОЙ ПЕРЕДАЧИ

АНАЛОГОВОГО СИГНАЛА МЕТОДОМ ДЕЛЬТА-МОДУЛЯЦИИ И ДВОИЧНОГО СИГНАЛА НИЗКОСКОРОСТНОЙ

ДИСКРЕТНОЙ ИНФОРМАЦИИ . 1.2

этом выход ключа подключен ко второму входу элемента ИЛИ, а ка приемной стороне - дельта-демодулятор, на управляющий вход которого поданы импульсы тактовой частоты, а выход является выходом аналогового сигнала, и последовательно соединенные ключ и формирователь-двоичного сигнала ИДИ, при этом сигнальный вход дельта-демодулятора соединен с первым входом ключа, а на управляющие входы ключа и формирователя двоичного сигнала ИДИ поданы иипульсы опорной частоты ИДИ, на передающей стороне введены последовательно соединенные блок анализа и блок коррекции, при этом первые входы блоков анализа и коррекции подключены к выходу дел1та-модулятора, вторые входы - подключены ко второму входу ключа, выход ко: торого соединён с третьим входом блока анализа, при этом первый выход блока коррекции подключен к третьему входу элемента запрета, а второй - подключен к третьему входу элемента ИЛИ, кроме того блок коррекции выполнен в виде элементов запрета и вставления импульсов, выходы которых, являющиеся соответственно первым и вторым выходами блока коррекции, через запоминающие блоки подключены ко входам элемента совпадения и к первым входам .элементов запрета и вставления импульсов, а выход элемента совпадения соединен с управляющи,ми входами запоминающих блоков, при этом вторые входы элементов запрета и вставления импульсов являются пербым входом блока коррекции, третьи входы - являются вторым входом блока коррекции, а третьи входы запоминающих блоков являются соответственно третьим и четвертым входами блока коррекции.

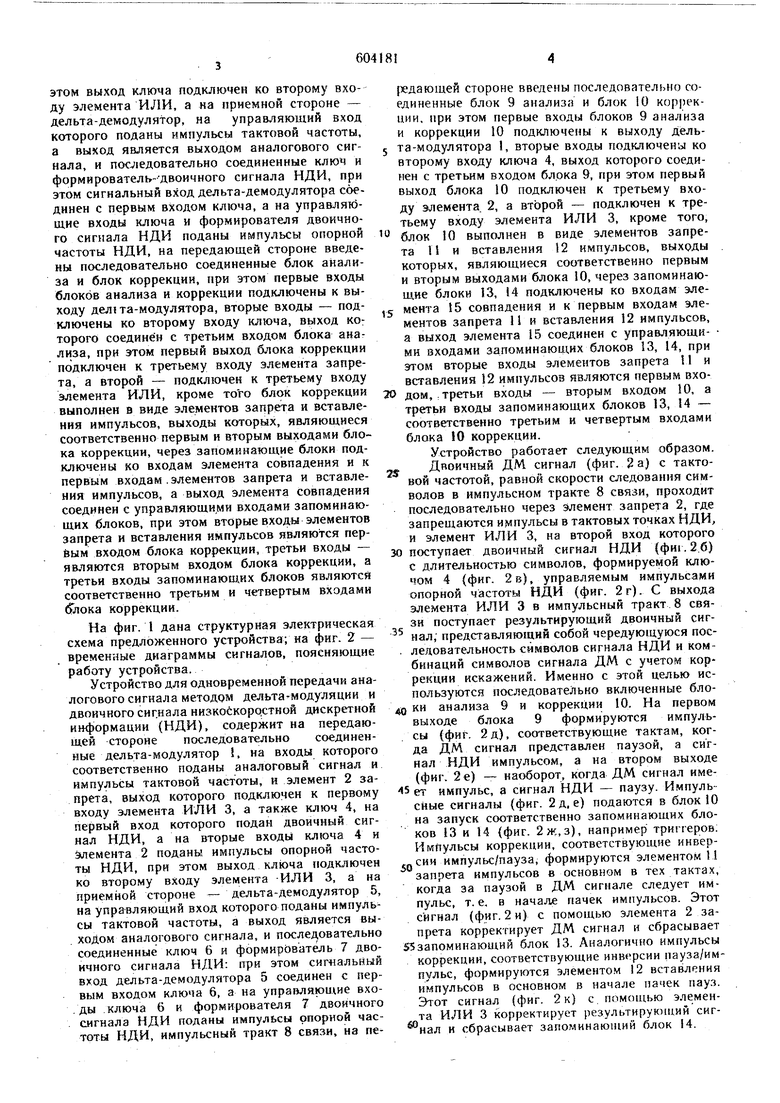

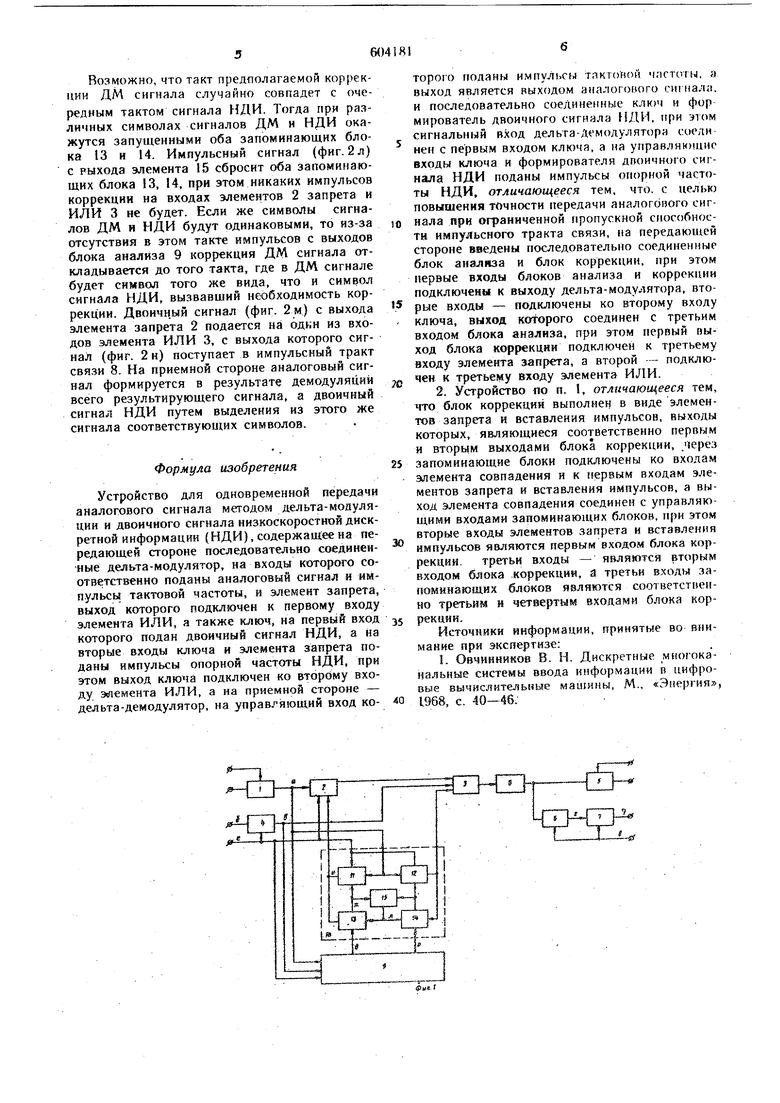

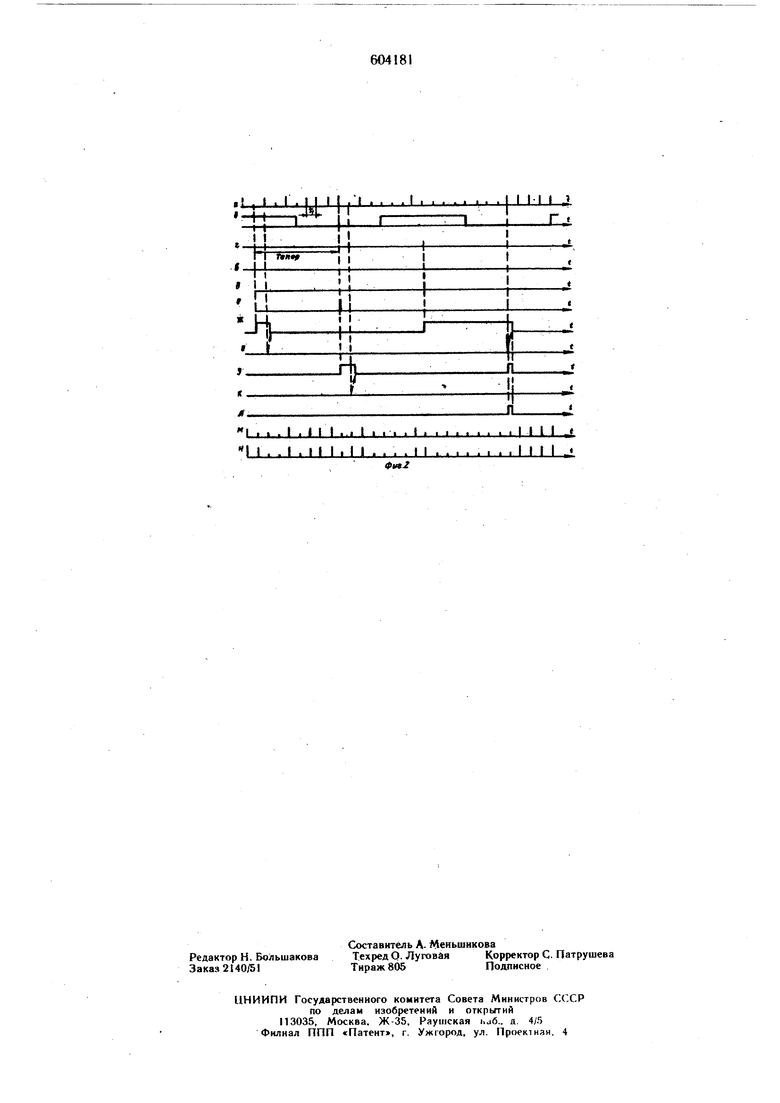

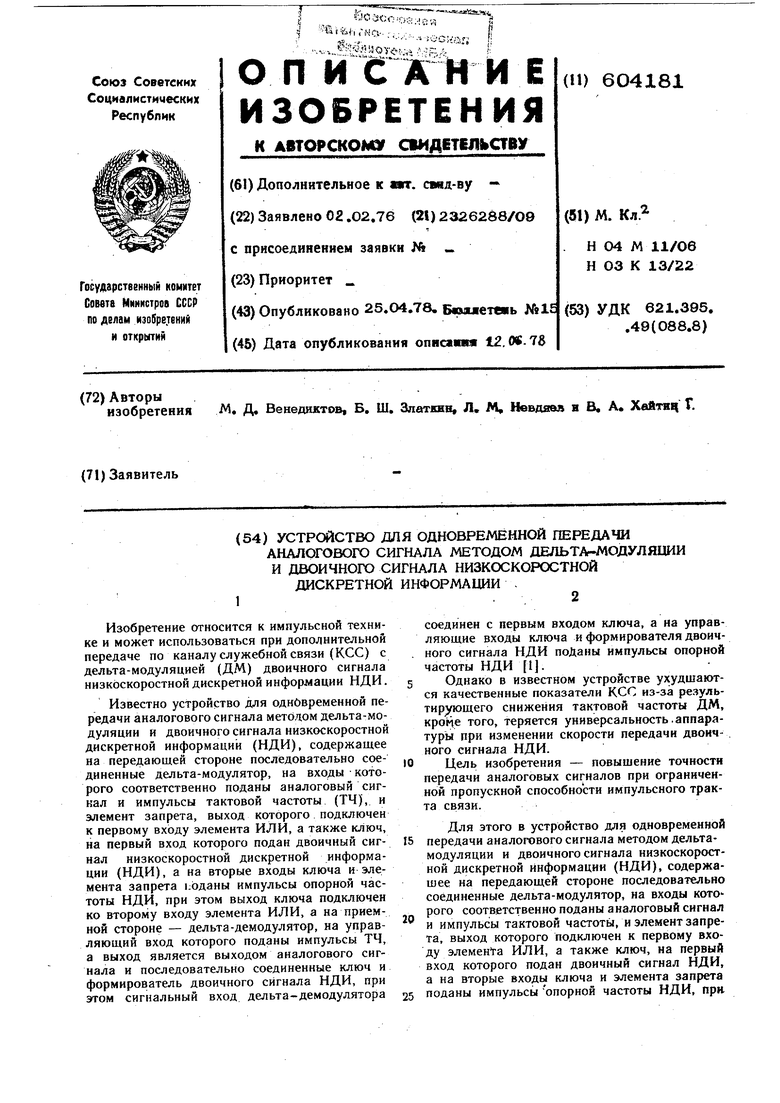

На фиг. 1 дана структурная электрическая схема предложенного устройства; на фиг. 2 - временные диаграммы сигналов, поясняющие работу устройства.

Устройство для одновременной передачи аналогового сигнала методом дельта модуляции и двоичного сигнала низкобкорцстной дискретной информации (НДИ), содержит на передающей стороне последовательно соединенные дельта-модулятор , на входы которого соответственно поданы аналоговый сигнал и импульсы тактовой частоты, и элемент 2 запрета, выход которого подключен к первому входу элемента ИЛИ 3, а также ключ 4, на первый вход которого подан двоичный сигнал НДИ, а на вторые входы ключа 4 и Элемента 2 поданы импульсы опорной частоты НДИ, при этом выход клк)ча подключен ко второму входу элемента ИЛИ 3, а на приемной стороне - дельта-демодулятор 5, на управляющий вход которого поданы импульсы тактовой частоты, а выход является выхоДом аналогового сигнала, и последовательно соединенные ключ 6 и формирователь 7 двоичного сигнала ИДИ: при этом сигнальный вход дельта-демодулятора 5 соединен с первым входом ключа 6, а на управляющие вхо. ды .ключа 6 и формирователя 7 двоичного сигнала НДИ поданы импульсы опорной частоты НДИ, импульсный тракт 8 связи, на пе(йдаюшей стороне введены последовательно соединенные блок 9 анализа н блок 10 коррекции, при этом первые входы блоков 9 анализа и коррекции 10 подключены к выходу дельта-модулятора 1, вторые входы подключены ко второму входу ключа 4, выход которого соединен с третьим входом блока 9, при этом первый выход блока 10 подключен к третьему входу элемента 2, а второй - подключен к третьему входу элемента ИЛИ 3, кроме того, блок 10 выполнен в виде элементов запрета П и вставления 12 импульсов, выходы которых, являющиеся соответственно первым и вторым выходами блока 10, через запоминающие блоки 13, 4 подключены ко входам элемента 15 совпадения и к первым входам элементов запрета П и вставления 12 импульсов, а выход элемента 15 соединен с управляющи- ми входами запоминающих блоков 13, 14, при этом вторые входы элементов запрета 11 и вставления 12 импульсов являются первым вхоО дом, : третьи входы - вторым входом 10, а третьи входы запоминающих блоков 13, 14 - соответственно третьим и четвертым входами блока 0 коррекции.

Устройство работает следующим образом. g Двоичный ДМ сигнал (фиг. 2 а) с тактовой частотой, равной скорости следования символов в импульсном тракте 8 связи, проходит последовательно через элемент запрета 2, где запрещаются импульсы в тактовых точках НДИ, и элемент ИЛИ 3, на второй вход которого 0 поступает двоичный сигнал НДИ (фиг. 2.6) с длительностью символов, формируемой ключом 4 (фиг. 2 в), управляемым импульсами опорной частоты ИДИ (фиг. 2 г). С выхода элемента ИЛИ 3 в импульсный тракт 8 связи поступает результирующий двоичный сиг5нал, представляющий собой чередующуюся пос. ледовательность символов сигнала НДИ н комбинаций символов сигнала ДМ с учетом коррекции искажений. Именно с этой целью используются последовательно включенные блоки анализа 9 и коррекции 10. На первом выходе блока 9 формируются импуль. сы (фиг. 2д), соответствующие тактам, когда ДМ сигнал представлен паузой, а сигнал НДИ импульсом, а на втором выходе (фиг. 2е) - наоборот, когда ДМ сигнал имеет импульс, а сигнал НДИ - паузу. Импуль сные сигналы (фиг. 2д. е) подаются в блок 10 на запуск соответственно запоминающих блоков 13 и 14 (фиг. 2ж,з), например триггеров: ИмЛульсы коррекции, соответствующие инвер,-сии импульс/пауза, формируются элементом 1 запрета импульсов в основном в тех тактах, когда за паузой в ДМ сигнале следует импульс, т. е. в начала пачек импульсов. Этот сигнал (фиг. 2 и) с помощью элемента 2 запрета корректирует ДМ сигнал н сбрасывает S5запоминающий блок 13. Аналогично импульсы коррекции, соответствующие инверсии пауза/импульс, формируются элементом 12 вставления импульсов в основном в начале пачек пауз. Этот сигнал (фиг. 2 к) с, помощью элемента ИЛИ 3 корректирует результирук)п.1ий сиг®нал и сбрасывает запоминающий блок 14.

Возможно, что такт предполагаемой коррекции ДМ сигнала случайно совпадет с очередным тактом сигнала HZIH. Тогда при различных символах сигналов ДМ и ИДИ окажутся запущенными оба запоминающих блока 13 и 14. Импульсный сигнал (фиг. 2л) с рыхода элемента 15 сбросит оба запоминающих блока 13, 14, при этом никаких импульсов коррекции на входах элементов 2 запрета и ИЛИ 3 не будет. Если же символы сигналов ДМ и ИДИ будут одинаковыми, то из-за отсутствия в этом такте импульсов с выходов блока анализа 9 коррекция ДМ сигнала откладывается до того такта, где в ДМ сигнале будет символ того же вида, что и символ сигнала ИДИ, вызвавщий необходимость коррекции. Двоичцый сигнал (фиг. 2м) с выхода элемента запрета 2 подается на один из входов элемента ИЛИ 3, с выхода которого сигнал (фиг. 2 и) поступает в импульсный тракт связи 8. На приемной стороне аналоговый сигнал формируется в результате демодуляций всего результирующего сигнала, а двоичный сигнал ИДИ путем выделения из этого же сигнала соответствующих символов.

Формула изобретения

Устройство для одновременной передачи аналогового сигнала методом дельта-модуляции и двоичного сигнала низкоскоростной дискретной информации (ИДИ), содержащее на передающей стороне последовательно соединенные дельта-модулятор, на входы которого соответственно поданы аналоговый сигнал и импульсь тактовой частоты, и элемент запрета, выход которого подключен к первому входу элемента ИЛИ, а также ключ, на первый вход которого подан двоичный сигнал ИДИ, а На вторые входы ключа и элемента запрета поданы импульсы опорной частоты ИДИ, при этом выход ключа подключен ко второму входу элемента ИЛИ, а на приемной стороне - дельта-демодулятор, на управляющий вход которого поданы импульсы тлкт(ж(п ( чпстоты, а выход является выходом аиа-чогового сшналл. и последовательно соединенные ключ и фор мирователь двоичного сигнала ИДИ, при этом сигнальный вход дельта-Демодулятора соели нен с первым входом ключа, а на управлянццнс входы ключа и формирователя двоичного сигнала ИДИ поданы импульсы опорной частоты ИДИ, отличающееся тем, что. с целью повыгшения точности передачи аналогового curio нала при ограниченной пропускной способности импульсного тракта связи, на передающей стороне введены последовательно соединенные блок аналяза и блок коррекции, при этом первые входы блоков анализа и коррекции подключены к выходу дельта-модулятора, вторые входы - подключены ко второму входу ключа, выход которого соединен с третьим входом блока анализа, при этом первый выход блока коррекции подключен к третьему входу элемента запрета, а второй - подклюQ чей к третьему входу элемента ИЛИ.

2. Устройство flo п. 1, отличающееся тем, что блок коррекций выполнен в виде элементов запрета и вставления импульсов, выходы которых, являющиеся соответственно первым и вторим выходами блока коррек 1ии, через 5 запоминающие блоки подключены ко входам элемента совпадения и к первым входам элементов запрета и вставления импульсов, а выход элемента совпадения соединен с управляющими входами запоминающих блоков, при этом вторые входы элементов запрета н вставлення

0 импульсов являются первым входом блока коррекции, третьи входы - являются вторым входом блока коррекции, а третьи входы запоминающих блоков являются соответственно третьим и четвертым входами блока кор5 рекцни.

Источники информации, принятые во внимание при экспертизе:

. Овчинников В. Н. Дискретные многоканальные системы ввода информации в цифровые вычислительные машины, М., «Энергия, 1968, с. 40-46.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для одновременной передачи дельта-модулированного сигнала и двоичного сигнала низкоскоростной дискретной информации | 1985 |

|

SU1248074A1 |

| Устройство для одновременной передачи дельта-модулированного сигнала и двоичного сигнала низкоскоростной дискретной информации | 1982 |

|

SU1077060A1 |

| Устройство для блокового кодирования дельта-модулированного сигнала | 1984 |

|

SU1275780A1 |

| Устройство для одновременной передачи дельта-модулированного сигнала и двоичного сигнала низкоскоростной дискретной информации | 1985 |

|

SU1259516A2 |

| Устройство для передачи дополнительной низкоскоростной цифровой информации по каналу связи с дельта-модуляцией | 1987 |

|

SU1494245A1 |

| Устройство для передачи и приема дельта-модулированного сигнала | 1983 |

|

SU1095396A1 |

| Устройство для асинхронного переприема дельта-модулированного сигнала | 1989 |

|

SU1665516A1 |

| Дельта-модулятор для передачи речевых сигналов | 1990 |

|

SU1795554A1 |

| Дельта-демодулятор для телефонного канала | 1976 |

|

SU640425A1 |

| СПОСОБ ВОССТАНОВЛЕНИЯ ИСХОДНОГО СИГНАЛА ПРИ ДЕЛЬТА-МОДУЛЯЦИИ И УСТРОЙСТВО ДЛЯ ДЕЛЬТА-ДЕМОДУЛЯЦИИ | 1994 |

|

RU2129333C1 |

Авторы

Даты

1978-04-25—Публикация

1976-02-20—Подача