О

о ел ел

а

Изобретение относится к технике связи и вычислительной технике и может быть использовано в цифровых системах передачи например в радиорелейных системах для организации служебных каналов свяхи путем сопряжения независимых дельта-моду- лированных (ДМ) сигналов по цифре.

Цель изобретения - повышение точности устройства за счет нерегулярной коррекции скорости передачи ДМ-сигнала,

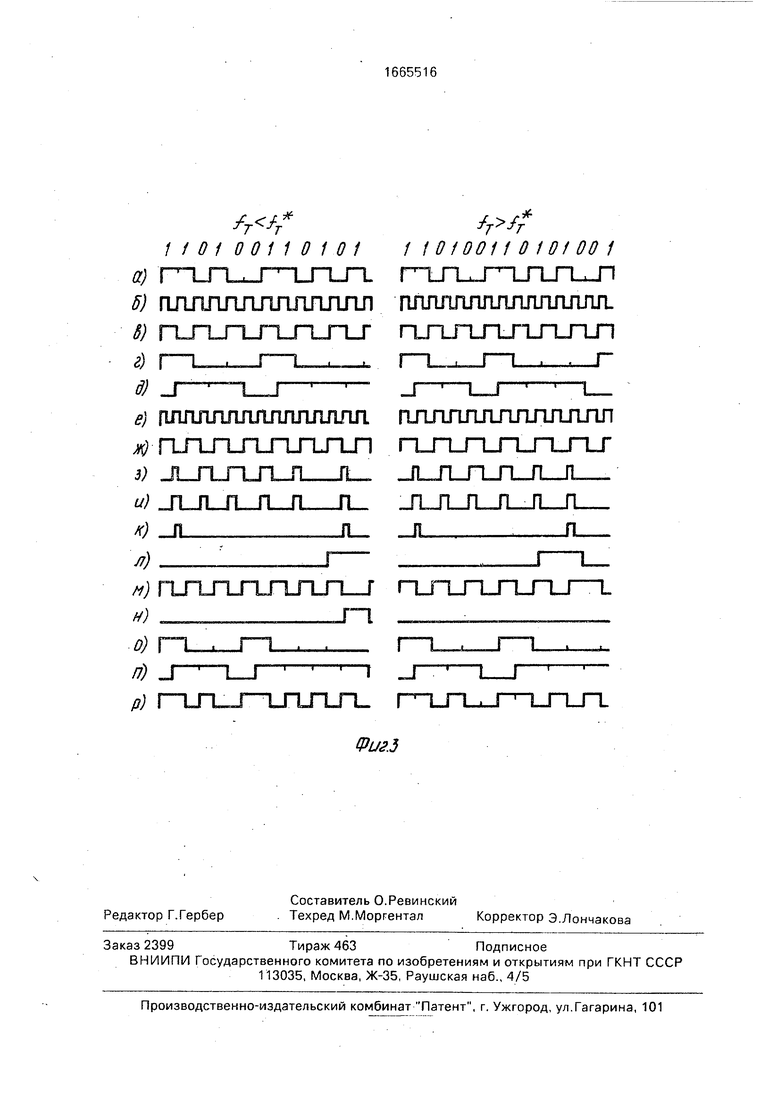

На фиг. 1 приведена функциональная схема устройства; на фиг. 2 - выполнение решающего блока; на фиг. 3 - временные диаграммы работы.

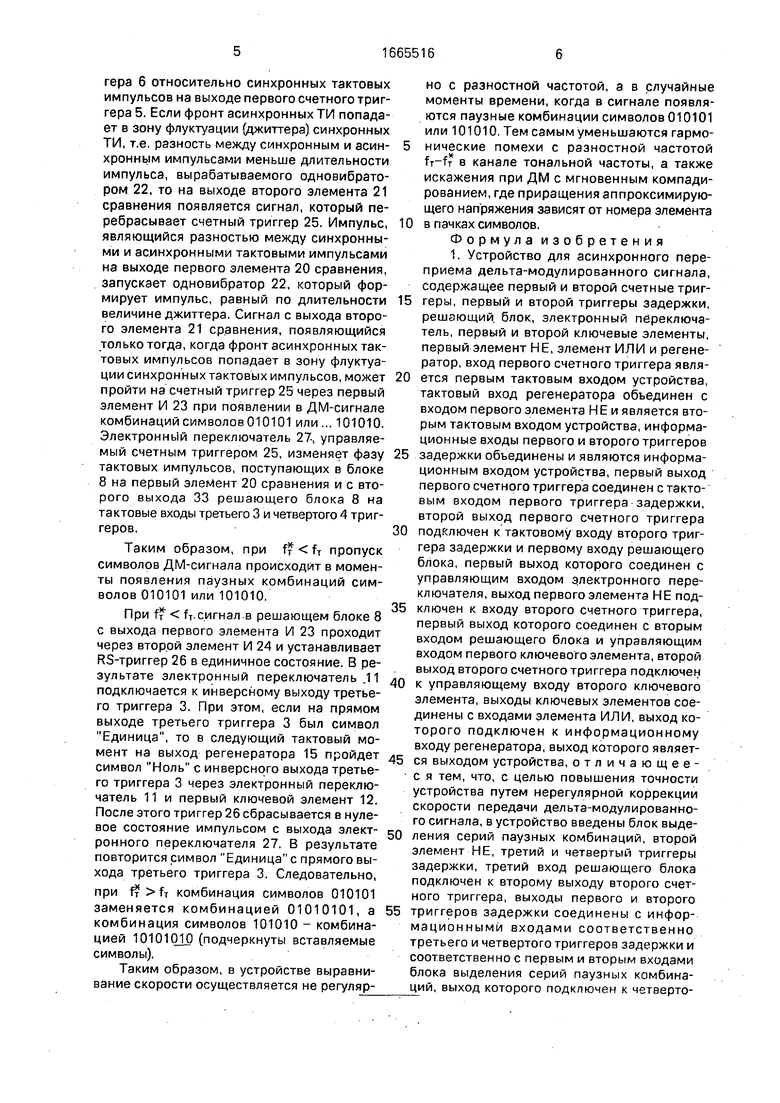

Устройство содержит первый-четвертый триггеры 1-4 задержки, первый 5 и второй 6 счетные триггеры, блок 7 выделения серий паузных комбинаций, решающий блок 8, первый 9 и второй 10 элементы НЕ, электронный переключатель 11, первый 12 и второй 13 ключевые элементы, элемент ИЛИ 14 и регенератор 15. На фиг. 1 обозначены информационный вход 16, первый 17, второй 18 тактовые входы, выход 19.

Блок 7 выделения серий паузных комбинаций символов 010101/101010 в простейшем случае может быть реализован на триггере и элементе равнозначности,

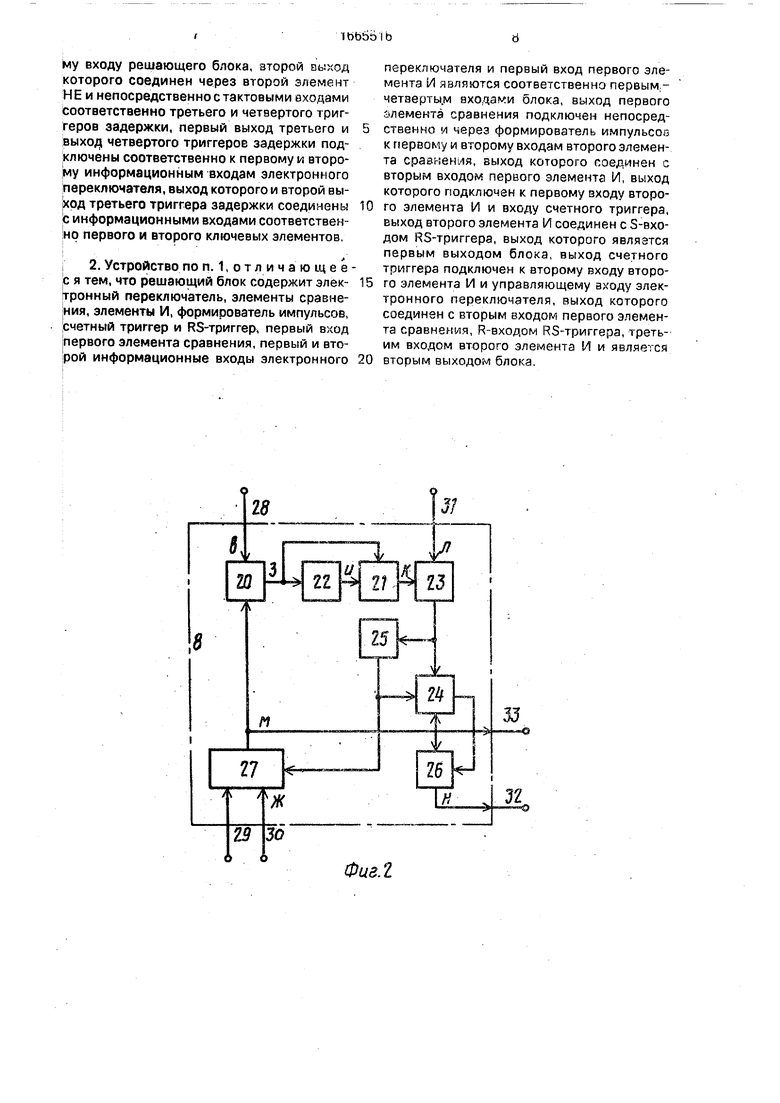

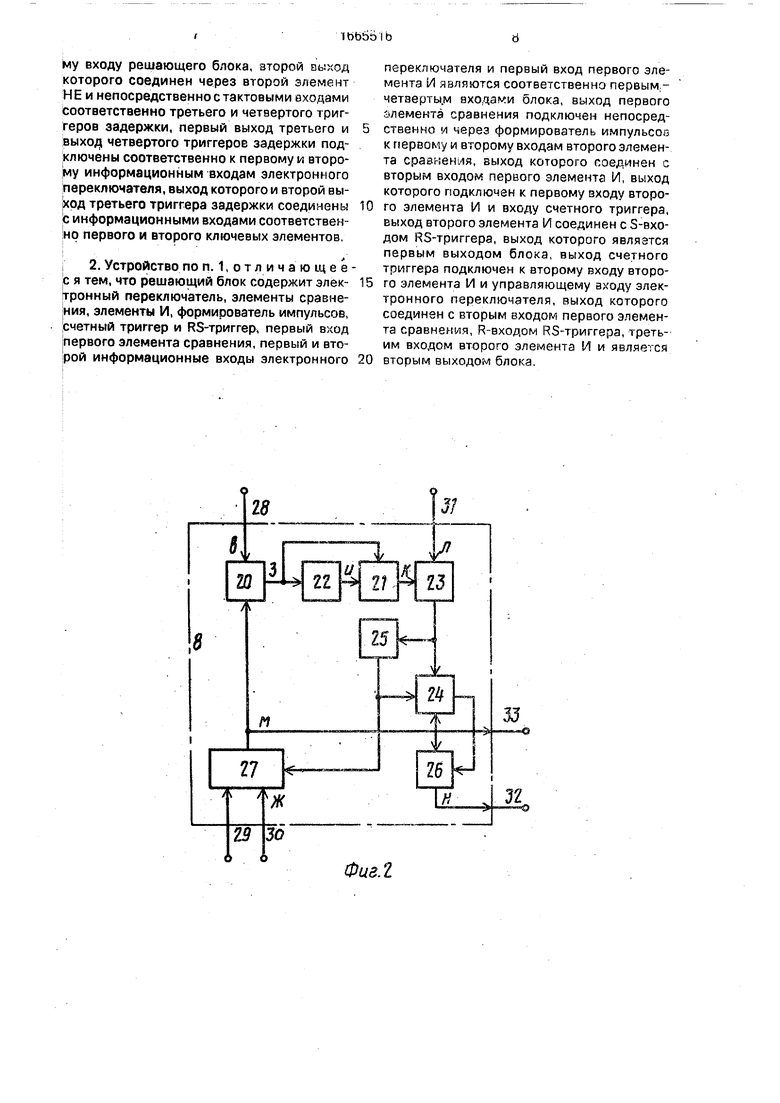

- Решающий блок 8 выполнен (фиг. 2) на первом 20 и втором 21 элементах сравнения, формирователе 22 импульсов (одновиб- раторе), первом 23 и втором 24 элементах И, счетном триггере 25, RS-триггере 26 и электронном переключателе 27. На фиг. 2 обозначены первый-четвертый входы 28-31 и первый 32 и второй 33 выходы блока 8.

Регенератор 15 выполнен так же, как и в известном устройстве.

На фиг, 3 обозначены следующие сигналы: а - входной ДМ-сигнал на входе 16; б - тактовые импульсы с частотой fT на входе 17; в - сигнал на втором выходе первого счетного триггера 5; г, д - сигналы на выходах сответственно первого 1 и второго 2 триггеров задержки; е - тактовые импульсы с частотой fT на входе 18; ж - сигнал на втором выходе второго счетного триггера б; з - сигнал на выходе первого элемента 20 сравнения решающего блока 8; и- сигнал на выходе формирователя 22 импульсов блока 8; к - сигнал на выходе второго элемента 21 сравнения блока 8;. л - сигнал с выхода блока 7 выделения серий паузных комбинаций; м, н - сигналы соответственно на втором 33 и первом 32 выходах решающего блока 8; о, п - сигналы на выходах соответственно первого 12 и второго 13 ключевых элементов; р - сигнал на выходе 19 устройства.

Устройство работает следующим образом.

Входной ДМ-сигнал, представляющий собой случайную последовательность двог ичных символов 1 и 0 длительностью , Т f т, поступает из линии связи на информационный вход 16 устройства,откуда подается на информационные входы первого 1 и второго 2 триггеров. Одновременно синхронная последовательность сопровождающих синхронных тактовых импульсов (ТИ) в

0 виде меандра с длительностью г Т/2 посту- пает от устройства тактовой синхронизации (не показано) через вход 17 синхронных тактовых импульсов на вход первого счетного триггера 5. При этом символы ДМ-сигнала

5 и синхронные тактовые импульсы сопровождаются фазовыми флуктуациями. Асинх- ронная последовательность тактовых импульсов также в виде меандра сдлителы ностью г Т /2 поступает без фазовых флук0 туаций, например от местного кварцевого генератора, на вход 18 асинхронных тактовых импульсов устройства.

С противофазных выходов первого счет-1 ного триггера 5 синхронные тактовые им5 пульсы уже с длительностью г Т и с частотой, поделенной в два раза, подаются на тактовые входы первого 1 и второго 2 триггеров. В результате ДМ-сигнал разделяется на две последовательности с длитель0 ностью символов т 2Т, одна из которых содержит четные, а другая -- нечетные элементы входного ДМ-сигнала, Далее, эти по- следовательности четных и нечетных элементоа ДМ-сигнала поступают соответ5 ственно на информационные входы третьего 3 и четвертого 4 триггеров, которые тактируются выходными сигналами решающего блока 8, причем четвертый триггер 4 подключен к второму выходу 33

0 решающего блока 8 непосредственно, а третий триггер 3 - через второй элемент НЕ 10. Последовательность четных элементов ДМ- сигнала преходит на вход элемента ИЛИ 14 через второй ключевой элемент 13. На дру5 гой вход элемента ИЛ И 14 может поступать; или последовательность нечетных элементов ДМ-сигнала через электронный переключатель 11 и первый ключевой элемент 12, млиже инвертированная последователь0 ность четных элементов ДМ-сигнала с противофазного выхода третьего триггера 3.

Элемент ИЛИ 14 преобразует последовательности четных и нечетных элементов в общий ДМ-сигнал. Выходной регенератор

5 15 обеспечивает синфазность ДМ-сигнала с асинхронными тактовыми импульсами.

Решающий блок 8 формирует свои сигналы путем сопоставления взаимного расположения асинхронных тактовых импульсов на выходе второго счетного триггера 6 относительно синхронных тактовых импульсов на выходе первого счетного триггера 5. Если фронт асинхронных ТИ попадает в зону флуктуации (джиггера) синхронных ТИ, т.е. разность между синхронным и асинхронным импульсами меньше длительности импульса, вырабатываемого одновибрато- ром 22, то на выходе второго элемента 21 сравнения появляется сигнал, который перебрасывает счетный триггер 25. Импульс, являющийся разностью между синхронными и асинхронными тактовыми импульсами на выходе первого элемента 20 сравнения, запускает одновибратор 22, который формирует импульс, равный по длительности величине джиттера. Сигнал с выхода второго элемента 21 сравнения, появляющийся только тогда, когда фронт асинхронных тактовых импульсов попадает в зону флуктуации синхронных тактовых импульсов, может пройти на счетный триггер 25 через первый элемент И 23 при появлении в ДМ-сигнале комбинаций символов010101 или... 101010. Электронный переключатель 27, управляемый счетным триггером 25, изменяет фазу тактовых импульсов, поступающих в блоке 8 на первый элемент 20 сравнения и с второго выхода 33 решающего блока 8 на тактовые входы третьего 3 и четвертого 4 триггеров.

Таким образом, при f fT пропуск символов ДМ-сигнала происходит в моменты появления паузных комбинаций символов 010101 или 101010.

При f fT сигнал в решающем блоке 8 с выхода первого элемента И 23 проходит через второй элемент И 24 и устанавливает RS-триггер 26 в единичное состояние. В результате электронный переключатель .11 подключается к инверсному выходу третьего триггера 3. При этом, если на прямом выходе третьего триггера 3 был символ Единица, то в следующий тактовый момент на выход регенератора 15 пройдет символ Ноль с инверсного выхода третьего триггера 3 через электронный переключатель 11 и первый ключевой элемент 12. После этого триггер 26 сбрасывается в нулевое состояние импульсом с выхода электронного переключателя 27. В результате повторится символ Единица с прямого выхода третьего триггера 3. Следовательно,

при f f т комбинация символов 010101 заменяется комбинацией 01010101, а комбинация символов 101010 - комбинацией 101010 1Р (подчеркнуты вставляемые символы).

Таким образом, в устройстве выравнивание скорости осуществляется не регулярно с разностной частотой, а в случайные моменты времени, когда в сигнале появляются паузные комбинации символов 010101 или 101010. Тем самым уменьшаются гармо- 5 нические помехи с разностной частотой fr-fr в канале тональной частоты, а также искажения при ДМ с мгновенным компади- рованием, где приращения аппроксимирующего напряжения зависят от номера элемента

10 в пачках символов.

Формула изобретения 1. Устройство для асинхронного переприема дельта-модулированного сигнала, содержащее первый и второй счетные триг15 геры, первый и второй триггеры задержки, решающий блок, электронный переключатель, первый и второй ключевые элементы, первый элемент НЕ, элемент ИЛИ и регенератор, вход первого счетного триггера явля0 ется первым тактовым входом устройства, тактовый вход регенератора объединен с входом первого элемента НЕ и является вторым тактовым входом устройства, информационные входы первого и второго триггеров

5 задержки объединены и являются информационным входом устройства, первый выход первого счетного триггера соединен с тактовым входом первого триггера задержки, второй выход первого счетного триггера

0 подключен к тактовому входу второго триггера задержки и первому входу решающего блока, первый выход которого соединен с управляющим входом электронного переключателя, выход первого элемента НЕ под5 ключей к входу второго счетного триггера, первый выход которого соединен с вторым входом решающего блока и управляющим входом первого ключевого элемента, второй выход второго счетного триггера подключен

0 к управляющему входу второго ключевого элемента, выходы ключевых элементов соединены с входами элемента ИЛИ, выход которого подключен к информационному входу регенератора, выход которого являет5 ся выходом устройства, отличающее- с я тем, что, с целью повышения точности устройства путем нерегулярной коррекции скорости передачи дельта-модулированного сигнала, в устройство введены блок выде0 ления серий паузных комбинаций, второй элемент НЕ, третий и четвертый триггеры задержки, третий вход решающего блока подключен к второму выходу второго счетного триггера, выходы первого и второго

5 триггеров задержки соединены с информационными входами соответственно третьего и четвертого триггеров задержки и соответственно с первым и вторым входами блока выделения серий паузных комбинаций, выход которого подключен к четвертому входу решающего блока, второй выход которого соединен через второй элемент НЕ и непосредственно с тактовыми входами соответственно третьего и четвертого триггеров задержки, первый выход третьего и выход четвертого триггеров задержки подключены соответственно к первому и второ- му информационным входам электронного переключателя, выход которого и второй выход третьего триггера задержки соединены с информационными входами соответственно первого и второго ключевых элементов,

2. Устройство поп. 1,отличающее с я тем, что решающий блок содержит элек- тронный переключатель, элементы сравнения, элементы И, формирователь импульсов, счетный триггер и RS-триггер, первый вход первого элемента сравнения, первый и второй информационные входы электронного

переключателя и первый вход первого элемента И являются соответственно первым,- четверты.м входами блока, выход первого элемента сравнения подключен непосредственно и через формирователь импульсов к первому и второму входам второго элемента сравнения, выход которого соединен с вторым входом первого элемента И, выход которого подключен к первому входу второго элемента И и входу счетного триггера, выход второго элемента И соединен с S-вхо- дом RS-триггера, выход которого является первым выходом блока, выход счетного триггера подключен к второму входу второго элемента И и управляющему входу электронного переключателя, выход которого соединен с вторым входом первого элемента сравнения, R-входом RS-триггера, третьим входом второго элемента И и является вторым выходом блока.

| название | год | авторы | номер документа |

|---|---|---|---|

| Дельта-кодек | 1987 |

|

SU1499501A1 |

| Устройство подавления шумов вТЕлЕфОННОМ СлужЕбНОМ КАНАлЕ | 1979 |

|

SU794742A1 |

| Устройство для передачи дополнительной низкоскоростной цифровой информации по каналу связи с дельта-модуляцией | 1987 |

|

SU1494245A1 |

| Дельта-демодулятор для телефонного канала | 1976 |

|

SU640425A1 |

| Обнаружитель активности канала в системе с дельта-модуляцией | 1987 |

|

SU1506564A2 |

| Адаптивный регенератор | 1986 |

|

SU1363490A1 |

| Устройство асинхронного ввода двоичных сигналов в цифровой тракт систем связи с двухсторонними временными сдвигами | 1973 |

|

SU472468A1 |

| ПРЕОБРАЗОВАТЕЛЬ ПОСЛЕДОВАТЕЛЬНОГО КОДА В ПАРАЛЛЕЛЬНЫЙ | 1973 |

|

SU407302A1 |

| Система связи с асинхронной дельта-модуляцией | 1989 |

|

SU1624695A1 |

| Устройство объединения сигналов дельта-модуляции | 1972 |

|

SU476682A1 |

Изобретение относится к технике связи и вычислительной технике. Его использование в цифровых системах передачи позволяет повысить точность устройства за счет нерегулярной коррекции скорости передачи дельта - модулированного сигнала. Устройство содержит триггеры 1, 2 задержки, счетные триггеры 5, 6, решающий блок 8, элемент 9 НЕ, электронный переключатель 11, ключевые элементы 12, 13, элемент 14 ИЛИ и регенератор 15. Благодаря введению триггеров 3, 4 задержки, блока 7 выделения серий паузных комбинаций и элемента 10 НЕ в устройстве обеспечивается выравнивание скоростей не с разностной частотой, а в случайные моменты времени при появлении паузных комбинаций символов 010101 или 101010. 1 з.п. ф-лы, 3 ил.

ОО

J/

1 lЈ

Фиг.2

-f Г/

1 / 0 1 00110101

5) гигпллшшллллл

В) nJTJTJH-TTJ LJ

г)Г r

д)j r

; {шггллллягшлшшл

л flJTJTJTJ lJlJnj J JLJbTLTLJlJL

; лл

M} FTJlJTJlJlJnLJT J

/у;п

. .

p-L

/7} J

p) riJl J TJlJTJl т т1 / 010ОП 0 1 Of 00 1

mja j n riJi- n пхишгглллллпллял.

riJHJljnj-lJTrLn

rn . в-i . . rолллшглллпяпл

nj-Unjnj LFLJ JLJ1J1 JTJT-JL Jl TLJLJL-fl JL

ФигЗ

| Техника средств связи | |||

| Сер | |||

| Техника радиосвязи | |||

| Устройство для видения на расстоянии | 1915 |

|

SU1982A1 |

| Техника средств связи | |||

| Сер | |||

| Техника радиосвязи | |||

| Приспособление для установки двигателя в топках с получающими возвратно-поступательное перемещение колосниками | 1917 |

|

SU1985A1 |

| Способ очистки нефти и нефтяных продуктов и уничтожения их флюоресценции | 1921 |

|

SU31A1 |

| Устройство подавления шумов вТЕлЕфОННОМ СлужЕбНОМ КАНАлЕ | 1979 |

|

SU794742A1 |

| Очаг для массовой варки пищи, выпечки хлеба и кипячения воды | 1921 |

|

SU4A1 |

Авторы

Даты

1991-07-23—Публикация

1989-06-08—Подача