i

Ico

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для перевода слов с одного языка на другой | 1990 |

|

SU1802365A1 |

| Устройство для изучения языка | 1990 |

|

SU1785029A1 |

| Ассоциативное оперативное запоминающее устройство | 1989 |

|

SU1714682A1 |

| Устройство для поиска информации в памяти | 1985 |

|

SU1309041A1 |

| Устройство для поиска информации в ассоциативной памяти | 1988 |

|

SU1617460A1 |

| Устройство для сопряжения каналов передачи данных с ЭВМ | 1985 |

|

SU1226476A1 |

| Ассоциативное оперативное запоминающее устройство | 1988 |

|

SU1667155A1 |

| Устройство для обучения | 1980 |

|

SU907570A1 |

| Ассоциативное оперативное запоминающее устройство | 1987 |

|

SU1462420A1 |

| Электронный словарь для изучения иностранного языка | 1988 |

|

SU1702394A1 |

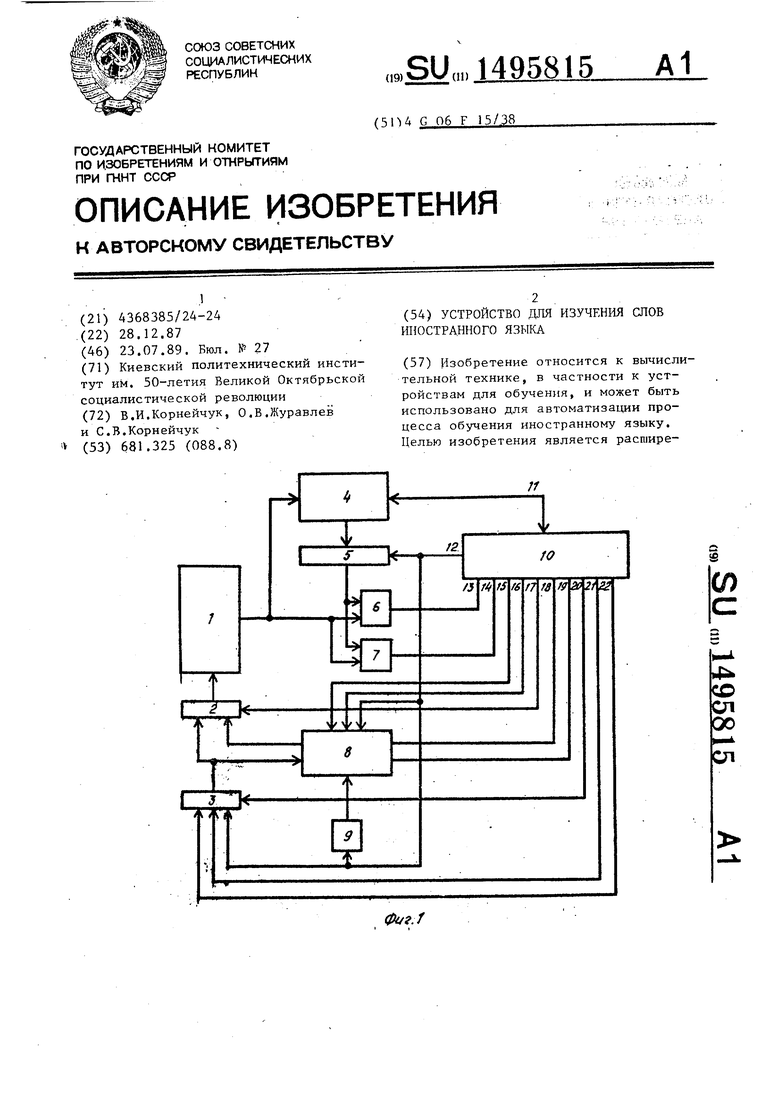

Изобретение относится к вычислительной технике, в частности к устройствам для обучения и может быть использовано для автоматизации процесса обучения иностранному языку. Целью изобретения является расширение функциональных возможностей устройства за счет выдачи переведенных значений слов, вводимых с однократной ошибкой. Устройство содержит блок 1 памяти слов, коммутатор 2, счетчик 3 адреса, блок 4 ввода и отображения, регистр 5 слова, схемы сравнения 6 и 7, блок 8 памяти адресов, генератор 9 импульсов, блок 10 управления. После введения пользователем при помощи блока 4 ввода и отображения слова на иностранном языке устройство сравнивает это слово со словами из блока памяти 1. Схемы 6 и 7 выполняют сравнение параллельно. Схема 7 учитывает возможность одной ошибки во введенном слове. Предполагается, что ошибка может быть в любой позиции и учитываются ошибки следующих типов: неправильная буква, пропущенная буква, лишняя буква. От пользователя не требуется указания места возможной ошибки. Поиск слова в блоке 1 ведется способом последовательного перебора. В результате поиска на экране индикатора блока 4 появляется либо введенное слово, если оно было найдено, либо слова, обнаруженные схемой 7. Кроме слов, вводится соответствующая справочная информация. 1 з.п. ф-лы, 2 ил.

4:

СО СП

сх (У1

149

ргие фуикциотга.ньиьгх яочможпостей

устройства ча счет вьщачи переяе- денных значений слов, вводимых с однократной ошибкой. Устройство содержит блок 1 памяти слов, KOMNtyra- тор 2, счетчик 3 адреса, блок 4 вво да и отображения, регистр 5 слова, схемы сравнения 6 и 7, беок 8 памяти адресов, генератор 9 импульсов, блок 10 управления. После введения пользователем при помопщ блока 4 ввода и отображения слова на иностраном языке устройство сравнивает это слово со словами из блока памяти 1. Схемы 6 и 7 выполняют сравнение параллельно. Схема 7 зачитывает возИзобретение относится к вычислительной технике, в частности к устройствам для обучения, и может быть использовано для автоматизации про- цесса обучения иностранному языку.

Целью изобретения является расширение функциональных возможностей за счет выдачи переведенных значений слов, вводимых с однократной ошибкой.

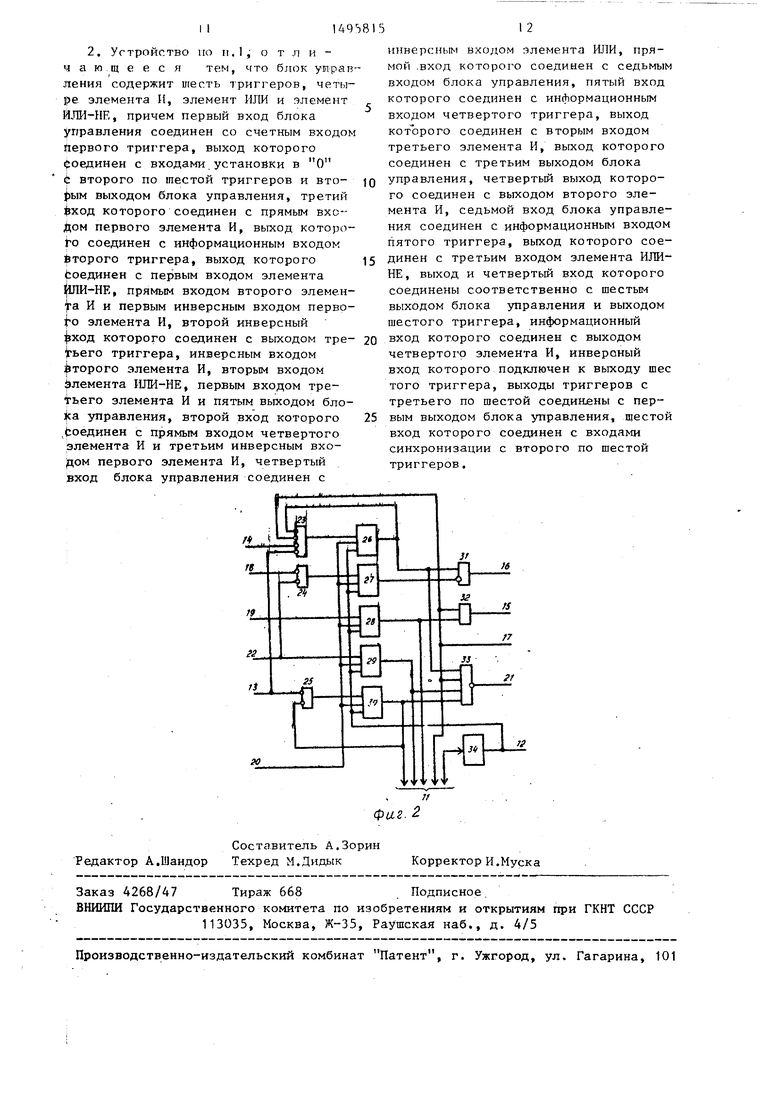

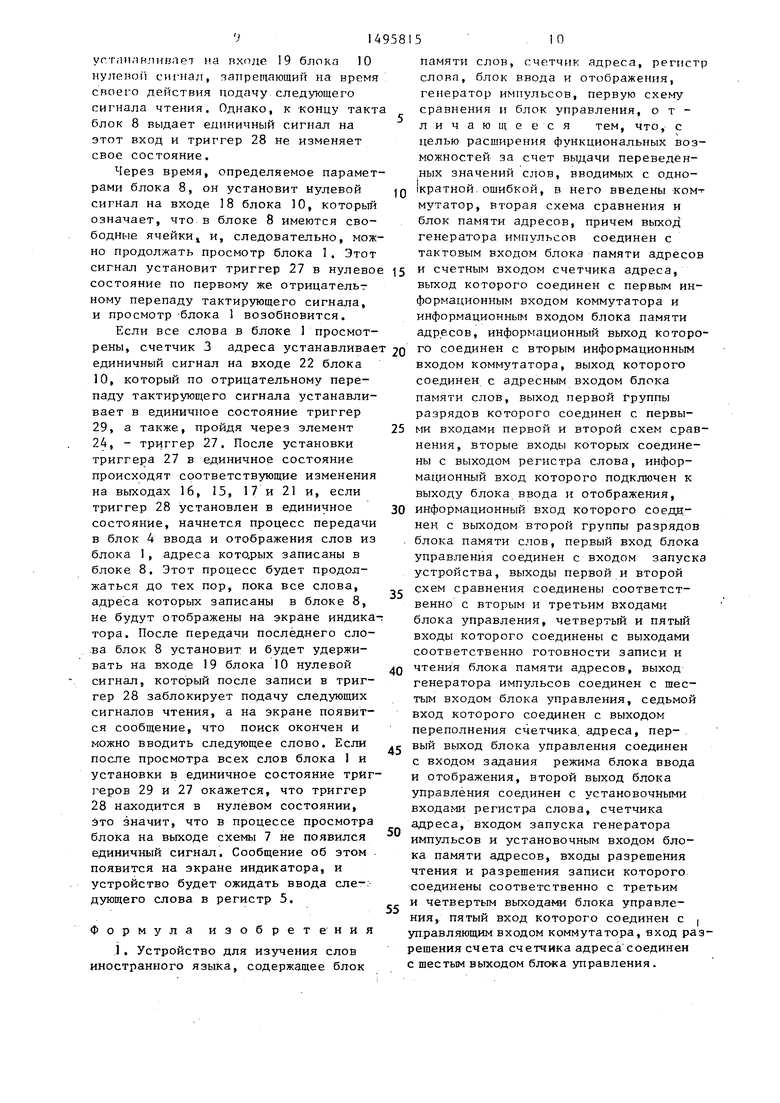

На фиг. представлена схема устройства для изучения слов иностранного языка; на фиг.2 - схема блока управления.

Устройство содержит блок 1 памяти слов, ко 1мутатор 2, счетчик 3 адреса блок 4 ввода и отображения, регистр 5 слова, схемы 6.и 7 сравнения, блок 8 памяти адресов, генератор 9 импуль сов, блок 10 управления, входы 11 устройства, выход 12 блока управле- : ния, входы 13 и 14 блока управления, (выходы 15 - 17 блока управления, входы 18 - 20 блока управления, выход 21 и вход 22 блока управления.

Блок управления содержит элемент И 23, элемент ИЛИ 24, элемент И 25, триггеры 26 - 30, элементы И 31 и 32

элемент РШИ-ПЕ 33 и триггер 34.

Устройство работает следующим образом.

Для включения устройства пользователь подает сигнал на вход триггера 34 (фиг.2). На выходе триггера 34 устанавливается сигнал высокого уровня, который устанавливает в состояние логического нуля триггеры 26-30, а также подается на выход 12

I

можность одной опшбки но введенном слове. Предполагается, что ошибка может быть в любой позиции и учитываются ошибки следующих типов: не- правильная буква, пропущенная буква, лишняя буква. От пользователя не требуется указания места возможной ошибки. Поиск слова в блоке 1 ведется способом последовательного перебора. В результате поиска на экране индикатора блока 4 появляется либо введенное слово, если оно было найдено, либо слова, обнаруженные схемой 7. Кроме слов, вводится соответствующая справочная информация. 1 з.п. ф-лы, 2 ил.

5

0

5

0 5

0

блока 10 управления, а затем - на установочный вход регистра 5 слова, блока 8 памяти адресов, счетчика 3 адреса и на вход генератора 9 импульсов, блокирующий выдачу импульсов. В таком состоянии устройство ожидает, пока пользователь с помощью блока 4 ввода и отображения не введет в регистр 5 слово, информацию о котором он хочет получить.

Одновременно с запоминанием слова в регистр 5 на вход триггера 34 поступает сигнал, который переводит его в состояние логического нуля. На выходе 12 блока 10 управления появляется сигнал низкого уровня, который снимает блокировку с генератора 9 тактовых импульсов. Тактовые импульсы поступают на вход счетчика 3. На выходе счетчика 3 адреса устанавливается адрес первого слова, записанного в блоке 1, который поступает на один из входов коммутатора 2 и передается на его выход под действием управляющего сигнала низкого уровня, поступающего с выхода 17 блока 10 управления, с выходов коммутатора 2 адрес передается на адресные входы блока 1 памяти слов. После этого на выходах блока 1 появляется первое слово, которое поступает на входы схем 6 и 7 сравнения. На вторые входы этих схем поступает слово из регистра 5.

Пусть, например, схемы 6 и 7 рас- читаны на сравнение слов не больше, чем из восьми букв. Обозначим слово

514958156

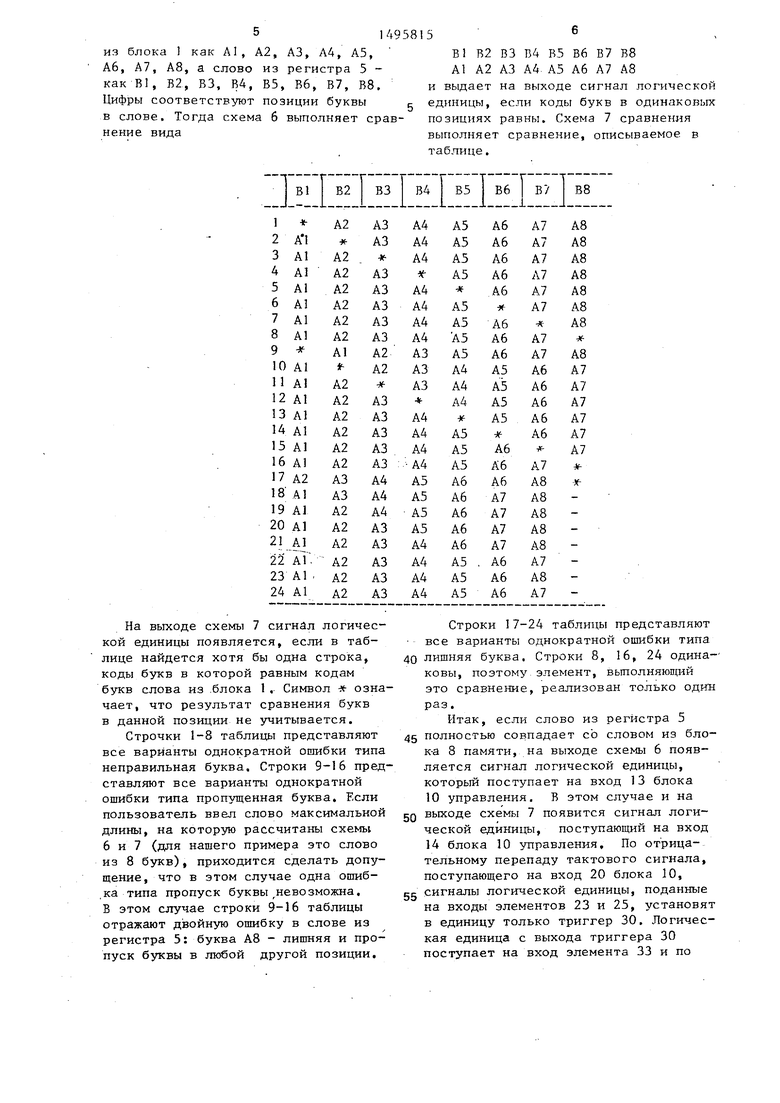

из блока 1 как А1, А2, A3, Л4, А5, В1 В2 ВЗ Б4 В5 Вб В7 В8 А6, А7, А8, а слово из регистра 5 - А1 А2 A3 А4 АЗ Аб А7 А8 как В1, В2, ВЗ, В4, ВЗ, В6, В7, В8, и выдает на выходе сигнал логической Цифры соответствуют позиции буквы единицы, если коды букв в одинаковых в слове. Тогда схема б выполняет срав- позициях равны. Схема 7 сравнения некие видавыполняет сравнение, описываемое в

таблице.

На выходе схемы 7 сигнал логической единицы появляется, если в таблице найдется хотя бы одна строка, коды букв в которой равным кодам букв слова из .блока 1. Символ означает, что результат сравнения букв в данной позиции Не учитывается.

Строчки 1-8 таблицы представляют все варианты однократной ошибки типа неправильная буква. Строки 9-16 представляют все варианты однократной ошибки типа пропущенная буква. Если пользователь ввел слово максимальной длины, на которую рассчитаны схемы 6 и 7 (для нашего примера это слово из 8 букв), приходится сделать допущение, что в этом случае одна ошиб- ,ка типа пропуск буквы невозможна. В этом случае строки 9-16 таблицы отражают двойную ошибку в слове из регистра 5: буква ЛВ - лишняя и пропуск буквы в любой другой позиции.

Строки 17-24 таблицы представляют все варианты однократной ошибки типа

40 лишняя буква. Строки 8, 16, 24 одинаковы, поэтому,элемент, выполняющий это сравнение, реализован только один раз.

Итак, если слово из регистра 3

45 полностью совпадает со словом из бло- к-а 8 памяти, на выходе схемы 6 появляется сигнал логической единицы, который поступает на вход 13 блока 10 управления, В этом случае и на

5Q выходе схемы 7 появится сигнал логической единиц., поступающий на вход 14 блока 10 управления. По отрицательному перепаду тактового сигнала, поступающего на вход 20 блока 10,

gg сигналы логической единицы, поданные на входы элементов 23 и 23, установят в единицу только триггер 30. Логическая единица с выхода триггера 30 поступает на вход элемента 33 и по

входу 1 - на вход блока 4 ввода и отображения. На выходе элемента 33 ( выход 21 блока 10 )появляется логический нуль, который поступает на локирующий вход счетчика 3 адреса. В следующем такте счетчик адреса не изменяется, а информация с выходов ;блока 1 памяти переписывается в блок А ввода и отображения, после чего ;Она отображается на экране индика- ;тора, В конце этого такта, т.е. по отрицательному пепепаду тактового ;сигнала,.триггер 30 устанавливается в состояние логического нуля из-за наличия обратной связи, i Если слово из регистра 5 удовлет- всряет одному из вариантов сравнения, ;Приведенных в таблице, сигнал логи- :ческой единицы появится только на выходе схемы 7 сравнения. По отрицательному перепаду тактового сигнала в состоянии логической единицы будет установлен триггер 26. С выхода триггера 26 сигнал логической едини- ;цы поступает на вход элементов 31 и ;33. На выходе элемента 33 формируется нулевой сигнал, который поступает на выход 21 блока 10 и далее на блокирующий вход счетчика 3 На выходе элемента 31 формируется единичный сигнал, который поступает на выход 16 блока 10 и далее на вход разрешения записи блока 8. По положительному перепаду следукяцего тактирующего сигнала адрес, сформированный в предыдущем такте, записывается в блок 8. При этом блок. 8 установит на входе 18 блока 10 нулевой сигнал, который должен запретить на время своего действия подачу следующего сигнала записи. Однако изменение состояния .триггера 27 в конце такта не произой- дет, так как длительности такта достаточно,, чтобы блок 8 выдал сигнал готовности, т.е. установил единичный сигнал на входе 18 блока 10. В конце .этого такта триггер 26 будет установлен в нулевое состояние из-за наличия обратной связи. Через время, опрделенное параметрами блока 8, на вход 19 блока 10 поступит единичный сигнал, который означает, что разрешено, чтение информации из блока 8. Этот сигнал будет записан в триггер 28 по очередному отрицательному перепаду тактирующего сигнала.

Если на выходе схем.6 и 7 единичный сигнал не появился, очередной

5 0 5 0 с о с

0

5

тактовый импульс, поступая на вход счетчика 3, увеличивает адрес на единицу. Новый адрес поступает через коммутатор 2 на адресные входы блока 1, JI описанный процесс повторяется до тех пор, пока не произойдет или полное заполнение блока 8, или все слова в блоке 1 не будут просмотрены. Полное заполнение блока 8 может произойти, если условиям частич- .ного совпадения (таблица 2) удовлетворяет такое количество слов, что емкости блока 8 не хватает для записи их адресов. В этом случае после записи очередного адреса в последнюю свободную ячейку блок 8 установит на входе 18 блока 10 нулевой сигнал, запрещающий на время своего действия подачу следующих сигналов записи. Этот сигнал не изменится до конца такта и установит триггер 27 в единичное состояние.

С выхода триггера 27 единичный сигнал поступает на входе элементов 31-33, на выход 17 блока 10 и в блок 4 ввода и отображения по входу 11. На выходе элемента 31 формируется нулевой сигнал, который поступает на выход 16 блока 10 и далее на управляющий вход блока 8, запрещая операцию записи. На выходе элемента 32 формируется единичный сигнал, которьш поступает на выход 15 блока 10 И:.далее на другой управляющий вход, разрещая операцию чтения. На выходе элемента 33 устанавливается нулевой сигнал, который блокирует изменение счетчика адреса. Единичный сигнал с выхода 17 поступает на управляющий, вход коммутатора 2 и подключает выходы блока 8 к адресным входам блока 1. По положительному перепаду тактирукщего сигнала адрес, который п-ервым был записан в блок 8, появляется на его выходах и через коммутатор 2 поступает на адресные входы блока 1.

На выходе блока 1 появляется информация, которая передается в блок 4 ввода и отображения, после чего отображается на экране индикатора. На выходе схемы 7 появится единичный сигнал. Так как с выхода триггера 27 единичный Сигнал поступает на инверсный вход элемента 23, то на его вькоде будет нулевой сигнал независимо ..от сигнала со схемы 7. Кроме того, во выдачи адреса блок 8

i14

угтапявливав на входе 19 блока 10 нулепоп сигнал, запрещающий на время своего действия подачу следующего сигнала чтения. Однако, к -концу такт блок 8 выдает единичный сигнал на этот вход и триггер 28 не изменяет свое состояние.

Через время, определяемое параметрами блока 8, он установит нулевой сигнал на входе 18 блока 10, которьш означает, что в блоке 8 имеются свободные ячейки и, следовательно, можно продолжать просмотр блока 1. Этот сигнал установит триггер 27 в нулево состояние по первому же отрицательному перепаду тактирующего сигнала, и просмотр -блока 1 возобновится.

Если все слова в блоке 1 просмотрены, счетчик 3 адреса устанавливае единичнБгй сигнал на входе 22 блока 10, который по отрицательному перепаду тактирующего сигнала устанавливает в единичное состояние триггер 29, а также, пройдя через элемент 24, - триггер 27. После установки триггера 27 в единичное состояние происходят соответствующие изменения на выходах 16, 15, 17и 21 и, если триггер 28 установлен в единичное состояние, начнется процесс передачи в блок 4 ввода и отображения слов из блока 1 , адреса кото.рых записаны в блоке 8. Этот процесс будет продолжаться до тех пор, пока все слова, адреса которых записаны в блоке 8, не будут отображены на экране индика тора. После передачи последнего слова блок 8 установит и будет удерживать на входе 19 блока 10 нулевой

сигнал, который после записи в триггер 28 заблокирует подачу следующих сигналов чтения, а на экране появится сообщение, что поиск окончен и можно вводить следующее слово. Если после просмотра всех слов блока I и установки в единичное состояние триггеров 29 и 27 окажется, что триггер 28 находится в нулевом состоянии, это значит, что в процессе просмотра блока на выходе схемы 7 не появился единичный сигнал. Сообщение об этом появится на экране индикатора, и устройство будет ожидать ввода сле-;- дующего слова в регистр 5.

Формула изобретения

i. Устройство для изучения слов иностранного языка, содержащее блок

Q 5

0 5 О

5

0

5

0

5

памяти слов, счетчик адреса, регистр слова, блок ввода и отображения, генератор импульсов, первую схему сравнения и блок управления, отличающееся тем, что, с целью расширения функциональных возможностей за счет выдачи переведенных значений слов, вводимых с одно- Кратной ошибкой, в него введены ком- мутатор, вторая схема сравнения и блок памяти адресов, причем выход генератора импульсов соединен с тактовым входом блока памяти адресов и счетным входом счетчика адреса, выход которого соединен с первым информационным входом коммутатора и информационным входом блока памяти адресов, информационный выход которого соединен с вторым информационным входом коммутатора, выход которого соединен с адресным входом блока памяти слов, выход первой Группы разрядов которого соединен с первыми входами первой и второй схем сравнения, вторые входы которых соединены с выходом регистра слова, информационный вход которого подключен к выходу блока ввода и отображения, информационный вход которого соедд- нен с выходом второй группы разрядов блока памяти слов, первый вход блока управления соединен с входом запуска устройства, выходы первой и второй схем сравнения соединены соответственно с вторым и третьим входами блока управления, четвертый и пятый входы которого соединены с выходами соответственно готовности записи и чтения блока памяти адресов, выход генератора импульсов соединен с шестым входом блока управления, седьмой вход которого соединен с выходом переполнения счетчика, адреса, первый выход блока управления соединен с входом задания режима блока ввода и отображения, второй выход блока управления соединен с установочными входами регистра слова, счетчика адреса, входом запуска генератора импульсов и установочным входом блока памяти адресов, входы разрешения чтения и разрешения записи которого соединены соответственно с третьим и четвертым выходами блока управления, пятый вход которого соединен с | управляющим входом коммутатора, вход разрешения счета счетчика адреса соединен с шестым выходом блока управления.

Фиг. 2

Составитель А.Зорин

Редактор А.Шандор Техред М.Дидык

Заказ 4268/47 Тираж 668Подписное,

ВНИИПИ Государственного комитета по изобретениям и открытиям при ГКНТ СССР 113035, Москва, Ж-35, Раушская наб., д. 4/5

СМ

Корректор И.Муска

Авторы

Даты

1989-07-23—Публикация

1987-12-28—Подача