Изобретение относится к области вычислительной техники и может быть применено в системах телеобработки и сетях ЭВМ, построенных на базе технических средств Единой системы ЭВМ для обмена информацией меязду абонентами и электронной вычислительной машиной или электронными вычислительными машинами по каналам передачи данных.

Целью изобретения является повышение коэффициента использования оборудования и упрощение устройства за счет сокращения числа связей.

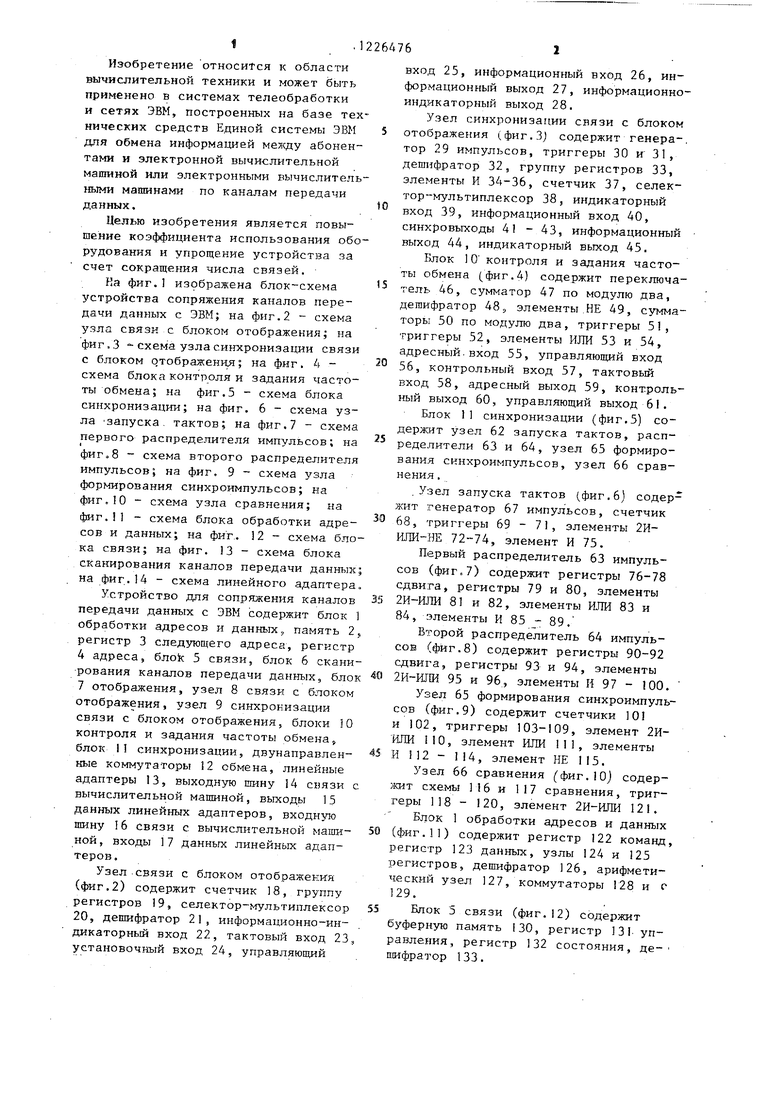

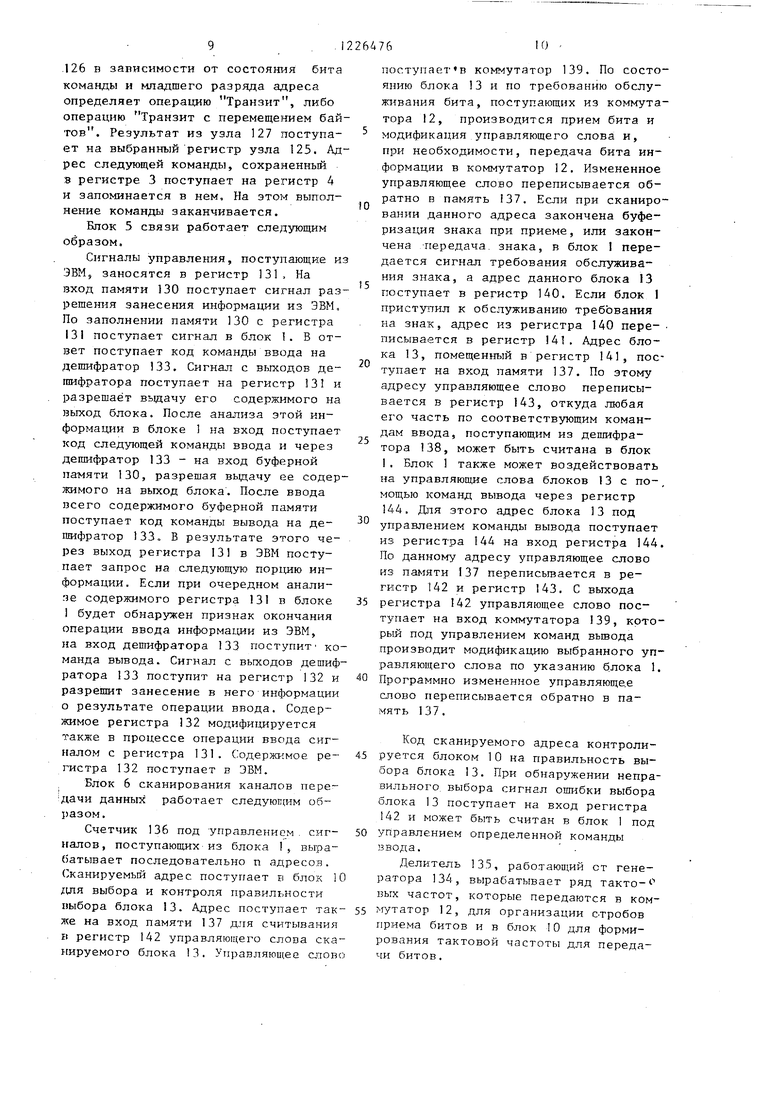

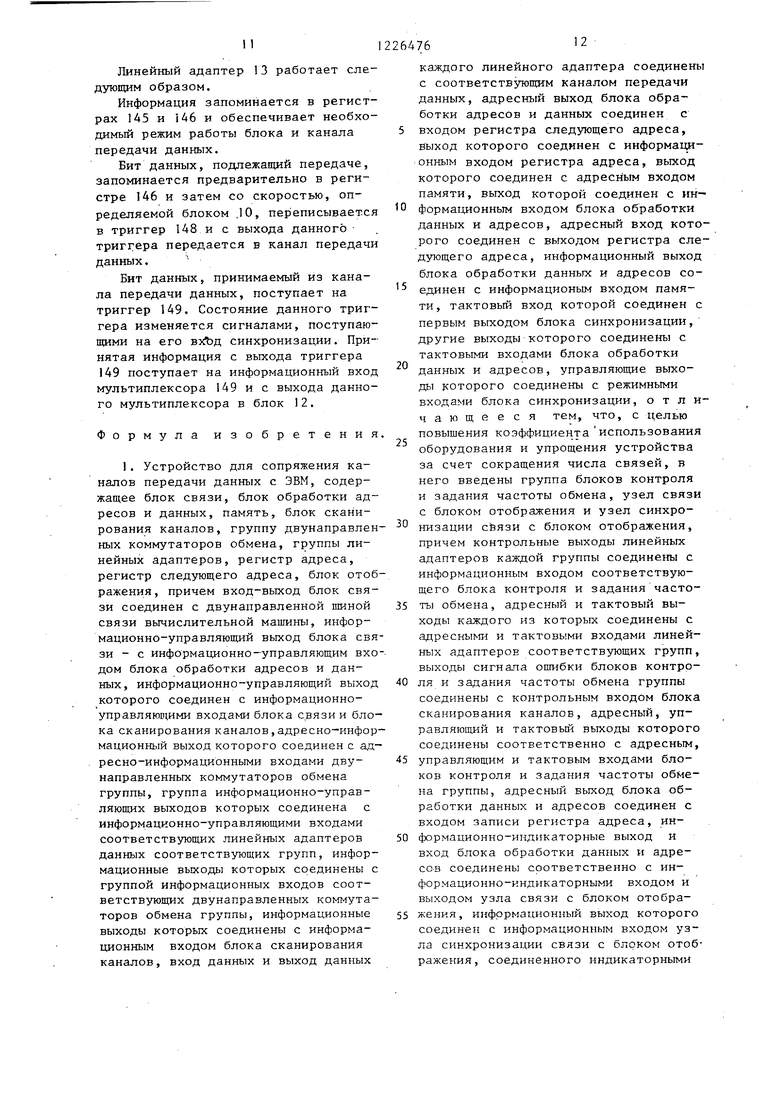

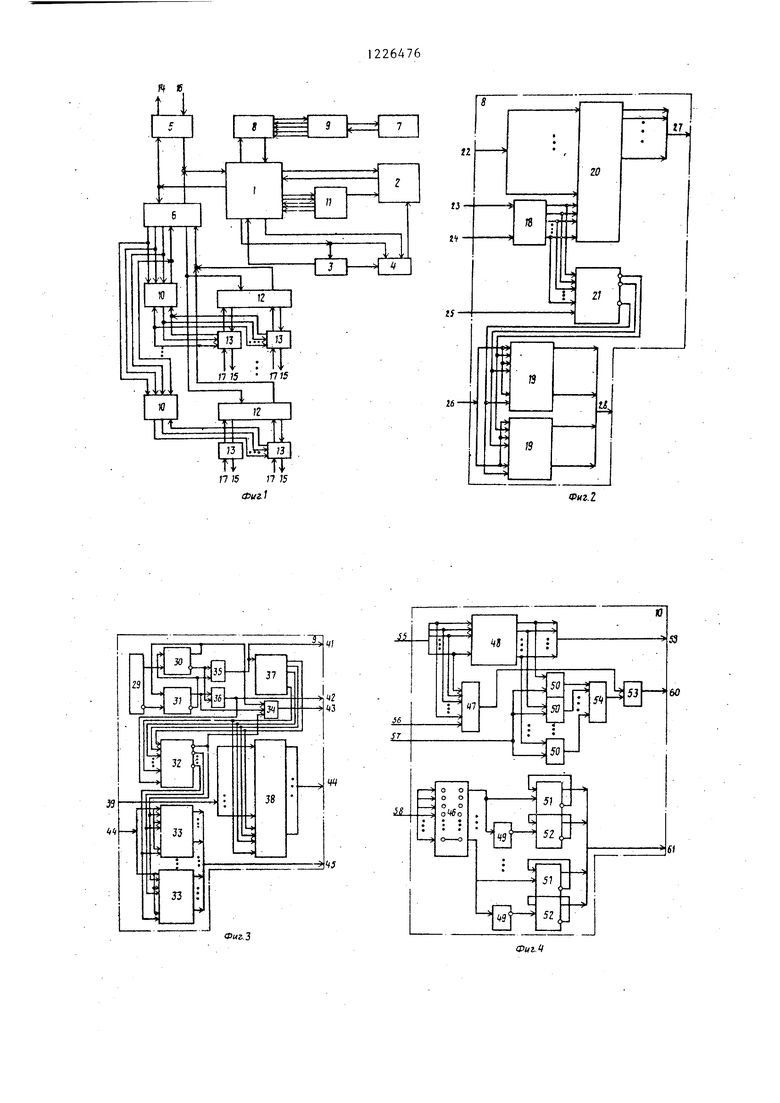

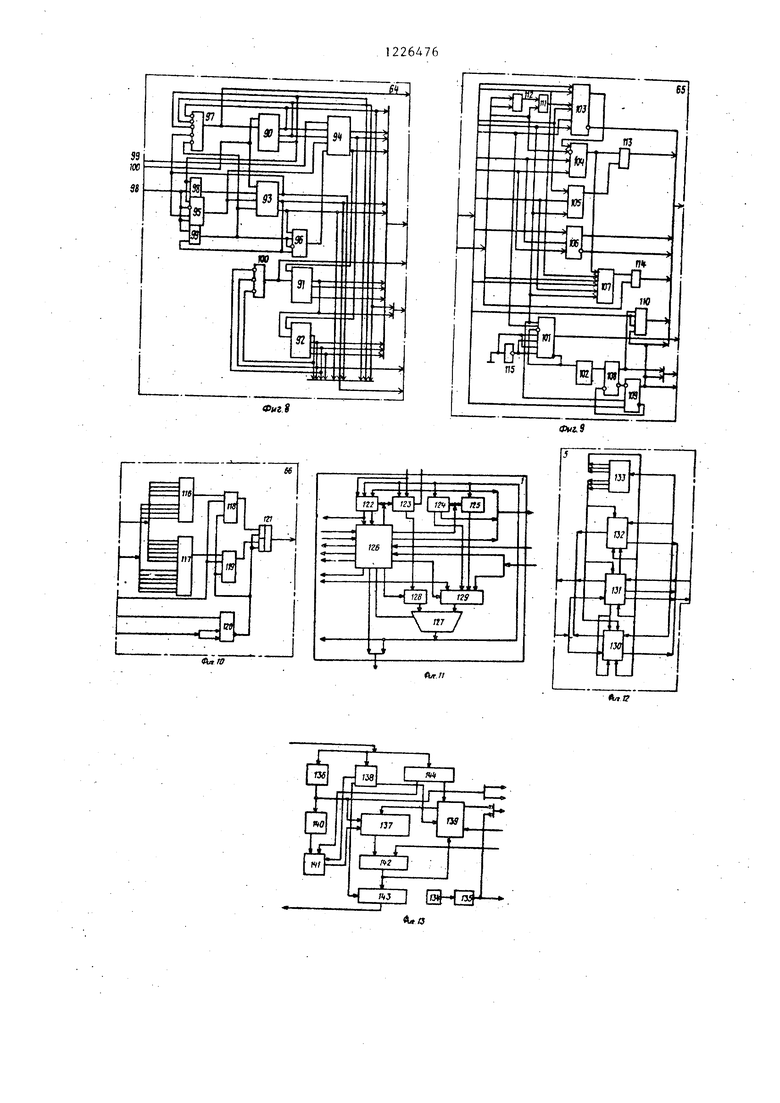

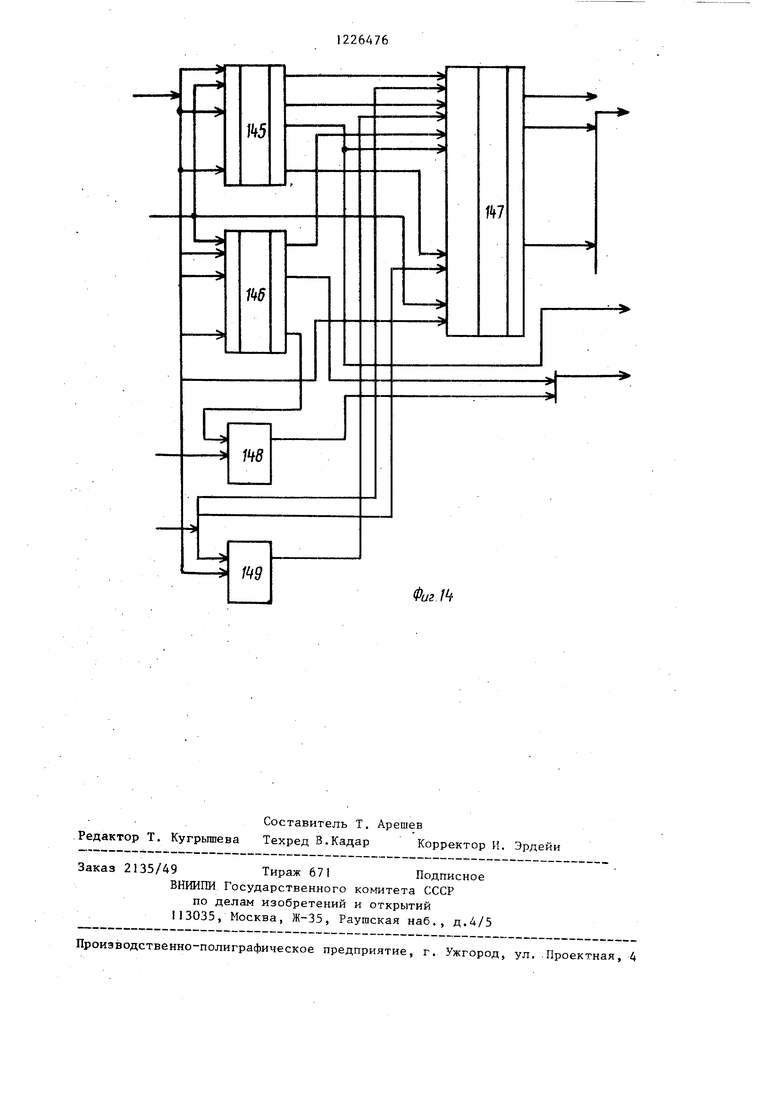

Ка фиг.1 изображена блок-схема устройства сопряжения каналов передачи данных с ЭВМ; на фиг.2 - схема узла связи с блоком отображения; на фиг.З - схема узла синхронизации связи с блоком отображения; на фиг. 4 - схема блока контроля и задания частоты обмена; на фиг.З - схема блока синхронизации; на фиг. 6 - схема узла запуска, тактов; на фиг.7 - схема первого распределителя импульсов; на фиг.8 - схема второго распределителя импульсов; на фиг, 9 - схема узла формирования синхроимпульсов; на фиг.10 - схема узла сравнения; на фиг.1 - схема блока обработки адресов и данных; на фиг.. 2 - схема блока связи; на фиг. 13 - схема блока сканирования каналов передачи данных на фиг.14 - схема линейного адаптера Устройство для сопряжения каналов передачи данных с ЭВМ содержит блок обработки адресов и данных, память 2 . регистр 3 следующего адреса, регистр 4 адреса, блok 5 связи, блок 6 скани рования каналов передачи данных, бло 7 отображения, узел 8 связи с блоком отображения, узел 9 синхронизации связи с блоком отображения 5 блоки 10 контроля и задания частоты обмена блок 11 синхронизации, двунаправлен ные коммутаторы 12 обмена, линейные адаптеры 13, выходную шину 14 связи вычислительной машиной, выходы 15 данных линейных адаптеров, входную шину 16 связи с вычислительной машиной , входы 17 данных линейных адаптеров.

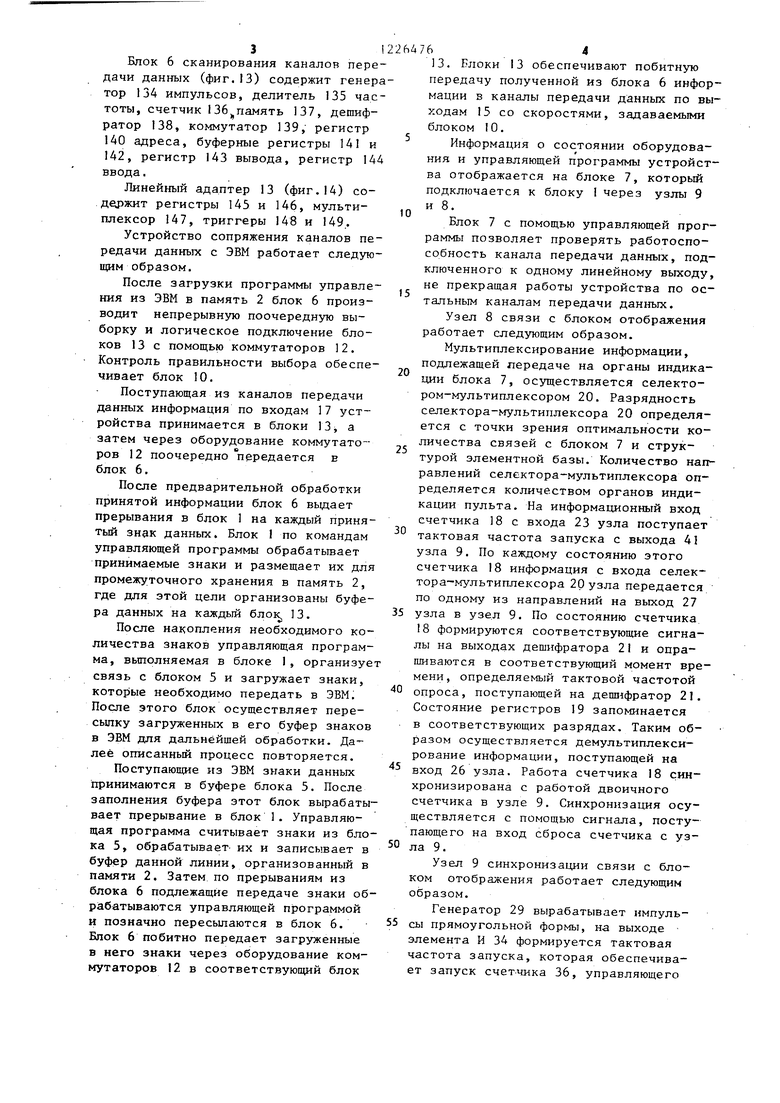

Узел .связи с блоком отображения (фиг.2) содержит счетчик 18, группу регистров 19, селектор-мультиплексор 20, дешифратор 21, информационно-индикаторный вход 22, тактовый вход 23 устано-вочный вход 24, управляющий

;. 1 , - к с ,

10

15

20

25

30

35

40

45

50

55

вход 25, информационный вход 26, информационный выход 27, информационно- индикаторный выход 28.

Узел синхронизации связи с блоком отображения (фиг.З) содержит генера-. тор 29 импульсов, триггеры 30 и 31, дешифратор 32, группу регистров 33, элементы И 34-36, счетчик 37, селектор-мультиплексор 38, индикаторный вход 39, информационный вход 40, синхровыходы 41 - 43, информационный выход 44, индикаторный выход 45.

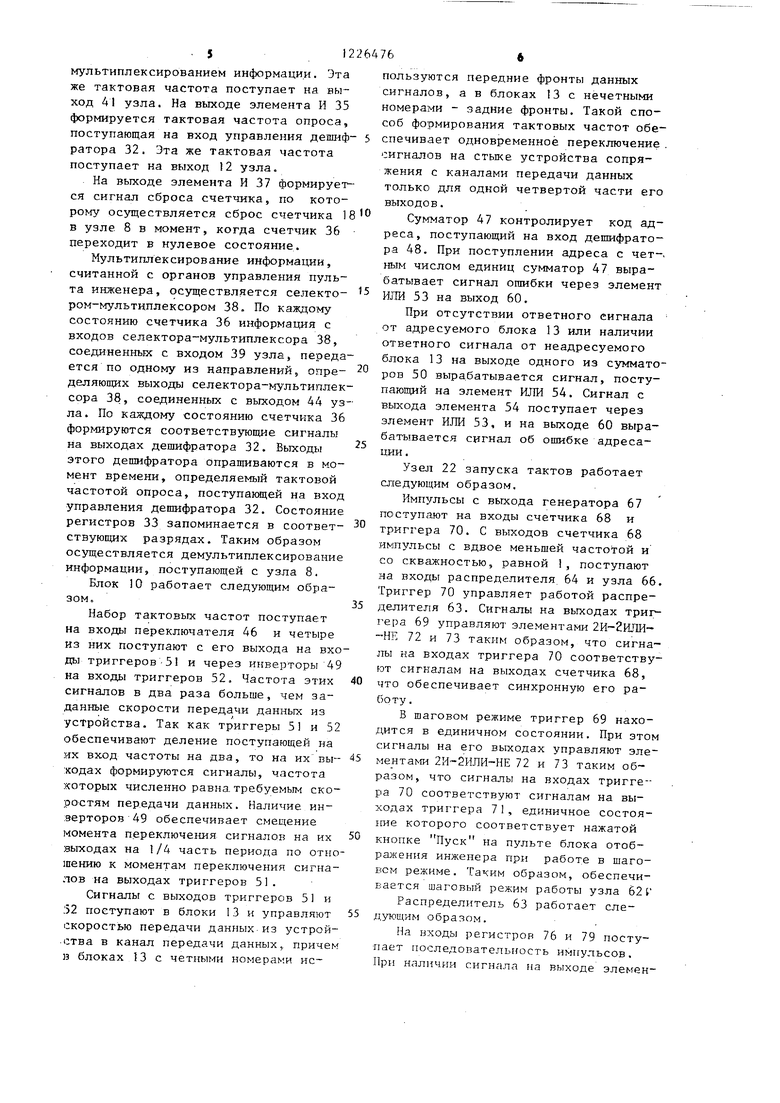

Блок 10 контроля и задания частоты обмена (фиг.4) содержит переключатель 46, сумматор 47 по модулю два, дешифратор 48, элементы .НЕ 49, сумматоры 50 по модулю два, триггеры 51, триггеры 52, элементы ИЛИ 53 и 54, адресный, вход 53, управляюш 1й вход 36, контрольный вход 37, тактовый вход 38, адресный выход 59, контрольный выход 60, управляющий выход 6I.

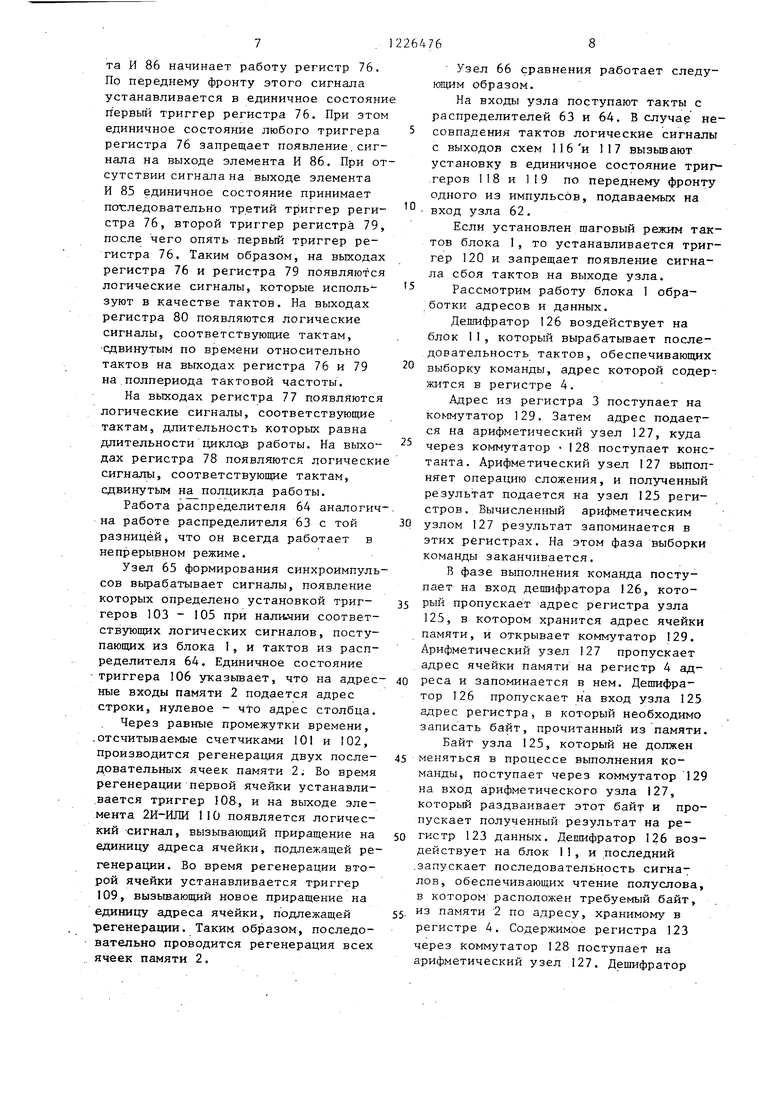

Б.ПОК 11 синхронизации (фиг.З) содержит узел 62 запуска тактов, распределители 63 и 64, узел 63 формирования синхроимпульсов, узел 66 сравнения .

.Узел запуска тактов (фиг.6) содержит генератор 67 импульсов, счетчик 68, триггеры 69 - 71, элементы 2И- ИЛИ-НЕ 12-1k, элемент И 75.

Первый распределитель 63 импульсов () содержит регистры 76-78 сдвига, регистры 79 и 80, элементы 2И-ИЛИ 81 и 82, элементы ИЛИ 83 и 84, элементы И 83 - 89.

Второй распределитель 64 импульсов (фиг.8) содержит регистры 90-92 сдвига, регистры 93 и 94, элементы 2И-ИГЕИ 93 и 96, элементы И 97 - 100.

Узел 63 формирования синхроимпульсов (фиг.9) содержит счетчики 10 и 102, триггеры 103-109, элемент 2И- ИЛИ по, элемент ИЛИ ill, элементы И 112 - 114, элемент НЕ 113.

Узел 66 сравнения фиг.Ю) содержит схемы 1I6 и 117 сравнения, триггеры 118 - 120, элемент 2И-ИЛИ 121.

Блок 1 обработки адресов и данных (фиг.11) содержит регистр 122 команд, регистр 123 данньпс, узлы 124 и 123 регистров, дешифратор 126, арифметический узел 127, коммутаторы 128 и с 129.

Блок 3 связи (фиг.12) содержит буферную память 130, регистр 131- управления,, регистр 132 состояния, де- шифратор 133.

3

Блок 6 сканирования каналов передачи данных (фиг.13) содержит генератор 134 импульсов, делитель 135 частоты, счетчик 1361 память 137, дешифратор 138, коммутатор 139, регистр 140 адреса, буферные регистры 141 и 142, регистр 143 вывода, регистр 144 ввода.

Линейный адаптер 13 (фиг.14) со- де1ржит регистры 145 и 146, мульти- плексор 147, триггеры 148 и 149.

Устройство сопряжения каналов передачи данных с ЭВМ работает следующим образом.

После загрузки программы управления из ЭВМ в память 2 блок 6 производит непрерывную поочередную выборку и логическое подключение блоков 13 с помощью коммутаторов 12. Контроль правильности выбора обеспечивает блок 10.

Поступающая из каналов передачи данных информация по входам 17 устройства принимается в блоки 13, а затем через оборудование коммутато- ров 12 поочередно передается в блок 6.

После предварительной обработки принятой информации блок 6 выдает прерывания в блок 1 на каждый принятый знак данных. Блок 1 по командам управляющей программы обрабатьгоает принимаемые знаки и размещает их для промежуточного хранения в память 2, где для этой цели организованы буфера данных на каждый блок 13.

После накопления необходимого количества знаков управляющая программа, выполняемая в блоке 1, организуе связь с блоком 5 и загружает знаки, которые необходимо передать в ЭВМ. После этого блок осуществляет пересылку загруженных в его буфер знаков в ЭВМ для дальнейшей обработки. Далее описанный процесс повторяется.

Поступающие из ЭВМ знаки данных принимаются в буфере блока 5. После заполнения буфера этот блок вырабатывает прерывание в блок 1. Управляющая программа считывает знаки из блока 5, обрабатывает их и записы.вает в буфер данной линии, организованный в памяти 2. Затем по прерываниям из блока 6 подлежащие передаче знаки обрабатываются управляющей программой и позначно пересылаются в блок 6. Кпок 6 побитно передает загруженные в него знаки через оборудование коммутаторов 12 в соответствующий блок

15

20

64

„

j,

5

30

0

5

0

764

13. Блоки 13 обеспечивают побитную передачу полученной из блока 6 информации в каналы передачи данных по выходам 15 со скоростями, задаваемыми блоком 10.

Информация о состоянии оборудования и управляющей программы устройства отображается на блоке 7, которьй подключается к блоку I через узлы 9 и 8.

Блок 7 с помощью управляющей программы позволяет проверять работоспособность канала передачи данных, подключенного к одному линейному выходу, не прекращая работы устройства по остальным каналам передачи данных.

Узел 8 связи с блоком отображения работает следующим образом.

Мультиплексирование информации, подлежащей передаче на органы индикации блока 7, осуществляется селектором-мультиплексором 20. Разрядность селектора-мультиплексора 20 определяется с точки зрения оптимальности количества связей с блоком 7 и структурой элементной базы. Количество направлений селектора-мультиплексора определяется количеством органов индикации пульта. На информационный вход счетчика 18 с входа 23 узла поступает тактовая частота запуска с выхода 41 узла 9. По каждому состоянию этого счетчика 18 информация с входа селектора-мультиплексора 20 узла передается по одному из направлений на выход 27 узла в узел 9, По состоянию счетчика 18 формируются соответствующие сигналы на выходах дешифратора 2I и опрашиваются в соответствующий момент времени, определяемый тактовой частотой опроса, поступающей на дешифратор 21. Состояние регистров 19 запоминается в соответствующих разрядах. Таким образом осуществляется демультиплексирование информации, поступающей на вход 26 узла. Работа счетчика 18 синхронизирована с работой двоичного счетчика в узле 9. Синхронизация осуществляется с помощью сигнала, поступающего на вход сброса счетчика с узла 9.

Узел 9 синхронизации связи с блоком отображения работает следующим образом.

Генератор 29 вырабатывает импульсы прямоугольной формы, на выходе элемента И 34 формируется тактовая частота запуска, которая обеспечивает запуск счет-чика 36, управляющего

мультиплексированием информации. Эта же тактовая частота поступает на выход 41 узла. На выходе элемента И 35 формируется тактовая частота опроса, поступающая на вход управления дешиф- ратора 32. Эта же тактовая частота поступает на выход 12 узла.

На выходе элемента И 37 формирует ся сигнал сброса счетчика, по которому осуществляется сброс счетчика 18 в узле 8 в момент, когда счетчик 36 переходит в нулевое состояние.

Мультиплексирование информации, считанной с органов управления пульта инженера, осуществляется селекто- ром-мультиплексором 38, По каждо;му состоянию счетчика 36 информация с входов селектора-мультиплексора 38, соединенных с входом 39 узла, передается по одному из направлений, опре- деляющих выходы селектора-мультиплексора 38, соединенных с выходом 44 узла. По каждому состоянию счетчика 36 формируются соответствующие сигналы на выходах дешифратора 32. Выходы этого дешифратора опрапшваются в момент времени, определяемый тактовой частотой опроса, поступакяцей на вход управления дешифратора 32. Состояние регистров 33 запоминается в соответствующих разрядах. Таким образом осуществляется демультиплексирование информации, поступающей с узла 8.

Блок 0 работает следующим образом.

Набор тактовых частот поступает на входы переключателя 46 и четыре из них поступают с его выхода на входы триггеров 51 и через инверторы 49 на входы триггеров 52, Частота этих сигналов в два раза больше, чем заданные скорости передачи данных из устройства. Так как триггеры 51 и 52 обеспечивают деление поступающей на их вход частоты на два, то на их вы ходах формируются сигналы, частота которых численно равна требуемым скоростям передачи данных. Наличие инверторов 49 обеспечивает смещение момента переключения сигналов на их выходах на 1/4 часть периода по отношению к моментам переключения сигналов на выходах триггеров 51.

Сигналы с выходов триггеров 51 и 32 поступают в блоки 13 и управляют скоростью передачи данных из устрой- ства в канал передачи данных, причем в блоках 13 с четными номерами ис

,-

25

5

5 20

264766

пользуются передние фронты данных сигналов, а в блоках 13 с нечетными номерами - задние фронты. Такой способ формирования тактовых частот обеспечивает одновременное переключение . сигналов на стыке устройства сопряжения с каналами передачи данных только для одной четвертой части его выходов.

Сумматор 47 контролирует код адреса, поступающий на вход дешифратора 48. При поступлении адреса с чет-, ным числом единиц сумматор 47 вырабатывает сигнал ошибки через элемент ИЛИ 53 на выход 60.

При отсутствии ответного сигнала от адресуемого блока 13 или наличии ответного сигнала от неадресуемого блока 13 на выходе одного из сумматоров 50 вырабатывается сигнал, поступающий на элемент ИЛИ 54. Сигнал с выхода элемента 54 поступает через элемент ИЛИ 53, и на выходе 60 вырабатывается сигнал об ошибке адресации .

Узел 22 запуска тактов работает следующим образом.

Импульсы с выхода генератора 67 поступ;1ют на входы счетчика 68 и триггера 70. С выходов счетчика 68 импульсы с вдвое меньшей частотой и со сквгшностью, равной , поступают на входы распределителя. 64 и узла 66. Триггер 70 управляет работой распределителя 63. Сигналы на выходах триг гера 69 управляют элементами 2И 2ИЛИ- НЕ 72 и 73 таким образом, что сигналы на входах триггера 70 соответствуют сигналам на выходах счетчика 68, что обеспечивает синхронную его работу .

В шаговом режиме триггер 69 находится в единичном состоянии. При этом сигналы на его выходах управляют элементами 2И-2ИЛИ-НЕ 72 и 73 таким образом, что сигналы на входах триггера 70 соответствуют сигналам на выходах триггера 71, единичное состоя- 1ме которого соответствует нажатой кнопке Пуск на пульте блока отоб- инженера при работе в шаго- всм режиме. Таким образом, обеспечи- Е;ается шаговый режим работы узла 62 f

Распределитель 63 работает следующим образом.

На входы регистров 76 и 79 поступает гюследователыпзсть импульсов. При наличии сигнала па выходе элемен30

35

40

45

50

55

та И 86 начинает работу регистр 76. По переднему фронту этого сигнала устанавливается в единичное состояни первый триггер регистра 76. При этом единичное состояние любого триггера регистра 76 запрещает появление.сигнала на выходе элемента И 86. При отсутствии сигнала на выходе элемента И 85 единичное состояние принимает последовательно третий триггер регистра 76, второй триггер регистра 79, после чего опять первый триггер регистра 76. Таким образом, на выходах регистра 76 и регистра 79 появляются логические сигналы, которые используют в качестве тактов. На выходах регистра 80 появляются логические сигналы, соответствующие тактам, сдвинутым по времени относительно тактов на выходах регистра 76 и 79 на полпериода тактовой частоты.

На выходах регистра 77 появляются логические сигналы, соответствующие тактам, длительность которых равна длительности гщкло13 работы. На выходах регистра 78 появляются логически сигналы, соответствующие тактам, сдвинутым на полцикла работы.

Работа распределителя 64 аналогична работе распределителя 63 с той разницей, что он всегда работает в непрерывном режиме.

Узел 65 формирования синхроимпульсов вырабатывает сигналы, появление которых определено установкой триггеров 103 - 105 при нали.чии соответствующих логических сигналов, поступающих из блока 1, и тактов из распределителя 64. Единичное состояние триггера 106 указьгоает, что на адресные входы памяти 2 подается адрес строки, нулевое - что адрес столбца.

Через равные промежутки времени, .отсчитываемые счетчиками 101 и 102, производится регенерация двух последовательных ячеек памяти 2. Во время регенерации первой ячейки устанавли- .вается триггер 108, и на выходе элемента 2И-ИЛИ ПО появляется логический -сигнал, вызывающий приращение на единицу адреса ячейки, подлежащей регенерации. Во время регенерации второй ячейки устанавливается триггер 109, вызывающий новое приращение на единицу адреса ячейки, подлежащей регенерации. Таким образом, последовательно проводится регенерация всех ячеек памяти 2.

Узел 66 сравнения работает следующим образом.

На входы узла поступают такты с распределителей 63 и 64. В случае не- 5 совпадения тактов логические сигналы с выходов схем 116 и 117 вызьшают установку в единичное состояние триггеров 118 и 119 по переднему фронту одного из импульсов, подаваемых на вход узла 62.

Еслн установлен шаговый режим тактов блока I, то устанавливается триггер 120 и запрещает появление сигнала сбоя тактов на выходе узла. 5 Рассмотрим работу блока 1 обработки адресов и данных.

Дешифратор 126 воздействует на блок 1I, который вырабатывает последовательность тактов, обеспечивающих 0 выборку команды, адрес которой содержится в регистре 4.

Адрес из регистра 3 поступает на коммутатор 129. Затем адрес подается на арифметический узел 127, куда через коммутатор 128 поступает константа. Арифметический узел 127 выполняет операцию сложения, и полученный результат подается на узел 125 регистров. Вычисленный арифметическим 0 узлом 127 результат запоминается в этих регистрах. На этом фаза выборки команды заканчивается.

В фазе выполнения команда поступает на вход дещифратора 126, кото- 5 рый пропускает адрес регистра узла 125, в котором хранится адрес ячейки памяти, и открывает коммутатор 129. Арифметический узел 127 пропускает адрес ячейки памяти на регистр 4 ад- 0 рвса и запоминается в нем. Дешифратор 126 пропускает на вход узла 125 адрес регистра, в который необходимо записать байт, прочитанный из памяти.

Байт узла 125, который не должен 5 меняться в процессе выполнения команды, поступает через коммутатор 129 на вход арифметического узла 127, который раздваивает этот байт и пропускает полученный результат на ре- 0 гистр 123 данных. Дешифратор 126 воздействует на блок 11, и последний .запускает последовательность сигналов, обеспечивающих чтение полуслова, в котором расположен требуемый байт, 5. из памяти 2 по адресу, хранимому в регистре 4. Содержимое регистра 123 через коммутатор 128 поступает на арифметический узел 127. Дешифратор

,126 в зависимости от состояния бита команды и младшего разряда адреса определяет операцию Транзит, либо операцию Транзит с перемещением байтов. Результат из уэла 127 поступает на выбранный регистр узла 125. Адрес следующей команды, сохраненньш S регистре 3 поступает на регистр 4 и запоминается в нем. На этом выполнение команды заканчивается.

Блок 5 связи работает следующим образом.

Сигналы управления, поступающие из ЭВМ, заносятся в регистр 131. На вход памяти 130 поступает сигнал разрешения занесения информации из ЭВМ. По заполнении памяти 130 с регистра 131 поступает сигнал в блок 1. В ответ поступает код команды ввода на дешифратор 133. Сигнал с выходов дешифратора поступает на регистр 131 и разрешает выдачу его содержимого на выход блока. После анализа этой информации в блоке I на вход поступает код следующей команды ввода и через дешифратор 133 - на вход буферной памяти 130, разрешая выдачу ее содержимого на выход блока. После ввода всего содержимого буферной памяти поступает код команды вывода на дешифратор 133. В результате этого через выход регистра 131 в ЭВМ поступает запрос на следующую поргщю информации. Если при очередном анали- гзе содержимого регистра 131 в блоке 1 будет обнаружен признак окончания операции ввода информации из ЭВМ, на вход депшфратора 133 поступит команда вывода. Сигнал с выходов дешифратора 133 поступит на регистр 132 и разрешит занесение в него информации о результате операции ввода. Содержимое регистра 32 модифи Д1руется также в процессе операции ввода сигналом с регистра 131. (юдерж мое регистра 132 поступает в ЭВМ.

Блок 6 сканирования каналов пере- 71ачи данных работает следуюпщм образом.

Счетчик 136 под управлением, сиг- налов, поступающих из блока 1, вьгра- батывает последовательно п адресов. (Сканируемый адрес поступает в блок 1 для выбора и контроля правильности выбора блока 13. Адрес поступает также на вход памяти 137 для считывания в регистр 142 управляющего слова сканируемого блока 13. Управляющее слов

0

5

0

5

0

5

0

5

поступает в коммутатор 139. По состоянию блока 3 и по требованию обслуживания бита, поступающих из коммутатора 12, производится прием бита и модификация управляющего слова и, при необходимости, передача бита информации в коммутатор 12. Измененное управляющее слово переписывается обратно в память 137. Если при сканировании данного адреса закончена буферизация знака при приеме, или закончена -передача, знака, в блок I передается сигнал требования обслуживания знака, а адрес данного блока 13 поступает в регистр 140. Если блок 1 приступил к обслуживанию требования на знак, адрес из регистра 140 пере- писывается в регистр 141. Адрес блока 13, помещенный в регистр 141, поступает на вход памяти 137. По этому адресу управляющее слово переписывается в регистр 143, откуда любая его часть по соответствующим командам ввода, поступающим из дешифратора 138, может быть считана в блок 1 . Блок 1 также может воздействовать на управляющие слова блоков I3 с по-, мощью команд вывода че.рез регистр 144. Для .этого адрес блока 13 под управлением команды вывода поступает из регистра 144 на вход регистра 144. По данному адресу управляющее слово из памяти 137 переписьшается в регистр 142 и регистр 143. С вьпсода регистра 142 управляющее слово поступает на вход коммутатора 139, который под управлением команд вьшода производит модификацию выбранного управляющего слова по указанию блока 1. Программно измененное управляющее слово переписывается обратно в память 137.

Код сканируемого адреса контролируется блоком 10 на правильность выбора блока 13. При обнаружении неправильного, выбора сигнал ошибки выбора блока 13 поступает на вход регистра 142 и может быть считан в блок 1 под управлением определенной команды ввода.

Делитехгь 135, работающий от генератора 134, вырабатывает ряд тaктo- вых частот, которые передаются в ком- гутатор 12, для организации с-тробов приема битов и в блок IО для формирования тактовой частоты для передачи битов.

Линейный адаптер 13 работает следующим образом.

Информация запоминается в регистрах 145 и 146 и обеспечивает необхо- димьш режим работы блока и канала передачи данных.

Бит данных, подлежащий передаче, запоминается предварительно в регистре 146 и затем со скоростью, определяемой блоком ,10, переписывается в триггер 148 и с выхода данного триггера передается в канал передачи данных.

Бит данных, принимаемый из канала передачи данных, поступает на триггер 149. Состояние данного триггера изменяется сигналами, поступающими на его синхронизации. Принятая информация с выхода триггера 149 поступает на информационный вход мультиплексора 149 и с выхода данного мультиплексора в блок 12.

Формула изобретения

1. Устройство для сопряжения каналов передачи данных с ЭВМ, содержащее блок связи, блок обработки адресов и данных, память, блок сканирования каналов, группу двунаправленных коммутаторов обмена, группы линейных адаптеров, регистр адреса, регистр следующего адреса, блок отображения , причем вход-выход блок связи соединен с двунаправленной шиной связи вычислительной машины, инфор- мационно-управляюш 1Й выход блока связи - с информационно-управляющим входом блока обработки адресов и данных, информационно-управляющий выход которого соединен с информационно- управляющими входами блока связи и блока сканирования каналов,адресно-информационный выход которого соединен с адресно-информационными входами двунаправленных коммутаторов обмена группы, группа информационно-управляющих выходов которых соединена с информационно-управляющими входами соответствующих линейных адаптеров данных соответствующих групп, информационные выходы которых соединены с группой информационных входов соответствующих двунаправленных коммутаторов обмена группы, информационные выходы которых соединены с информационным входом блока сканирования каналов, вход данных и выход данных

0

5

каждого линейного адаптера соединены с соответствующим каналом передачи данных, адресный выход блока обработки адресов и данных соединен с 5 входом регистра следующего адреса, быход которого соединен с информационным входом регистра адреса, выход которого соединен с адресным входом памяти, выход которой соединен с ин-

0 формационным входом блока обработки данных и адресов, адресный вход которого соединен с выходом регистра следующего адреса, информационный выход блока обработки данных и адресов со единен с информационым входом памяти, тактовый вход которой соединен с первым выходом блока синхронизации, другие выходы которого соединены с тактовыми входами блока обработки данных и адресов, управляющие выходы которого соединены с режимными входами блока синхронизации, отличающееся тем, что, с целью повышения коэффициента использования оборудования и упрощения устройства за счет сокращения числа связей, в него введены группа блоков контроля и задания частоты обмена, узел связи с блоком отображения и узел синхро низации сйязи с блоком отображения, причем контрольные выходы линейных адаптеров каждой группы соединены с информационным входом соответствующего блока контроля и задания часто5 ты обмена, адресный и тактовый выходы каждого из которых соединены с aдpecны ш и тактовыми входами линейных адаптеров соответствующих групп, выходы сигнала ошибки блоков контрр0 ля и задания частоты обмена группы соединены с контрольным входом блока сканирования каналов, адресный, управляющий и тактовый выходы которого соединены соответственно с адресным,

5 управляющим и тактовым входами блоков контроля и задания частоты обмена группы, адресный выход блока обработки данных и адресов соединен с входом записи регистра адреса, ин0 формационно-индикаторные выход и вход блока обработки данных и адресов соединены соответственно с информационно-индикаторными входом и выходом узла связи с блоком отображенкя, информационный выход которого соединен с информационным входом узла синхронизации связи с блоком отображения, соединенного индикаторными

13

выходом и входом соответственно с входом и выходом блока отображения, первый, второй и третий синхровыходы и информационный выход узла синхронизации связи с блоком отображения соединены соответственно с установочным, тактовым, управляющим и информационным входами узла связи с блоком отображения.,

2, Устройство по п,1, о т л и - чающееся тем, что каждый блок контроля и задания частоты обмена содержит,переключатель, дешифратор, сумматор по модулю два, группу суъп- а- торов по модулкр два, две группы триггеров, два элемента ИЛИ, причем входы дешифратора и группа входов сумматоров по модулю два соединены с адресным входом блока, управляющий вход которого через соединенные последовательно сумматор по модулю два и -первьш элемент ИЛИ соединен с выходом сигнала ошибки блока, тактовый вход которого через переключатель соединен с синхровходами триггеров первой группы и входами элементов НЕ группы, выходы которых соединены с синхровходами соответствующих триггеров второй группы, нулевые выходы триггеров первой и второй групп соединены со своими информационными входами, единичные выходы триггеров обеих групп соединены с тактовым выходом блока, адресный выход которого соединен с выходами дешифратора и первыми входами сумматора по модулю два группы, выходы которых через второй элемент ИЛИ соединены с входом первого элемента ИЛИ, информационный вход блока соеди- нен с вторыми входами сумматоров по модулю два группы.

3. Устройство по П.1, отличающееся тем, что узел связи с блоком отображения содержит счетчик, дешифратор, селектор-мультиплексор и группу регистров, причем информа- 1Ц1бинр индикаторный вход узла соединен с информационной группой входов селектора-мультиплексора, выходы которого соединены с информационным

10

5

20

.1226476ВЫХОДОМ узла, тактовый и установоч- ный входы которого соединены соответственно с информационным и установочным входами .счетчика, выходы которого соединены с управляющей группой входов селектора-мультиплексора и через дешифратор, с соответствующими входами группы регистров, выходы которых соединены с информационно-индикаторным выходом узла, управляющий и информационный входы которого соединены соответственно -с управляющим входом дешифратора и соответств тощими входами группы регистров.

4. Устройство по п.I, о -Т л и ч а- ю щ е е с я тем, что узел синхронизации связи с блоком отображения содер- ясит генератор импульсов, селектор- мультиплексор, группу регистров, счетчик, дешифратор, два триггера, три элемента И, причем прямо.й и инверсный выходы генератора импульсов соединены с синхровходами соответственно первого и второго триггеров, прямой выход первого триггера соединен с первым входом первого элемента И и информационным -входом второго триггера, инверсный выход которого соединен с входом второго элемента И и информационным входом первого триггера, инверсный выход которого соединен с входом третьего элемента И и через второй элемент И с вторым синхровы- ходом узла и входом счетчика, выходы которого соединены с первой груп-. пой входов селектора-мультиплексора и через дешифратор с вторым входом первого элемента И и соответствующими входами группы регистров, выхо.- ды которых соединены с индикаторным выходом узла, индикаторный вход которого через селектор-мультиплексор соединен с информационным выходом узла, информационный вход которого соединен с соответствующими входами группы регистров, прямой выход второго триггера через соответственно пер-, вый и третий элементы И соединен.с первым и третьим. синхровыходами 50 узла.

25

30

35

40

45

вг

S7

тг

73

V

6Э

041.7

fatn

Лт.//

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для подключения устройств ввода-вывода к многосегментной магистрали | 1987 |

|

SU1564638A2 |

| Устройство для сопряжения электронно-вычислительной машины с группой внешних устройств | 1989 |

|

SU1734098A1 |

| Система ввода телевизионных изображений в ЭВМ | 1989 |

|

SU1665391A1 |

| Устройство для контроля и диагностирования цифровых узлов | 1989 |

|

SU1755207A1 |

| Устройство для сопряжения ЭВМ с каналами связи | 1985 |

|

SU1288706A1 |

| Устройство связи для вычислительной системы | 1984 |

|

SU1164722A1 |

| Устройство связи для вычислительной системы | 1982 |

|

SU1042008A1 |

| Станция локальной сети | 1987 |

|

SU1478221A1 |

| Устройство для подключения устройств ввода-вывода к многосегментной магистрали | 1985 |

|

SU1272336A2 |

| Устройство для сопряжения ЭВМ с внешними устройствами | 1987 |

|

SU1501077A1 |

Изобретение относится к вычислительной технике и может быть применено в системах телеобработки и сетях ЭВМ, построенных на базе технических средств Единой Системы (ЕС) ЭВМ для обмена информацией между абонентами и ЭВМ или электронными вычислительными машинами по каналам передачи данных. Цель изобретения - повышение коэффициента использования оборудования и упрощение устройства за счет сокрап1ения числа связей. Это достигается за счет введения в устройство группы блоков контроля и задания частоты обмена, узла связи с блоком отображения и узла синхронизации связи с блоком отображения с соответствующими функциональными связями между ними и известными блоками устройства. 3 з.п. ф-лы, 14 ил. (Л N9 О) Од

Фиг 1

| Устройство для сопряжения | 1980 |

|

SU926645A2 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Патент США № 3735357, кл | |||

| Способ отопления гретым воздухом | 1922 |

|

SU340A1 |

Авторы

Даты

1986-04-23—Публикация

1985-01-09—Подача