Предлагаемое изобретение относится к автоматике и вычислительной технике, в частности к устройствам для обучения, и может быть использовано для автоматизации процесса обучения иностранному языку.

Известна машина для обучения простым словам некоторых европейских языков (заявка Японии № 58-13942), содержащая связанные соответствующим образом устройство ввода, запоминающее устройство, блок формирования адреса, узел считывания, схему совпадения, устройство индикации.

Недостатком данного устройства является низкая надежность, сложность блока формирования адреса, а также малая эффективность, поскольку устройство пригодно для изучения ограниченного набора наиболее простых слов.

Известно также устройство для обучения языку (заявка Великобритании № 2137398), содержащее связанные соответствующим образом клавиатуру, устройство индикации, формирователь, микропроцессор, устройство памяти, выходной блок и синтезатор звукового сигнала.

Недостатком данного устройства является ограниченность области применения, связанная с его принципиальной непригодностью для изучения глаголов, наречий, местоимений, а также большинства существительных, прилагательных и числительных,

Наиболее близким по технической сущности и достигаемому эффекту к изобретению является электронное устройста для изучения морфологии иностранного языка (авт.св. № 1417025), содержащее блок ввода, регистр, счетчик, запоминающий блок, элементы И, бпок индикации, четыре элемента ИЛИ, схему совпадения, схему сравнения, одновибратор, триггер, селектор, генератор тактовых импульсов, двухвходовый регистр и сумматор, причем .первый выход блока

VI

ш

ел

ввода связан с первыми входами первого и второго элементов ИЛИ, двухвходового регистра, триггера, блока индикации и счетчика, второй выход блока ввода соединен с первым входом регистра, выход которого подключен к входу схемы сравнения, первому входу селектора и к соответствующим входам схемы совпадения, а выход последней через первый вход первого элемента И связан со вторым выходом триггера, при этом выход триггера присоединен к первым входам третьего элемента ИЛИ, второго элемента И и к второму входу селектора, выход которого подключен к второму входу блока индикации, причем первый вход схемы сравнения через второй вход третьего элемента ИЛИ и прямой вход третьего элемента И подключен к входу генератора Тактовых импульсов, выход которого присоединен ко вторым входам второго элемента ИЛИ, счетчика и второго элемента И, а выход второго элемента И через первый вход четвертого элемента ИЛИ связан с третьим входом блока индикации, при этом второй выход схемы сравнения через одно- вибратор соединен со вторыми входами первого элемента И и первого элемента ИЛИ, выход которого подключен к второму входу регистра, а выход одновибратора присоединён к третьему входу счетчика, второму входу четвертого элемента ИЛИ и к третьему входу второго элемента ИЛИ, связанного выходом с вторым входом двухвходового регистра, причем третий вход двухвходового регистра связан с выходом сумматора, а выход - с первым входом сумматора и через четвертый вход счетчика с входом запоминающего блока, при этом соответствующие выходы запоминающего блока связаны с третьим входом селектора, вторым входом сумматора, четвертым входом двухвходового регистра, с инверсным входом третьего элемента И и вторым входом схемы сравнения.

Основным недостатком прототипа являются низкие дидактические возможности, имеющие место вследствие недостаточной информационной емкости, которая определяется необходимостью хранения в запоминающем устройстве большого количества информации чисто служебного характера.

Целью изобретения является повышение дидактических возможностей устройства.

Для достижения поставленной цели в устройстве для изучения языка, содержащем блок памяти, первый блок совпадения, блок сравнения, счетчик, выходы которого соединены с адресными входами блока Памяти, первый и второй регистры и сумматор, информационные входы первой группы которого соединены с выходами первого регистра, новым является то, что введены два

коммутатора, второй блок совпадения, два блока регистров, блок управления, третий регистр и дешифратор, входы которого соединены с информационными входами первой группы блока сравнения и с выходами

0 первой группы первого блока регистров, являющимися информационными выходами устройства, выходы дешифратора соединены соответственно с первым и вторым ин- формционными входами блока управления,

5 третий информационный вход которого является входом запуска устройства, а тактовый вход соединен с управляющими входами первого и второго блоков регистров, первого, второго и третьего регистров

0 и счетчика и является синхронизирующим взодом устройства, первой группой информационных входов которого являются соответствующие входы второго регистра, вход записи которого соединен с первым выхо5 дом блока управления, а выходы соединены с информационными входами второго блока регистров, входы сдвига и записи которого соединены соответственно с вторым и третьим выходами блока управления, а вы0 ходы подключены к информационным входам второй группы блока сравнения, выходы которого соединены с четвертым и пятым информационными входами блока управления, четвертый и пятый выходы ко5 торого являются синхронизирующими выходами устройства, а шестой информационный вход соединен с выходом первого блока совпадения, информационные входы первой группы которого соедине0 ны с информационными входами первой группы первого коммутатора, информационными входами первого регистра, информационными входами первой группы второго блока совпадения и выходами счет5 чика, а информационные входы второй группы соединены с информационными входами второй группы сумматора и выходами третьего регистра, вход записи которого соединен с шестым выходом блока

0 управления, а входы соединены с выходами первого коммутатора, информационные входы второй группы которого являются второй группой нформационных входов устройства, а управляющий вход соединен с

5 седьмым выходом блока управления, седьмой информационный вход которого соединены с выходом второго блока совпадения, информационные входы второй группы которого соединены с выходами первого регистра, выходы сумматора соединены с

информационными входами первой группы второго коммутатора, информационные входы второй группы которого соединены с выходами второй группы первого блока регистров, вход записи которого соединен с восьмым выходом блока управления, девятый и десятый выходы которого соединены соответственносустановочным и записывающим входами первого регистра, а одиннадцатый выход соединен с управляющим входом второго коммутатора, выходы которого соединены с информационными входами счетчика, суммирующий, вычитающий и записывающий входы которого соединены соответственно с двенадцатым, тринадцатым и четырнадцатым выходами блока управления.

Известно использование счетчика в электронном словаре с клавишей автостопа (пат. Ms 4438505 США). Однако применяемый в известном устройстве счетчик используется для подсчета числа букв во вводимом словаре, тогда как в заявляемом устройстве счетчик используется для формирования адреса. Различны и алгоритмы поиска информации в заявляемом и известном устройствах.

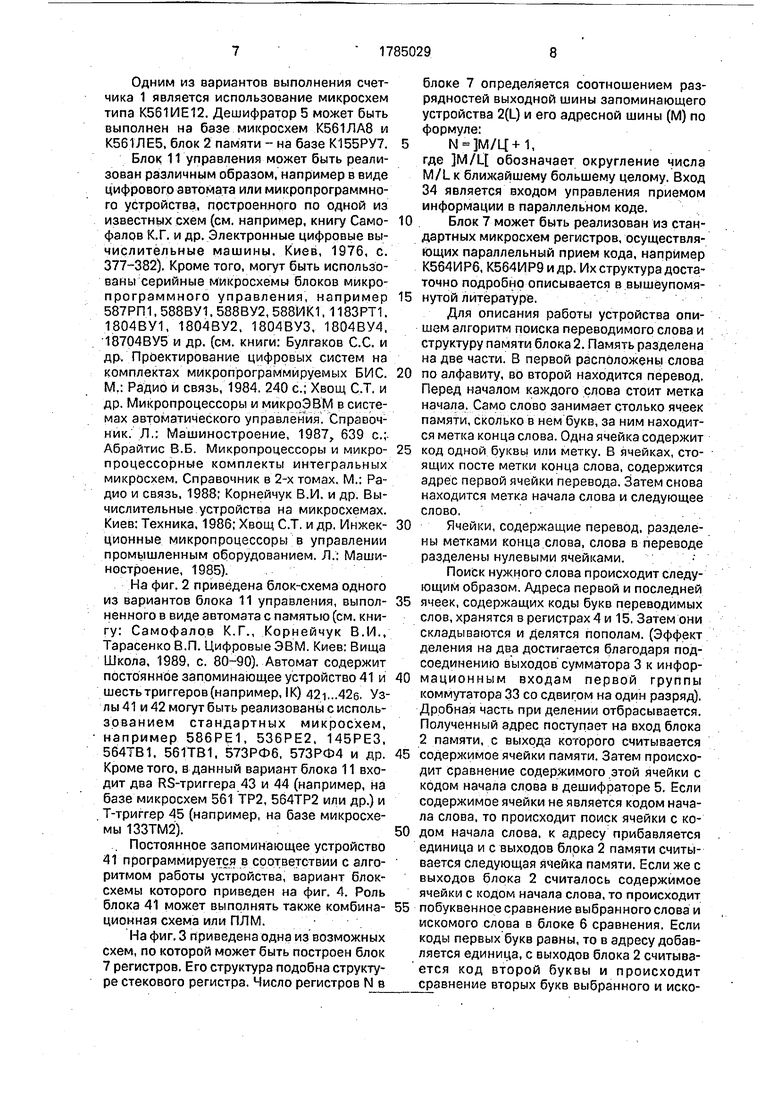

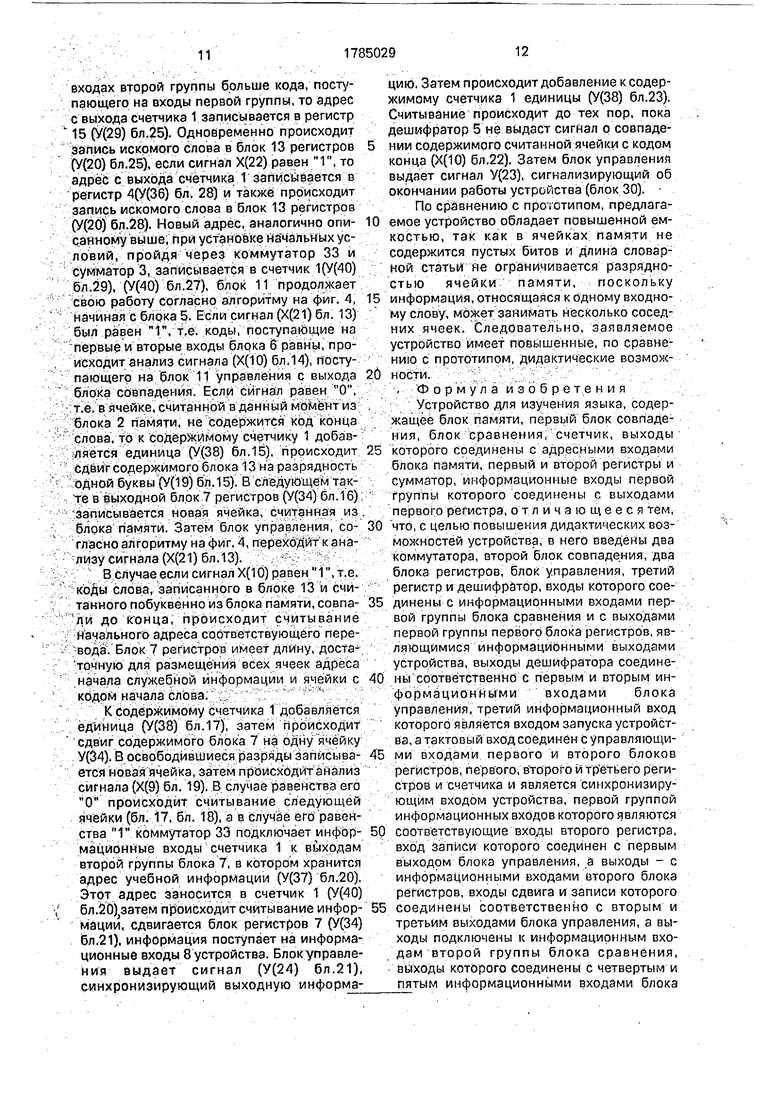

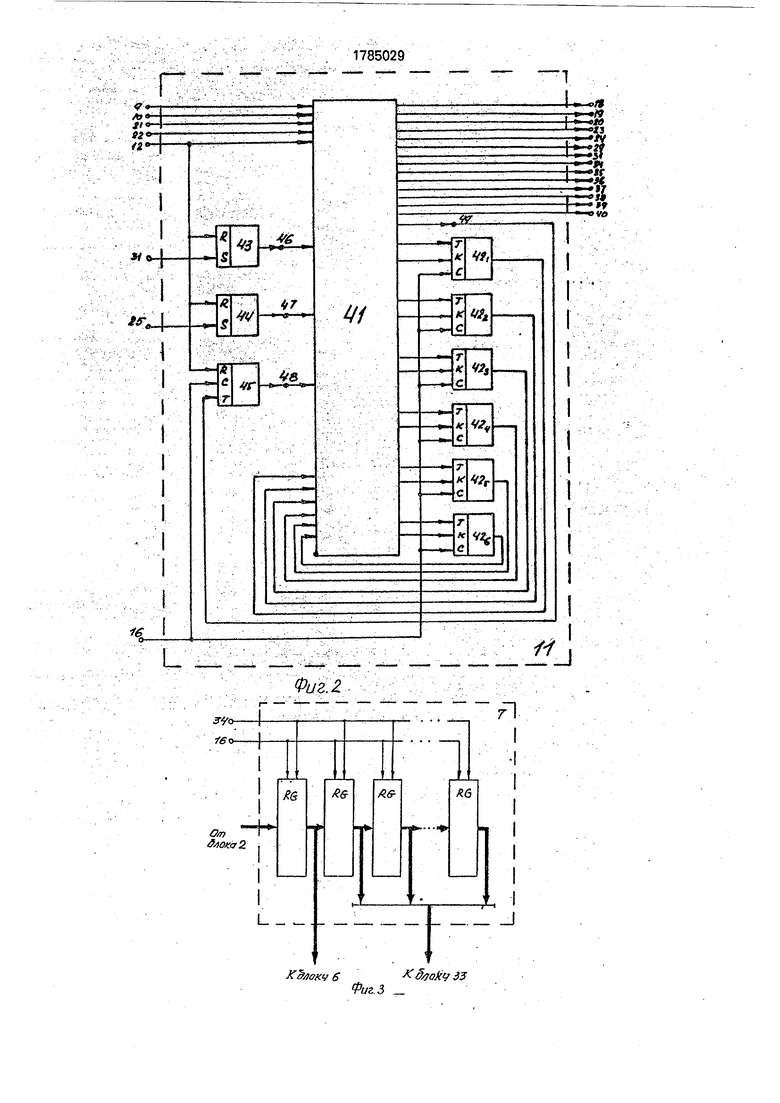

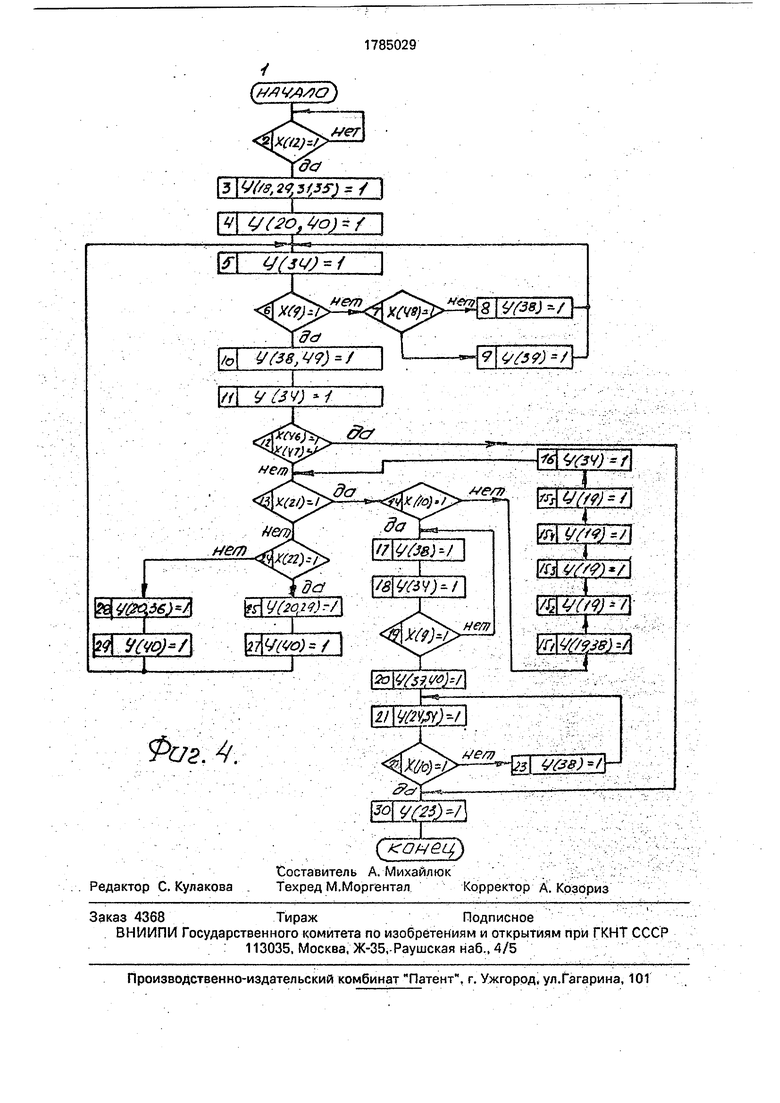

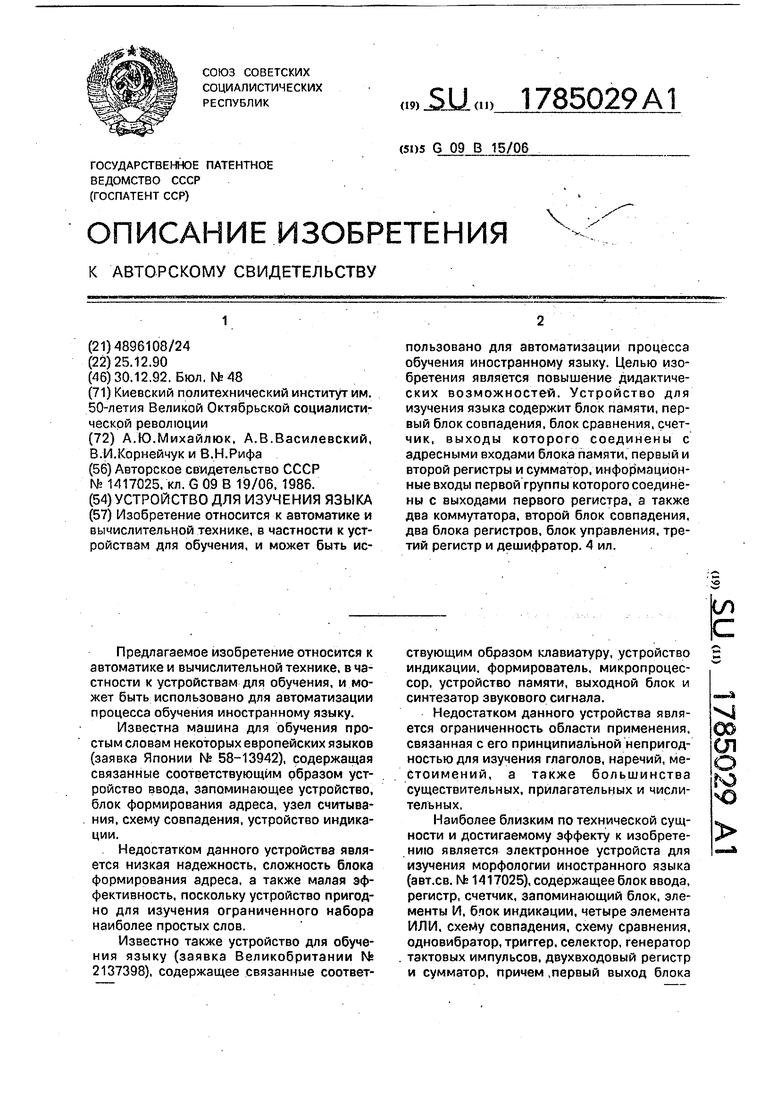

На фиг. 1 представлена блок-схема предлагаемого устройства; на фиг. 2 - блок управления (вариант блок-схемы); на фиг 3

-блок регистров (вариант схемы); на фиг, 4

-алгоритм работы устройства

Устройство для изучения языка (фиг. 1) содержит счетчик 1, выходы которого соединен с адресным входом блока 2 памяти, сумматор 3, информационные входы первой группы которого связаны с выходами первого регистра 4, дешифратор 5, входы которого соединены с информационными входами первой группы блока 6 сравнения и с выходами первой группы первого блока 7 регистров, являющимися информационными выходами 8 устройства, выходы 9 и 10 дешифратора 5 соединены соответственна с первым и вторым информационными входами блока 11 управления, третий информационный вход которого является входом 12 запуска устройства, а тактовый вход соединен с управляющими входами первого 7 и второго 13 блоков регистров, первого 4, второго 14 и третьего 15 регистров и счетчика 1 и является синхронизирующим входом 16 устройства, первой группой информационных входов которого являются соответствующие входы 17 второго регистра 14, вход записи 18 которого соединен с первым выходом блока 11 управления, а выходы соединены с информационными входами второго блока 13 регистров, входы сдвига 19 и записи 20 которого соединены соответственно со вторым и третьим выходами блока 11, а выходы подключены к информационным входам второй группы блока б, выходы 21 и 22 которого соединены с четвертым и 5 пятым информационными входами блока 11, четвертый 23 и пятый 24 выходы которого являются синхронизирующими выходами устройства, а шестой информационный вход соединен с выходом 25 первого блока

0 26 совпадения, информационные входы первой группы которого соединены с информационными входами первой группы первого коммутатора 27, информационными входами первого регистра 4, информаци5 онными входами первой группы второго блока 28 совпадения и выходами счетчика 1, а информационные входы второй группы соединены с информационными входами второй группы сумматора 3 и выходами

0 третьего регистра 15, вход записи 29 которого соединен с шестым выходом блока 11, а входы соединены с выходами первого коммутатора 27, информационные входы второй группы которого являются второй

5 группой информационных входов 30 устройства, а управляющий вход 31 соединен с седьмым выходом блока 11, седьмой информационный вход которого соединен с выходом 32 второго блока 28, информационные

0 входы второй группы которого соединены с выходами первого регистра 4, выходы сумматора 3 соединены с информационными входами первой группы второго коммутатора 33, информационные входы второй груп5 пы которого соединены с выхода второй группы первого блока регистров 7, вход 34 записи которого соединен с восьмым выходом блока 11 управления, девятый и десятый выходы которого соединены

0 соответственно с установочным 35 и записывающим 36 входами первого регистра 4, а одиннадцатый выход соединен с управляющим входом 37 второго коммутатора 33, выходы которого соединены с информаци5 онными входами счетчика 1, суммирующий 38, вычитающий 39 и записывающий 40 входы которого соединены соответственно с двенадцатым, тринадцатым и четырнадцатым выходами блока 11.

0 Заявляемое устройство для изучения языка может быть реализовано с использованием серийно выпускаемых микросхем различных серий. Например, для реализации узлов 4, 13,14,15 могут быть задейство5 ваны микросхемы 561ИР9, для реализации коммутаторов 27 и 33 - микросхемы 561КП1, для реализации блока б сравнения и блоков 26 и 28 совпадения - микросхемы 561ИП2. Сумматор 3 может быть выполнен на базе микросхем 561ИМ1.

Одним из вариантов выполнения счетчика 1 является использование микросхем типа К561ИЕ12. Дешифратор 5 может быть выполнен на базе микросхем К561ЛА8 и К561ЛЕ5, блок 2 памяти - на базе К155РУ7.

Блок 11 управления может быть реализован различным образом, например в виде цифрового автомата или микропрограммного устройства, построенного по одной из известных схем (см. например, книгу Самофалов К.Г. и др. Электронные цифровые вычислительные машины. Киев, 1976, с. 377-382). Кроме того, могут быть использованы серийные микросхемы блоков микропрограммного управления, например 587РП1,588ВУ1.588ВУ2,588ИК1,1183РТ1. 1804ВУ1, 1804ВУ2. 1804ВУЗ, 1804ВУ4. 18704ВУ5 и др. (см. книги: Булгаков С.С. и др. Проектирование цифровых систем на комплектах микропрограммируемых БИС. М.: Радио и связь, 1984. 240 с.; Хвощ С.Т. и др. Микропроцессоры и микроЭВМ в системах автоматического управления. Справочник. Л.: Машиностроение, 1987,, 639 с.; Абрайтис В.Б. Микропроцессоры и микропроцессорные комплекты интегральных микросхем. Справочник в 2-х томах. М.: Радио и связь, 1988; Корнейчук В.И. и др. Вычислительные устройства на микросхемах. Киев: Техника. 1986; Хвощ С.Т. и др. Инжек- ционные микропроцессоры в управлении промышленным оборудованием. Л.: Машиностроение, 1985).

На фиг. 2 приведена блок-схема одного из вариантов блока 11 управления, выполненного в виде автомата с памятью (см. книгу: Самофалов К.Г., Корнейчук В.И., Тарасенко В.П. Цифровые ЭВМ. Киев: Вища Школа, 1989, с. 80-90). Автомат содержит постоянное запоминающее устройство 41 и шесть триггеров (например, IК) 42i,..42e. Узлы 41 и 42 могут быть реализованы с исполь- зованием стандартных микросхем, например 586РЕ1, 536РЕ2. 145РЕЗ. 5647В1, 561ТВ1, 573РФ6, 573РФ4 и др. Кроме того, в данный вариант блока 11 входит два RS-триггера 43 и 44 (например, на базе микросхем 561 ТР2, 564ТР2 или др.) и Т-триггер 45 (например, на базе микросхемы 133ТМ2).

Постоянное запоминающее устройство 41 программируется в соответствии с алгоритмом работы устройства, вариант блок- схемы которого приведен на фиг. 4. Роль блока 41 может выполнять также комбинационная схема или ПЛМ.

На фиг. 3 приведена одна из возможных схем, по которой может быть построен блок 7 регистров. Его структура подобна структуре стекового регистра. Число регистров N в

блоке 7 определяется соотношением разрядностей выходной шины запоминающего устройства 2(1) и его адресной шины (М) по формуле:

N ,

где М/Ц обозначает округление числа M/L к ближайшему большему целому. Вход 34 является входом управления приемом информации в параллельном коде.

0 Блок 7 может быть реализован из стандартных микросхем регистров, осуществляющих параллельный прием кода, например К564ИР6, К564ИР9 и др. Их структура достаточно подробно описывается в вышеупомя5 нутой литературе.

Для описания работы устройства опишем алгоритм поиска переводимого слова и структуру памяти блока 2. Память разделена на две части. В первой расположены слова

0 по алфавиту, во второй находится перевод. Перед началом каждого слова стоит метка начала. Само слово занимает столько ячеек памяти, сколько в нем букв, за ним находится метка конца слова. Одна ячейка содержит

5 код одной буквы или метку. В ячейках, стоящих посте метки конца слова, содержится адрес первой ячейки перевода. Затем снова находится метка начала слова и следующее слово.

0 Ячейки, содержащие перевод, разделены метками конца слова, слова в переводе разделены нулевыми ячейками.

Поиск нужного слова происходит следующим образом. Адреса первой и последней

5 ячеек, содержащих коды букв переводимых слов, хранятся в регистрах 4 и 15. Затем они складываются и делятся пополам. (Эффект деления на два достигается благодаря подсоединению выходов сумматора 3 к инфор0 мационным входам первой группы коммутатора 33 со сдвигом на один разряд). Дробная часть при делении отбрасывается. Полученный адрес поступает на вход блока 2 памяти, с выхода которого считывается

5 содержимое ячейки памяти. Затем происходит сравнение содержимого этой ячейки с кодом начала слова в дешифраторе 5. Если содержимое ячейки не является кодом начала слова, то происходит поиск ячейки с ко0 дом начала слова, к адресу прибавляется единица и с выходов блока 2 памяти считывается следующая ячейка памяти. Если же с выходов блока 2 считалось содержимое ячейки с кодом начала слова, то происходит

5 побуквенное сравнение выбранного слова и искомого слова в блоке 6 сравнения. Если коды первых букв равны, то в адресу добавляется единица, с выходов блока 2 считывается код второй буквы и происходит сравнение вторых букв выбранного и искомого слов. Таким образом, сравнение происходит до тех пор, пока с выхода блока памяти не считается ячейка с кодом конца слова. Тогда дешифратор 5 выдает соответствующий сигнал и происходит считывание адреса ячейки с кодом первой буквы перевода или учебной информации. Затем этот адрес поступает на вход запоминающего устройства и происходит считывание перевода или учебной информации.

В случае если код буквы на выходах блока 2 памяти больше кода буквы искомого слова, то текущий адрес сравниваемой буквы записывается в регистр 15, в котором хранился адрес ячейки с кодом последней буквы переводимых слов, а если меньше, то в регистр 4 с адресом ячейки с кодом первой буквы переводимых слов. Новые адреса складываются и делятся пополам. Новый адрес поступает на вход блока памяти и на его выходе появится содержимое новой ячейки памяти,

Далее поиск слова будет происходить аналогично описанному выше, однако поиск начала слова будет осуществляться не путем прибавления к адресу единицы, а путем вычитания 1. Если же слово опять не будет найдено, то поиск начала слова в следующем такте снова будет происходить путем добавления к адресу единицы.

В случае если искомого слова нет в блоке памяти, то на некотором шаге поиска в один из регистров, хранящих адреса сравниваемых ячеек, будет повторна записан хранящийся в нем адрес, через такт в другой регистр будет повторно записан адрес, хранящийся в нем. После того, как оба эти события произойдут, поиск слова прекращается.

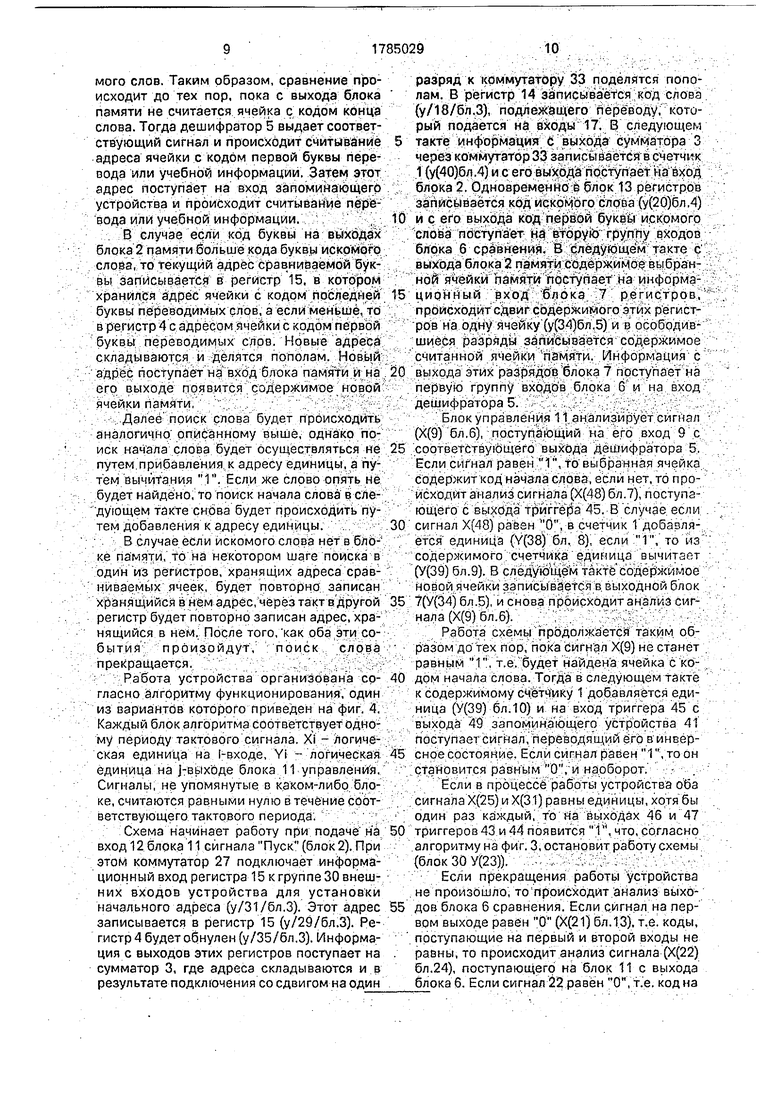

Работа устройства организована согласно алгоритму функционирования, один из вариантов которого приведен на фиг. 4. Каждый блок алгоритма соответствует одному периоду тактового сигнала Xi - логическая единица на i-входе, Yi - логическая единица на j-выходе блока 11 управления, Сигналы, не упомянутые в каком-либо блоке, считаются равными нулю в течение соответствующего тактового периода.

Схема начинает работу при подаче на вход 12 блока 11 сигнала Пуск (блок 2), При этом коммутатор 27 подключает информационный вход регистра 15 к группе 30 внешних входов устройства для установки начального адреса (у/31/бл.З). Этот адрес записывается в регистр 15 (у/29/бл.З). Регистр 4 будет обнулен (у/35/бл.З). Информация с выходов этих регистров поступает на сумматор 3, где адреса складываются и в результате подключения со сдвигом на один

разряд к коммутатору 33 поделятся пополам. В регистр 14 записывается код слова (у/18/бл.З), подлежащего переводу, коти- рый подается на входы 17, В следующем

такте информация С выхода сумматора 3 через коммутатор 33 записывается в счетчик 1 (у(40)бл.4) и с его выхода поступает на вход блока 2. Одновременно в блок 13 регистров записывается код искомого слова (у(20)бл,4)

0 и с его выхода код первой буквы искомого слова поступает на вторую группу входов блока 6 сравнения, В следующем такте с выхода блока 2 памяти содержимое выбранной ячейки памяти поступает на информа5 ционный вход блока 7 регистров, происходит сдвиг содержимого этих регистров на одну ячейку (у(34)бп.5) и в осободив- шиеся разряды записывается содержимое считанной ячейки памяти. Информация с

0 выхода этих разрядов блока 7 поступает на первую группу входов блока б и на вход дешифратора 5.

Блок управления 11 анализирует сигнал (Х(9) бл.б), поступающий на его вход 9 с

5 соответствующего выхода дешифратора 5. Если сигнал равен 1, то выбранная ячейка содержит код начала слова, если нет, то происходит анализ сигнала (Х(48) бл 7), поступающего с выхода триггера 45. В случае если

0 сигнал Х(48) равен О, в счетчик 1 добавляется единица (Y(38) бл. 8), если 1, то из содержимого счетчика единица вычитает (У(39) бл.9). В следующем такте содерх имое новой ячейки записывается в выходной блок

5 7(У(34) бл 5), и снова происходит анализ сигнала (Х(9) бл.б).

Работа схемы продолжается таким образом до тех пор, пока сигнал Х(9) не станет равным 1, т.е. будет найдена ячейка с ко0 дом начала слова. Тогда в следующем такте к содержимому счетчику 1 добавляется единица (У(39) бл.10) и на вход триггера 45 с выхода 49 запоминающего устройства 41 поступает сигнал, переводящий его в инвер5 сное состояние. Если сигнал равен 1,тоон становится равным О, и наоборот.

Если в процессе работы устройства оба сигнала Х(25) и Х(31) равны единицы, хотя бы один раз каждый, то на выходах 46 и 47

0 триггеров 43 и 44 появится 1м, что, согласно алгоритму на фиг. 3, остановит работу схемы (блок 30 У(23)).

Если прекращения работы устройства не произошло, то происходит анализ выхо5 дов блока 6 сравнения. Если сигнал на первом выходе равен О (Х(21) бл.13), т.е. коды, поступающие на первый и второй входы не равны, то происходит анализ сигнала (Х(22) бл.24), поступающего на блок 11с выхода блока 6. Если сигнал 22 равен О, т.е. код на

входах второй группы больше кода, поступающего на входы первой группы, то адрес с выхода счетчика 1 записывается в регистр 15 (У(29) бл.25). Одновременно происходит запись искомого слова в блок 13 регистров (У(20) бл.25), если сигнал Х(22) равен 1, то адрес с выхода счетчика 1 записывается в регистр 4(У(36) бл. 28) и также происходит запись искомого слова в блок 13 регистров (У(20) бл.28). Новый адрес, аналогично описанному выше, при установке начальных условий, пройдя через коммутатор 33 и сумматор 3, записывается в счетчик 1(У(40) бл.29), (У(40) бл.27), блок 11 продолжает свою работу согласно алгоритму на фиг. 4, начиная с блока 5. Если сигнал (Х(21) бл. 13) был равен 1, т.е. коды, поступающие на первые и вторые входы блока б равны, происходит анализ сигнала (Х(10) бл.14), поступающего на блок 11 управления с выхода блока совпадения. Если сигнал равен О, т.е. в ячейке, считанной в данный момент из блока 2 памяти, не содержится код конца слова, то к содержимому счетчику 1 добавляется единица (У(38) бл.15), происходит Сдвиг содержимого блока 13 на разрядность одной буквы (У(19) бл.15). В следующем такте в выходной блок 7 регистров (У(34) бл,1б) записывается новая ячейка, считанная из блока памяти. Затем блок управления, согласно алгоритму на фиг. 4, перехбдйт к анализу сигнала (Х(21) бл. 13).

В случае если сигнал Х(10) равен 1, т.е. коды слова, записанного в блоке 13 и считанного побуквенно из блока памяти, совпали до конца, происходит считывание начального адреса соответствующего перевода. Блок 7 регистров имеет длмну, доста- точную для размещения всех ячеек адреса начала служебной информации и ячейки с кодом начала слова. ,

К содержимому счетчика 1 добавляется единица (У(38) бл.17), затем происходит сдвиг содержимого блока 7 на одну ячейку У(34). В освободившиеся разряды записывается новая ячейка, затем происходит анализ сигнала (Х(9) бл. 19). В случае равенства его О происходит считывание следующей ячейки (бл. 17, бл. 18), а в случае его равенства 1 коммутатор 33 подключает информационные входы счетчика 1 к выходам второй группы блока 7, в котором хранится адрес учебной информации (У(37) бл.20). Этот адрес заносится в счетчик 1 (У(40) бл.20)дзатем происходит считывание информации, сдвигается блок регистров 7 (У(34) бл.21), информация поступает на информационные входы 8 устройства. Блок управления выдает сигнал (У(24) бл.21), синхронизирующий выходную информацию. Затем происходит добавление к содержимому счетчика 1 единицы (У(38) бл.23). Считывание происходит до тех пор, пока дешифратор 5 не выдаст сигнал о совпадении содержимого считанной ячейки с кодом

конца (Х(10) бл.22). Затем блок управления

выдает сигнал У(23), сигнализирующий об

окончании работы устройства (блок 30).

По сравнению с про.отипом, предлага0 емое устройство обладает повышенной емкостью, так как в ячейках памяти не содержится пустых битов и длина словарной статьи не ограничивается разрядностью ячейки памяти, поскольку

5 информация, относящаяся к одному входному слову, может занимать несколько соседних ячеек. Следовательно, заявляемое устройство имеет повышенные, по сравнению с прототипом, дидактические возмож0 ности.

Формула изобретения Устройство для изучения языка, содержащее блок памяти, первый блок совпадения, блок сравнения, счетчик, выходы

5 которого соединены с адресными входами блока памяти, первый и второй регистры и сумматор, информационные входы первой группы которого соединены с выходами первого регистра, отличающееся тем,

0 что, с целью повышения дидактических возможностей устройства, в него введены два коммутатора, второй блок совпадения, два блока регистров, блок управления, третий регистр и дешифратор, входы которого сое5 динены с информационными входами первой группы блока сравнения и с выходами первой группы первого блока регистров, являющимися информационными выходами устройства, выходы дешифратора соедине0 ны соответственно с первым и вторым информационными входами блока управления, третий информационный вход которого является входом запуска устройства, а тактовый вход соединен с управляющи5 ми входами первого и второго блоков регистров, первого, второго и третьего регистров и счетчика и является синхронизирующим входом устройства, первой группой информационных входов которого являются

0 соответствующие входы второго регистра, вход записи которого соединен с первым выходом блока управления, а выходы - с информационными входами второго блока регистров, входы сдвига и записи которого

5 соединены соответственно с вторым и третьим выходами блока управления, а выходы подключены к информационным входам второй группы блока сравнения, выходы которого соединены с четвертым и пятым информационными входами блока

управления, четвертый и пятый выходы которого являются синхронизирующими выходами устройства, а шестой информационный вход соединен с выходом первого блока совпадения, информационные входы первой группы которой соединены с информационными входами первой группы первого коммутатора, информационными входами первого регистра и инфор- мационными входами первой группы второго блока совпадения и выходами счетчика, а информационные входы второй груп- пы соединены с информационными входами второй группы сумматора и выходами третьего регистра, вход записи которого соединен с шестым выходом блока управления, а входы - с выходами первого коммутатора, информационные входы второй группы которого являются информационными входами второй группы устройства, а управляющий вход соединен с седьмым выходом блока управления, седьмой информационный вход которого соединен с выходом второго блока совпадения, информационные входы второй группы которого соединен с выходами первого регистра, выходы сумматора соединены с информационными входами первой группы второго коммутатора, информационные входы второй группы которого соединены с выходами второй группы первого блока регистров,

вход записи которого соединен с восьмым выходом блока управления, девятый и десятый выходы которого соединены соответственно с установочным и записывающим входами первого регистра, а одиннадцатый

выход соединен с управляющим входом вто- рого коммутатора, выходы которого соединены с информационными входами счетчика, суммирующий, вычитающий и записывающий входы которого соединены соответственно с двенадцатым, тринадцатым и четырнадцатым выходами блока управления.

Г

| название | год | авторы | номер документа |

|---|---|---|---|

| Ассоциативное оперативное запоминающее устройство | 1987 |

|

SU1462420A1 |

| Устройство для фиксации трассы выполнения программы | 1983 |

|

SU1136170A1 |

| Запоминающее устройство | 1987 |

|

SU1520592A1 |

| Электронный словарь для изучения иностранного языка | 1988 |

|

SU1702394A1 |

| Ассоциативное оперативное запоминающее устройство | 1989 |

|

SU1714682A1 |

| Устройство для обучения иностранным языком | 1989 |

|

SU1649591A1 |

| Ассоциативное оперативное запоминающее устройство | 1988 |

|

SU1667155A1 |

| Устройство для отладки программ | 1983 |

|

SU1290334A1 |

| Электронный словарь для изучения иностранного языка | 1988 |

|

SU1559367A1 |

| Электронный словарь для изучения иностранного языка | 1989 |

|

SU1649568A1 |

Изобретение относится к автоматике и вычислительной технике, в частности к устройствам для обучения, и может быть использовано для автоматизации процесса обучения иностранному языку. Целью изобретения является повышение дидактических возможностей. Устройство для изучения языка содержит блок памяти, первый блок совпадения, блок сравнения, счетчик, выходы которого соединены с адресными входами блока памяти, первый и второй регистры и сумматор, информационные входы первой группы которого соединены с выходами первого регистра, а также два коммутатора, второй блок совпадения, два блока регистров, блок управления, третий регистр и дешифратор. 4 ил.

I

Фиг. 2

cTfo76 о1R6

К&

I|

бK§/joktf 33

ФигЗ

J

Л

ASЛб

)

,) -/J

У (20, SO) г /

Я WW /

/о

У&8,49)/

|//i у; -7 (

./i

Й72. .

Редактор С. Кулакова

(Wg)

Составитель А. Михайлюк

Техред М.МоргенталКорректор А. Козориз

)/

ЈШ2Ы

| Электронное устройство для изучения морфологии иностранного языка | 1986 |

|

SU1417025A1 |

| Разборный с внутренней печью кипятильник | 1922 |

|

SU9A1 |

| Пневматический водоподъемный аппарат-двигатель | 1917 |

|

SU1986A1 |

Авторы

Даты

1992-12-30—Публикация

1990-12-25—Подача