}

Изобретение относится к автоматике и вычислительной технике, в частности к обучающим машинам, и может быть использовано в качестве устройства для генерации тестов, предназначенных для контроля знаний в учебных заведениях по различным дисциплинам .

Известно устройство для обучения, содержащее блок ввода учебной информации, блок управления, блок памяти ответов, блок вьюода учебной информации, блок анализа формы представления информации, дешифратор и блок памяти вопросов L1Однако это устройство имеет низкую надежность генерируемой информации и сложную структуру.

Известно также устройство для контроля знаний учащихся, которое содержит связанные соответствующим образом блок ввода, блок управления устройством, логический блок, блок предъявления информации, блок оценки, связанный с блоком индикации и регистрации, блок автоматического генерирования вопросов и ответов, блок записи информации, блок счетчиков количества вопросов и ответов, блок анализа информации С Недостатками устройства являются низкое быстродействие и ограниченные функциональные возможности.

Наиболее близким по технической

10 сущности и достигаемому эффекту к предлагаемому является устройство для обучения, содержащее блок ввода учебной информации, соединенный с блоком управления, блок памяти отве15тов, блок вывода информации, формирователь учебной информации, блок памяти учебной информации, блок анализа формы представления информации, дешифратор, блок памяти симво20ла разделов учебной информации, блок сравнения и блок совпадения 3j

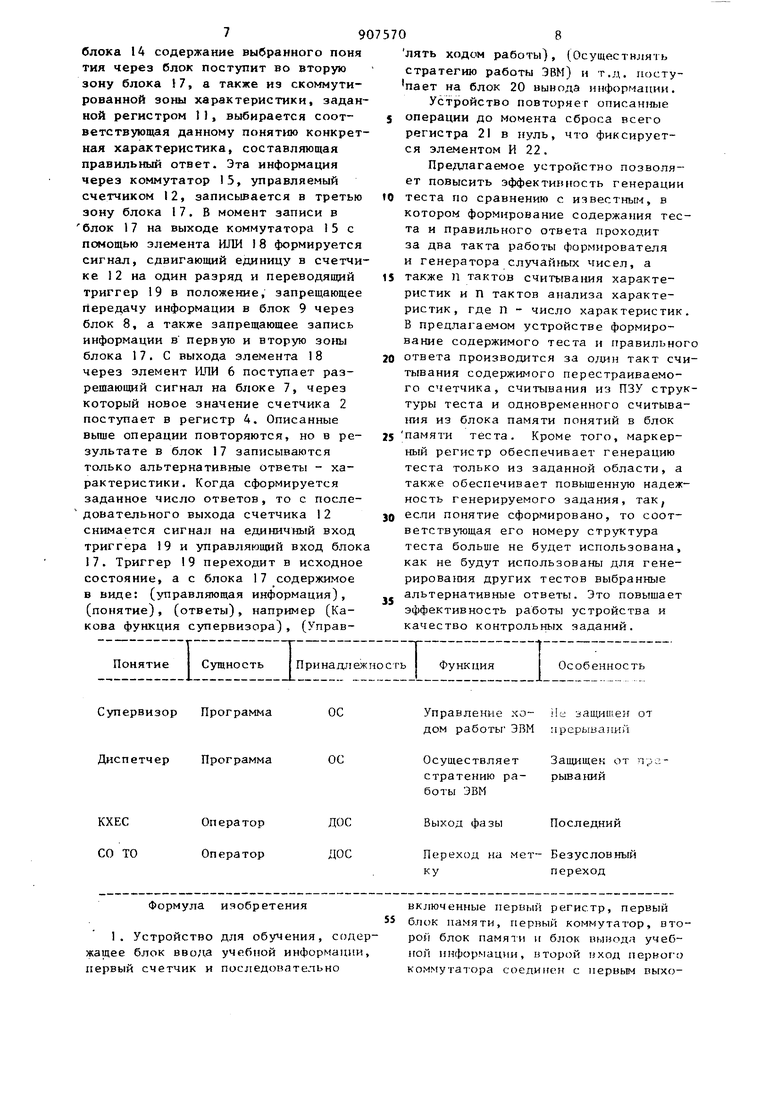

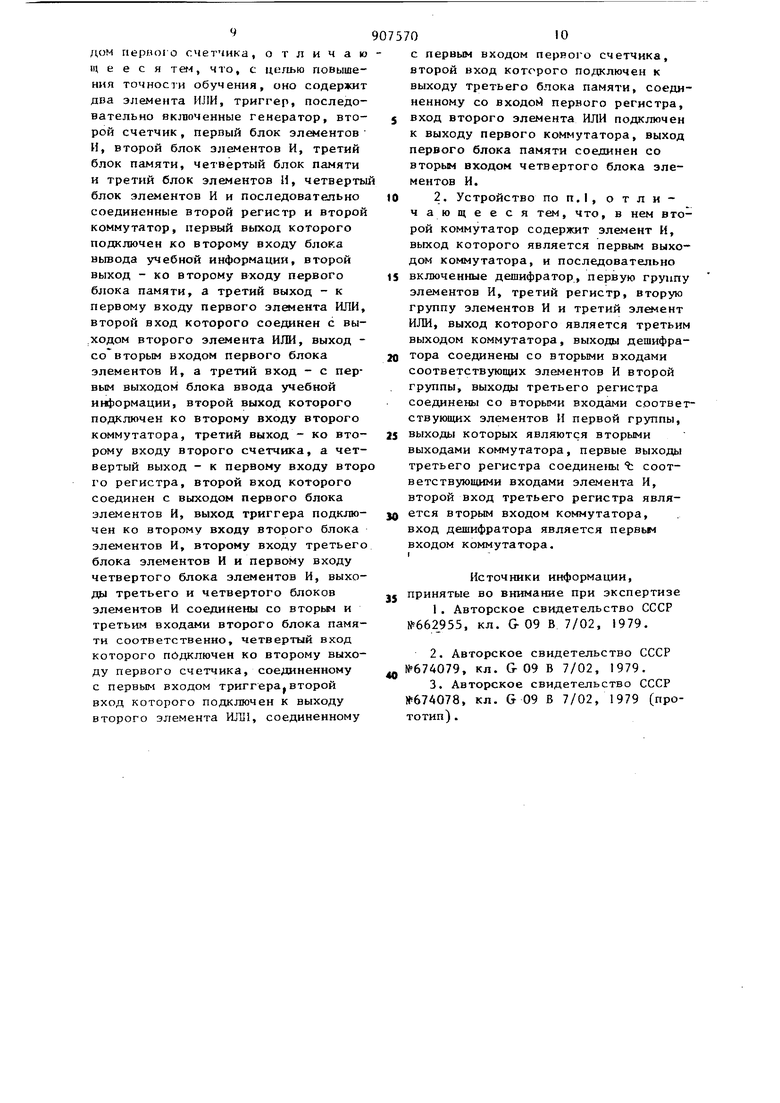

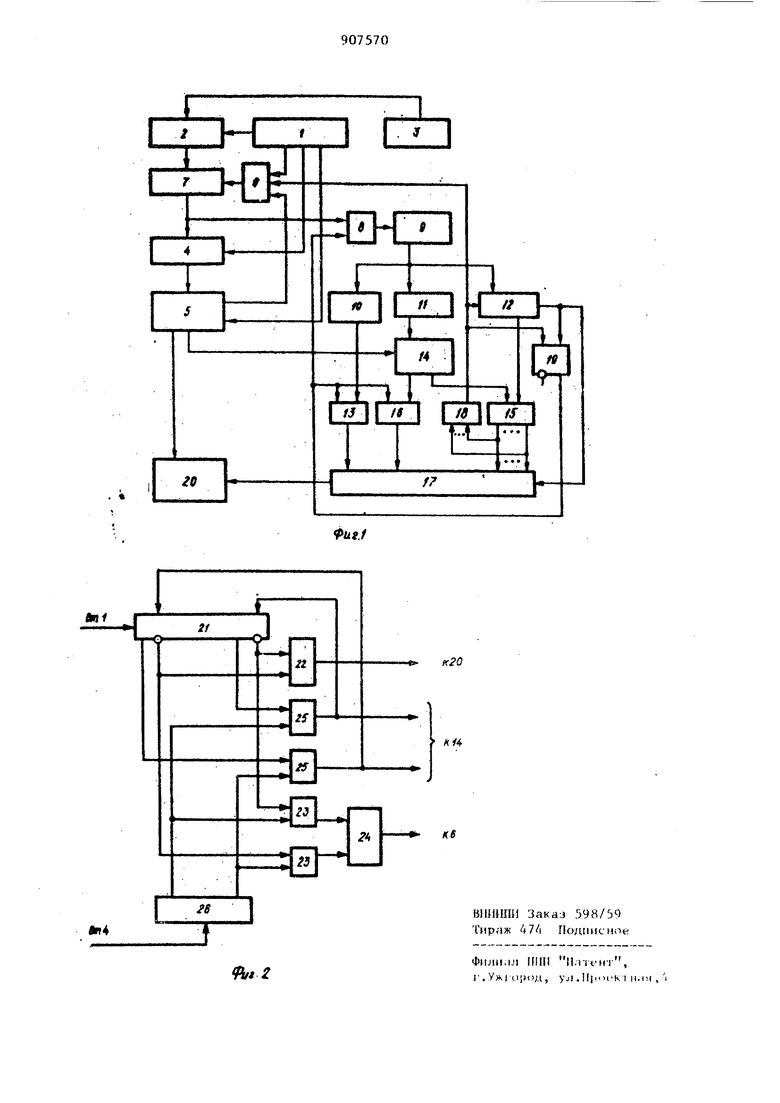

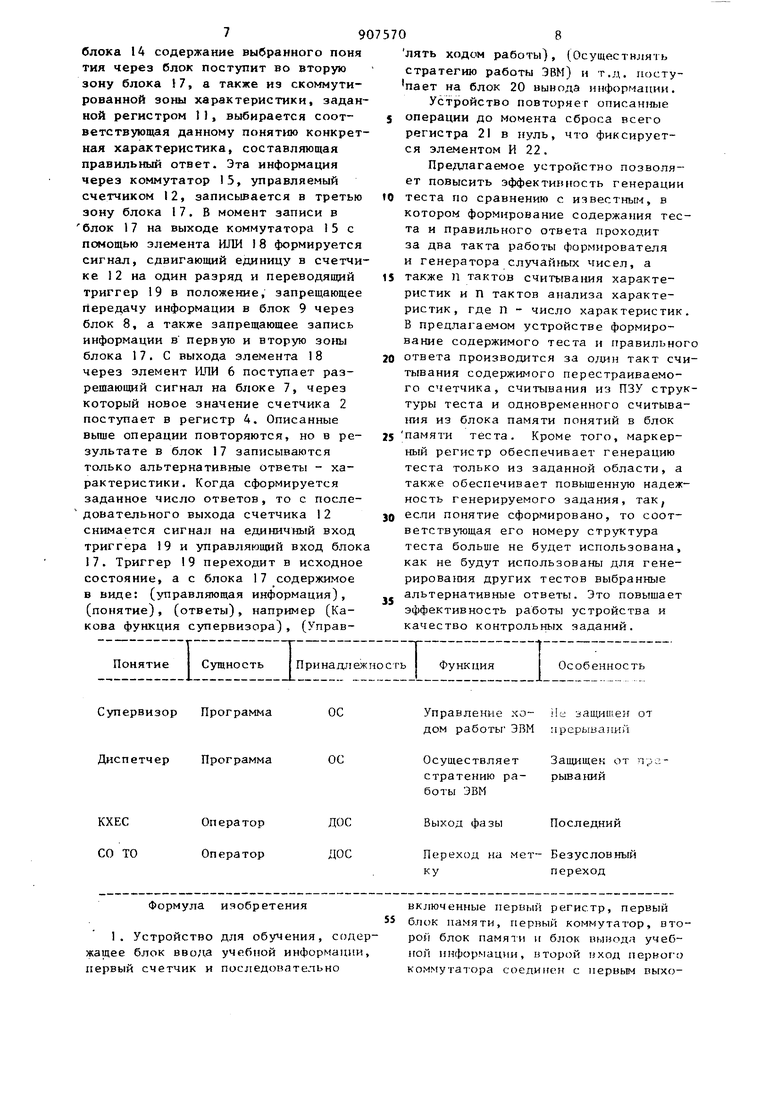

Известное устройство позволяет расширить дидактические возможности. однако имеет недостаточное быстродей ствие и низкую надежность из-за сложности структуры и большого количества последовательных условно зависящих операций. Цель изобретения - повышение точ ности обучения. Указанная цель достигается тем, что в устройство, содержащее блок ввода учебной информации, первый счетчик и последовательно включенные первый регистр, первый блок памяти, первый коммутатор, второй блок памяти и блок вывода учебной информации, второй вход первого ком мутатора соединен с первым выходом первого счетчика, в него введены два элемента ИЛИ, триггер, последовательно включенные генератор, второй счетчик, первый блок элементов И, второй блок злементов И, третий блок памяти, четвертый блок памяти и третий блок элементов И, четвертый блок элементов И и последовател но соединенные второй регистр и второй коммутатор, первый выход которого подключен ко второму входу блока вывода учебной информации, вт рой выход - ко второму входу первог блока памяти, а третий выход - к первому входу первого элемента ИЛИ, второй вход которого соединен с вых дом второго элемента ИЛИ, выход - с вторым входом первого блока элементов И, а третий вход - с первьм выходом блока ввода учебной информаци второй выход которого подключен ко второму входу второго коммутатора, третий выход - ко второму входу второго счетчика, а четвертый выход - к первому входу второго регистра, второй вход к.оторого соедин с выходом первого блока элементов И, выход триггера подключен ко второму входу второго блока элементов И, второму входу третьего блока эле ментов И и первому входу четвертого блока элементов И, выходы третьего и четвертого блоков элементов И соединены со вторым и третьим входами второго блока памяти соответственно четвертый вход которого подключен к второму выходу первого счетчика, соединенному с первым входом тригге ра, второй вход которого подключен к выходу второго элемента ИЛИ, соед ненному с Первым входом первого счетчика, второй вход которого подключен к выходу третьего TJ.TOK памяти, соединенному со входом первого регистра, вход второго элемснтя ИЛИ подключен к выходу перво -о коммутатора, выход первого блока ггамяти соединен со вторьи входом чртпертосо блока элементов Н. Кроме того, в нe второй коммутатор содержит элемент И, выход которого является первым выходом коммутатора, и последовательно включенные дешифратор, первую группу элементов И, третий регистр, вторую группу элементов I и третий элемент ИЛИ, выход которого является третьим выходом коммутатора, выходь дешифратора соединены со вторыми входами соответствующих элементов И второй группы, выходы третьего регистра соединены со вторыми входами соответствующих элементов И гтервой группы, выходы которых являются вторьпчи выходами коммутатора, первые выходы третьего регистра соединены с соответствующими входами элемента ц, второй вход третьего регистра является вторым входом коммутатора, вход дешифратора является первым входом коммутатора. На фиг. 1 изображена структура устройства для обучения; на фиг. 2 структура коммутатора, сл жащего для выборки понятия. Устройство для обучения содержит блок 1 ввода учебной информации, соединенный своими выходами непосредственно с перестраиваемым счетчиком 2, подключенным к выходу г-енеpaiopa 3, с регистром 4, коммут.тором 5 и через элемент ИЛИ i с блоком 7 элементов И, другям входом связанным со .счетчиком 2, а выходом - с регистром 4 и через блок 8 элементов И с блоком 9 памяти, выходом связанного с блоком 10 памяти регистром 11 и счетчиком 12 (количества ответов), выходы которых связаны соответственно с блоком 13 элементов И, блоком 14 памяти и коммутатором 15, второй вход которого подсоединен к блоку 14, соединенным с выходом коммутатора 5 и блоком 16 элементов И, выходы блока 13, блока 16и коммутатора 15 связаны с блоком 17памяти (теста). Кроме того, Hhixoды коммутатора 15 через элемент ИЛИ 18 соединены с элементом ИЛИ 6, подклБоченным входом также к коммута5lopy ), со счетным . (че1Ч11ьл 12 и нуленым нходом гри11Ч;ра 19, е ц|цнч)1ый нход которого coennFien г.и счетчиком 12, свя-клшым итим же выходом с блоком 17, а выход тригтера 19 подключен ко нторым входам блоков 8,.13 и 16. Выход блока 17 связан с блоком 20 вывода информации, подсоединенным также к выходу комму татора 5. Коммутатор 5 содержит регистр 21 инверсными выходами соединенный с элементом И 22 и через группу элементов Н 23 с элементом ИЛИ 24. Пря мые выходы регистра 21 через группу элементов И 25 соединены с нулевыми входами разрядов регистра 21, К вторым входам одноименных элементов блоков 23 и 25 подключены соответствующие выходы дешифратора 26. Блок 14 содержит словарь понятий который имеет следующую структуру. Список характеристик понятий может быть расширен. Список понятий ограничен только емкостью блока памяти. На базе словаря указанной структуры и управляющих слов, определяющих цель вопроса, могут генерироваться тесты различной структур с альтернативными ответами. В каждо строке блока 9 записана информация в виде трех цифр i, j, k, где i кодовый номер управляющей информаци определяющий тип структуры теста; j - номер колонки характеристики, соответствующей данному типу структуры теста; k - заданное число альтернативных ответов, включая правильный, возможных для данной струк туры теста. Управляющая информации в виде закодированных буквенных символов хранится в блоке 10. Каждая строка этих символов, записанная в одну ячейку, образует один из возможных вопросов. Например: Какова сущность..., В чем состоит функция.. Определители принадлежность... и т.п . Устройство для обучения работает следующим образом. Из блока 1 в коммутатор 5ц а именно в регистр 21, заносятся единицы в разряды регистра, соответствующие номера Понятий.в блоке 14, относящихся к данной области контро лируемых знаний. В регистр 4 из бло ка 1 заносится в первую зону каO6чальный номер понятия, относящегося к заданной области, а на управляю щих входах перестраиваемого счетчика 2 устанавливается код, ограничивающий коэффициент пересчета счетчика 2 размером заданно11 области понятий. По.сле включения устройства генератор 3 вырабатывает тактовые импульсы, поступающие на счетный вход счетчика 2, а с выхода блока I через элемент ИЛИ 6 поступает сигнал, разрешающий считывание со счетчика 2 ;ерез блок 7. Находящийся в данный момент на счетчике 2 код поступает во вторую зону регистра 4 и через открыты триггером 19 блок 8 И (п качестве адреса) в блок 9. Из блока 9 считывается по данному адресу структура теста в виде строки трех цифр i, j, k. Номер i управляющих слов поступает в блок 10, в результате из i-ой ячейки блока 10 через блок I3 считывается закодированная управляющая информация, которая записывается в первую зону блока 17. Номер j-ой характеристики, соответствующей j-ой управляющей информации, записывается в регистр 11, который коммутирует в блоке 1Д столбец соответствующей характеристики выборки правильного ответа. В счетчик 12 записывается число ответов для данного типа структуры теста. Одновременно информация, записанная в регистре 4, расшифровывается дешифратором 26 в направление, соответствующее номеру понятия. Если в регистре 21 соответствующий разряд находится в нулевом состоянии, то, следовательно, данное понятие уже использовалось и необходимо повторить операции для другого номера понятия. Это обеспечивается прохождением сигнала через один из элементов И 23, элемент ИЛИ 24 наэлемент ИЛИ 6, чем достигается считывание со счетчика 2 нового значения. Операция повторяется до того момента, когда направление, коммутируемое дешифратором 26, совпадет на одном из элементов 4 блока 25 с единичным состоянием соответствующего разряда регистра 21. Сигнал с этого элемента поступит на нулевой вход лаиного разряда регистра 21 и сброСИ1 его в нуль, а также поступит в блок 14. В результате этого из

блока 14 содержание выбранного пеня тия через блок поступит во вторую зону блока 17, а также из CKONfMyTHрованной зоны характеристики, заданной регистром 1I, выбирается соответствующая данному понятию конкретная характеристика, составляющая правильный ответ. Эта информация через коммутатор 5, управляемый счетчиком 12, записывается в третью зону блока 17. В момент записи в

блок 17 на выходе коммутатора 15 с псмощью элемента ИЛИ I8 формируется сигнал, сдвигающий единицу в счетчике 12 на один разряд и переводящий триггер 19 в положение, запрещающее передачу информации в блок 9 через блок 8, а также запрещающее запись информации в первую и вторую зоны блока 17. С выхода элемента 18 через элемент ИЛИ 6 поступает разрещающий сигнал на блоке 7, через который новое значение счетчика 2 поступает в регистр 4. Описанные вьше операции повторяются, но в результате в блок 17 записываются только альтернативные ответы - характеристики. Когда сформируется заданное число ответов, то с последовательного выхода счетчика 12 снимается сигнал на единичный вход триггера 19 и управлякзщий вход блок 17. Триггер 19 переходит в исходное состояние, а с блока 17 содержимое в виде: (управляющая информация), (понятие), (ответы), например (Какова функция супервизора), (УправI Сущность Понятие П ри на дг1 еж но сть

Супервизор Программа ОС

Диспетчер Программа ОС

лять ходом работы), (Осуществлять стратегию работы ЭВМ) и т.д. поступает на блок 20 вывода информации. Устройство повторяет описанные операции до момента сброса всего регистра 21 в пуль, что фиксируется элементом И 22.

Предлагаемое устройство позволяет повысить эффективность генерации теста по сравнению с известным, в котором формирование содержания теста и правильного ответа проходит за два такта работы формирователя и генератора случайных чисел, а

также п тактов считывания характеристик и П тактов анализа характеристик, где П - число характеристик. В предлагаемом устройстве формирование содержимого теста и правильного

ответа производится за один такт считывания содержи ого перестраиваемого счетчика, считывания из ПЗУ структуры теста и одновременного считывания из блока памяти понятий в блок памяти теста. Кроме того, маркерный регистр обеспечивает генерацию теста только из заданной области, а также обеспечивает повышенную надежность генерируемого задания, так, если понятие сформировано, то соответств тощая его номеру структура теста больше не будет использована, как не будут использованы для генерирования других тестов выбранные альтернативные ответы. Это повышает эффективность работы устройства и качество контрольных заданий.

Не защитен от прерываний

Защищен от пр рываНИИ Особенность Функция

| название | год | авторы | номер документа |

|---|---|---|---|

| Обучающее устройство | 1981 |

|

SU974394A1 |

| Устройство для обучения | 1981 |

|

SU985813A1 |

| Устройство для контроля знаний обучаемых | 1981 |

|

SU985811A1 |

| Устройство для контроля знаний обучаемых | 1981 |

|

SU1005152A1 |

| Устройство для контроля знаний обучаемых | 1982 |

|

SU1035633A1 |

| Обучающее устройство | 1979 |

|

SU842924A1 |

| Устройство для обучения | 1980 |

|

SU985814A1 |

| Устройство для обучения | 1981 |

|

SU963063A1 |

| Устройство для контроля знаний обучаемых | 1981 |

|

SU982063A1 |

| Обучающее устройство | 1978 |

|

SU752454A1 |

Формула изобретения 1. Устройство для обучения, содержащее блок ввода учебной информации, первый счетчик и последовательно включенные первый регистр, первый блок памяти, первый коммутатор, второй блок памя1и и блок ныиоДЧ учеб1ГОЙ информации, второй ход первого коммутатора соединен с иервым выходом первого счетчика, отличаю щееся ref-t, что, с целью повышения точности обучения, оно содержит два элемента ИЛИ, триггер, последовательно яключенные генератор, второй счетчик, первый блок элементов И, второй блок элементов И, третий блок памяти, четвертый блок памяти и третий блок элементов И, четверть блок элементов И и последовательно соединенные второй регистр и второй коммутатор, первый выход которого подключен ко второму входу блока вьгеода учебной информации, второй выход - ко второму входу первого блока памяти, а третий выход - к первому входу первого элемента ИЛИ, второй вход которого соединен с выходом второго элемента ИЛИ, выход со вторым входом первого блока элементов И, а третий вход - с первым выходом блока ввода учебной информации, второй выход которого подключен ко второму входу второго коммутатора, третий выход - ко второму входу второго счетчика, а четвертый выход - к первому входу втор го регистра, второй вход которого соединен с выходом первого блока элементов И, выход триггера подключен ко второму входу второго блока элементов И, второму входу третьего блока элементов И и первому входу четвертого блока элементов И, выходы третьего и четвертого блоков элементов И соединены со вторьм и третьим входами второго блока памяти соответственно, четвертый вход которого подключен ко второму выходу первого счетчика, соединенному с первьм входом триггера второй вход которого подключен к выходу второго элемента , соединенному 010 с первым входом перво1о счетчика, второй вход которого подключен к выходу третьего блока памяти, соединенному со входов первого регистра, вход второго элемента ИЛИ подключен к выходу первого коммутатора, выход первого блока памяти соединен со вторым входом четвертого блока элементов И. 2. Устройство по п,|, отличающееся тем, что, в нем второй коммутатор содержит элемент И, выход которого является первым выходом коммутатора, и последовательно включенные дешифратор, первую группу элементов И, третий регистр, вторую группу элементов И и третий элемент ИЛИ, выход которого является третьим выходом коммутатора, выходы дешифратора соеда1нены со вторыми входами соответствующих элементов И второй группы, выходы третьего регистра соединены со вторыми входами соответствующих элементов И первой группы, выходы которых являются вторыми выходами коммутатора, первые выходы третьего регистра соединены t соответствующими входами элемента И, второй вход третьего регистра является вторым входом коммутатора, вход дешифратора является первьм входом коммутатора. Источники информации, принятые во внимание при экспертиэе 1.Авторское свидетельство СССР №662955, кл. & 09 В 7/02, 1979. 2.Авторское свидетельство СССР 674079, кл. G- 09 В 7/02, 1979. 3.Авторское свидетельство СССР 674078, кл. G 09 В 7/02, 1979 (прототип) .

Авторы

Даты

1982-02-23—Публикация

1980-04-07—Подача