&

ее сл

ko со

00

Фие.1

Изобретение относится к вычисли- .тельной технике и может быть исполь- |зовано в системах передачи информа- |ции.

I Целью изобретения является повы- 1шение быстродействия преобразователя

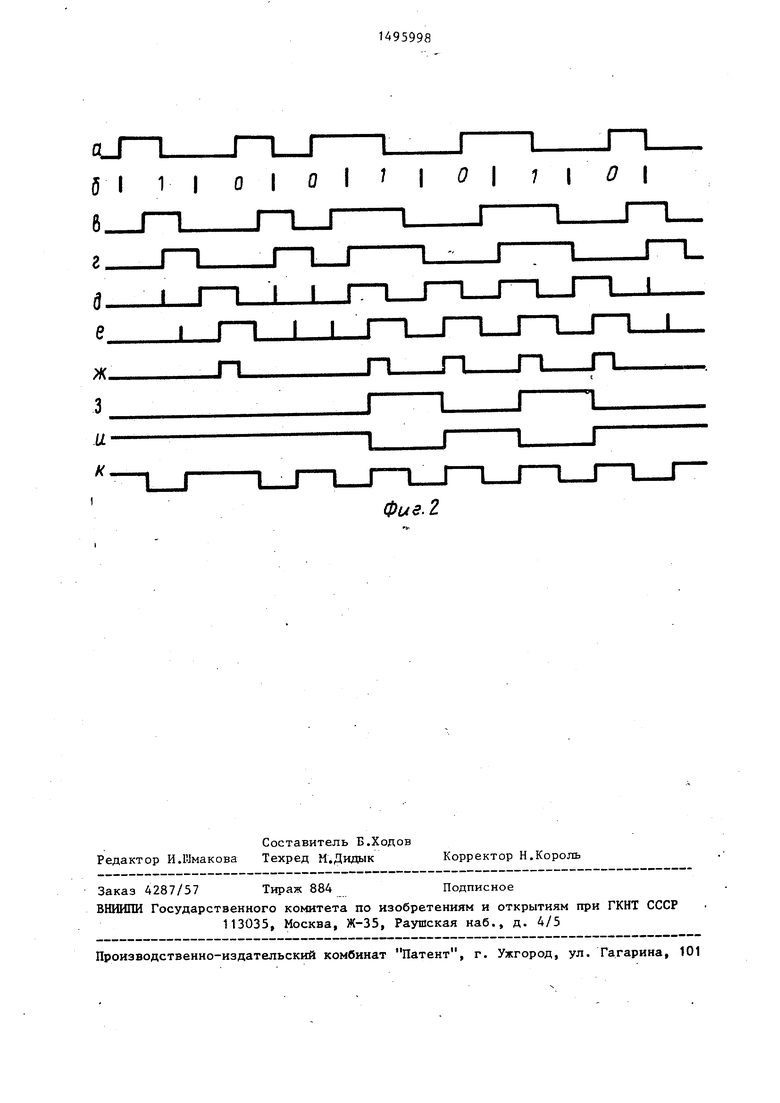

На фиг. 1 представлена функцио- нальная схема преобразователя; на 1ФИГ. 2 - временные диаграммы, пояс |няющие работу преобразователя. I Преобразователь кода содержит |первый элемент 1 задержки, элемент ИСКЛЮЧАЮЩЕЕ или 2 триггер 3, элемент И 4, второй элемент 5 задержки и элемент 6 равнозначности и имеет вход 7, первый 8 и второй 9 выходы.

На фиг. 2 обозначены следующие сигналы: а - сигнал на входе 7; б - логическая информация; в - сиг- нал на первом выходе элемента 1; г - сигнал на втором выходе элемента 1; д. - сигнал на выходе элемента 6; е - сигнал на выходе элемента 5; ж - сигнал на выходе элемента 4; 3, и - сигналы на выходах триггера 3; к - сигнал на выходе 8. I Преобразователь кода работает iследующим образом.

На вход 7 преобразователя посту- .пают данные в коде Манчестера, coof- ;Ветствующие логической информагщи. Элемент 1 задержки задерживает вход- ные сигналы по первому выходу в пре- ;делах от времени переключения эле- мента И 4 до 1/2 тактового интервала а по второму выходу задержка равна 1/2 тактового интервала Сигнал с выхода элемента 6 равнозначности непосредственно и через второй элемент 5 задержки, величина которой может л-ежать в пределах от величины задержки в. элементе И 4 до этой величины плюс 1/2 тактового интервала, поступает на входы элемента И 4. Сигнал . с выхода элемента И 4 передним фронтом тактирует входные данные, посту

лающие с входа 7 на информационный вход триггера 3. На прямом и инверсном выходах триггера 3 формируются сигналы в коде без возврата к нулю (БВН) поступающие соответственно на выход 9 и на вход элемента ИСКЛЮЧАЮЩЕЕ ИЛИ 2, на другой вход которого поступают задержанные входные данные с выхода элемента 1 задержки. На выходе элемента ИСКЛЮЧАЮЩЕЕ ИЛИ 2 путем суммирования по модулю два входных сигналов формируются тактовые импульсь, пocтyпaюI J e на выход 8 устройства. Таким образом, преобразователь кода обеспечивает декодирование кода Манчестера в код БВН и вьщеление тактовых импульсов.

Формула изобретения . Преобразователь кода, содержащий первый элемент задержки, вход которого является входом преобразователя,, первый выход соединен с первым входом элемента ИСКЛЮЧАЮЩЕЕ ИЛИ, выход которого является первым выходом преобразователя, триггер, инверсный выход которого соединен с вторым входом элемента ИСКЛ10ЧА10Р1ЕЕ 1ШИ., прямой выход триггера является вторым выходом преобразователя, о т л и ч а- ю щ и и с я тем, что, с целью повышения быстродействия, 1з преобразователь введены элемент И, второй элемент задеряски и элемент РАВНОЗНАЧ- .НОСТЬ, выход которого соединен непосредственно с первым входом элемента И, через второй .элемент задержки с вторым входом элемента И, выход которого соединен с входом синхронизации триггера, информационный вход которого обьединен с первым входом элемента РАВНОЗНАЧНОСТЬ и с входом первого элемента задержки, второй выход которого соединен с вторьм входом элемента РАВНОЗНАЧНОСТЬ.

| название | год | авторы | номер документа |

|---|---|---|---|

| Преобразователь кода | 1986 |

|

SU1372624A1 |

| Преобразователь кода | 1986 |

|

SU1325707A1 |

| Преобразователь кода | 1985 |

|

SU1290533A1 |

| Преобразователь кода | 1984 |

|

SU1266007A1 |

| УСТРОЙСТВО ДЛЯ ПЕРЕДАЧИ ДВОИЧНОЙ ИНФОРМАЦИИ | 1991 |

|

RU2022479C1 |

| Преобразователь кода | 1990 |

|

SU1783614A1 |

| Преобразователь частотно-модулированного кода | 1990 |

|

SU1809538A1 |

| Преобразователь частотно-модулированного кода | 1990 |

|

SU1809537A1 |

| УСТРОЙСТВО для ПАРАЛЛЕЛЬНОГО ПРЕОБРАЗОВАНИЯ РЕФЛЕКСНОГО КОДА В ДВОИЧНЫЙ КОД | 1973 |

|

SU369706A1 |

| ПРЕОБРАЗОВАТЕЛЬ КОДА | 2003 |

|

RU2260907C2 |

Изобретение относится в вычислительной технике и может быть использовано в системах передачи информации. Цель изобретения - повышение быстродействия преобразователя за счет сокращения времени задержки формирования выходных сигналов при преобразовании кода Манчестера в код БВН. Кроме того, обеспечивается достоверная работа не только после изменения состояния входного кода с "0" на "1", но также и при изменении состояния с "1" на "0". Преобразователь кода содержит два элемента 1 и 5 задержки, элемент ИСКЛЮЧАЮЩЕЕ ИЛИ 2, триггер 3, элемент 4 И и элемент 6 равнозначности. 2 ил.

Фие.2

| Преобразователь кода | 1984 |

|

SU1266007A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1989-07-23—Публикация

1987-12-14—Подача