КйбВН

00

о ю ел ы -ч

Изобретение относится к вычислительной технике, предназначено для преобразования частотно-манипулированного (ЧМ) кода в код без возвращения к нулю (БВН) и может быть использовано в аппаратуре пё- редачи информации.

Целью изобретения является повышение быстродействия преобразователя.

На фиг. 1 приведена структурная схема заявляемого преобразователя (пример кон- кретного выполнения); на фиг.2 - возможные выполнения расширителя импульсов.

Преобразователь содержит первый элемент 1 НЕ, элемент 2 задержки, второй элемент 3 НЕ D-триггеры 4,5, третий элемент 6 НЕ, элемент 7 И и расширитель 8 импульсов. . . : . .. -. -.. ...,

Расширитель 8 импульсов может быть реализован различными способами.

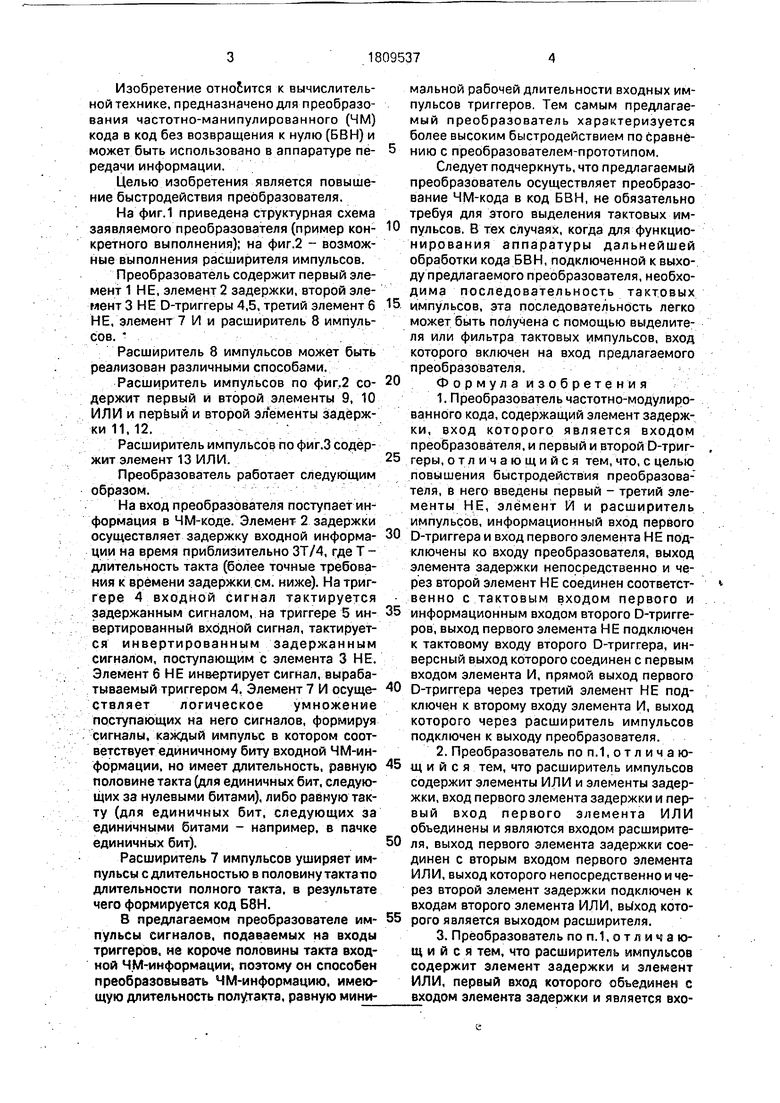

Расширитель импульсов по фиг.2 со- держит первый и второй элементы 9, 10 ИЛИ и первый и второй элементы задержки 11,12.:

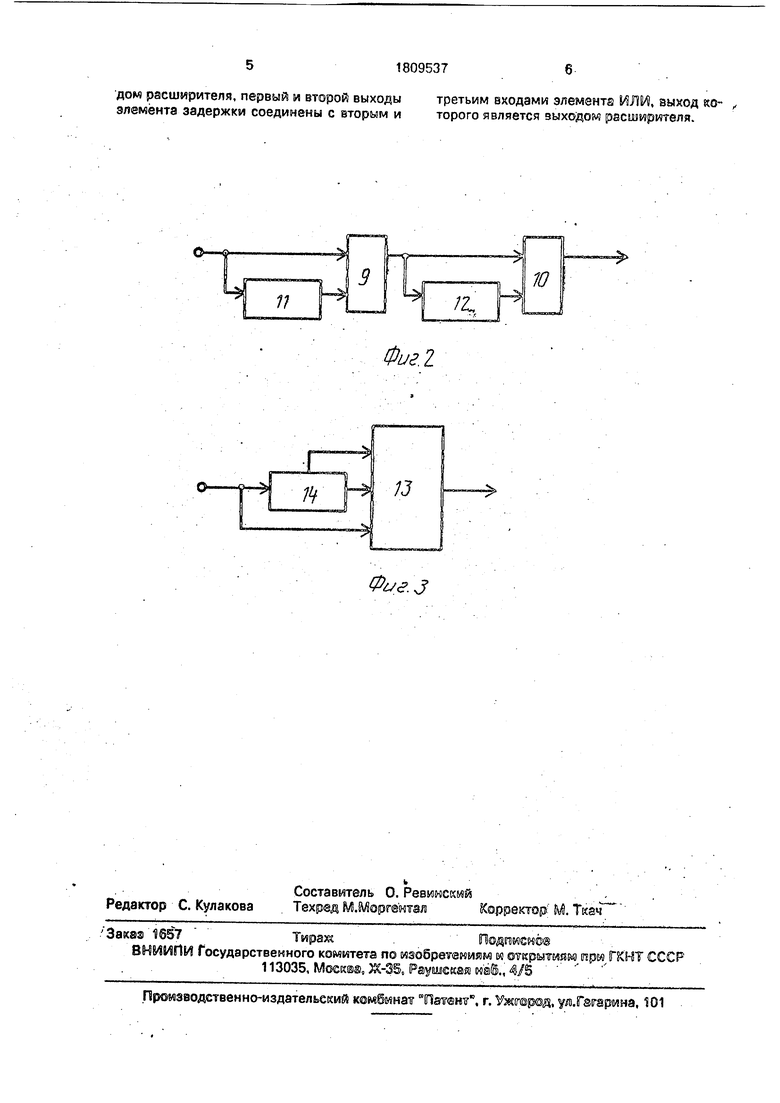

Расширитель импульсов по фиг.З содержит элемент 13 ИЛИ.

Преобразователь работает следующим образом.

На вход преобразователя поступает информация в ЧМ-коде. Элемент 2 задержки осуществляет задержку входной информа- ции на время приблизительно ЗТ/4, где Т - длительность такта (более точные требования к времени задержки см. ниже). На триггере 4 входной сигнал тактируется задержанным сигналом, на триггере 5 ин- вертированный входной сигнал, тактируется инвертированным задержанным сигналом, поступающим с элемента 3 НЕ. Элемент б НЕ инвертирует сигнал, вырабатываемый триггером 4, Элемент 7 И осуще- ствляет логическое умножение поступающих на него сигналов, формируя сигналы, каждый импульс в котором соответствует единичному биту входной ЧМ-ин- формации, но имеет длительность, равную половине такта (для единичных бит, следующих за нулевыми битами), либо равную такту (для единичных бит, следующих за единичными битами - например, в пачке единичных бит).

Расширитель 7 импульсов уширяет импульсы с длительностью в половинутактатю длительности полного такта, в результате чего формируется код Б8Н.

В предлагаемом преобразователе им- пульсы сигналов, подаваемых на входы триггеров, не короче половины такта входной ЧМ-информации, поэтому он способен преобразовывать ЧМ-информацию, имеющую длительность полутакта, равную минимальной рабочей длительности входных импульсов триггеров. Тем самым предлагаемый преобразователь характеризуется более высоким быстродействием по сравнению с преобразователем-прототипом.

Следует подчеркнуть, что предлагаемый преобразователь осуществляет преобразование ЧМ-кода в код БВН, не обязательно требуя для этого выделения тактовых импульсов. В тех случаях, когда для функционирования аппаратуры дальнейшей обработки кода БВН, подключенной к выходу предлагаемого преобразователя, необходима последовательность тактовых импульсов, эта последовательность легко может быть получена с помощью выделителя или фильтра тактовых импульсов, вход которого включен на вход предлагаемого преобразователя.

Формула изобретения

1. Преобразователь частотно модулиро- ванного кода, содержащий элемент задержки, вход которого является входом преобразователя, и первый и второй D-триггеры, о т л и ч а ю щ и и с я тем, что, с целью повышения быстродействия преобразователя, в него введены первый - третий элементы НЕ, элемент И и расширитель импульсов, информационный вход первого D-триггера и вход первого элемента НЕ подключены ко входу преобразователя, выход элемента задержки непосредственно и через второй элемент НЕ соединен соответственно с тактовым входом первого и информационным входом второго D-тригге- ров, выход первого элемента НЕ подключен к тактовому входу второго D-триггера, инверсный выход которого соединен с первым входом элемента И, прямой выход первого D-триггера через третий элемент НЕ подключен к второму входу элемента И, выход которого через расширитель импульсов подключен к выходу преобразователя.

2. Преобразователь по п.1, от л и ч а ю- щ и и с я тем, что расширитель импульсов содержит элементы ИЛИ и элементы задержки, вход первого элемента задержки и пер- вый вход первого элемента ИЛИ объединены и являются входом расширителя, выход первого элемента задержки соединен с вторым входом первого элемента ИЛИ, выход которого непосредственно и через второй элемент задержки подключен к входам второго элемента ИЛИ, вь(ход которого является выходом расширителя.

3. Преобразователь по п. 1. о т л и ч а ю- щ и и с я тем, что расширитель импульсов содержит элемент задержки и элемент ИЛИ, первый вход которого объединен с входом элемента задержки и является входом расширителя, первый и второй выходы третьим входами элемента ИЛИ, выход ко- ,, элемента задержки соединены с вторым и торого является выходом расширителя.

| название | год | авторы | номер документа |

|---|---|---|---|

| Преобразователь частотно-модулированного кода | 1990 |

|

SU1809538A1 |

| "Преобразователь кода Фибоначчи в код "золотой" пропорции" | 1990 |

|

SU1783616A1 |

| Устройство для умножения | 1985 |

|

SU1254473A1 |

| Преобразователь биимпульсного кода в код "без возврата к нулю | 1986 |

|

SU1405112A1 |

| Преобразователь напряжение-код с коррекцией динамической погрешности | 1975 |

|

SU898609A1 |

| Преобразователь кода | 1985 |

|

SU1290533A1 |

| Аналого-цифровой преобразователь | 1990 |

|

SU1720160A1 |

| Устройство для передачи и приема цифровой информации | 1984 |

|

SU1285614A1 |

| СПОСОБ ПРЕОБРАЗОВАНИЯ ДВОИЧНОГО СИГНАЛА В ПЯТИУРОВНЕВЫЙ СИГНАЛ | 2010 |

|

RU2428787C1 |

| Устройство для формирования циклического синхроимпульса | 1989 |

|

SU1725404A1 |

Изобретение относится к вычислительной технике. Его использование в аппаратуре передачи информации позволяет повысить быстродействие. Преобразователь содержит элемент 2 задержки и триггеры 4,5. Благодаря введению элементов НЕ 1,3,6 элемента И 7 и расширителя 8 импульсов импульсы, подаваемые на входы триггеров 4,5, не короче половины такта входных ЧМ-сигналов, полутакт которых поэтому может быть, равен минимальной рабочей длительности входных импульсов триггеров 4,5. 2 з.п.ф-лы, 3 ил.

Фиг.

0k/e. j

| Электронная техника .в автоматике, 1986 | |||

| Печь для сжигания твердых и жидких нечистот | 1920 |

|

SU17A1 |

| Electronic Design, 1978, v.26, № 22, рр.84-91 | |||

| Патент США № 4746898, кл | |||

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Механическая топочная решетка с наклонными частью подвижными, частью неподвижными колосниковыми элементами | 1917 |

|

SU1988A1 |

Авторы

Даты

1993-04-15—Публикация

1990-12-27—Подача