1

Изобретение может быть использовано в быстродействуюндих цифровых вычислительных машинах параллельного действия, а также в системах с импульсно-кодовой модуляцией.

Известны устройства для параллельного преобразования рефлексного кода в двоичный код, работающие по принципу логического сложения.

Однако известные преобразователи имеют низкую скорость работы. Подобные преобразователи устойчиво работают на частотах порядка 100-200 кгц, когда можно пренебречь временем задержки кодовых сигналов в ячейках отрицания равнозначности. На высоких частотах (10-20 мгц) при соизмеримых значениях времени задержки ячейки отрицания равнозначности и периода преобразуемых импульсов возникают ошибки преобразования, обусловленные неодновременным появлением анализируемых разрядов на входах ячеек отрицания равнозначности. Кроме того, величина ошибок существенно увеличивается даже при незначительных отклонениях временных положений входных импульсов рефлексного кода. Эти факторы приводят к ограничению числа реализуемых разрядов преобразователя и к снижению его быстродействия.

Применение временных регенераторов между схемами отрицания равнозначности не

исключает возникновения ошибок на них выходах, вызываемых временными отклонениями сигналов рефлексного кода, и значительно увеличивает время задерлхки распространения на

один разряд, что также ограничивает быстродействие преобразователя.

С целью уменьшения ошибок преобразования при увеличении частоты входных импульсов в предлагаемом устройстве между входом

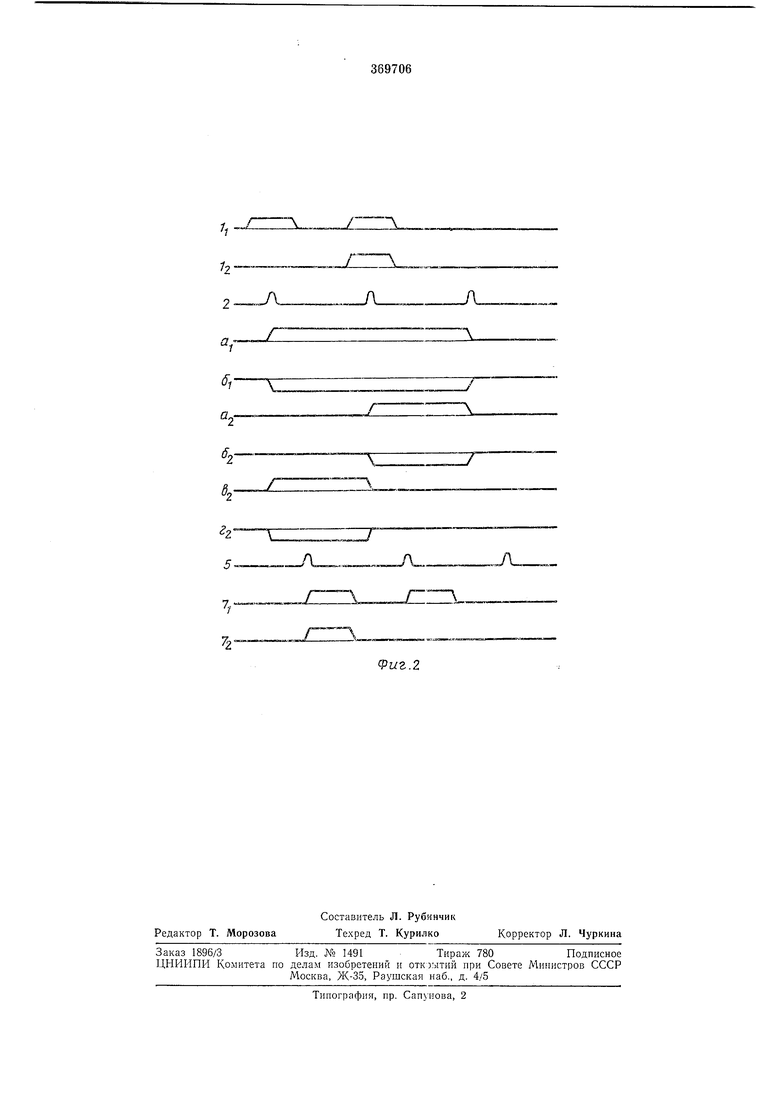

разряда преобразователя и соответствующей схемой отрицания равнозначности включен блок формирования обобщенного телеграфного сигнала. На фиг. 1 дана блок-схема предлагаемого

устройства; на фиг. 2--временные диаграммы работы первых двух разрядов преобразователя.

Предлагаемое устройство содержит входы Л - In разрядов рефлексного кода (1-й разряд - старший); вход 2 синхросигнала, управляющего ячейками преобразовання двоичного кода в обобщенный телеграфный сигнал, ячейки 3i-Зп, преобразующие двоичный код в обобщенный телеграфный сигнал, необходимые для увеличения времени преобразования сигналов от величины длительности импульсов до величины длительности периода импульса; ячейки 2-4п, реализующие логическую операцию отрицания равнозначности, которая является ключевой операцией при преобразоваНИИ рефлексного кода в натуральный код (нервый, старший разряда не содержит ячейки отрнцання равнозначности, рефлексного кода, так как он соответствует нервому разряду натурального,.хода и в иреобразовании не нуждается; вход 5 стробируюидего синхросигнала, формирующего выборки сигналов натурального кода из задержанных выходных сигналов схем отрицания равнозначности, ячейки 6i-6п стробирования н формирования импульсов натурального кода, формирующие из обобщенного телеграфного сигнала импульсы заданной длительности при определенном временном иоложении; выходы разрядов натурального кода; элемент 5 задержки, необходимый для задержки синхросигнала на величину задержки распространения сигналов через схему отрицания равнозначности одного разряда; элемент 9 задержки, необходимый для задержки сигналов рефлексного кода на суммарную величину задержек ячеек 4 всех предшествующих разрядов; схему «И/НЕ 10, регистрирующую совпадения сигнала рефлексного кода соответствующего разряда и синхросигнала; схему «И }1, регистрирующую совпадение инверсного значения сигнала рефлексного кода (отсутствие импульса на входе данного разряда) и синхросигнала; триггер 12 с раздельными входами, предназначенный для расширения длительности входного импульса до длительности его периода; схему «И 13, регистрирующую совпадение выходного сигнала ячейки 4 предыдущего разряда инверсного значения сигнала на выходе триггера данного разряда, необходимую для преобразования рефлексного кода в натуральный код, когда на прямом выходе ячейки 4 предыдущего разряда имеется сигнал, а в рефлексном коде данного разряда сигнал отсутствует (в случае отсутствия импульса на входе данного разряда триггер находится в нулевом состоянии, а на инверсном выходе - единица); схему «И 14, регистрирующую совпадение инверсного значения выходного сигнала ячейки 4 иредыдущего разряда и сигнала на прямом выходе триггера данного разряда, необходимую для преобразования рефлексного кода в натуральный код, когда на прямом выходе ячейки 4 предыдущего разряда отсутствует сигнал, а в рефлексном коде данного разряда сигнал имеется; схему «ИЛИ 15, объединяющую значение сигналов на выходах схем 13 и 14; элемент 16 задержки, необходимый для задержки сигналов преобразованного рефлексного кода на суммарную величину задержек всех ячеек 4 последующих разрядов; схему «И 17 стробирования выходного сигнала ячеек 4 узким стробирующим импульсом со входа 5, исключающую возможные ошибки ячейки 4 на границах тактового интервала, возникновение которых обусловлено отклонением положений сигналов рефлексного кода; схему 18 формирования заданной длительности, формы и амплитуды сигналов натурального кода.

«-разрядный преобразователь кодов состоит из п ячеек 3i-Зп, осуществляющих перевод рефлексного кода в обобщенный телеграфный сигнал; h - 1 ячеек 42-4п, выполняющих логические операции отрицания равнозначности, и п ячеек 6i-5„ формирования импульсов двоичного натурального кода.

Применение обобщенного телеграфного сигнала для схем отрицания равнозначности позволяет увеличить время преобразования до тактового интервала (периода импульсов рефлексного кода), а требования к временной стабильности сигналов рефлексного кода существенно снижаются, так как ошибки, возникающие на выходах схем отрицания равнозначности из-за сдвига анализируемых разрядов, исключаются последующим стробированием.

Работа преобразователя происходит следующим образом.

Функциональное построение всех разрядов преобразователя, кроме первого полностью идентично. Отличие первого, старшего, разряда от остальных заключается в отсутствии схемы отрицания равнозначности, так как старщий разряд в рефлексном коде соответствует старшему разряду натурального кода.

Сигналы рефлексного кода подаются на выходы /1-In преобразователя и через элементы задержки 9, компенсирующие задержку распространения старших разрядов, поступают на первые входы схем «И - НЕ 10 ячеек 3i- Зп. (Здесь и далее работа преобразователя рассматривается на иримере 3-го разряда, раскрытого на блок-схеме фиг. 1 до функциональной схемы). Нри наличии на первом входе схемы «И - НЕ 10 сигнала рефлексного кода, а на втором входе - синхросигнала, этой схемой регистрируется совпадение, и сигнал с прялЮго выхода схемы «И - НЕ 10 устанавлквает триггер в единичное состояние. При отсутствии сигнала рефлексного кода на входе схемы «И - НЕ 10 схемой «Н // регистрируется совпадение инверсного значения выхода схемы «И - НЕ 10 и синхросигнала, в результате чего выходной сигнал схемы «И 11 сбрасывает триггер 12 в нулевое состояние.

Таким образом, ячейка 3 преобразует двоичиый рефлексиый код в обобщенный телеграфный сигнал.

Далее с прямого и инверсного выходов триггера сигнал поступает на входы схем «И 13 и 14 ячейки 4 отрицания равнозначности. Применение двойных связей (по прямому и инверсному значению сигналов) между ячейками 3 и 4 позволяет исключить из классической схемы отрицания равнозначности два инвертора, что, в свою очередь, уменьшает общую задержку, вносимую схемами отрицания равнозначности.

На другие входы схем «И 13 и 14 подается прямое инверсное значение сигнала соседнего старшего разряда. Схема «И 13 регистрирует совпадение, когда на прямом выходе ячейки 4 старшего разряда имеется сигнал, а в рефлексном коде данного разряда сигнал отсутствует. Схема «И 14 регистрирует совиадение, когда на прямом выходе ячейки 4 старшего разряда отсутствует сигнал, а в рефлексном коде данного разряда сигнал имеется.

Выходные значения сигналов схем «И 13 и 14 объединяются схемой «ИЛИ 15 и постуиают на схему отрицания равнозначности следующего младшего разряда и на ячейку 6 формирования и стробирования импульсов натурального кода. В ячейке 6 сигнал задерживается элементом 16 задержки на величину задержки всех последующих ячеек 4 младщих разрядов, что необходимо для одновременного сгробирования (схема «И 17 сигналов.

Схема 18 формирования формирует заданную амплитуду и длительность сигналов натурального кода.

Предмет изобретения

Устройство для параллельного иреобразования рефлексного кода в двоичный код, содержащее соединенные последовательно схемы отрицания равнозначности ио одной в каждом разряде преобразователя, кроме старщего, каждая из которых подключена к соответствующей схеме стробирования, отличающееся тем, что, с целью уменьшения ошибок преобразования npii увеличении частоты в.ходных импульсов, между входом каждого разряда

преобразователя и соответствующей схемой отрицания равнозначности включен блок формирования обобщенного телеграфного сигнала.

yrm.

ъ2ZI

d;-Y

А

И

| название | год | авторы | номер документа |

|---|---|---|---|

| Преобразователь параллельного кода в последовательный | 1987 |

|

SU1547076A1 |

| Преобразователь двоичного однопеременного кода в позиционный двоичный код | 1980 |

|

SU955023A1 |

| Преобразователь кодов | 1987 |

|

SU1444957A1 |

| ПРЕОБРАЗОВАТЕЛЬ ПОКАЗАНИЙ ОБЪЕМНОГО СЧЕТЧНКА В ПОСЛЕДОВАТЕЛЬНЫЙ ДВОИЧНО-ДЕСЯТИЧНЫЙ КОД | 1968 |

|

SU220623A1 |

| Логическое запоминающее устройство | 1972 |

|

SU464017A1 |

| СИСТЕМА ДЛЯ ПЕРЕДАЧИ И ПРИЕМА ИНФОРМАЦИИ КОДОМ ПЕРЕМЕННОЙ ДЛИНЫ | 1996 |

|

RU2123765C1 |

| Датчик случайных кодов | 1973 |

|

SU459773A1 |

| Преобразователь перемещения в код | 1980 |

|

SU886025A1 |

| Аналого-цифровой преобразователь с самокоррекцией в кодах с естественной избыточностью | 1986 |

|

SU1381703A1 |

| Устройство для сортировки двоичных чисел | 1983 |

|

SU1104504A1 |

2

5JX.

.2

Авторы

Даты

1973-01-01—Публикация