Фиг

00

о

Ю

ел

OJ 00

l/.зобретение относится к вычислительной технике, предназначено для преобразования частотно-манипулированного (ЧМ) кода в код без возвращения к нулю (БВН) и может быть использовано в аппаратуре передачи информации,

Целью изобретения является повышение быстродействия работы преобразователя.

Сущность изобретения заключается в сдвиге входной ЧМ-информации, выделение пауз, соответствующих нулевым битам высокого и низкого уровня входной инфор мации, путем тактирования задержанной входной информации срезами импульсов входной информации и инвертированной задержанной входной информации срезами импульсов инвертированной входной информации, и формировании с помощью выделенных пауз кода БВН.

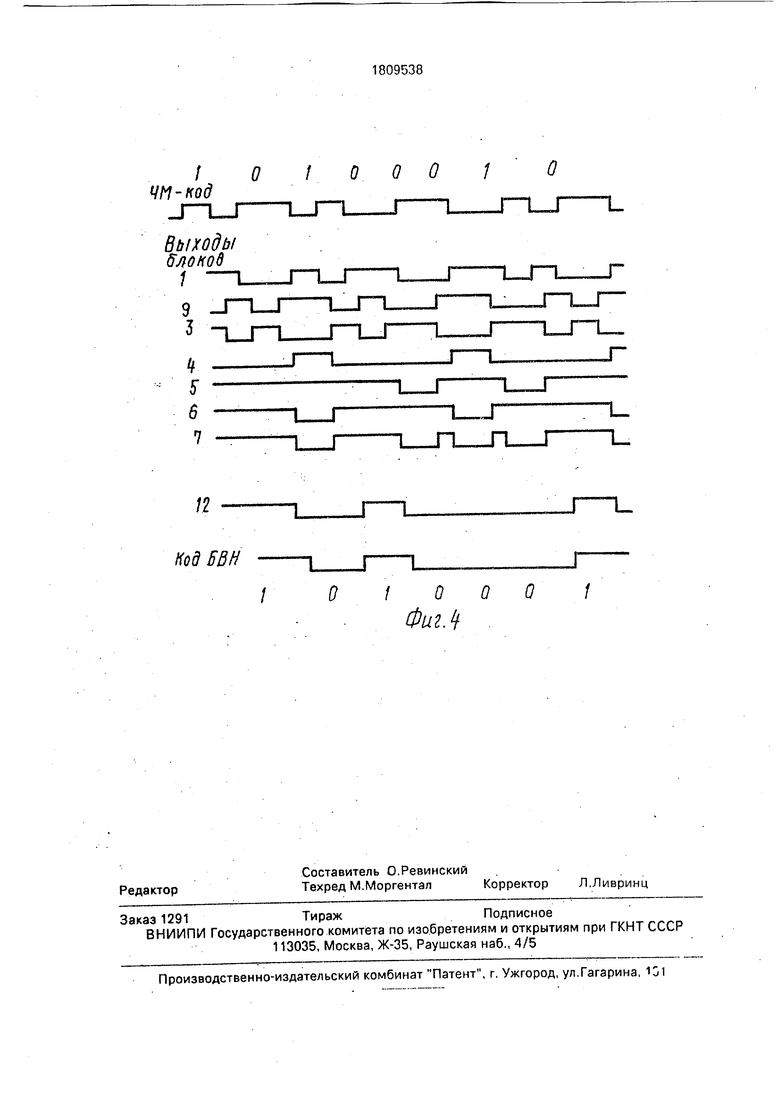

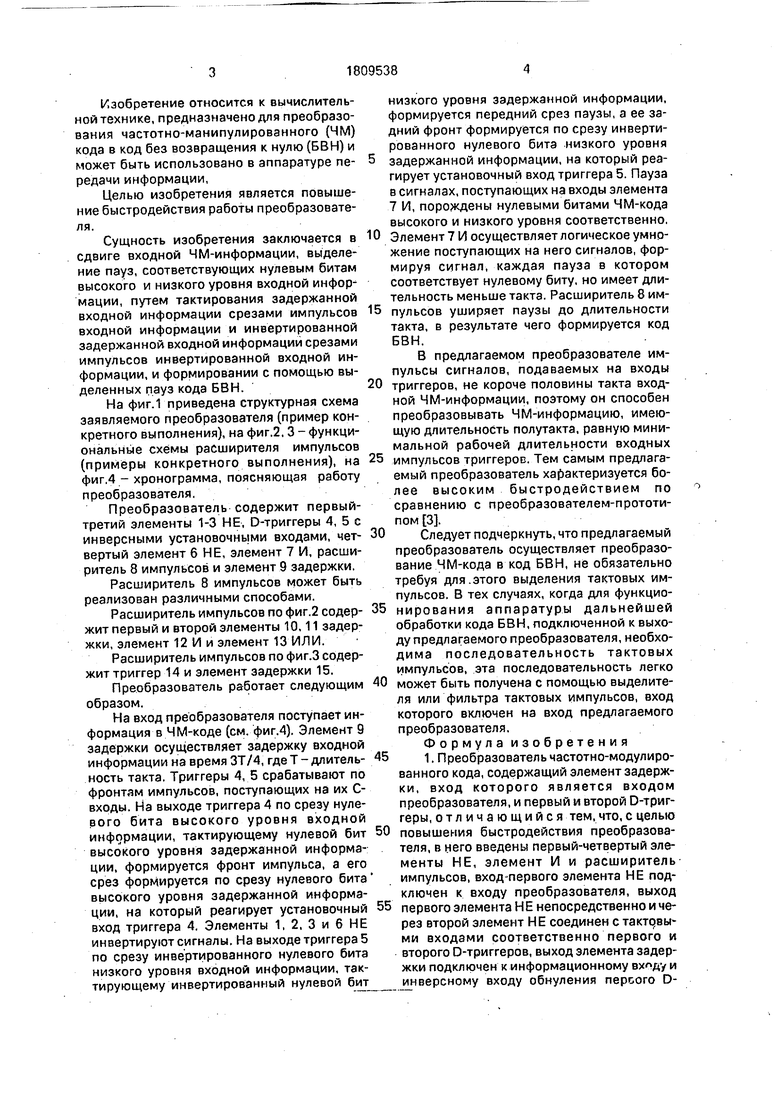

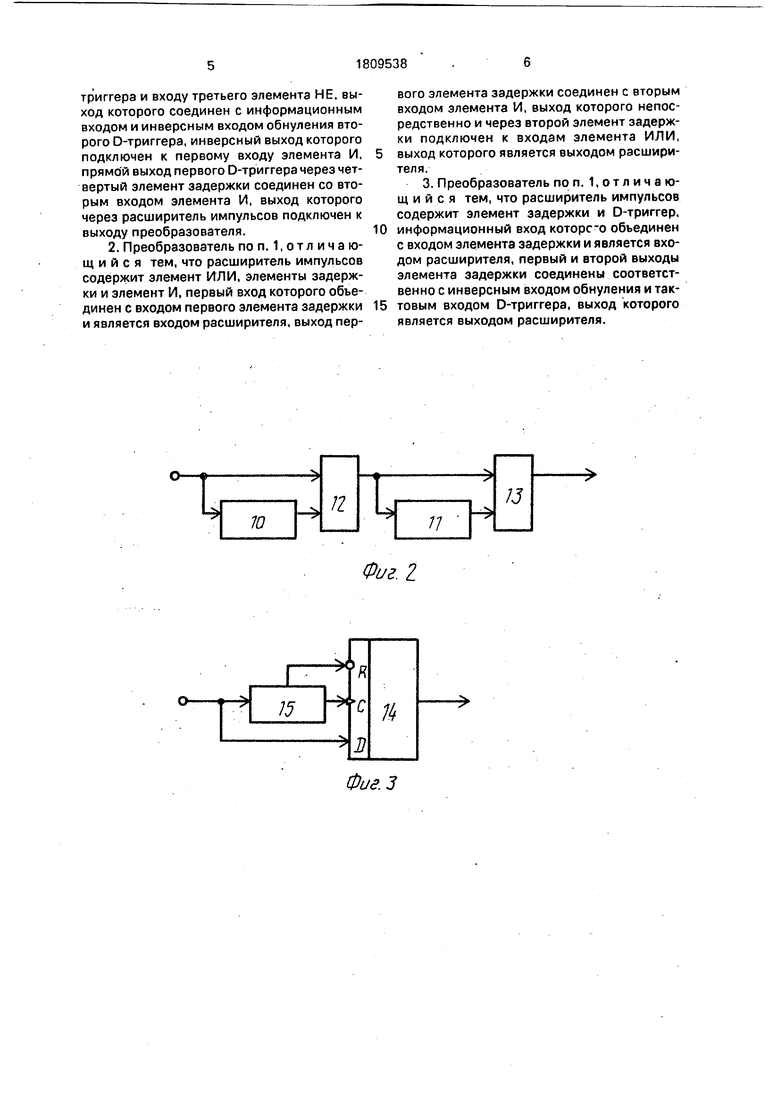

На фиг. 1 приведена структурная схема заявляемого преобразователя (пример конкретного выполнения), на фиг.2, 3 - функциональные схемы расширителя импульсов (примеры конкретного выполнения), на фиг.4 - хронограмма, поясняющая работу преобразователя.

Преобразователь содержит первый- третий элементы 1-3 НЕ, D-триггеры 4, 5 с инверсными установочными входами, четвертый элемент 6 НЕ, элемент 7 И, расширитель 8 импульсов и элемент 9 задержки. Расширитель 8 импульсов может быть реализован различными способами.

Расширитель импульсов по фиг.2 содержит первый и второй элементы 10,11 задержки, элемент 12 И и элемент 13 ИЛИ.

Расширитель импульсов по фиг.З содержит триггер 14 и элемент задержки 15.

Преобразователь работает следующим образом.

На вход преобразователя поступает информация в ЧМ-коде (см. фиг.4). Элемент 9 задержки осуществляет задержку входной информации на время ЗТ/4, где Т - длительность такта. Триггеры 4, 5 срабатывают по фронтам импульсов, поступающих на их С- входы. На выходе триггера 4 по срезу нулевого бита высокого уровня входной информации, тактирующему нулевой бит высокого уровня задержанной информации, формируется фронт импульса, а его срез формируется по срезу нулевого бита высокого уровня задержанной информации, на который реагирует установочный вход триггера 4. Элементы 1, 2, 3 и 6 НЕ инвертируют сигналы. На выходе триггера 5 по срезу инвертированного нулевого бита низкого уровня входной информации, тактирующему инвертированный нулевой бит

низкого уровня задержанной информации, формируется передний срез паузы, а ее задний фронт формируется по срезу инвертированного нулевого бита низкого уровня

задержанной информации, на который реагирует установочный вход триггера 5. Пауза в сигналах, поступающих на входы элемента 7 И, порождены нулевыми битами ЧМ-кода высокого и низкого уровня соответственно.

0 Элемент 7 И осуществляет логическое умножение поступающих на него сигналов, формируя сигнал, каждая пауза в котором соответствует нулевому биту, но имеет длительность меньше такта. Расширитель 8 им5 пульсов уширяет паузы до длительности такта, в результате чего формируется код БВН.

В предлагаемом преобразователе импульсы сигналов, подаваемых на входы

0 триггеров, не короче половины такта входной ЧМ-информации, поэтому он способен преобразовывать ЧМ-информацию, имеющую длительность полутакта, равную минимальной рабочей длительности входных

5 импульсов триггеров. Тем самым предлагаемый преобразователь характеризуется более высоким быстродействием по сравнению с преобразователем-прототипом 3.

0 Следует подчеркнуть, что предлагаемый преобразователь осуществляет преобразование ЧМ-кода в код БВН, не обязательно требуя для.этого выделения тактовых импульсов. В тех случаях, когда для функцио5 нирования аппаратуры дальнейшей обработки кода БВН, подключенной к выходу предлагаемого преобразователя, необходима последовательность тактовых импульсов, эта последовательность легко

0 может быть получена с помощью выделителя или фильтра тактовых импульсов, вход которого включен на вход предлагаемого преобразователя.

Формула изобретения

5 1. Преобразователь частотно-модулированного кода, содержащий элемент задержки, вход которого является входом преобразователя, и первый и второй D-триггеры, отличающийся тем, что, с целью

0 повышения быстродействия преобразователя, в него введены первый-четвертый элементы НЕ, элемент И и расширитель импульсов, вход первого элемента НЕ подключен к входу преобразователя, выход

5 первого элемента НЕ непосредственно и через второй элемент НЕ соединен с тактрвы- ми входами соответственно первого и второго D-триггеров, выход элемента задержки подключен к информационному входу и инверсному входу обнуления первого Dтриггера и входу третьего элемента НЕ, выход которого соединен с информационным входом и инверсным входом обнуления второго D-триггера, инверсный выход которого подключен к первому входу элемента И, прямой выход первого D-триггера через четвертый элемент задержки соединен со вторым входом элемента И, выход которого через расширитель импульсов подключен к выходу преобразователя.

2. Преобразователь по п. 1, о т л и ч а ю- щ и и с я тем, что расширитель импульсов содержит элемент ИЛИ, элементы задержки и элемент И, первый вход которого объединен с входом первого элемента задержки и является входом расширителя, выход пер0

5

вого элемента задержки соединен с вторым входом элемента И, выход которого непосредственно и через второй элемент задержки подключен к входам элемента ИЛИ, выход которого является выходом расширителя.

3. Преобразователь по п. 1, о т л и ч а ю- щ и и с я тем, что расширитель импульсов содержит элемент задержки и D-триггер, информационный вход которс о объединен с входом элемента задержки и является входом расширителя, первый и второй выходы элемента задержки соединены соответственно с инверсным входом обнуления и тактовым входом D-триггера, выход которого является выходом расширителя.

| название | год | авторы | номер документа |

|---|---|---|---|

| Преобразователь частотно-модулированного кода | 1990 |

|

SU1809537A1 |

| Преобразователь биимпульсного кода в код "без возврата к нулю | 1986 |

|

SU1405112A1 |

| Преобразователь кода | 1985 |

|

SU1290533A1 |

| Устройство для контроля ошибок канала цифровой магнитной записи | 1988 |

|

SU1510007A1 |

| Преобразователь кода | 1986 |

|

SU1325707A1 |

| УСТРОЙСТВО ДЛЯ ПЕРЕДАЧИ ДВОИЧНОЙ ИНФОРМАЦИИ | 1991 |

|

RU2022479C1 |

| Преобразователь кода | 1984 |

|

SU1266007A1 |

| "Преобразователь кода Фибоначчи в код "золотой" пропорции" | 1990 |

|

SU1783616A1 |

| Устройство для сдвига с самоконтролем | 1986 |

|

SU1352535A1 |

| СПОСОБ ПРЕОБРАЗОВАНИЯ ДВОИЧНОГО СИГНАЛА В ПЯТИУРОВНЕВЫЙ СИГНАЛ | 2010 |

|

RU2428787C1 |

Изобретение относится к вычислительной технике. Его использование в аппаратуре передачи информации позволяет повысить быстродействие. Преобразователь содержит триггеры 4, 5 и элемент 9 задержки, Благодаря введению элементов НЕ 1, 2, 3, 6, элемента И 7 и расширителя 8 импульсов в импульсы, подаваемые на входы триггеров 4, 5, не короче половины такта входной ЧМ-последовательности. Поэтому полутакт последней может быть равен минимальной рабочей длительности входных импульсов триггеров 4, 5. 2 з.п. ф-лы, 4 ил.

70

И

Фиг.З

ц- 77. -

-

Фиг. 2

.

5

6

7

Код 6В Н

,. ,..,,„„Г I

о / о о

о

Фиг.}

| Электронная техника в автоматике | |||

| Пневматический водоподъемный аппарат-двигатель | 1917 |

|

SU1986A1 |

| Печь для сжигания твердых и жидких нечистот | 1920 |

|

SU17A1 |

| Аппарат для нагревания окружающей его воды | 1920 |

|

SU257A1 |

| Electronic Design, 1978, v.26, № 22, рр.84-91 | |||

| Патент США № 4746898, кл | |||

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Механическая топочная решетка с наклонными частью подвижными, частью неподвижными колосниковыми элементами | 1917 |

|

SU1988A1 |

Авторы

Даты

1993-04-15—Публикация

1990-12-27—Подача