(21)4259857/24-09

(22)10.06о87

(46) 30о07о89о Бюпо № 28

(71)Владимирский политехнический институт

(72)ВоИоКленов

(53)621 „372oS42 (088.8)

(56)Авторское свидетельство СССР № 1403382, кло Н 04 В 3/04, 1986,

(54)АДАПТИВНЫЙ ВЗАИМНО БАЗИСНЫЙ КОРРЕКТОР

(57)Изобретение относитсч к электросвязи и другим областям, связанным

с передачей сигналов по каналам с изменяющимися параметрами, и предназначено для коррекции межсимвольной инте)ференции в системах чи с амплитудной модуляцией Цель изобретения - повьппение скорости и

точности настройки корректора Корректор содержит формирователь 1 исходного сигнального базиса, блок 2 синхронизации корректора, блок 3 настройки, блок 4 регуляторов затуханий, сумматор 5, блок 6 стробиро- ванияа Для достижения цели в блок 3 настройки введены блок анализа размерности, АЦП, блок решения системы линейных уравнений, блок выборки-хранения, ЦАП и формирователь тактовых импульсов. Повышение скорости настройки достигается за счет автоматизации процесса настройки, а повьштение точности настройки - за счет исключения определенных нулевых отсчетов реакции канала на единичный элемент при формировании результирующих сигналов на выходе блока 3 настройки устр-ва„ 3 иЛо

ё

(Л

| название | год | авторы | номер документа |

|---|---|---|---|

| Взаимно-базисный корректор | 1986 |

|

SU1403382A1 |

| Устройство для преобразования сигналов | 1984 |

|

SU1234991A1 |

| МНОГОКАНАЛЬНОЕ УСТРОЙСТВО РАДИОМОНИТОРИНГА | 2012 |

|

RU2523913C2 |

| СПОСОБ И УСТРОЙСТВО ОРТОГОНАЛЬНОГО ЧАСТОТНОГО УПЛОТНЕНИЯ | 2014 |

|

RU2542573C1 |

| СПОСОБ И УСТРОЙСТВО ВОССТАНОВЛЕНИЯ ПЕРЕДАВАЕМОЙ ИНФОРМАЦИИ ПРИ ОРТОГОНАЛЬНОМ ЧАСТОТНОМ УПЛОТНЕНИИ | 2015 |

|

RU2599930C1 |

| Адаптивный корректор межсимвольной интерференции | 1987 |

|

SU1540009A1 |

| Цифровой адаптивный корректор межсимвольных искажений в сигналах данных | 1979 |

|

SU921099A2 |

| Способ автоматической реконструкции фотопортретов из скетчей и система для его осуществления | 2016 |

|

RU2628125C1 |

| Устройство для разложения цифровых сигналов по Уолшо-подобным базисам | 1983 |

|

SU1108461A1 |

| СПОСОБ ФОРМИРОВАНИЯ КАНАЛЬНЫХ СИГНАЛОВ И УСТРОЙСТВО ЕГО РЕАЛИЗУЮЩЕЕ | 2011 |

|

RU2459359C1 |

Изобретение относится к электросвязи и другим областям, связанным с передачей сигналов по каналам с изменяющимися параметрами, и предназначено для коррекции межсимвольной интерференции в системах передачи с амплитудной модуляцией. Цель изобретения - повышение скорости и точности настройки корректора. Корректор содержит формирователь 1 исходного сигнального базиса, блок 2 синхронизации корректора, блок 3 настройки, блок 4 регуляторов затуханий, сумматор 5, блок 6 стробирования. Для достижения цели в блок 3 настройки введены блок анализа размерности, АЦП, блок решения системы линейных уравнений, блок выборки-хранения, ЦАП и формирователь тактовых импульсов. Повышение скорости настройки достигается за счет автоматизации процесса настройки, а повышение точности настройки - за счет исключения определенных нулевых отсчетов реакции канала на единичный элемент при формировании результирующих сигналов на выходе блока 3 настройки устройства. 3 ил.

k|

U

Фиб. 1

3149

Изобретение относится к электросвязи и другим областям, связанным с передачей сигналов по каналам с изменяющимися параметрами, и предназна чено для коррекции межсимвольной интерференции (МСИ) в системах передачи с амплитудной модуляцией.

Цель изобретения - повьгаение скорости и точности настройки корректо- pa.

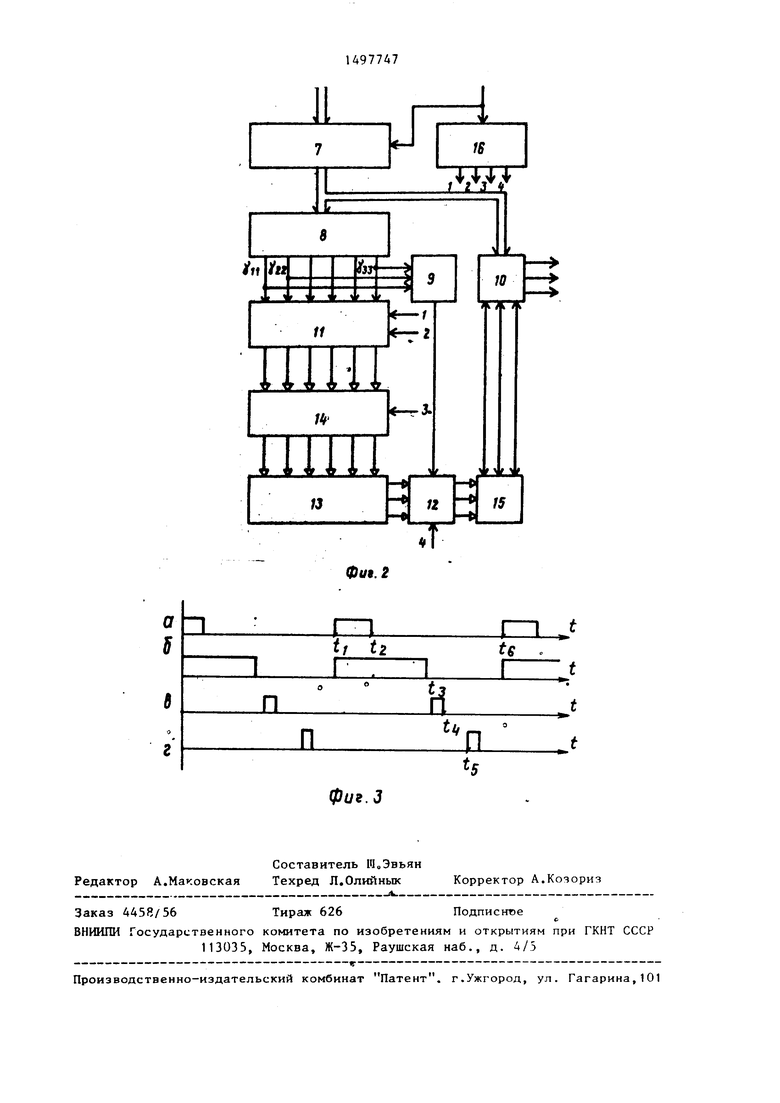

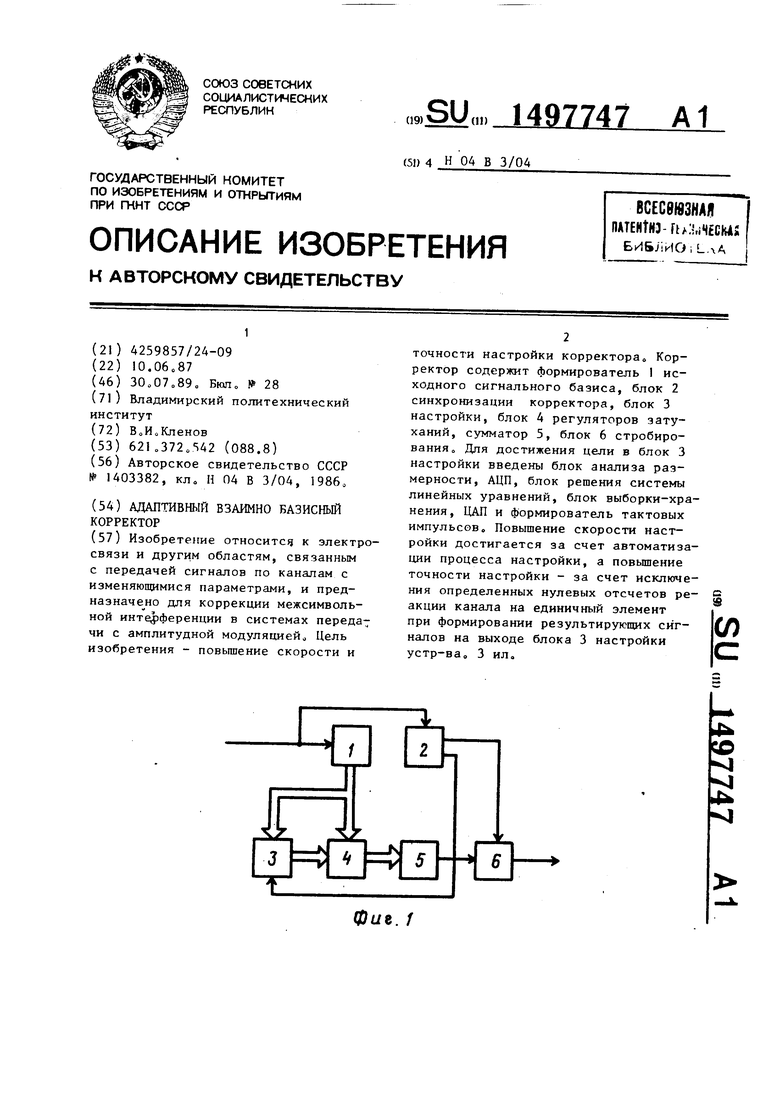

На фиг.1 представлена структурная электрическая схема адаптивного взаимно базисного корректора; на фиг„2 структурная электрическая схема бло- ка настройки; на фиг. 3 - временные диаграммы сигналов на выходе формирователя импульсов

Взаимно базисный корректор содержит формирователь 1 исходного сиг- напьного базиса, блок 2 синхронизации корректора, блок 3 настройки,бло 4 регуляторов затуханий, сумматор 5, блок 6 стробирования.

Блок 3 настройки (фиг,2) содержит блок 7 оценки реакции канала, блок

8формирования матрицы Грама, блок

9анализа размерности, матричный перемножитель 10, аналого-цифровой преобразователь 11, первый блок 12 выборки-хранения, блок 13 решения системы линейных уравнений, второй блок 14 выборки и хранения, цифроаналого- вый преобразователь 15, формирователь 16 актовых импульсов.

Взаимно базисный корректор работает следующим образом

Сигнал с выхода канаЛа связи поступает на вход блока 1 формирования исходного сигнального базиса,состоящего из совокупности аналоговых сек- цирнированных линий задержки.

Сигналы с отводов указанных линий задержки поступают в блок 3 настройки и блок 4 регуляторов затуханий Посредством блока 3 настройки формируются сигналы, изменяющие коэффициенты передачи регуляторов затухания блока 4.

После суммирования сигналов с вы

кодов блока 4 регуляторов затуханий в сумматоре 5 они через блок 6 стро- Оирования поступают на выход в заимнс базисного корректора В блоке 2 синх ронизации корректора осуществляется вьиеление и подстройка синхроколеба- иий, необходимых для работы устройства.

При подаче на вход устройства полезного сигнала на выходах блока 7 оценки реакции канала имеют место оценки отсчетов реакции канала на единичный элемент для текущего состояния канала связи

Эти отсчеты поступают на входы блока 8 формирования матрицы Грама, в котором реализуется операция вычисления матрицы Грама порядка КхК, т.е. матрицы Г А Л, где А - блочная матрица размерности КяК; А h , hj,«. ,h 3 , h a ;,, a ,j , ...a 1 - матрица-строка из элементов исходного базиса а J

В результате вычислений на выходах блока 8 имеют место сигналы,соответствующие значениям элементов матрицы Грама (г), которые после оцифроки в аналого-цифровом преобразователе 1 1 и запоминания в блоке 14 выбор ки-хранения подаются в блок 13 рете- ния

На выходах блока 13 решения устанавливаются кодовые сигналы,соответствующие вектору решения х системы Гх Ъ, которые заносятся в регистры блока 12 выборки-хранения, Щ)и этом Ъ - за(анный вектор правой части системы размерности К, первая компонента которого равна значению амплитуды импульса тестового (рабочего) сигнала, а остальные равны нулю.

Работа цифровой части блока 3 настройки поясняется фиг.З, где приведены эпюры синхросигналов а,б,в,г на выходе формирователя 16 тактовых колебаний, где (, ) - время гашения АЦП 5, (tj-t) - время преобразования АЦП 5 (tg-t) - время вьща- чи данных АЦП 5, (tg-t,) Тц - длительность такта работы цифровой части устройства.

Предположим, что в процессе эксплуатации устройства относительная память канала К может принимать значение б, в, тогда при К 2 блок 9 анализа размерности формирует нулевой потенциал на управляемом входе второго блока 12 выборки-хранения, при этом обнуляется регистр, соот- ветствуюш 1Й третьей компоненте вектора решения Xj (х5(О, Xj(2)... ...Xj(m), где п - размерность кода

Решение системы Гх Ъ дает представление базисного вектора U

взсчмного базиса U А х, который ортогонален к компонентам межсимвольной интерференции и не ортогонален к информационной компоненте сигнала После цифроаналогового преобразования в блоке 15 сигналы, соответствующие компонентам вектора х, подаются на соответствующие входы перемножителя 10, который реализует операцию умножения матрицы на вектор и выходной сигнал U которого есть вектор управления для взаимно базисного корректора.

Повышение скорости настройки достигается за счет автоматизации процесса настройки, а повьипение точности настройки - за счет исключения определенных нулевых отсчетов реакции канала на единичный элемент при формировании результирующих сигналов на выходе блока настройки устройства

Формула изобретения

Адаптивный взаимно-базисный корректор, содержащий последовательно соединенные блок формирования исходного сигнального базиса, блок настройки, блок регуляторов затухания, второй вход которого соединен с выходом блока формирования исходного сигнального базиса, сумматор и блок стробирования, блок синхронизации, вход которого соединен с входом блока формирования исходного сигнального базиса и является входом адаптивного и взаимно базисного.корректора, а первый и второй выходы блока синхронизации подключены соответственно к входам синхронизации блока настройки и блока стробирования, выход кото-

.

10

15

20

97747

рого является выходом адаптивного взаимно базисного корректора, при этом блок настройки состоит из последовательно соединенных блока оценки реакции канала, вход которого является входом блока настройки, и блока формирования матрицы Грама, первого блока выборки-хранения и матричного перемножителя, первый вход которого соединен с выходом блока оценки реакции канала, отличающий- с я тем, что, с целью повышения скорости и точности настройки корректора; в блок настройки введены последовательно соединенные аналого-цифровой преобразователь, вход которого соединен с выходом блока формирования матрицы Грама, второй блок выборки-хранения информации и блок решения системы линейных уравнений, выход которого подключен к входу первого блока выборки-хранения, блок анализа размерности, вход которого подключен к выходу блока формирования матрицы Грана, а выход - к управляющему входу первого блока выборки-хранения, цнфроаналоговый преобразователь, вход которого подключен к выходу первого блока выборки-хранения,а выход - к второму входу матричного переьшожитепя, выход которого является выходом блока настройки, формирователь тактовых импульсов, вход которого является яходом синхронизации блока настройки и сккхровхо- дом блока оценки реакции канала, а выходы подключены к входам синхронизации аналого-цифрового преобразователя, первого и второго блоков выборки-хранения и блока оценки реакции канала.

25

30

35

40

Авторы

Даты

1989-07-30—Публикация

1987-06-10—Подача