(21)4122661/24-09

(22)24.06.86

(46) 15.06.88. Бюл. 22

(71)Владимирский политехнический институт

(72)В. И.Кленов и В.В.Исакевич (53) 621.391.8(088.8)

(56)Тамм Ю.А. Адактивная коррекция сигнала ПД, М,: Связь, 1978, с.116,

с. 53.

(54).ВЗАИМНО-БАЗИСНЫЙ КОРРЕКТОР

(57)Изобретение относится к электросвязи и может использоваться для коррекции межсимвольной интерференции (МСИ) в системах передачи данных с амплитудно-импульсной манипуляцией. Цель изобретения - расширение диапазона корректируемых линейных искажений сигнала. Взаимно-базисный корректор содержит блок 1 формирования исходного сигнального базиса, блок 2

синхронизации, блок 3 настройки, блок 4 регуляторов затухания, сумматор 5 и блок 6 стробиро- вания. Блок 1 состоит из нескольких линий задержки. В блоке 3 настройки в результате определения злементов матрицы Грама и регулировки опорных напряжений формируется вектор управления для блока 4 регуляторов затухания. При последовательном прохождении сигнала через блоки 1, 4, сумматор 5 и блок 6 стробирования на выходе последнего имеют место текущие значения скалярного произведения текущего вектора исходного сигнального базиса с компонентами МСИ и вектора взаимного базиса, который заведомо ортогонален к компонентам МСИ. При . этом на выходе устр-ва формируется информационная сигнальная последовательность с подавлением МСИ. 6 ил.

I

(Л

| название | год | авторы | номер документа |

|---|---|---|---|

| Адаптивный взаимно базисный корректор | 1987 |

|

SU1497747A1 |

| ПРИЕМНИК ЦИФРОВЫХ СИГНАЛОВ | 2010 |

|

RU2423794C1 |

| СПОСОБ ПЕРЕДАЧИ ИНФОРМАЦИИ С ИСПОЛЬЗОВАНИЕМ СХЕМЫ MIMO В ГИПЕРКОМПЛЕКСНОМ ПРОСТРАНСТВЕ | 2023 |

|

RU2809479C1 |

| ЦИФРОВОЙ КОМПЕНСАТОР ПАССИВНЫХ ПОМЕХ | 1994 |

|

RU2087000C1 |

| АДАПТИВНЫЙ ОБРАЩАЮЩИЙ ФИЛЬТР | 1994 |

|

RU2086999C1 |

| Система последовательного финитного управления конечным состоянием линейных стационарных динамических объектов | 1987 |

|

SU1467534A1 |

| УСТРОЙСТВО ДЛЯ ДЕМОДУЛЯЦИИ ДВОИЧНЫХ СИГНАЛОВ | 1991 |

|

RU2065668C1 |

| АДАПТИВНАЯ СИСТЕМА ТЕРМИНАЛЬНОГО УПРАВЛЕНИЯ | 2012 |

|

RU2500009C1 |

| УСТРОЙСТВО ОБНАРУЖЕНИЯ СЛОЖНЫХ ШИРОКОПОЛОСНЫХ ЧАСТОТНО-МОДУЛИРОВАННЫХ СИГНАЛОВ С ФИЛЬТРАЦИЕЙ В МАСШТАБНО-ВРЕМЕННОЙ ОБЛАСТИ НА ОСНОВЕ ДИСКРЕТНОГО ВЕЙВЛЕТ-ПРЕОБРАЗОВАНИЯ | 2010 |

|

RU2439601C1 |

| Анализатор спектра фурье | 1979 |

|

SU800994A1 |

00

со

00

ю

дзие. 1

15

Изобретение относится к электросвязи и может быть использовано для коррекции межсимвольной интерференции (МСИ) в системах передач данных- с амплитудно-импульсной манипуляцией,

Цель изобретения - расширение диапазона корректируемых линейных искажений сигнаяа.

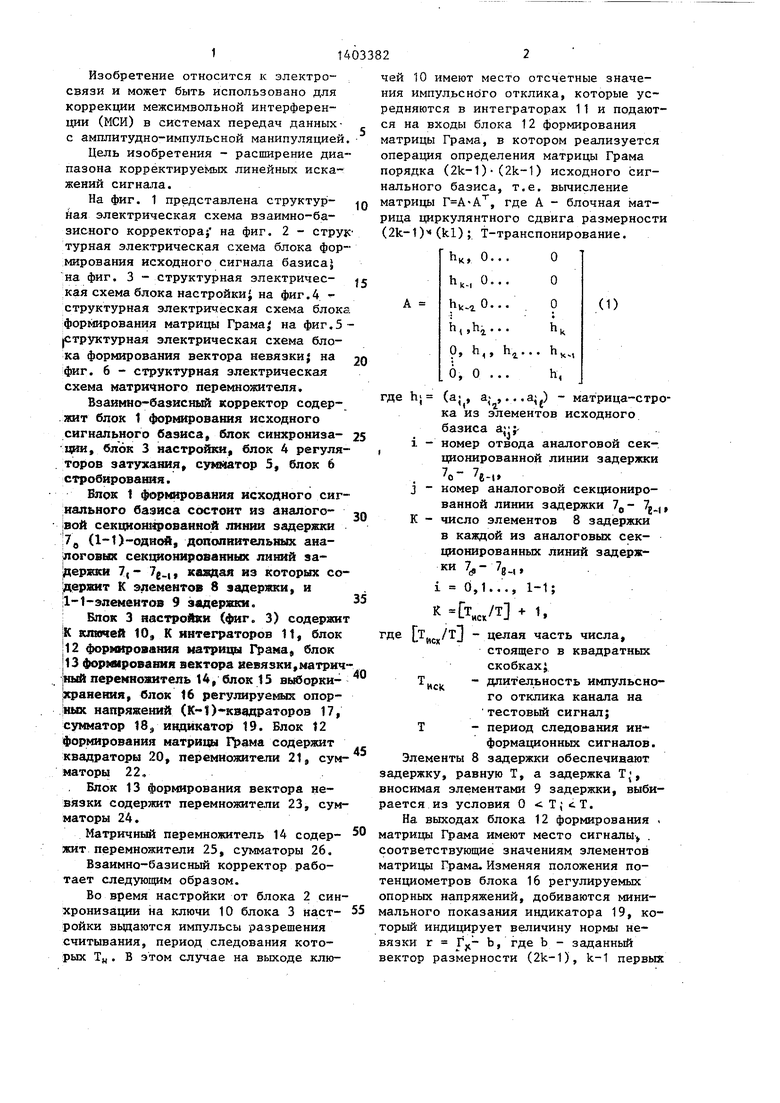

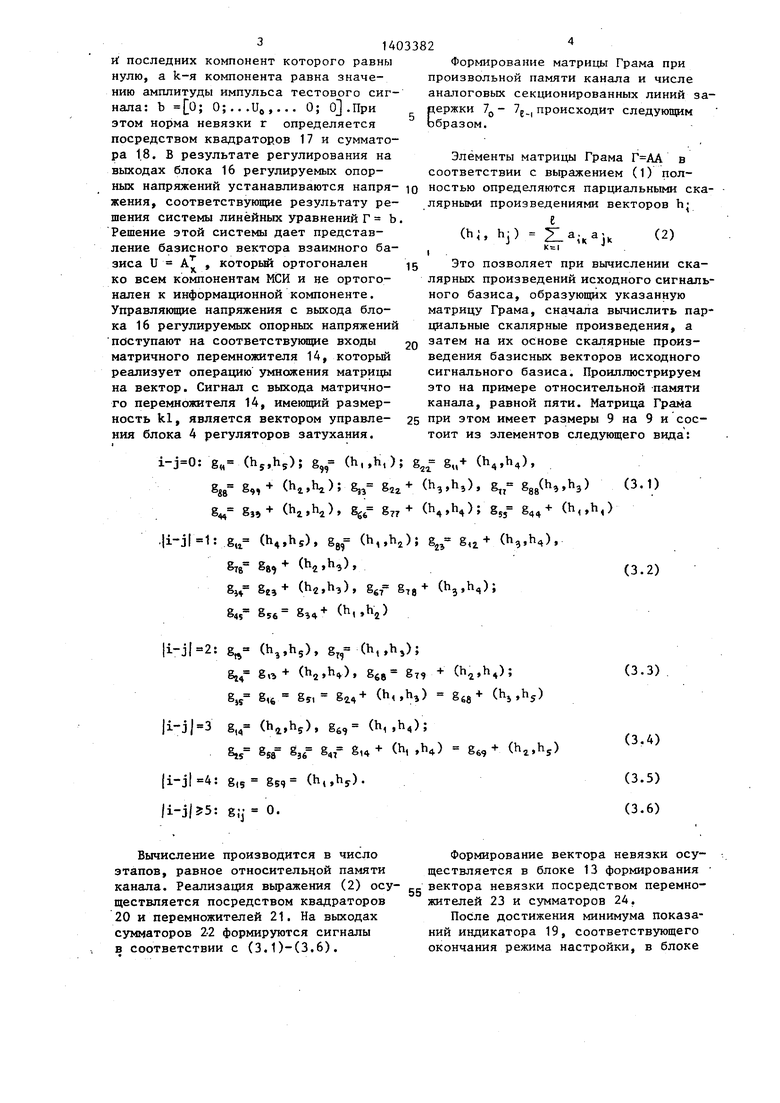

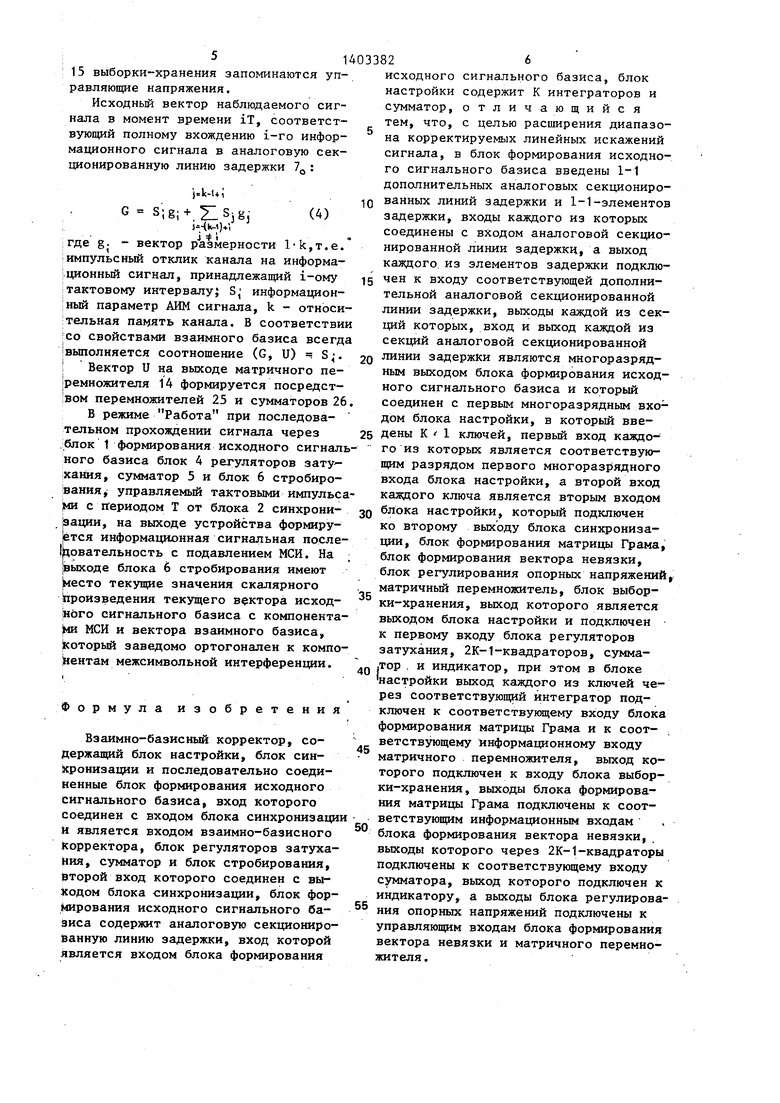

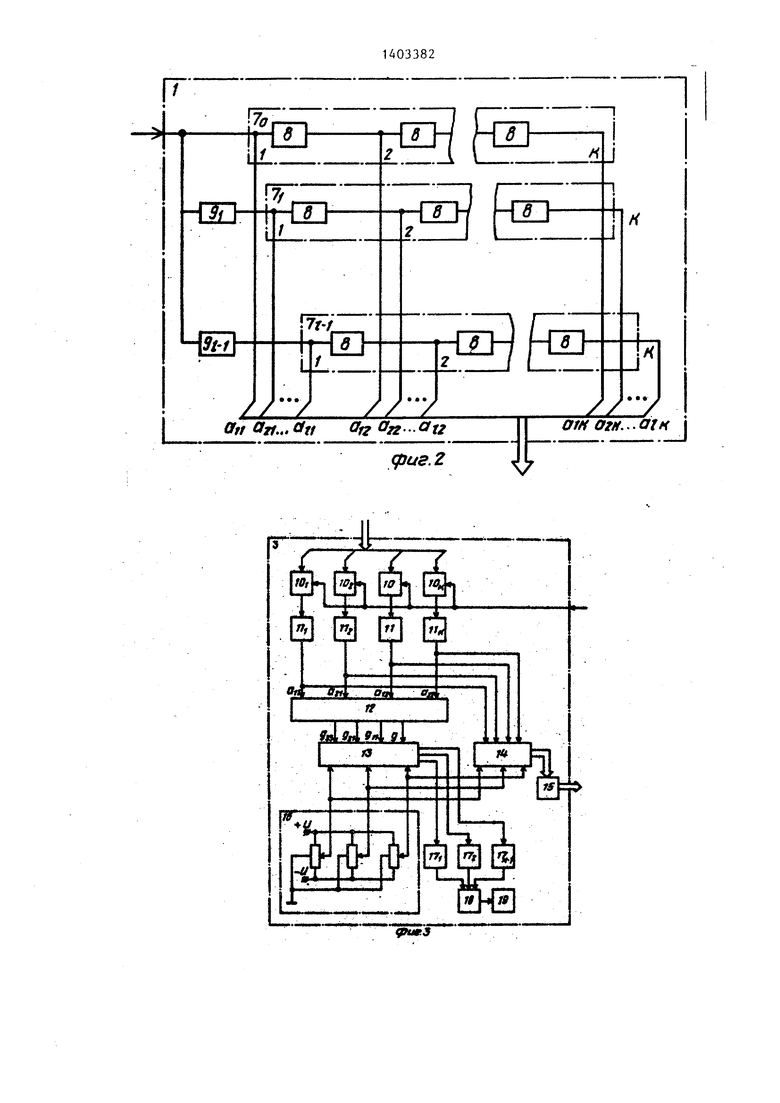

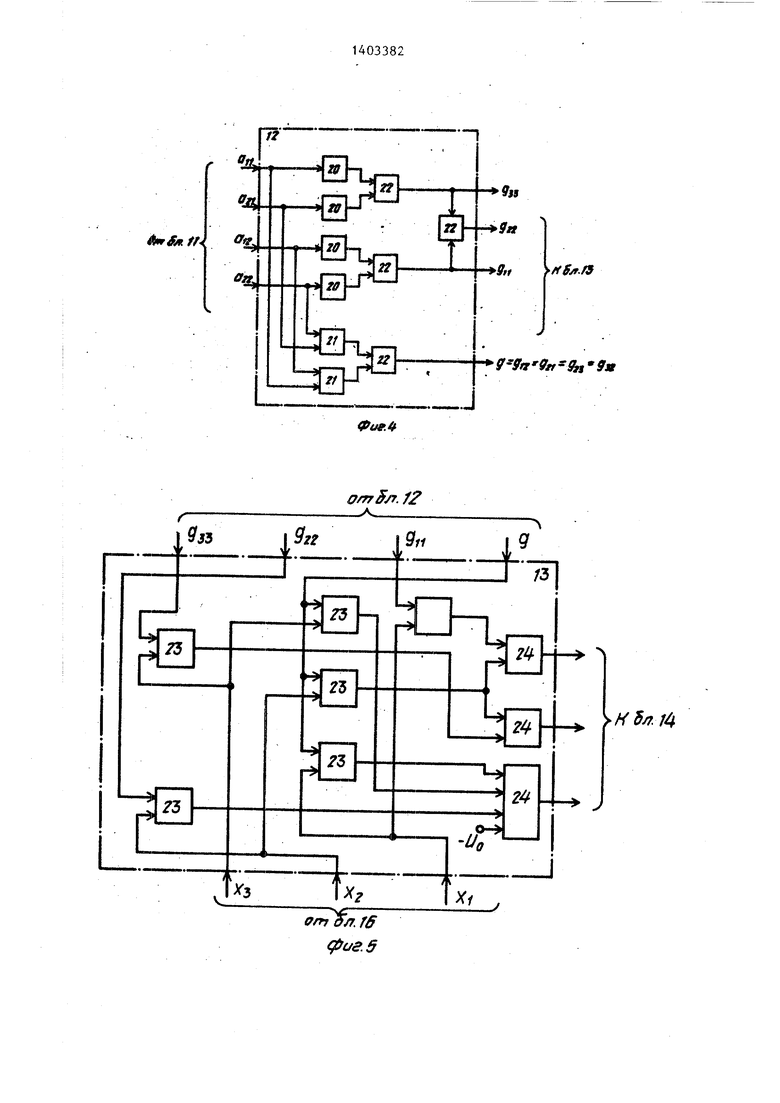

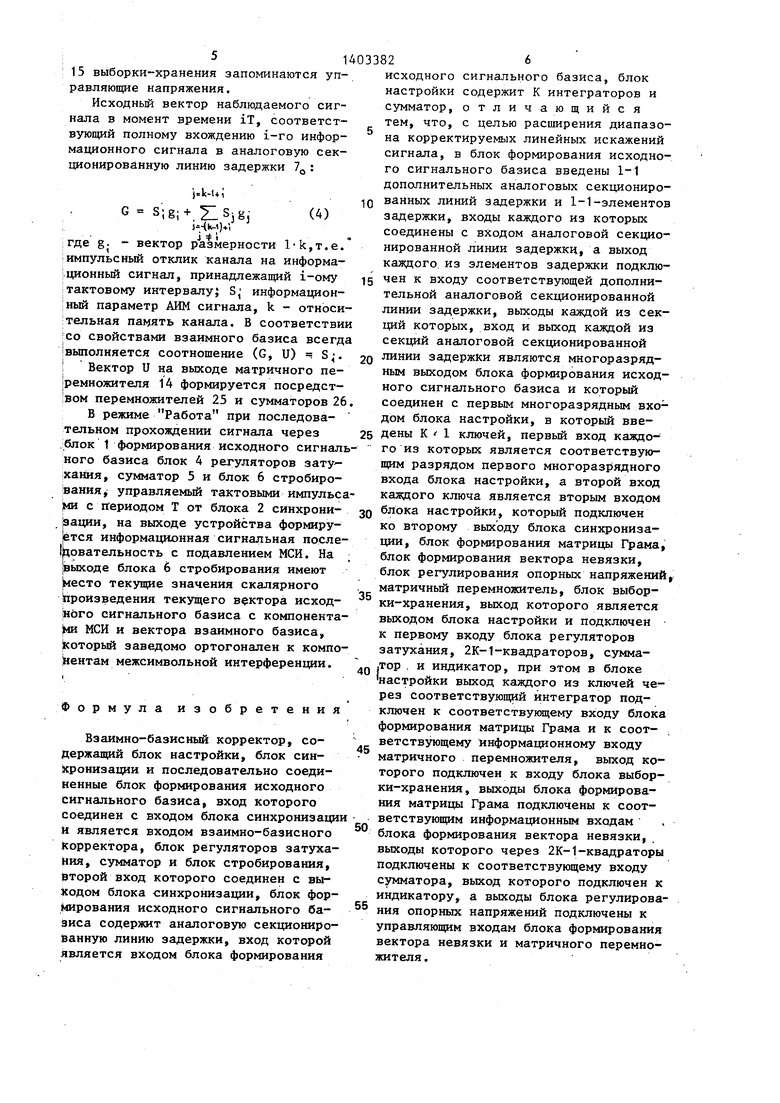

На фиг. 1 представлена структур- Q йая электрическая схема взаимно-базисного корректора} на фиг, 2 - струк турная электрическая схема блока формирования исходного сигнала базисаJ на фиг. 3 - структурная электрическая схема блока настройки на фиг.4 структурная электрическая схема блока формирования матрицы Грама на фиг.5 - Структурная электрическая схема блока формирования вектора невязки; на 20 фиг. 6 - структурная электрическая схема матричного перемножителя.

Взаимно-базисный корректор содер- жит блок 1 формирования исходного сигнального базиса, блок синхрониза- 25 ции, блок 3 настройки, блок 4 регуля- торов затухания 5, блок 6 стробирования.

Блок 1 формирования исходного сигнального базиса состоит из аналого- |вой секционированной линии задержки 7 (1-1)-однай, дополнительных ана- |логовых сек1; ;Иониро8анных линий за- ержки 7, - 7g,, каяяая из которых со- |держит К элементов 8 задержки, и |1-1-элементов 9 задержки. : Блок 3 настройки (фиг. 3) содержит |К ялючей 10, К интеграторов 11, блок |12 формирования катрищл Грама, блок |l3 фl p вlpoвaния вектора иевязки матрич- |Ный перемножйтель 14, блок 15 выборки- Охранения, блок 16 регулируемых опор- ;ных напряжений (К-)- -кгадраторов 17, сумматор 18,, индикатор 19. Блок 12 формирования матрицы содержит квадраторы 20, перемнояа{тели 21, сумматоры 22,

Блок 13 формирования вектора невязки содержит перемножители 23, сумматоры 24.

Матричный перемножитель 14 содержит перемнозштели 25, сумматоры 26.

Взаимно-базисный корректор работает следующим образом.

Во время настройки от блока 2 синхронизации на ключи 10 блока 3 наст- 55 ройки вьщаются импульсы разрешения считывания, период следования которых TH. Б этом случае на выходе клю30

35

40

45

50

чей 10 имеют место отсчетные значения импульсного отклика, которые усредняются в интеграторах 11 и подаются на входы блока 12 формирования матрицы Грама, в котором реализуется операция определения матрицы Грама порядка (2k-1)(2k-1) исходного сигнального базиса, т.е. вычисление матрицы , где А - блочная матрица циркулянтного сдвига размерности (2k-1) (kl) ; t-транспонирование.

5

Q 0

5

5

0

5

0

5

0

А

h,,ha О, h

6, О где hj (а

Ьк О- h,, 0... hfc.aO...

1

О О

О

ч

Ьк.

h,

(1)

1 J К , а;,...а;р - матрица-строка из элементов исходного базиса aj jномер отвода аналоговой секционированной линии задержки

7о- 7е-,,

номер аналоговой секционированной линии задержки 7 - 7.,, число элементов 8 задержки в каждой из аналоговых секционированных линий задержки 7g.,,

i 0,1..., 1-1;

К т„ск/т - 1.

где Гт /Т I - целая часть числа,

исх .

стоящего в квадратных скобкахi

длительность импульсного отклика канала на тестовый сигнал; Т - период следования информационных сигналов. Элементы 8 задержки обеспечивают задержку, равную Т, а задержка Т;, вносимая элементами 9 задержки, выбирается из условия О Т; сТ.

На выходах блока 12 формирования . матрицы Грама имеют место сигналы , . соответствующие значениям элементов матрицы Грама, Изменяя положения потенциометров блока 16 регулируемых опорных напряжений, добиваются минимального показания индикатора 19, который: индицирует величину нормы невязки г b, где b - заданньй вектор размерности (2k-1), k-1 первых

иск

140

rf последних компонент которого равны нулю, а k-я компонента равна значению амплитуды импульса тестового сигнала: b 0; 0;...Uo,... 0; о .При этом норма невязки г определяется посредством квадраторов 17 и сумматора 1,8. В результате регулирования на выходах блока 16 регулируемых опор

ных напряжений устанавливаются напря- ю костью определяются парциальными скажения, соответствующие результату решения системы линейных уравнений Г b Решение этой системы дает представление базисного вектора взаимного базиса и , которьй ортогонален ко всем компонентам МСИ и не ортогонален к информационной компоненте. Управляющие напряжения с выхода блока 16 регулируемых опорных напряжений поступают на соответствукицие входы матричного перемножителя 14, который реализует операцию умножения матрицы на вектор. Сигнал с выхода матричного перемножителя 14, имеющий размерность kl, является вектором управления блока 4 регуляторов затухания.

(3.2)

§„ (h5,h5); g,, (h,,h,); g g,,+ (h4,h4),

849 g,,+ (h,l4) (h,,hj), g, ggg(h,,h3)(3.1)

g,, (hi,h2), gg, (Ь,Ц); g, g4,+ (h,,h,)

|i-Jl 1: g,i (h4,hs), gg, (h,,h2); g g, + (,У,

678 8в9 (Ц,Ц),

Sir (Ьг,Ьэ), gg (Ьз,Ь);

ё45 g56 (h,,h2)

|i-j| 2: g (h,,h5), g,, (h,,h5);

gi4 g,+ (ha,), g68 &-,) + (h,h);

e« 2я SM (,) gjg+ (hj,h5) ji-Jl 3 g,4 (h.hf), g6, (h, ,h);

8i5 8s8 ёз, gi4 - ( 4) §69- (hj.hy) ( 8(5 8s9 (h,,hy). li-j| 5: gi- 0.

(3.3)

(3.4)

(3.5) (3.6)

Вычисление производится в число этапов, равное относительной памяти канала. Реализация вьфажения (2) осуществляется посредством квадраторов 20 и перемножителей 21. На выходах сумматоров 2-2 формируются сигналы в соответствии с (3.1)-(3.6).

Формирование матрицы Грама при произвольной памяти канала и числе аналоговых секционированных линий задержки 7д - 7j,| происходит следующим образом.

Элементы матрицы Грама в соответствии с выражением (1) поллярными произведениями векторов hе

(hj, ьр 21,4

К |

(2)

Это позволяет при вычислении скалярных произведений исходного сигнального базиса, образующих указанную матрицу Грама, сначала вычислить парциальные скалярные произведения, а

затем на их основе скалярные произведения базисных векторов исходного сигнального базиса. Проиллюстрируем это на примере относительной памяти канала, равной пяти. Матрица Грама

при этом имеет размеры 9 на 9 и состоит из элементов следующего вида:

(3.2)

(3.3)

(3.4)

(3.5) (3.6)

Формирование вектора невязки осуществляется в блоке 13 формирования вектора невязки посредством перемножителей 23 и сумматоров 24.

ПоЬле достижения минимума показаний индикатора 19, соответствующего окончания режима настройки, в блоке

15 выборки-хранения запоминаются управляющие напряжения,

Исходньй вектор наблюдаемого сигнала в момент времени 1Т, соответствующий полному вхождению i-ro информационного сигнала в аналоговую секционированную линию задержки

i«k-t+;

G SjgjH- ZlSjgj

(4)

)ЦМ)+|

где g. - вектор размерности l k,T.e. ;импульсный отклик канала на информа- |ционный сигнал, принадлежащий i-ому I тактовому интервалу; S, информацион- |ный параметр АИМ сигнала, k - относи- Iтельная канала. В соответствии со свойствами взаимного базиса всегда |выполняется соотношение (G, U) S. Вектор и на выходе матричного пе- |ремножителя 14 формируется посредст- |Вом перемножителей 25 и сумматоров 26.

В режиме Работа при последовательном прохождении сигнала через блок 1 формирования исходного сигнального базиса блок 4 регуляторов зату хания, сумматор 5 и блок 6 стробиро- вания управляемый тактовыми импульса- |ми с периодом Т от блока 2 синхрони- |эации, на выходе устройства формиру- ется информационная сигнальная последовательность с подавлением МСИ. На |выходе блока 6 стробирования имеют текущие значения скалярного Ьроизведения текущего вектора исход- Ного сигнального базиса с компонента- МСИ и вектора взаимного базиса, |который заведомо ортогонален к компо- |нентам межсимвольной интерференции.

Формула изобретения

Взаимно-базисный корректор, содержащий блок настройки, блок син- ронизацин и последовательно соединенные блок формирования исходного сигнального базиса, вход которого соединен с входом блока синхронизаци И является входом взаимно-базисного Корректора, блок регуляторов затухания, сумматор и блок стробирования, второй вход которого соединен с выходом блока :инхронизации, блок формирования исходного сигнального базиса содержит аналоговую секционированную линию задержки, вход которой Является входом блока формирования

исходного сигнального базиса, блок настройки содержит К интеграторов и сумматор, отличающийся тем, что, с целью расширения диапазона корректируемых линейных искажений сигнала, в блок формирования исходного сигнального базиса введены 1-1 дополнительных аналоговых секциониро- ванньк линий задержки и 1-1-элементов задержки, входы каждого из которых соединены с входом аналоговой секционированной линии задержки, а выход каждого, из элементов задержки подклю5 чек к входу соответствующей дополнительной аналоговой секционированной линии задержки, вьпсоды каждой из секций которых, вход и выход каждой из секций аналоговой секционированной

0 линии задержки являются многоразрядным выходом блока формирования исходного сигнального базиса и который соединен с первым многоразрядным входом блока настройки, в который вве5 дены К 1 ключей, первый вход каждо- го из которых является соответствую-- щим разрядом первого многоразрядного входа блока настройки, а второй вход каждого ключа является вторым входом блока настройки, который подключен ко второму выходу блока синхронизации, блок формирования матрицы Грама, блок формирования вектора невязки, блок регулирования опорных напряжений, матричный перемножитель, блок выборки-хранения, выход которого является выходом блока настройки и подключен к первому вкоду блока регуляторов затухания, 2К-1-квадраторов, сумма- ,тор . и индикатор, при этом в блоке настройки выход каждого из ключей через соответствующий интегратор подключен к соответствующему входу блока формирования матрицы Грама и к соот- , ветствующему информационному входу матричного перемножителя, выход которого подключен к входу блока выборки-хранения, выходы блока формирования матрицы Грама подключены к соответствующим информационным входам блока формирования вектора невязки, выходы которого через 2К-1-квадраторы подключены к соответствующему входу сумматора, выход которого подключен к индикатору, а выходы блока регулирова ния опорных напряжений подключены к управляющим входам блока формирования вектора невязки и матричного перемножителя .

0

5

0

5

0

Г

4-t7о

7Г-/

LL..

// У

Oft On... Cftf ОГ2

(pus.Z

tr

П

1

к

//У

IOfff O2H,.. OtH

LJ

Л oj

/Kff4

ff

3-b

A7

LflTU

:s

Sa

,t

ftS.fS

U

UP

9 9fg 9« 9n 9

am 5л. 2 j

Hb/7.1

от S/j. fG фиг. 6

Н5л.15

. .J

Авторы

Даты

1988-06-15—Публикация

1986-06-24—Подача