Изобретение относится к вычислител ной технике и может быть использовано для построения устройств цифровой фильтрации, помехоустойчивого кодирования и сокращения избыточности, основанных на алгоритме быстрого раз ложения по Уолшо-подобному базису цифровых сигналов, заданных vniji..., m отсчетами, где m,- - четные натуральные числа. Известно устройство, выполняющее разложение цифровых сигналов, задаиньк отсчетами, по базисной сист ме функций Уолша. Это устройство реа лизует разложение цифрового сигнала по системе функции Уолша с прореживанием по времени. Устройство содержит блок управления и п последовательно соединенных каналов каждый из которых содержит два блока задерж ки, арифметический блок и переключатель управляющий вход арифметическо го блока и переключателя подключены к соответствующему выходу блока управления, а вход устройства подключен к входу первого блока задержки и к первому входу арифметического блока первого канала. Вход первого блока задержки и первый вход арифметического блока каждого канала подключен к выходу предьдущего канала. Первый выход арифметического блока, на который поступают суммарные сигналы от входа и выхода первого блока задержки, через первый информационный вход переключателя подключен к выходу канала, а второй выход арифме тического блока, на который поступают разностные сигналы, подключен к выходу канала через второй блок задержки и второй информационный вход переключателя канала. Переключатель чередует суммарный и разностный сигнал с временным интервалом, равным времени задержки в блоках задержки канала. Блоки задержки каждого после дующего канала задерживают сигнал на время вдвое большее, чем блоки задержки предыдущего канала. Блоки задержки в первом канале задерживают сигнал на один такт. Выход последнего п-го, канала подключен к выходу всего устройства СП. Недостатком этого устройства является невозможность его применения для разложения цифровых сигналов, заданных не Н 2 отсчетами. 1 612 Наиболее близким к IIpt.дJIaг,()мy является устройство, содержаще;е блок управления и п последовательно сокдиненных каналов, каждый из которых содержит два блока задержки и арифметический блок, управляющий вход которого подключен к соответствующему выходу блока управления, а выход арифметического блока каждого канала, кроме последнего, подключен ко входу первого блока задержки и первому входу арифметического блока последующего канала, выход первого блока задержки в каждом канале подключен ко второму входу арифметического блока и через второй блок задержки к третьему входу арифметического блока, вход устройства подключен к входу первого блока задержки и к первому входу арифметического блока первого канала, выход арифметического блока последнего канала подключен к выходу устройства 2. Недостатком известного устройства является невозможность его использования в задачах разложения сигналов, когда число отсчетов сигнала отлично от степени двойки. Цель изобретения - расширение области применения за счет обработки сигналов, заданных , . .. ,mt; отсчетами, где т - четные натуральные числа. Поставленная цель достигается тем. что в устройстве для разложения циф ровых сигналов по Уолшо-подобным базисам, содержащем К+1 вычислительных оков и блок синхронизации, г-я (,О группа выходов которого соединена с группой управляющих входов -го вычислительного блока, причем информационный выход i-ro (, Ы-1) вычислительного блока подключен к информационному входу (t + 1)-ro вычислительного блока, информационный вход г-го () вычислительного блока является информационным входом устройства, а информационный выход C--ro вычислительного блока является информационным выходом устройства, г-ый (i 1,(s) вычислительный блок содержит 2т;арифметических узлов, 2т;-1 сдвиговых регистров с разрядностью N-t- IT (где п - разрядность операндов) каждый И выходной коммутатор, причем 3-и ( 1,2TViO арифметический узел содержит узел памяти, сумматорвычитатель, сдвиговый регистр с рая31108461рядностью At-/ П и коммутатор, первый выход которого подключен к первому входу сумматора-вычитателя, выход которого соединен с информационным входом сдвигового регистра, вы- 5 ходы разрядов которого соответственно подключены ко входам коммутатора, информационный выход узла памяти соединен с информационным входом узла памяти и управляющим входом суммато- Ю ра-вычитателя,второй выход коммутатора первого арифметического узла соединен с первым входом выходного коммутатора, з-й (2,) вход которого подключен к информационному выходу 15 ()го сдвигового регистра, информационный вход которого соединен со вторым выходом коммутатора -i -го арифметического узла, вторые входы сумматоров-вычитателей 2 Ш-; арифметичес- 20 ких узлов объединены и являются информационным входом т.-го вычислительного блока, управляющие входы узлов памяти 2 арифметических узлов объединены и являются первым управляющим 25 входом группы г-го вычислительного блока, управляющие входы коммутаторов арифметических узлов объединены и являются вторым управляющим входом группы i/-ro вычислительного 39 блока, управляющий вход выходного коммутатора является третьим управляющим входом группы i-ro вычислительного блока, тактовый вход д-го (j 1,2vvij-1) сдвигового регистра являет- ,, ся (4+3)-м управляющим входом группы г-го вычислительного блока, а выход выходного коммутатора является информационным выходом i-ro вычислительного блока.40 Устройство рассчитано на разложение цифрового сигнала по Уолшо-подобной системе с прореживанием по времени. Устройство предназначено для вы- j полнения матричного преобразования

(1)

,

где f - вектор размерности .vn,.. . ,iO()(ti F - его спектр размерности VIк; Нус. - квадратная ортогональная матрица порядка Ы, строки которой являются Уолшо-подобными функциями. Матрица строится по рекурентной формуле

Lj г 1 и Г 1 4 ,Le.гд ма «1 ри ка + 1 гд lrv цы лов

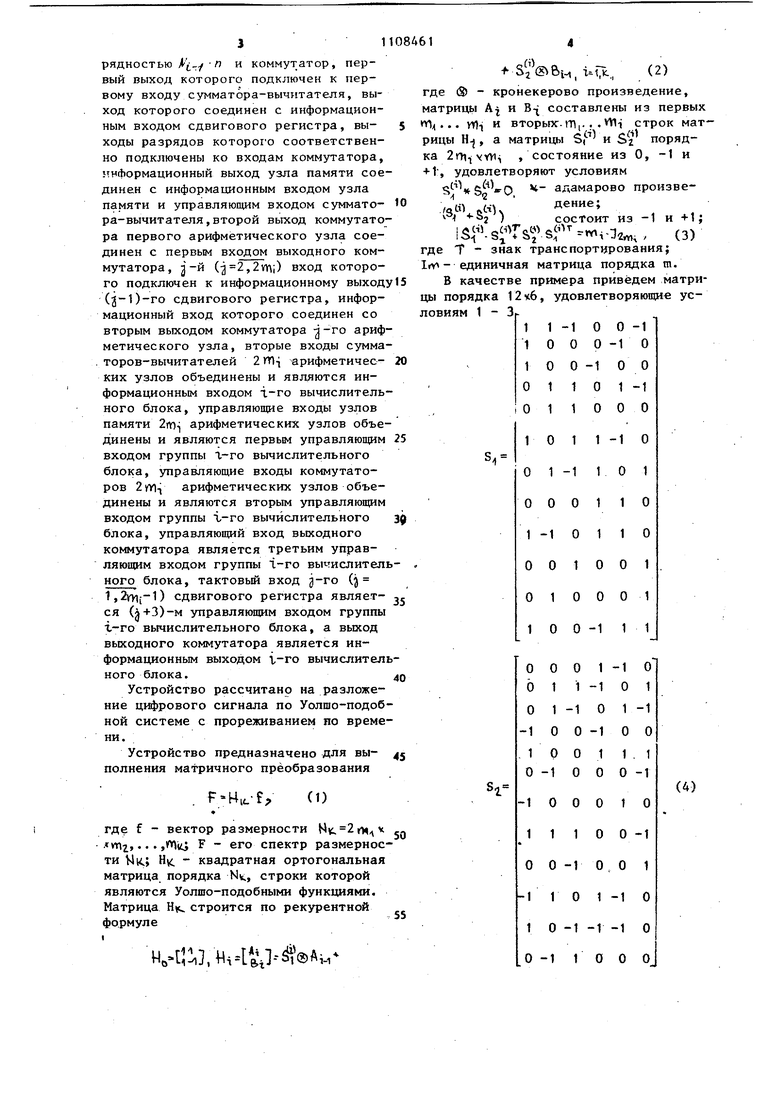

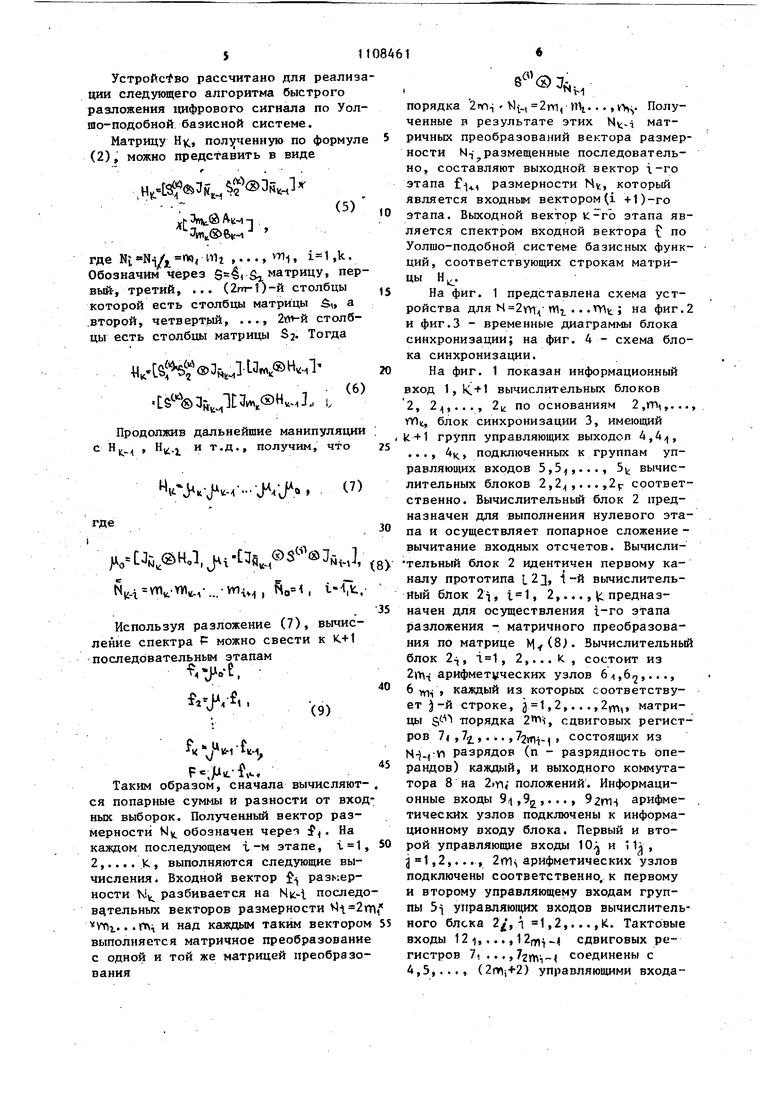

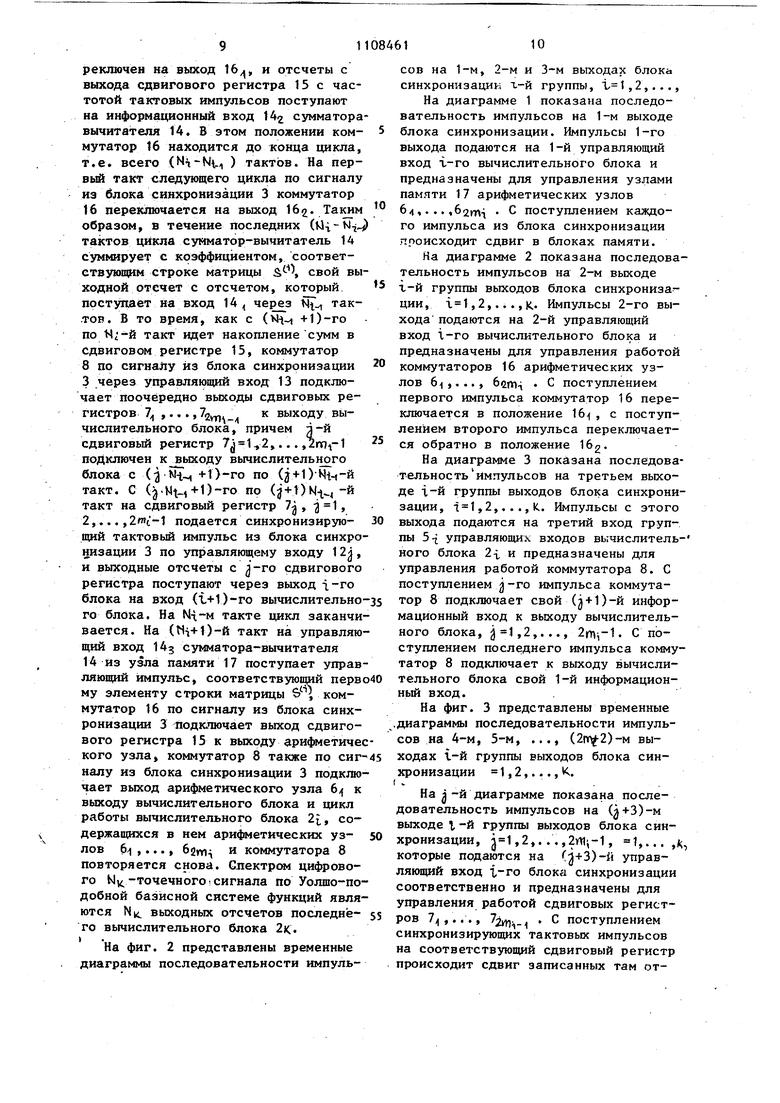

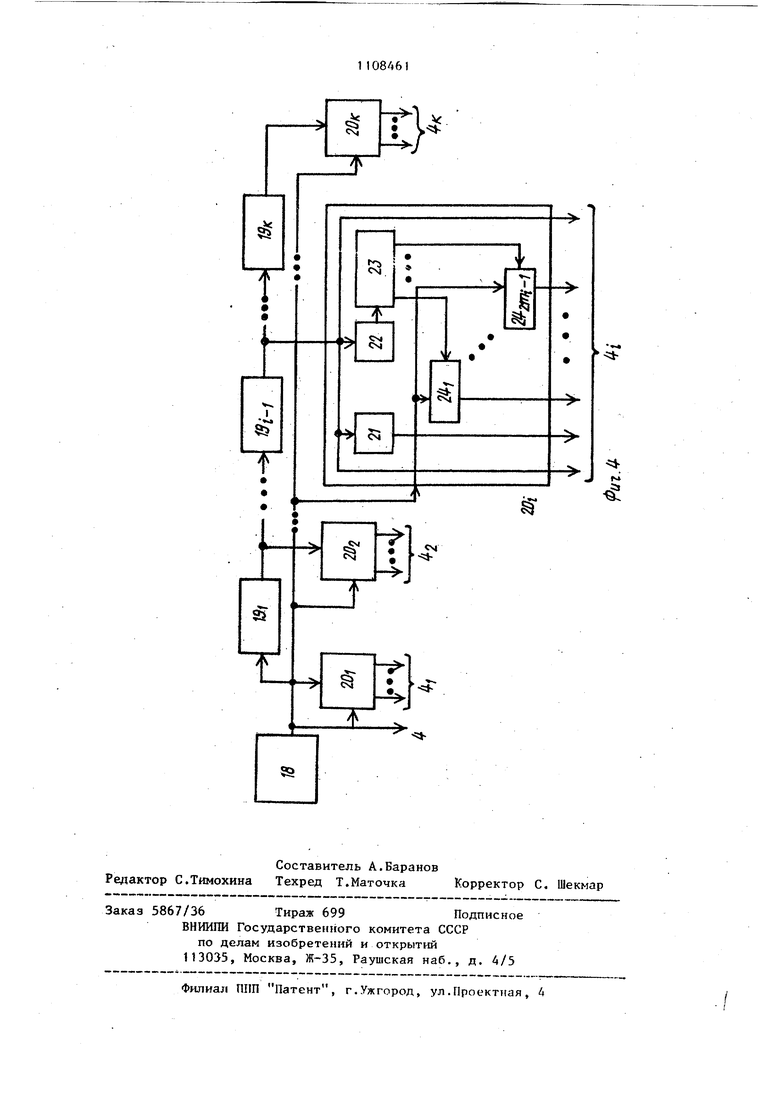

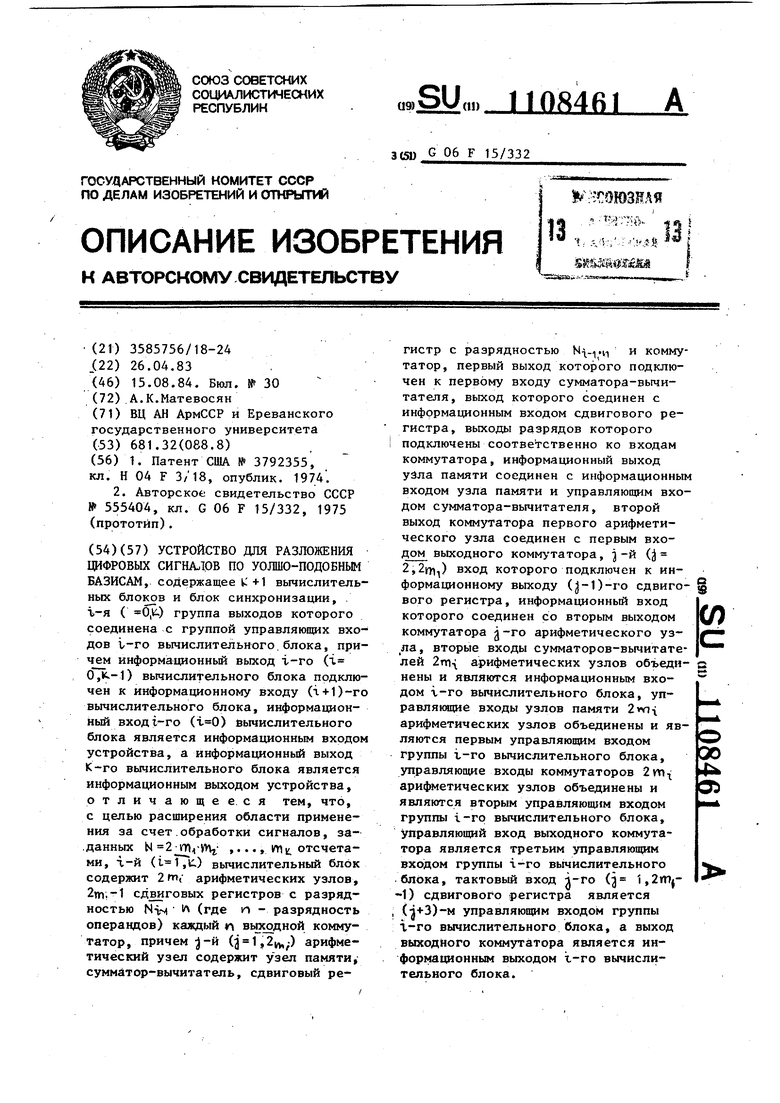

(4) ,гм7 .(2) ® - кронекерово произведение, иць А и В-| составлены из первых . Yfli и вторьпс.П,. . . vVl-i строк матH-J, а матри1№1 ( и Sz порядrh 4vvi , состояние из О, -1 и удовлетворяют условиям 1 tW. .s ч- адамарово произве .ti«K Д , -i-bj ) состоит из -1 и -И; i jCii ,,,W (iU . -. , 10 S Jim / (3) т - знак транспортирования; единичная матрица порядка т. качестве примера приведем матрирядка 12 6, удовлетворяющие усм 1 - Зг YcTpoftcfBO рассчитано для реализ ции следующего алгоритма быстрого разложения цифрового сигнала по Уол шо-подобной базисной системе. Матрицу HK., полученную по формул (2), можно представить в виде ,H,,V. „h /VKW| -, где NI «НVi Мг ,..., , Л V Обозначим через 3-4г5г Р ВЫЙ-, третий, ... (2пг-1)-и столбцы которой есть столбцы матрицы Зо а .второй, четвертой, ..., столбцы есть столбцы матрицы 32- Тогда .., Продолжив дальнейшие манипуляции t-i получим, что и т.д. .-J.M-J //. 7 .®Ha,j rC:is,,.,V , оИ. t-Ct .. Используя разложение (7), вычисление спектра Р можно свести к tC+1 последовательным этапам .- f.J.-ft . . F-.,c. Таким образом, сначала вычисляют ся попарные суммы и разности от вхо ных выборок. Полученный вектор размерности М(( обозначен череч f. На каждом последующем i-м этапе, 2,.... К, выполняются следующие вычисления. Входной вектор f размерности Му, разбивается на Nic-l поспед вдтельньк векторов размерности куМг.. .т, и над каждым таким векторо выполняется матричное преобразовани с одной и той же матрицей преобразо вания порядка 2in-i V)t-, 2ni, ПЧ- VHs Полученные в результате этих Nv:-i матричных преобразований вектора размерности N-, размещенные последовательно, составляют выходной вектор г-го этапа f, размерности Ne, которьй является входным вектором(i +1)-го этапа. Выходной вектор к-го этапа является спектром входной вектора по Уолшо-подобной системе базисных функций, соответствующих строкам матрицы Н. На фиг. 1 представлена схема устройства для Шт. .. .t j нз фиг.2 и фиг.З - временные диаграммы блока синхронизации; на фиг. 4 - схема блока синхронизации. На фиг. 1 показан информационный вход 1,1 + 1 вычислительных блоков 2, 2,..., 2i по основаниям 2,т,,..., YY)t, блок синхронизации 3, имеющий k+1 групп управляющих выходол 4,4, .. . , 4), подключенных к группам управляющих входов 5,5,..., вычислительных блоков 2,2,...,2р соответственно. Вычислительный блок 2 предназначен для выполнения нулевого этапа и осуществляет попарное сложение вычитание входных отсчетов. Вычислительный блок 2 идентичен первому каналу прототипа 122, 1-и вычислительный блок 2i, 1 1. 2Vi предназначен для осуществления г-го этапа разложения - матричного преобразования по матрице Ц(8). Вычислительный блок 2, 1 1, 2,...К, состоит из 2| арифметических узлов 6,62,..., 6 f , каждый из которых соответствует J-й строке, ,2,.. .,2,, матрицы -порядка сдвиговых регистров It ,7,,. ,. ,72щ. , состоящих из N- -j-vi разрядов (п - разрядность операндов) каждый, и выходного коммутатора 8 на положений. Информационные входы 9/( ,9,..., 92ГТЦ арифметических узлов подключены к информационному входу блока. Первый и второй управляющие входы Юл и 11i , ,2,..., 2щ арифметических узлов подключены соответственно, к первому и второму управляющему входам группы 5 управляю1цих входов вычислительного блока 2,л 1,2,..., К. Тактовые входы 12 ,..., сдвиговых регистров 7i ..., ( соединены с 4,5,..., (2mi-f2) управляющими входами соответственно группы S-J вычислительного блока 2. Управляюиц1Й вход

13коммутатора 8 подключен к третьему управляющему входу вычислительного блока 2-, Арифметический узел 6 состоит из сумматора-вьгчитателя 14 сдвигового регистра 15, имеющего VI разрядов, коммутатора 16 на два положения и узла памяти 17 (на сдвиговых регистрах, состоящего из 2п регистров). Первый информационный вход. сумматора-вычитателя

14подключен к информационному входу 9 арифметического узла, а выход сумматора-вычитателя 14 через сдвйго вый регистр 15 и выход 16.i коммутатора 16 подключен к информационному входу 14 сумматора-вычитателя 14.

Выход 162 коммутатора 16 подключен к выходу арифметического узла 6, Выход 17t узла памяти 17 на сдвиговых регистрах подключен к входу 17,2 узла памяти 17 и управляющему входу 14а, сумматора-вьгчитателя 14. Управляющий вход 17я, узла памяти 17 и управляющий вход 16а, коммутатора 16 подключены соответственно к первому и второму управляющим входам 10 и 11 арифметического узла 6 Всё остальные арифметические узлы 6,. .. , 2m-i вычислительного блока 2-j, идентичны арифметическому узлу 6 и отличаются -друг от друга только содержимым узла памяти 17 каждого узла. Узел памяти 1.7 в j-й функциональной ячейке ,2,...,2т предназначен для хранения (в виде двухразрядных двоичных кодов) элементов строки матрицы S) порядка 2г,, с элементами вида О, -1, +1.

Устройство работает следующим образом..

На вход 1 устройства, который подключен ко входу вычислительного блока 2, с частотой тактовых импульсов подаются отсчеты вектора , спектр которого по Уолшо-подобной базисной системе необходимо получить. В вычислительном блоке 2 производится попарное сложение-вычитание первого и второго., третьего и четвертого и т.д. отсчетов вектора Г. Эти суммы и разности с той же тактовой частотой поступают на вход блока 2 д. Поскольку строение и работа блоков 2 ,..., 2 ц. идентичны, то опишем только работу блока 2, предназначенного дпя выполнения г-гр этапа разложения

цифрового сигнала по Уолгао-подобной базисной системе. Вычислительньп1 блок 2т и содержащиеся в нем арифметические узлы 6 ,. . . , б2т-1 . 1 1,2,...,к

и коммутатор 8 работают периодически повторяющимися, одинаковыми циклами, выполнение каждого из которых длится N 4 тактов. Рассмотрим работу блока 2- в течение одного такого цикла, при этом будем описывать работ ту только первого ар114я етического уз-ла 61, так как работа всех остальных полностью идентична и совпадает с работой узла 6 . С выхода предыдущего

блока 21-1 на вход 14 сумМатора-вычитателя 14 через вход блока и вход 9/ арифметического узла 6 с тактовой частотой поступают отсчеты. Сумматор-вычитатель 14 в зависимрсти

от поступившего управляющего импульса

из узла памяти 17 дает на выходе а2+0 а(, , и а2+а,, где и а значения отсчетов на 1-ми 2-м информационных входах сумматора-вьгчитателя 14 соответственно. Управляющие импульсы из узла памяти 17 с частотой тактовых импульсов подаются на . управляющий вход 14 сумматора-вычи- . тателя 14, причем сдвиг в узле памяти 17 и тем самым смена управляющего импульса на сумматор-вычитатель :14 происходит через каждые Ы{ тактов и производится по сигналу из блока синхронизации 3 через управляющий

вход 17з узла памяти 17. Выходные отсчеты сумматора-вычитателя 14 с тактовой частртой поступают на вход СДВИГОВОГО регистра 15, а выходные отсчеты сдвигового регистра 15 с тактовой частотой поступают на информационный вход коммутатора 16. Первые 7. тактов цикла коммутатор 16 под- , ключает выход сдвигового регистра 15 к выходу арифметического узла 6.

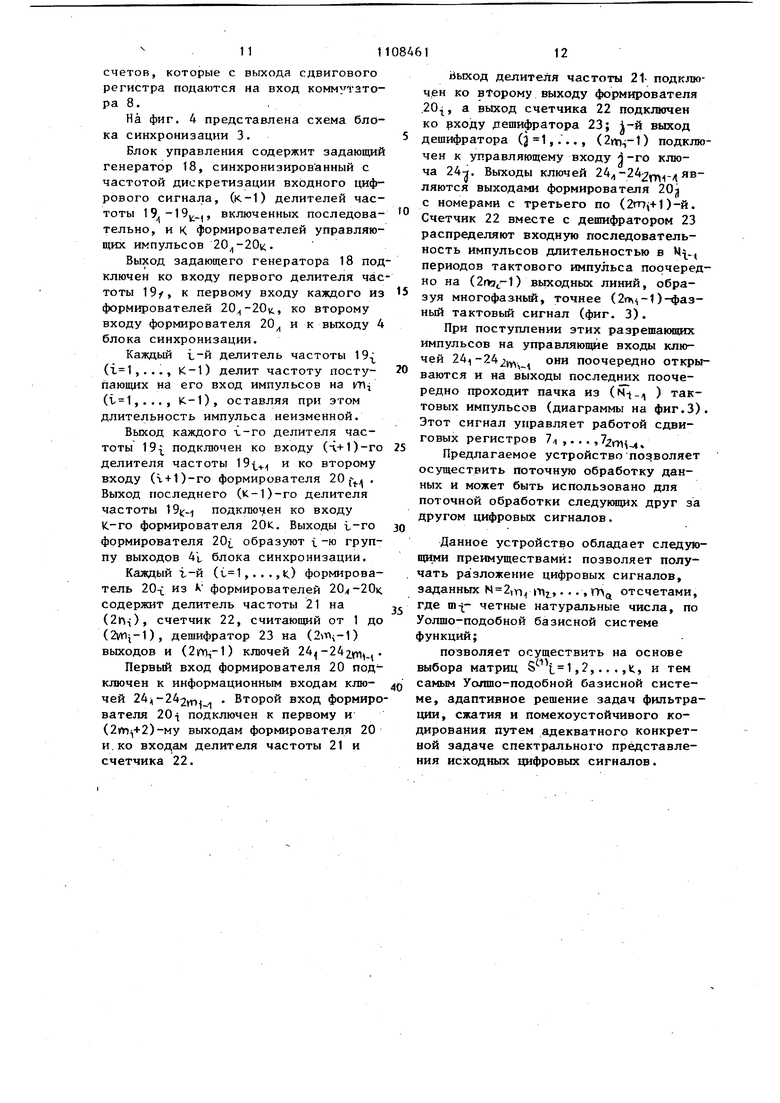

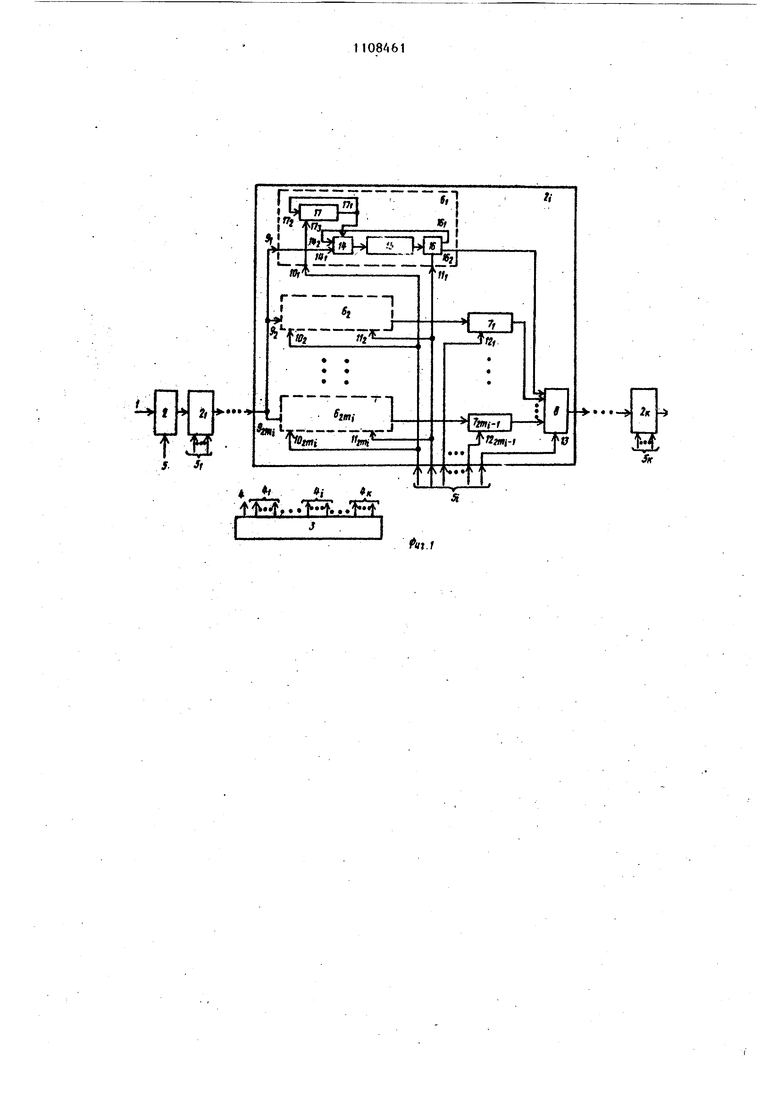

При этом выход арифметического узла 6f через первый информационный вход коммутатора 8 подключен к выходу -вычислительного блока и выходные отсчеты арифметического узла 6 с частртой тактовых импульсов поступают через выход i-io блока 2 на вход (г + 1)-го блока 2i.i|. Первые Ц.,, выходньгк отсчетрв арифметических узлов 62, ... ,. запоминаются в сдвиговых регистрах 7;, ,. .. ,72rti -1 .Начиная с (Vlt-( ОГо такта коммутатор 16 по сигналу из блока синхронизации 3 через управляющий вход б переключен на выход 16, и отсчеты с выхода сдвигового регистра 15 с частотой тактовых импульсов поступают на информационный вход 14 сумматора вычитателя 14. В этом положении коммутатор 16 находится до конца цикла, т.е. всего (Ni-Nvi ) тактов. На первый такт следующего цикла по сигналу из блока синхронизации 3 коммутатор 16 переключается на выход 162. Таким образом, в течение последних (W-i-N-jтактов цикла сумматор-вычитатель 14 суммирует с коэффициентом, соответствующим строке матрицы свой вы ходной отсчет с отсчетом, который поступает на вход 14 через fj так.тов. В то время, как с (vH-i +1)-го по такт идет накопление сумм в сдвиговом регистре 15, коммутатор 8 по сигналу из блока синхронизации 3 через управляющий вход 13 подключает поочередно выходы сдвиговых регистров 7( ,..., 72у к выходу вычислительного блока, причем сдвиговый регистр 7 1,2... , подключен к выходу вычислительного блока с (з Wi-1 +1)-го по (з + 1)-М1м-й такт. С (j.Mt-i+l)ro О (j+l)N-t-.4-и такт на сдвиговый регистр 7 , 3 подается синхронизирующий тактовый импульс из блока синхро низации 3 по управляющему входу 12j, и выходные отсчеты с -го сдвигового регистра поступают через выход т.-го блока на вход (1+1)-го вычислительно го блока. На такте цикл заканчи вается. На (И-г+О-й такт на управляю щий вход 14з сумматора-вычитателя 14 из узла памяти 17 поступает управ ляющий импульс, соответствую11 ;ий перв му элементу строки матрицы , коммутатор 16 по сигналу из блока синхронизации 3 подключает выход сдвигового регистра 15 к выходу арифметиче кого узла, коммутатор 8 также по сиг налу из блока синхронизации 3 подклю чает выход арифметического узла 6,( к выходу вычислительного блока и цикл работы вычислительного блока 2{., содержащихся в нем арифметических узлов 6i(п и коммутатора 8 повторяется снова. Спектрсм цифрового Nvc T04e4HorOi сигнала по Уолшо-по добной базисной системе функций явля ются NK выходных отсчетов последнёго вычислительного блока 2i(.. На фиг. 2 представлены временные диаграммы последовательности импульсов на 1-м, 2-м и 3-м выходах блока синхронизации г-й группы, ,2,..., На диаграмме 1 показана последовательность импульсов на 1-м выходе блока синхронизации. Импульсы 1-го выхода подаются на 1-й управляющий вход г-го вычислительного блока и предназначены для управления узлами памяти 17 арифметических узлов 64,....62mi С поступлением каждого импульса из блока синхронизации происходит сдвиг в блоках памяти. На диаграмме 2 показана последовательность импульсов на 2-м выходе г-й группы вьпсодов блока синхронизации, 1 1,2,.. ., к.. Импульсы 2-го выхода подаются на 2-й управляющий вход i-ro вычислительного блока и предназначены для управления работой коммутаторов 16 арифметических узлов 6,..., 6(1|Пт поступлением первого импульса коммутатор 16 переключается в положение 16, с поступлением второго импульса переключается обратно в положение 162. На диаграмме 3 показана последовательность импульсов на третьем выходе г-й группы выходов блока синхронизации, -1 1,2,. . ., К. Импульсы с этого выхода подаются на третий вход группы 5-1 управляющих входов вычислительного блока 2, и предназначены для управления работой коммутатора 8. С поступлением ГО импульса коммутатор 8 подключает свой С + О-й информационный вход к выходу вычислительного блока, 1,2,..., 2тр1. С поступлением последнего импульса коммутатор 8 подключает к выходу вычислительного блока свой 1-й информационный вход. На фиг. 3 представлены временные диаграммы последовательности импульсов на 4-м, 5-м, ..., ()-M выходах 1-й группы выходов блока синхронизации 1,2,..., К. . На -и диаграмме показана последовательность импульсов на ( выходе t-и группы выходов блока синхронизации, ,2,. ..,2i11p1, 1,... ,;, которые подаются на (+3)-й управляющий вход i-ro блока синхронизации соответственно и предназначены для управления работой сдвиговых регистров 7,| ,..., 72. . С поступлением синхронизирующих тактовых импульсов на соответствующий сдвиговый регистр происходит сдвиг записанных там отсчетов, которые с выхода сдвигового регистра подаются на вход коммутатора 8..

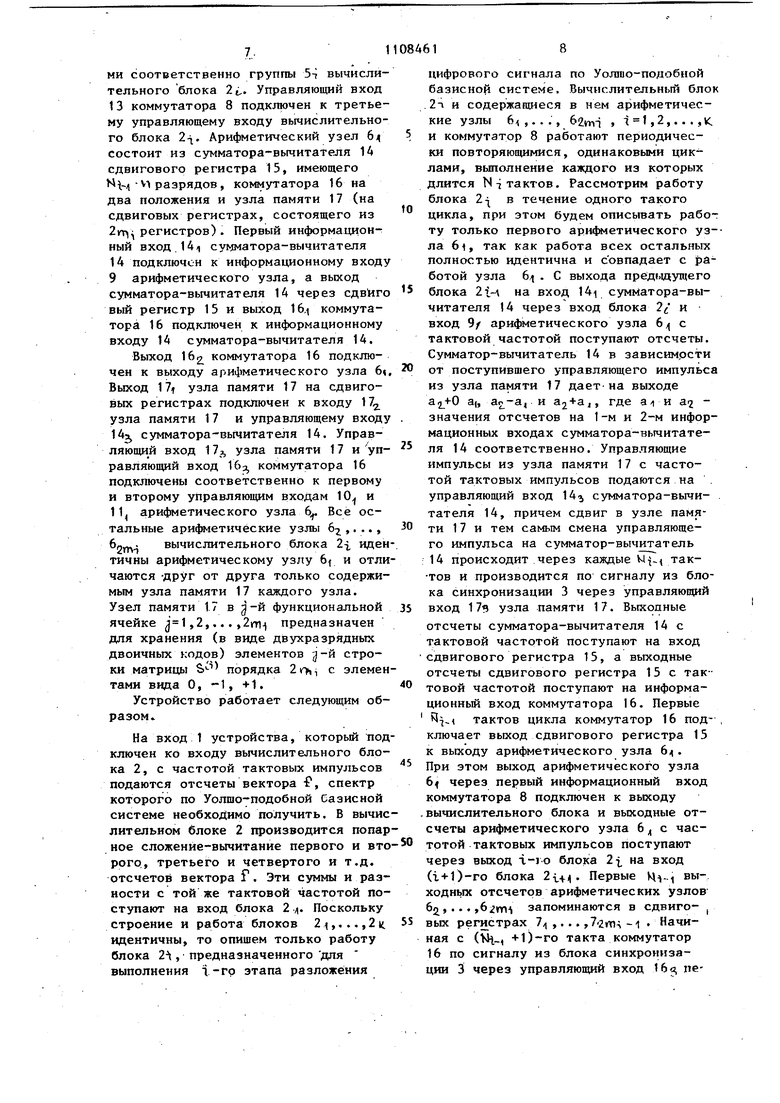

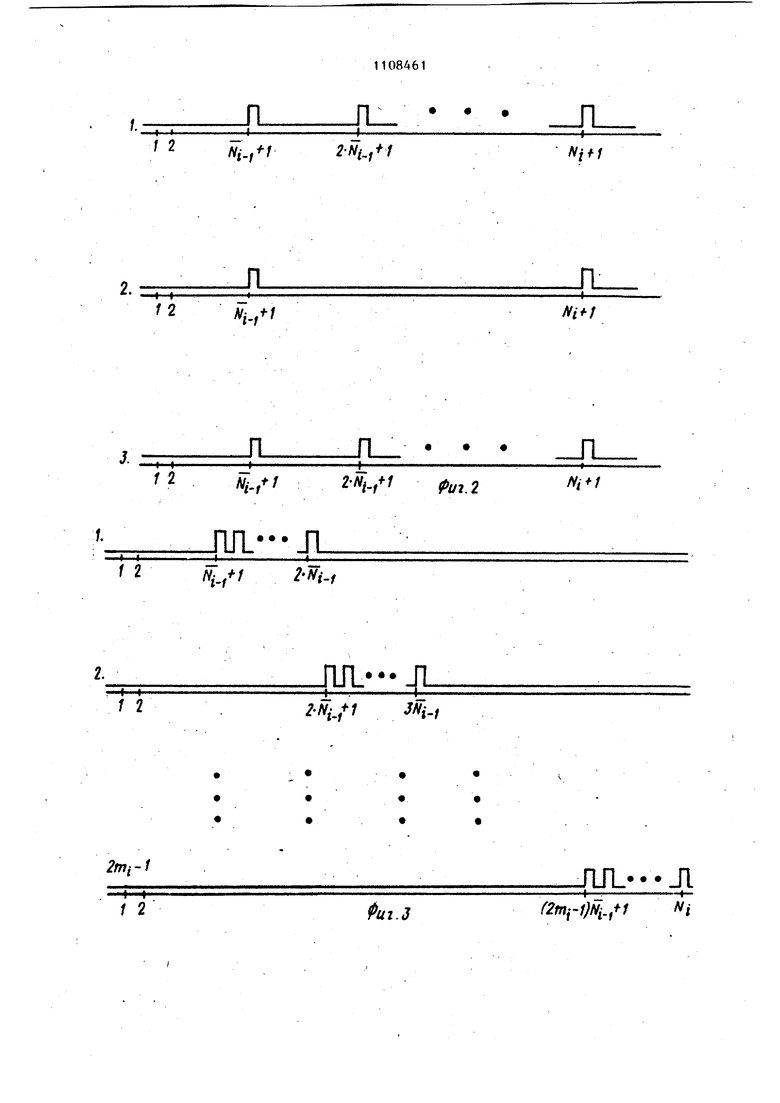

На фиг. 4 представлена схема блока синхронизации 3.

Блок управления содержит задающий генератор 18, синхронизированный с частотой дискретизации входного цифрового сигнала, (к.-1) делителей частоты 19,-19,, включенных последовательно, и К формирователей управляющих импульсов 20 -20vi.

Выход задающего генератора 18 подключен ко входу первого делителя частоты 19/, к первому входу каждого из формирователей , ко второму входу формирователя 20 и к выходу 4 блока синхронизации.

Каждый i-й делитель частоты 19 (,..., К-1) делит частоту поступающих на его вход импульсов на И1 (i 1,..., К.-1), оставляя при этом длительность импульса неизменной.

Выход каждого х-го делителя частоты 19-j подключен ко входу (Ч+1)-го делителя частоты 19; и ко второму входу (г + 1)-го формирователя 20 f . Выход последнего (К-1)-го делителя частоты подключен ко входу (С-го формирователя 20ic. Выходы i-ro формирователя 20; образуют 1 -ю группу выходов 41 блока синхронизации.

Каждый г-и (,...,к) формирователь 20 из V формирователей содержит делитель частоты 21 на (), счетчик 22, считающий от 1 до (2vnj-1), дешифратор 23 на (2 ini-1) выходов и (2infVi-1) ключей ,.

Первый вход формирователя 20 подключен к информационным входам ключей . Второй вход формирователя 20i подключен к первому и (2пг)+2)-му выходам формирователя 20 и.ко входам делителя частоты 21 и счетчика 22.

йыход делителя частоты 21- подключен ко вtopому выходу формирователя .20, а выход счетчика 22 подключен ко рходу дешифратора 23; -й выход дешифратора (,..., () подключен к управляющему входу i-ro ключа 24-J. Выходы ключей являются выходами формирователя 20j с номерами с третьего по ()-й. Счетчик 22 вместе с депшфратором 23 распределяют входную последовательность импульсов длительностью в М., периодов тактового импульса поочередно на () вьпсодных линий, образуя многофааный, точнее ()-фазный тактовый сигнал (фиг. 3).

При поступлении этих разрешакщих импульсов на управляющие входы ключей 24i-242ty, очи поочередно открываются и на выходы последних поочередно проходит пачка из (М ) тактовых импульсов (диаграммы на фиг.З) Этот сигнал управляет работой сдвиговых регистров 7 , ,2т(

Предлагаемое устройствопозволяет осуществить поточную обработку данных и может быть использовано для поточной обработки следующих друг за другом цифровых сигналов.

Данное устройство обладает следующими преимуществами: позволяет получать разложение цифровых сигналов, заданных ,r) tTi2.,. . ПЛ отсчетами, где четные натуральные числа, по Уолшо-подобной базисной системе функций;

позволяет осуществить на основе выбора матриц S {,-1,2. , и тем самым Уолшо-подобной базисной системе, адаптивное решение задач фильтрации, сжатия и помехоустойчивого кодирования путем адекватного конкретной задаче спектрального представления исходных цифровых сигналов.

A

f У

J. Jf

f/ 5

4 «t t«. «УУ p-- -

г« ч

В

SK

f 2

Ni.l2-Щ.1

Л

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для быстрого преобразования Уолша в реальном масштабе времени | 1988 |

|

SU1709341A1 |

| Устройство для вычисления быстрого преобразования Фурье | 1989 |

|

SU1619300A1 |

| Цифровой анализатор спектра Уолша речевых сигналов | 1987 |

|

SU1425710A1 |

| Устройство для ортогонального преобразования по Уолшу-Адамару | 1988 |

|

SU1571610A1 |

| Генератор функций Уолша | 1985 |

|

SU1262470A1 |

| Устройство для выполнения обратного преобразования Хаара | 1983 |

|

SU1104528A1 |

| Устройство для ортогонального преобразования цифровых сигналов по функциям Хаара | 1983 |

|

SU1116435A1 |

| Устройство быстрого преобразования сигналов по Уолшу с упорядочением по Адамару | 1990 |

|

SU1784996A1 |

| Процессор для преобразования цифровых сигналов по Хааро-подобным базисам | 1984 |

|

SU1168966A1 |

| Устройство для ортогонального преобразования цифровых сигналов по Уолшу-Адамару | 1987 |

|

SU1509930A1 |

УСТРОЙСТВО ДЛЯ РАЗЛОЖЕНИЯ ЦИФРОВЫХ СИГНА.10В ПО УОЛШО-ПОДОБНЫМ БАЗИСАМ, содержащее t; +1 вычислительных блоков и блок синхронизации, г-я ( 0,Vi) группа выходов которого соединена с группой управляющих входов 1-го вычислительного,блока, причем информационньй выход г-го (i 0,К-1) вычислительного блока подключен к информационному входу (т. + 1)-го вычислительного блока, информационный вход i-ro () вычислительного блока является информационным входом устройства, а информационный выход К-го вычислительного блока является информационным выходом устройства, отличающееся тем, что, с целью расширения области применения за счет.обработки сигналов, за.данных ,..., ITIt отсчетами, г-й () вычислительный блок содержит 2 гп( арифметических узлов, 2гп;-1 сдвиговых регистров с разрядностью NTH (где п - разрядность операндов) каждый г вьгходной коммутатор, причем -и

- -f2 -.,., I .,/2-/V./f ф,2

JUL--rJl

2/y.f/ f./y,-.,

Ч-t/ 2

./V,.//3Ni.

f/n,-/

-+-h

/ 2

л

JUL-Jl

/ w/-/; // /

ifZ.J

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Патент США № 3792355, кл | |||

| Очаг для массовой варки пищи, выпечки хлеба и кипячения воды | 1921 |

|

SU4A1 |

| ПРИБОР ДЛЯ ЗАПИСИ И ВОСПРОИЗВЕДЕНИЯ ЗВУКОВ | 1923 |

|

SU1974A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Устройство для ортогонального преобразования цифровых сигналов по уолшу-адамару | 1975 |

|

SU555404A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1984-08-15—Публикация

1983-04-26—Подача