33 V

СО со оэ оэ

00

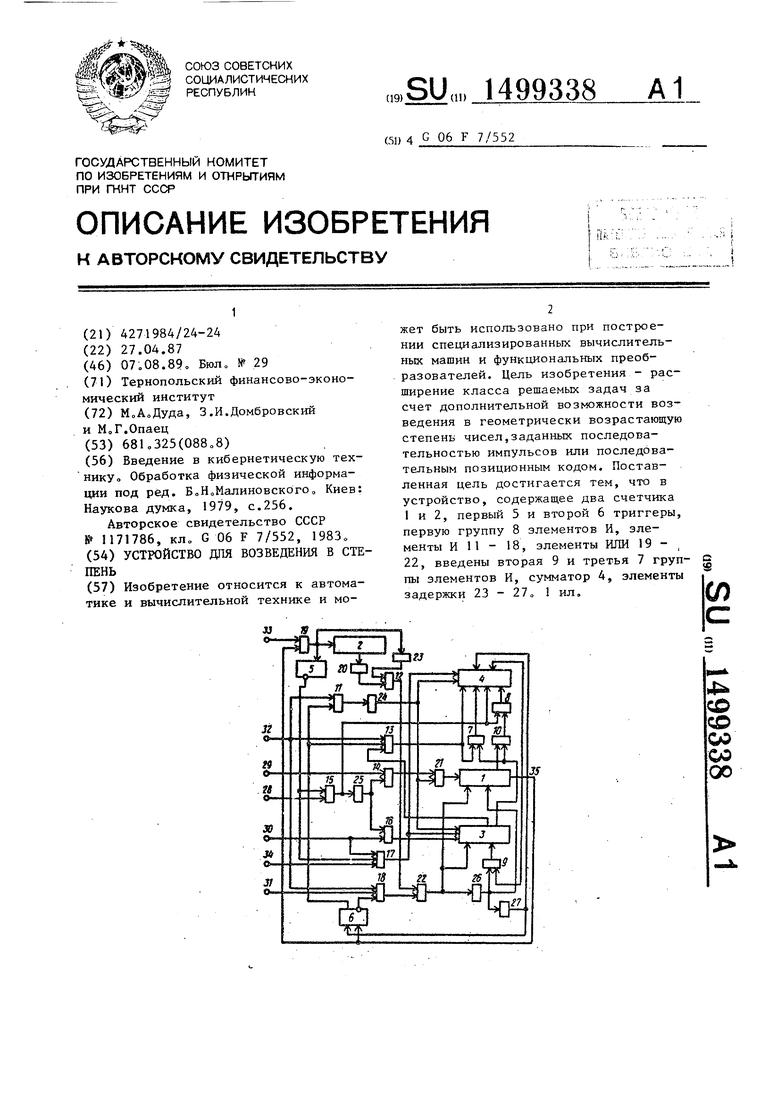

Изобретение относится к области автоматики и вычислительной техники, в частности может быть использовано при построении специализированных вычислительных машин и функциональных преобразователей,

Цельго изобретения является расширение класса решаемых задач за счет дополнительной возможности возведения в геометрически возрастающую степень чисел, заданных последовательностью импульсов или последовательным позиционным кодом.

На чертеже представлена структурная схема устройства для возведения в степень

На схеме .обозначены: счетчики 1 и 2, регистр 3 сдвига, сумматор 4,триггеры 5 и 6, группы элементов И 7 - 9, группа элементов ИЛИ 10, элементы И 11, 12, 13- 18, ИЛИ 19 - 22, элементы 23 - 27 задержки, информационный вход 28, входы 29-31 задания реступает на информационные входы группы элементов И 8 через rpyimy элементов ИЛИ 10)„ Затем импульс с выхода элемента И 15 прохбдит через элемент 25 задержки, элементы И 14, ИЛИ 21 и прибавляет единицу к содержимому счетчика 1.

Аналогичные вычисления проводят10 ся для каждого импульса, поступившего на информационный вход 28 устройства ,

Сигнал сброса, поступающий после числа X на вход 33, через элемент

15 ИЛИ 19 устанавливает триггер 5 в единичное состояние и вычитает единицу из числа К, записанного в счетчике 2, Если значение К К-1 равно нулю, то на выходе элемента ИЛИ 20 будет ну20 левой сигнал и процесс вычисления прекращается. При этом в сумматоре 4 будет значение X „

В случае, если значение К К-1 больше нуля, то на выходе элемента .жима, тактовый вход 32, вход 33 сбро- 25 ИЛИ 20 единичный сигнал остается.При

са, управляющий вход 34, выход 35 счетчика 1.

Устройство работает следующим образоМо

При возведении в геометрически возрастающута степень числа X, заданного последовательностью импульсов и поступающего на информационный вход 28, на входе 29 задания режима работы должен быть единичный, а на входах 30, 31 и 34 устройства нулевые сигналы При этом счетчик 1 и сумматор 4 свободны, а в счетчике 2 должно быть записано число К, равное двоичному логарифму степени (например, для степени 2 - число I; для степени 2 - число 2; для степени 2 - число К), вследствие чего на выходе элемента ИЛИ 20 есть единичный сигнал Вместе с тем, на вход 32 поступают тактовые импульсы определенной частоты, а триггеры 5 и 6 - в нулевом состоянии

С приходом первого импульса на информационный вход 28 через элемент И 15 к содержимому сумматора 4 прибавляется единица. Кроме того, импульс с выхода элемента И 15 открывает группу элементов ИЗ, через которую содержимое счетчика 1 передается на первую группу входов (в п младших разрядов) сумматора 4 со сдвигом на один разряд влево, , удвоенное значение (содержимое счетчика 1 по35

40

этом импульс с выхода элемента ИЛИ 19 проходит через элемент 23 задержки, вследствие чего на выходе элемента И 12 возникает единичный сиг30 нал. Этот сигнал через элемент ИЛИ 22 устанавливает счетчик 1 и регистр сдвига 3 в нулевое состояние, а затем через элемент 26 задержки переписывает содержимое сумматора 4 в регистр 3 сдвига и устанавливает в счетчике 1 в дополнительном коде число, равное количеству разрядов п регистра 3 сдвига. Далее сигнал с входа элемента 26 задержки через элемент 27 задержки устанавливает сумматор 4 в нулевое состояние, а три:- гер 6 - в единичное состояние. При этом на единичном выходе.триггера 6 возникает единичный сигнал.

Если на выходе первого (самого младшего) разряда регистра 3 сдвига единичный сигнал, то первый тактовый импульс, поступающий на вход 32; через элемент И. 13 открьшает группу

50 элементов И 7, через которую содержимое регистра 3 сдвига, кроме самого младшего разряда, передается на вторую группу входов (в п+1.старших разрядов) сумматора 4 со сдвигом

55 на один разряд влево, т.е. удвоенное значение. Вместе с тем к содержимому сумматора 4 в (2п+1)-й разряд прибавляется единица. Затем первый так- товый импульс через элемент И 11 и 45

ступает на информационные входы группы элементов И 8 через rpyimy элементов ИЛИ 10)„ Затем импульс с выхода элемента И 15 прохбдит через элемент 25 задержки, элементы И 14, ИЛИ 21 и прибавляет единицу к содержимому счетчика 1.

Аналогичные вычисления проводятся для каждого импульса, поступившего на информационный вход 28 устройства ,

Сигнал сброса, поступающий после числа X на вход 33, через элемент

ИЛИ 19 устанавливает триггер 5 в единичное состояние и вычитает единицу из числа К, записанного в счетчике 2, Если значение К К-1 равно нулю, то на выходе элемента ИЛИ 20 будет нулевой сигнал и процесс вычисления прекращается. При этом в сумматоре 4 будет значение X „

5

0

этом импульс с выхода элемента ИЛИ 19 проходит через элемент 23 задержки, вследствие чего на выходе элемента И 12 возникает единичный сиг0 нал. Этот сигнал через элемент ИЛИ 22 устанавливает счетчик 1 и регистр сдвига 3 в нулевое состояние, а затем через элемент 26 задержки переписывает содержимое сумматора 4 в регистр 3 сдвига и устанавливает в счетчике 1 в дополнительном коде число, равное количеству разрядов п регистра 3 сдвига. Далее сигнал с входа элемента 26 задержки через элемент 27 задержки устанавливает сумматор 4 в нулевое состояние, а три:- гер 6 - в единичное состояние. При этом на единичном выходе.триггера 6 возникает единичный сигнал.

Если на выходе первого (самого младшего) разряда регистра 3 сдвига единичный сигнал, то первый тактовый импульс, поступающий на вход 32; через элемент И. 13 открьшает группу

0 элементов И 7, через которую содержимое регистра 3 сдвига, кроме самого младшего разряда, передается на вторую группу входов (в п+1.старших разрядов) сумматора 4 со сдвигом

5 на один разряд влево, т.е. удвоенное значение. Вместе с тем к содержимому сумматора 4 в (2п+1)-й разряд прибавляется единица. Затем первый так- товый импульс через элемент И 11 и 5

5

элемент 24 задержки осуществляет сдвиг содержимого сумматора 4 на два разряда вправо и сдвиг содержимого регистра 3 сдвига на один разряд вправо„

Кроме того, импульс с выхода элемента 24 задержки проходит через элемент ИЛИ 21 и прибавляет единицу к содержимому счетчика 1 о

В случае, если на выходе самого младшего разряда - нулевой сигнал, то первый тактовый импульс только через элемент И И и элемент 24 задержки осуществляет сдвиг содержимо- го сумматора 4 на два разряда вправо и сдвиг содержимого регистра 3 сдвига на один разряд вправо, В этом случае импульс с выхода элемента 24 задержки также проходит через элемент ШШ 21 и прибавляет единицу к содержимому счетчика 1.

Аналогичные вычисления проводятся для каждого тактового импульса, поступившего на вход 32. После сдвига числа в регистре 3 сдвига п раз в счетчик 1 поступит п импульсов,вследствие чего на выходе 35 этого счетчика возникает единичный сигнал, который устанавливает триггер 6 в нуле- вое состояние. Благодаря этому поступление тактовых импульсов через элементы И 13 и 11 прекращается. Вместе с тем единичный сигнал с выхода 35 счетчика 1 через элементы ИЛИ 19 вычитает единицу из числа К, записанного в счетчике 2..

Если К К-1 больше нуля, то на выходе элемента ИЛИ 20 останется еди ничньй сигнал. При этом единичный сигнал с выхода элемента ИЛИ 19 проходит через элемент 23 задержки, вследствие чего на выходе элемента И 12 возникает единичный сигнал.

Далее устройство работает знало- гично описанному.

В случае, если значение К К-1 равно нулю, то на выходе элемента ИЛИ 20 возникает нулевой сигнал и процесс вычисления прекращается.

В результате в сумматоре 4 будет значение х, где К - первоначальное значение, записанное в счегчи- ке 2„

ма работы должен быть единичный, а на входах 29 и 31 устройстпа нулевые сигналы. При этом регистр 3 сдвига, сумматор 4 и счетчик I свободны, а в счетчике 2 записано число К, равное двоичному логарифму степени, вследствие чего на выходе элемента ИЛИ 20 есть единич№1Й сигнал.Вместе с тем, на вход 32 поступают тактовые импульсы определенной частоты,а триггеры 5 и 6 - в нулевом состоянии

В первом такте на вход 34 управления поступает единичный сигнал,который через элемент И 17 осуществляет сдвиг содержимого сумматора 4 и регистра 3 сдвига соответственно на два и один разряд влево. Во втором такте при наличии единицы в данном разряде последовательного кода, поступающего на информационный вход 28 устройства, через элемент И 15 к содержимому сумматора 4 прибавляется единицао Кроме того, импульс с выхода элемента И 15 открывает группу элементов И 8, через которую содержимое регистра 3 сдвига, кроме: первого самого младшего разряда, передается на первую группу входов сумматора 4 со сдвигом на один разряд влево, т.е удвоенное значение. Затем импульс с выхода элемента И 15 проходит через элемент 25 задержки, элемент И 16 и записывает единицу в регистр 3 сдвига.

В случае, если в данном разряде п последовательного кода, поступающего на информационный вход 28 устройства, единица отсутствует, то второй такт не выполняется

Аналоп-гчные вычисления производятся для каждого разряда, поступившего на информационный вход 28 устройства.

После окончания числа х, заданного последователышм позиционным кодом, на вход 33 поступает сигнал сброса. При этом последующие вычисления выполняются в устройстве так, как при поступлении сигнала сброса после числа, заданного последовательностью импульсов. В результате

Л1/

в сумматоре 4 будет значение х . В случае возведения в степень чис

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для возведения двоичных чисел в квадрат /его варианты/ | 1984 |

|

SU1280615A1 |

| Арифметическое устройство | 1987 |

|

SU1476459A1 |

| Устройство для вычисления квадрата числа | 1983 |

|

SU1115051A1 |

| Устройство для вычисления @ , @ , @ аргумента,заданного параллельным и число-импульсным кодом | 1980 |

|

SU999047A1 |

| Устройство для возведения в куб | 1985 |

|

SU1257640A1 |

| Преобразователь @ -ичного позиционного кода в двоичный код | 1983 |

|

SU1115045A1 |

| Устройство для медианной фильтрации двумерных массивов | 1987 |

|

SU1524067A1 |

| Устройство для извлечения корня третьей степени | 1974 |

|

SU551641A1 |

| Устройство для возведения в степень (его варианты) | 1982 |

|

SU1076905A1 |

| Устройство для моделирования систем массового обслуживания | 1982 |

|

SU1067508A1 |

Изобретение относится к автоматике и вычислительной технике и может быть использовано при построении специализированных вычислительных машин и функциональных преобразователей. Цель изобретения - расширение класса решаемых задач за счет дополнительной возможности возведения в геометрически возрастающую степень чисел, заданных последовательностью импульсов или последовательным позиционным кодом. Поставленная цель достигается тем, что в устройство, содержащее два счетчика 1 и 2, первый 5 и второй 6 триггеры, первую группу 8 элементов И, элементы И 11-18, элементы ИЛИ 19-22, введены вторая 9 и третья 7 группы элементов И, сумматор 4, элементы задержки 23-27. 1 ил.

В случае возведения в геометричес- - ла, заданного параллельным кодом, ки возрастающую степень числа х, за- на входе 31 задания режима должен данного последовательным позиционным быть единичный, а на входах 28, 29,

.30, 33 и 34 устройства нулевые сигналы. При этом в сумматоре 4 записакодом и поступающего на информационный вход 28, на шине 30 задания, режино число, которое необходимо возвести в степень 2, а в счетчике 2 записано число К, равное двоичному логарифму степени, вследствие чего на выхбде элемента ИЛИ 20 есть единичный сигнало Вместе с тем, на вход 32 поступают тактовые импульсы определенной частоты, а триггер; 1 5 и 6 - в нулевом состоянии.

Первый тактовый импульс, поступающий на вход 32, проходит через элементы И 18 и ИЛИ 22о Далее устройство работает так, как при прохождении единичного сигнала с выхода элемента И 12 через элемент ИЛИ 22 при возведении в степень числа, заданного последовательностью импульсов, В результате в сумматоре 4 будет записано значение х.

Формула изобретения

Устройство для возведения в степень, содержащее два счетчика, регистр, первый и второй триггеры,первую группу элементов И, элементы И, ИЛИ, группу элементов ИЛИ, отличающееся тем, что,- с целью расширения класса решаемых задач за счет обеспечения дополнительной возможности возведения в геометрически возрастающую степень чисел, заданных последовательным позиционным кодом или последовательностью импульсов, в него введены вторая и 1 ретья группы элементов И, сумматор и элементы задержки, причем информацион- 1а1й вход устройства соединен с первым входом первого элемента И, выход которого непосредственно соединен с первым входом сумматора и управляющими входами элементов И первой группы, а через первый элемент за- дерлжи - с первыми входами второго и третьего элементов И, второй вход последнего из которых и первый вход четвертого элемента И подключены к первому входу задания режима устройства, второй и третий входы задания режима кото-рого подключены соответственно к первому входу пятого элемента И и второму входу второго элемента И, выходы которых соединены с первыми входами первого и второго элементов ИЛИ соответственно, выход первого из которых соединен непосредственно с установочными входами первого счетчика и регистра сдвига, а че

5

0

5

0

5

рез второй элемент задержки - с управляющими входами элементов И второй группы, с входом третьего элемента задержки и информационным входом первого счетчика, выход которого подключен к входу установки в О первого триггера и первому входу третьего элемента ИЛИ, второй вход которого соединен с входом сброса устройства, а выход - с входом установки в 1 второго триггера , со счетным входом второго счетчика и входом четвертого элемента задержки, выход которого подключен к первому входу шестого элемента И, второй вход которого соединен с выходом четвертого элемента ИЛИ, вход которого подключен к выходу второго счетчика, инверсный выход второго триггера соединен с вторыми входами первого и четвертого элементов И, третий вход последнего из которых подключен к управляющему входу устройства, а выход - к первым управляющим входам регистра сдвига и сумматора, вторые управляющие входы которых и второй вход второго элемента ИЛИ соединены с выходом пятого элемента задержки, вход которого соединен с выходом седьмого элемента И, первый вход которого и первые входы пятого и восьмого элементов И подключены к тактовому входу устройства, вторые входы седьмого и восьмого элементов И соединены с прямым выходом первого триггера, инверсный выход которого подключен к третьему входу пятого И, а вход установки в 1 - к

40

выходу третьего элемента задержки и входу установки в О сумматора, выходы которого соединены с информационными входами элементов И зторой группы, выходы элементов И которой подключены к информационным входам

регистра сдвига, третий управляющий вход которого соединен с вькодом третьего элемента И, третий вход восьмого элемента И соединен с выходом регистра сдвига, а выход - с вторым.

входом сумматора и управляющими входами элементов И третьей группы, ин- , формационные входы элементов И рой и первые входы элементов ИЛИ группы соединены с группой выходов

регистра сдвига, вторые входы и выходы элементов ИЛИ группы соединены соответственно с разрядными выходами первого счетчшса и с информационными входами элементов И первой груп 149933810

,пы, выходы элементов И которой ивходов сумматора соответственно, втовыходы элементов И третьей группы со- рой вход перйого элемента ИЛИ соеди- единены с первой и второй группаминей с выходом шестого элемента И.

| Введение в кибернетическую технику Обработка физической информации под ред | |||

| БоНоМалиновскогОо Киев: Наукова думка, 1979, с.256 | |||

| Устройство для возведения в степень | 1983 |

|

SU1171786A1 |

Авторы

Даты

1989-08-07—Публикация

1987-04-27—Подача