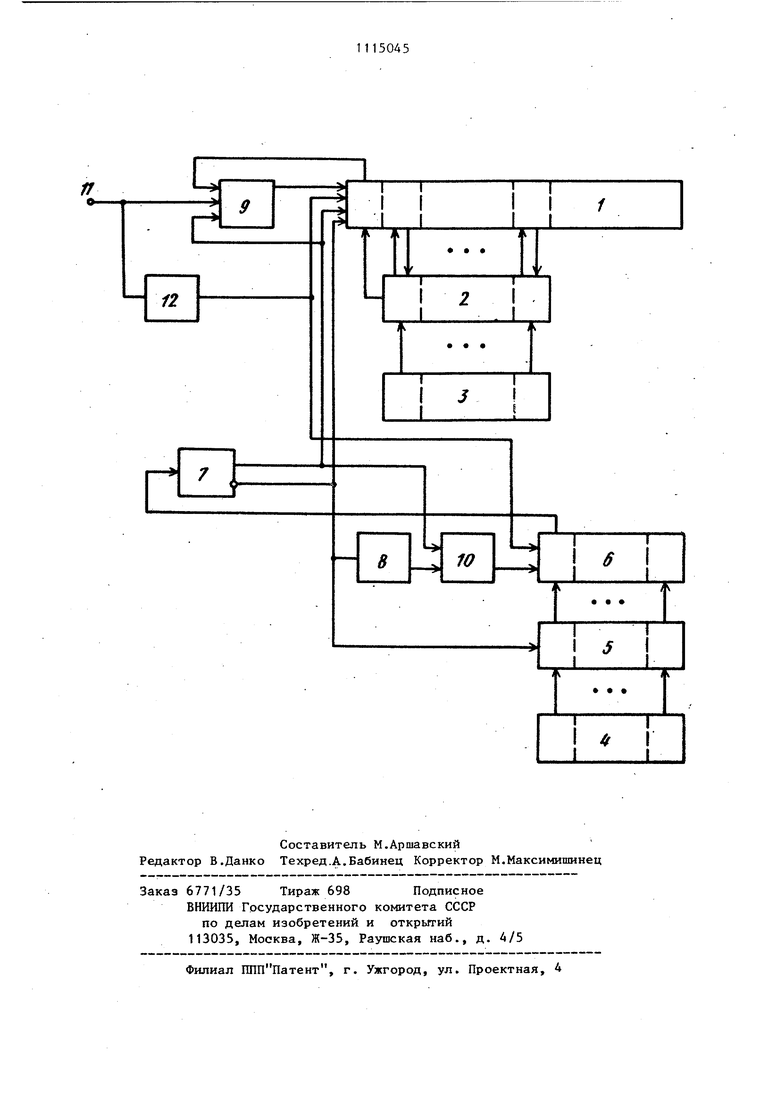

Изобретение относится к вычислительной технике и предназначено для преобразования целях К-разрядных два ично-кодированньЕх чксел из позиционной системы счисления с любым основанием Р в двоичную систему . счисления. Известен преобразователь кодрв из позиционной системы счисления с основанием Р 2 в двоичный код, содержащий сдвиговые регистры, много разрядный вычислитель, блоки управле ния алгебраического суммирования, умножитель и элементы И и ИЛИ с соответствуюпщми связями. Перевод числа из одной системы счисления в другую вьтолняется как многошаговая пос ледовательность операций сдвига и ко рекции 1 . Наиболее близким техническим реше нием к изобретению является преобразователь р-ичного кода в двоичный код, содержащий накопительньш сумматор, регистр основания, сумматор основания и сдвиговьм регистр, к вхо дам старших разрядов которого, начиная со второго, подключены 1 logjp входов сумматора основания, а выходы этих разрядов регистра соединены с первой группой входов сумматора основания, вторая группа входов которого соединена с выходами регистра основания. Процесс преобразования ос ществляется путем сдвига и суммиро-. вания кодов в накопительных сумматорах на каждом шаге t2. Недостаток известных устройств .большая сложность, Целью изобретения является упроще ние преобразователя. Поставленная цель достигается тем что преобразователь р-ичного позиционного кода в двоичный код, содержащий накопительный сумматор, регистр основания, сумматор основания и сдвиговый регистр, входы ХоЗпрС старших разрядов которого, начиная со второго, соединены соответственно с разрядными выходами сумматора основания, первая группа входов которого соединена с соответствующими выходами сдвигового регистра, а вторая группа входов сумматора основания - с выходами сдвигового регистра основания, содерясит элемент И, элемент ИЛИ, первый и второй элементы задержки, регистр контстанты, счетчи и триггер, счетный вход которого сое динен с выходом переполнения счетчика, информационные входы которого соединены с выходами накопительного сумматора, информационные входы которого соединены с выходами регистра константы, а управля.ощий вход накопительного сумматора - с нулевым вы содом триггера, с входом сдвига влево сдвигового регистра и через первьй элемент задержки - с первым входом элемента ИЛИ, второй вход которого соединен с единичным выходом триггера, с первым входом элемента И и входом сдвига вправо сдвигового регистра, вход старшего разряда которого соединен с выходом переноса сумматора основания, а выход старшего разряда - с втррым входом элемента И, выход которого соединен с входом записи сдвигового регистра, а третий вход элемента И - с тактовым входом преобразователя и через второй элемент задержки- с тактовым входом сдвигового регистра и счетным входом счетчика, вход записи которого соединен с выходом элемента ИЛИ. На чертеже изображена структурная схема преобразователя кодов. Преобразователь содержит сдвиговьй регистр 1, сумматор 2 основания и регистр 3 основания. Регистр 3 основания и сумматор 2 имеют по m 31о§,2 Р пда двоичных разрядов, где Р( максимальное основание системы счисления, из которой осуществляется преобразование двоично-кодированньк чисел в двоичную систему счисления. Регистр 1 является реверсивным сдвигающим регистром с цепями циклического сдвига из старшего разряда в t-шадший (при сдвиге информации влево) и из мпадшего разряда в старший (при сдвиге вправо). Длина в двоичных разрядах регистра 1 определяется вьфажением шК + 1, где К - количество разрядов числа с основанием Р(щу I; Устройство также содержит регистр 4константы, накопительный сумматор 5и счетчик 6, имеющие nojlog CK 1) ш l| двоичных разрядов. Выход переноса (переполнения) счетчика 6 соединен с счетным входом триггера 7, нулевой выход которого подключен к первому управляющему входу регистра 1 к управляющему входу накапливающего сумматора 5 и к входу элемента 8 задержки. Единичный выход триггера 7 соединен с вторым управлякяцим входом регистра 1, с входЪм элемента И 9 и с одним входом элемента ИЛИ 10, другой вход которого соединен с выходом элемента 8 задер кн. тактовый вход 11 преобразователя соединен с входом элемента И 9 элемента 12 задержки. Узлы 1-6 устройства составляют его опера)дионную часть, а элементы 7-12 - его управляющую часть. Первый и второй входы регистра 1 предназначены для управления направлени ем сдвига в регистре и являются потенциальными. Если единичный сигнал потенциал) присутствует на первом управляющем входе, то в регистре 1 осуществляется сдвиг влево (в сторо старших разрядов), а при наличии ед ничного сигнала на втор,ом управляющем2ц

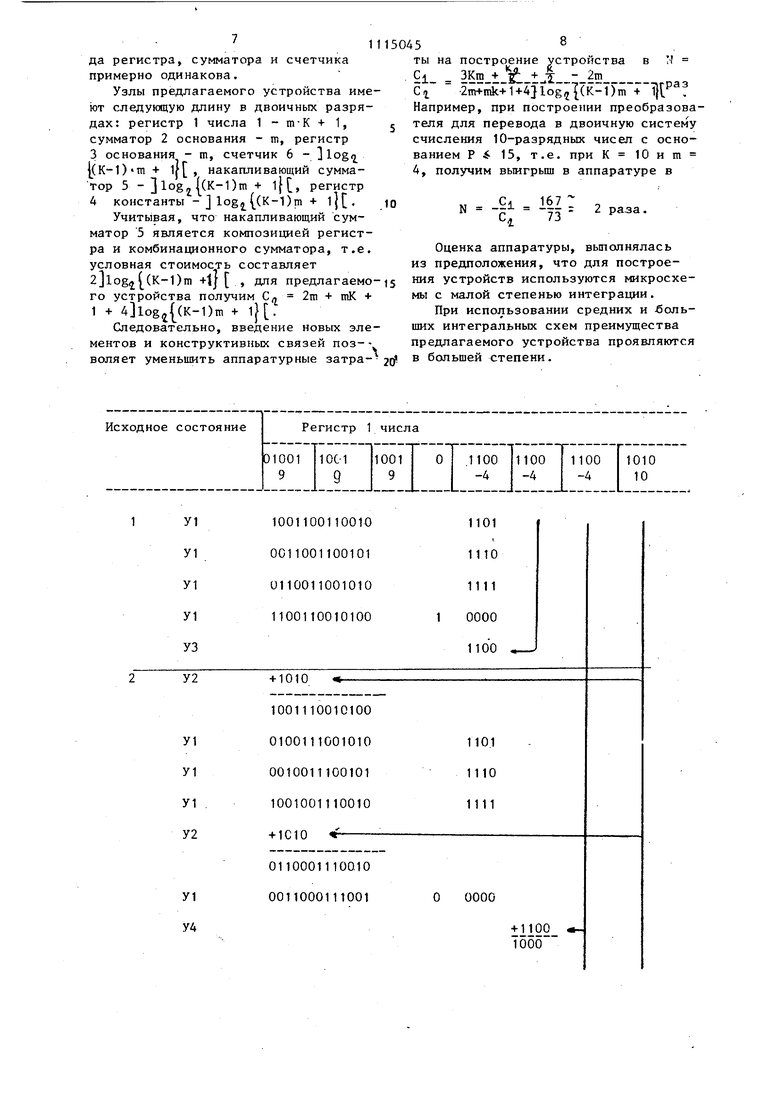

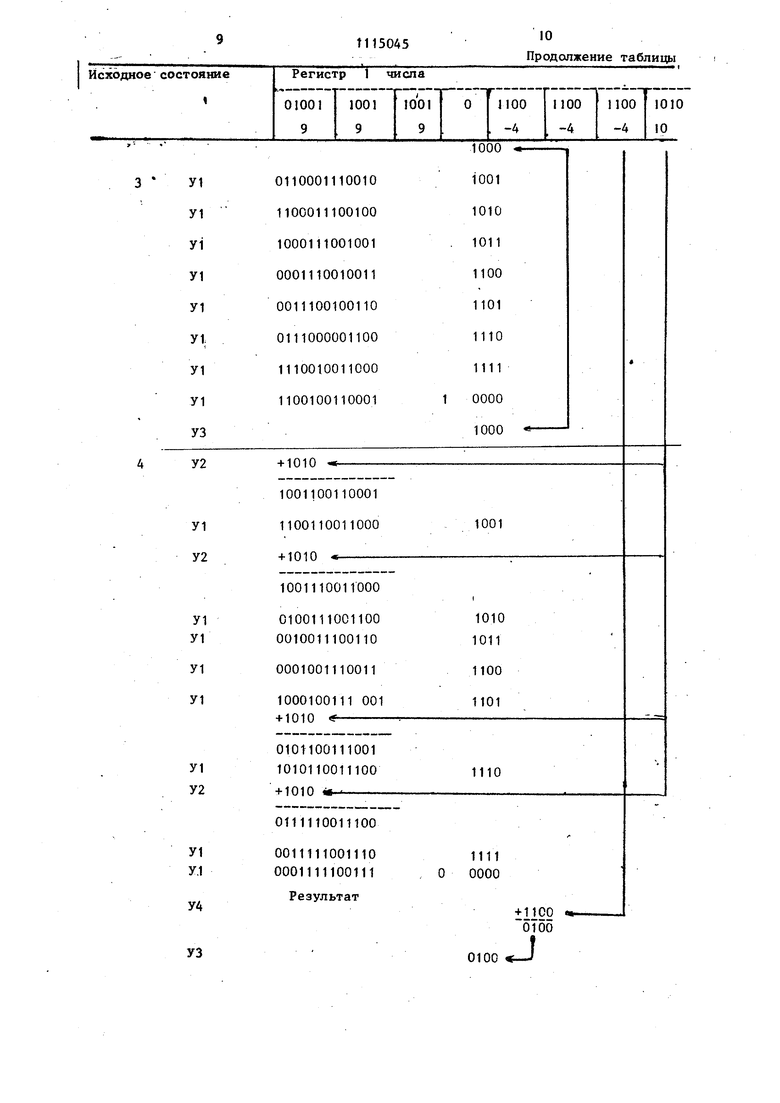

входе - сдвиг информации вправо. Все остальные управляющие входы узлов 1, 5 и 6 устройства, обеспечивают изменение их состояния при изменении у уровня сигналов (для определенности, при переходе из О в 1), т.е. по фронту сигналов. Третий управляющий вход регистра 1 предназначен для сдвига информации в регистре на один разряд, а четвертый - для приема информации на регистр с выходов сумматора 2 основания (при этом информация принимается только в те разряды регистра 1, которые связаны с выходами сумматора 2 основания, значения остальных разрядов регистра при этом не изменяются) Управляющий вход накопительного сумматора 5 предназначен для разрешения суммирования содержимого сумматора и содержимого регистра 4 константы. Первый управляющий вход счетчика 6 является счетным, т.е. обеспечивает увеличение содержимого счетчика 6 на единицу, а второй управляющий вход предназначен для занесения в счетчик 6 информации параллельным кодом с выходом накапливающего сумматора 5. Длина счетчика, регистров и сумматоров устройства определяется максимальным основанием P, . В исходном состоянии в регистре 3 основания записано основание Р в двоичной системе счисления,. Код основания имеет log-jPf двоичных разрядов. Если J log,jPf, , то код основания устанайливается в старших разрядах регистра 3, а оставС началом работы преобразователя на вход 11 начинают поступать синхросигналы. Процесс работы устройства можно разбить на 2К - 2 цикла. В . 454 . шиеся младшие разряды - в нулевое состояние. В старшем разряде регистра 1 записан нуль, а справа-от этого разряда записаны подряд р-ичные разряды преобразуемого числа (начиная со старшего). В регистр 4 константы, накапливающий сумматор 5 и счетчик 6 записано в дополнительном коде двоичное число Jlogrt C равное числу двоичных разрядов, необходимых для представления одной р-ичной цифры. Триггер 7 в исходном со стоянии установлен на нуль, т.е. регистр 1 подготовлен для 1Д1клического сдвига информащ1и влево, так как единичный сигнал при атом поступает на первый управляющий вход этого регистра (цепи установки исходного со стояния устройства условно не показаны) . каждом нечетном цикле осуществляется циклический сдвиг информации в регистре числа 1 влево, а в каждом четном - вправо, причем в этом случае одновременно осуществляется и преобразование информации в регистре 1. В первом цикле (как и в каждом последукхцем нечетном цикле) элемент И 9 закрыт нулевым сигналом с единичного выхода триггера 7, т.е. на четвертый управляющий вход регистра 1 сигналы не поступают. Каждый синхросигнал с входа 11 через элемент 12 задержки поступает на третий управляющий вход регистра 1 и на второй управляющий вход счетчика 6. В регистре 1 при этом каждый раз осуществляется циклический сдвиг на один двоичный разряд влево а в счетчике 6 - прибавление единицы к его содержимому. Поскольку в исходном состоянии в счетчике 6 быпо записано в дополнительном коде число , то после прихода такого же количества синхросигналов формируется сигнал переполнения счетчика 6, который, поступая на счетный вход триггера 7, изменяет его состояние на противоположное (в первом цикле на единичное). Положительный перепад потенциала, формирующийся на единичном выходе триггера 7, через элемент ИЛИ 10 поступает на второй управляющий вход счетчика 6 и осуществляет запись с выходов накопительного сумматора 5 в счетчик 6 дополнительного кода исла . На этом первый цикл зака.нчивается. ТаКИМ образом, после вьтолнения первого 5 цикла в регистре 1 информация циклически сдвинулась на один р-ичньш разряд (или на двоичных разрядов), а в счетчике 6, как и перед выполнением цикла, записано число JlogrtP в дополнительном коде. Поскольку триггер 7 находится в единичном состоянии, то перед выполнением второго (как и каждого четного) цикла регистр 1 подготовлен для циклического сдвига вправо. Во втором цикле, если в старшем разряде регистра 1 находится единица, синхросигнал с входа 11 через элемент И 9 поступает на четвертый управляющий вход этого регистра. С п мощью сумматора 2 основания к содержимому регистра 1 прибавляется основание Р, записанное в регистре 3 основания, причем перенос, формирующий ся на сумматоре, записывается в стар ший разряд регистра 1. Если в старшем разряде регистра 1 записан нуль, то суммирование не вьшолняется. Затем сигнал с выхода элемента 12 задержки осуществляет сдвиг на один ДВОИЧНЫЙ разряд содержимого регистpa 1 и прибавление единицы к счетчик 6, После поступления } синхросигналов, как и в первом цикле, формируется сигнал переполнения счетчика 6, который изменяет состояние триггера 7 на нулевое, Положительньй перепад потенциала с нулевого выхода триггера 7 поступает на управляющий вход сумматора 5, в результате чего к его содержимому прибавляется содер жимое регистра 4 контстанты. Этот же . положительный перепад через элемент задержки и элемент ИЛИ 10 поступает на второй управляющий вход счетчика 6 и осуществляет запись в счетчик ко да, полученного на накапливающем сум маторе 5 (если этого требует используемая элементная база, то из перепада потенциала: можно получить сигна нужной длительности с помощью формир вателей, например РС-цепочек). Следо вательно, после вьтолнения второго цикла в счетчике 6 и накапливающем сумматоре 5 записан дополнительный код числа 2 , а в регистре 1 произошло частичное преобразование информации. Последующие циклы отличаются от указанных двух первых циклов только количеством тактов. В каждой последующей паре циклов число тактов на log Р больше, чем в предьщущей. так как после каждого четного цикла содержимое счетчика 6 увеличивается на величину logn Р. После вьтолнения 2К - 2 циклов процесс преобразования заканчивается. Результаты преобразования (двоичное число) находятся в регистре 1. Проиллюстрируем работу устройства на следующих примерах. Будем, для определенности, считать, что устройство предназначено для преобразования целых трехразрядных чисел с произвольным основанием Р 4 10 в двоичную систему счисления, т.е. 10, к 3. В этом случае регистр 1 числа содержит + 1 J log |j + 1 13 двоичных разрядов, регистр 3основания и сумматор 2 основания по logij loC 4 разряда, а счетчик 6, накапливающий сумматор 5 и регистр 4констайты - по log.((K-l) logi2 10 + 1/ 4 разряда. Пусть исходное двоично-десятичное число X(2.|Q равно 1001, 1001 1001 (т.е. Хц 999 в десятичной системе счисления). Тогда двоичное . число X должно быть равно 1111100111. Обозначим через У1, У2, УЗ и У4 управлякяцие сигналы, формирующиеся соответственно на выходе элемента 12 задержки, элемента И 9, элемента ИЛИ 10 и на нулевом выходе триггера 7. Процесс такого преобразования иллюст.рируется таблицей. Заметим, что старший разряд регио ра 1 в процессе суммирования участия не принимает, так как он не подключен к входам сумматора 2 основания.В указанный разряд записывается перенос, формирующийся на сумматоре 2 основания. В процессе преобразования в каждом нечетном цикле по сигналу У1 осуществляется циклический сдвиг информации в регистре числа влево, а в кажом четном - вправо. Обоснование технико-экономической эффектичности проводится по отношению к базовому объекту. Аппаратурные затраты на предлагаемое устройство оценим в суммарном числе двоичных разрядов регистров, сумматоров и счетчика, т.е. будем считать, что стоимость одного разря/,

да регистра, сумматора и счетчика примерно одинакова.

Узлы предлагаемого устройства имеют следующую длину в двоичных разрядах: регистр 1 числа 1 - т-К + 1, сумматор 2 основания - т, регистр

3основания - т, счетчик 6 - llogq |(K-1)m + l , накапливающий сумматор 5 - (K-1)m + l, регистр

4константы - logj((K-1)m + IjCУчитывая, что накапливающий сумматор 5 является композицией регистра и комбинационного сумматора, т.е. условная стоимость составляет

2jlog l CK-Dm +1j , для предлагаемого устройства получим С 2т + тК + 1 + (K-1)m + l.

Следовательно, введение новьсх элементов и конструктивных связей поз-воляет уменьшить аппаратурные затра15045S

ты на построение устройства в М . GI ЗКга + L..-.m Ci 2iiH iiik+1+4}rog,j|(K-T) Например, при построении преобразова5 теля для перевода в двоичную систему счисления 10-разрядных чисел с основанием Р 15, т.е. при К 10 и m 4, получим выигрьш в аппаратуре в

167

Cl

2 раза. 73

Оценка аппаратуры, выполнялась из предположения, что для построения устройств используются микросхемы с малой степенью интеграции.

При использовании средних и -больших интегральных схем преимущества предлагаемого устройства проявляются в большей степени.

0111110011100

0011111001110 0001111100111

Результат

1111 0000

+ 1100

оТбо

J

0100

| название | год | авторы | номер документа |

|---|---|---|---|

| Преобразователь двоичного кода в р-ичный позиционный код | 1983 |

|

SU1163479A1 |

| Преобразователь двоичного кода в двоично-десятичный код | 1978 |

|

SU742923A1 |

| Устройство для умножения чисел с плавающей запятой | 1985 |

|

SU1280624A1 |

| Генератор псевдослучайных чисел | 1980 |

|

SU942014A1 |

| Устройство для преобразования избыточного двоичного кода в код со смешанным основанием | 1975 |

|

SU618737A1 |

| Преобразователь двоичного кода угла в двоично-десятично-шестидесятиричный код | 1980 |

|

SU943703A1 |

| Преобразователь позиционного кода с одним основанием в позиционный код с другим основанием | 1977 |

|

SU734667A1 |

| Преобразователь двоично-К-ичного кода в двоичный код | 1983 |

|

SU1126946A1 |

| Преобразователь линейного позиционного кода в двоичный код | 1980 |

|

SU935944A1 |

| Цифровой нелинейный масштабирующий преобразователь | 1981 |

|

SU1057953A1 |

ПРЕОБРАЗОВАТЕЛЬ р-ИЧНОГО ПОЗИЦИОННОГО КОДА В ДВОИЧНЫЙ КОД, содержащий накопительный сумматор, регистр основания, сумматор основания и сдвиговый регистр, вxoды log p старших разрядов которого, начиная со второго, соединены соответственно с разрядными выходами сумматора основания, первая группа входов которого соединена с соответствующими выходами сдвигового регистра, a вторая группа входов сумматора основания с выходами регистра основания, отличающийся тем, что, с целью упрощения преобразователя, он содержит элемент И, элемент ИЛИ, первый и второй элементы задержки, ре-, .гистр константы, счетчик и триггер, счетный вход которого соединен с выходом переполнения счетчика, информационные входы которого соединены с выходами накопительного сумматора, информационные входы которого соединены с выходами регистра константы, a управляющий вход накопительного сумматора - с нулевым выходом триггера, с входом сдвига влево сдвигового регистра и через первый элемент задержки - с первым входом элемента ИЛИ, второй вход которого соединен с единичным выходом триггера, с первым входом элемента И и входом, сдвига вправо сдвигового регистра, вход (Л старшего разряда которого соединен с выходом переноса сумматора основания, a выход старшего разряда соедив нен с вторым входом элемента И, выход которого соединен с входом записи сдвигового регистра, a третий вход элемента И - с тактовым входом преобразователя и через второй элемент задержки - с тактовым входом сдвигового регистра и счетным входом счетчика, вход записи которого соединен с выходом элемента ИЛИ. U1

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Преобразователь кодов | 1973 |

|

SU526884A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Преобразователь кодов | 1973 |

|

SU467343A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1984-09-23—Публикация

1983-03-05—Подача