регистра результата соединен с выходом второго элемента И и первым входом элемента ИЩ, выход которого соединен с входом сдвига регистра аргумента, третьим входом третьего эле1115051

мента И и счетным входом счетчика циклов, вход записи кода регистра результата соединен с вторым входом элемента ИЛИ и выходом переполнения счетчика задержки.

| название | год | авторы | номер документа |

|---|---|---|---|

| Цифровой генератор функций | 1981 |

|

SU1035594A1 |

| Устройство для возведения в степень | 1976 |

|

SU744556A1 |

| Устройство для возведения в квадрат | 1975 |

|

SU606156A1 |

| Устройство для вычисления квадратного корня | 1983 |

|

SU1141407A1 |

| Устройство для деления чисел | 1981 |

|

SU1012241A1 |

| Арифметическое устройство | 1977 |

|

SU669353A1 |

| Устройство для вычисления квадратного корня | 1987 |

|

SU1481753A1 |

| Вычислительное устройство | 1986 |

|

SU1432510A1 |

| Устройство для вычисления @ | 1983 |

|

SU1156067A1 |

| Устройство для вычисления квадратного корня | 1981 |

|

SU1008736A1 |

УСТРОЙСТВО ДЛЯ ВЫЧИСЛЕНИЯ КВАДРАТА ЧИСЛА,содержащее регистр аргумента,регистр результата,сумматор,первую и вторую группы элементов И, группу элементов ИЛИ, генератор импульсов, первый входы i -х .элементов группы (i 1, П -2, где п разрядность . аргумента) соединены с выходами i -х элементов И первой группы, вторые входы 1 -X элементов ИЛИ группы соединены с выходами i -х элементов И второй труппы, выходы i-X элементов ИЛИ группы соединены с входами (i + +1)-х разрядов первого слагаемого сумматора, разрядные выходы которого соединены соответственно с разрядными .входами регистра результата, выходы -X разрядов которого ( Г, 2п-4) соединены с входами ( )-х разрядов второго слагаемого сумматора, i-e разрядные выходы регист1ра аргумента соединены с первыми входами ч-X элементов И первой группы, и-е разрядные выходы регистра аргумента (к. 2, п-2) соединены с прямыми входами

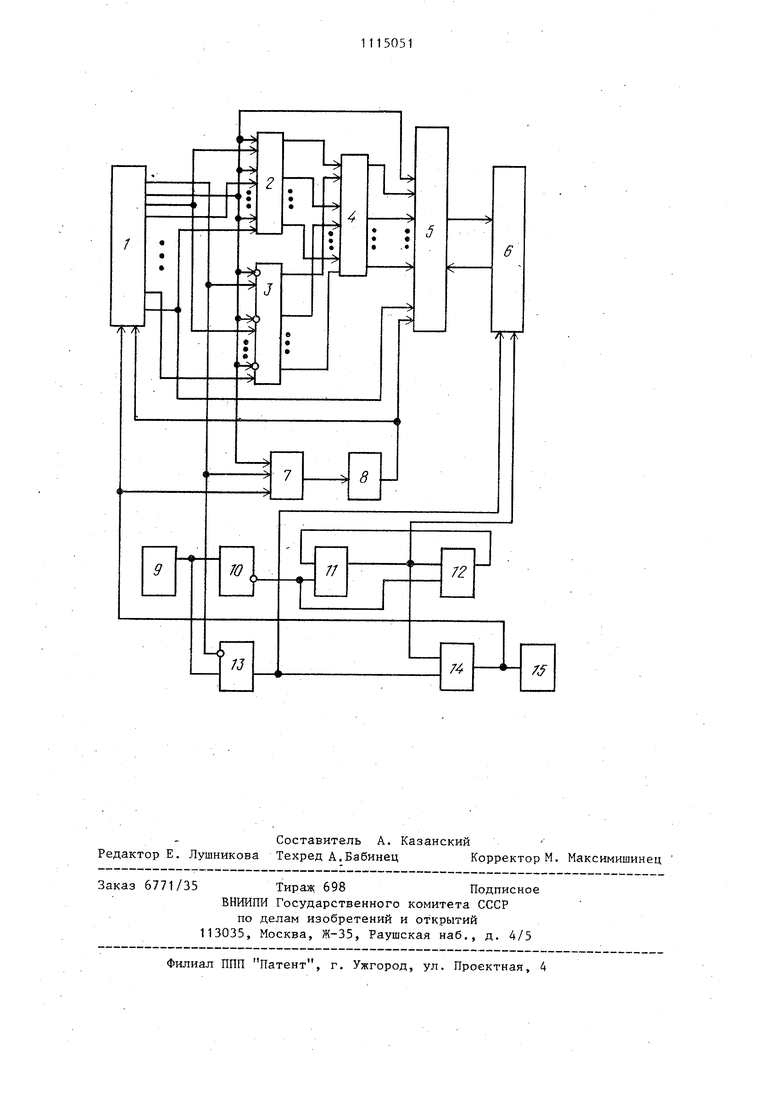

Изобретение относится к вычислительной технике и может быть применено в цифровых вычислительных машинах и устройствах. Известно устройство для вычислени квадрата числа, содержащее рвоичный счетчик, элементы И и сумматор. Устройство предназначено для вычисления квадрата числа, представленного число-импульсным кодом 13. Недостатком устройства является низкое быстродействие, например, для возведения в квадрат числа, равного N, необходимо выполнить N сложен1й. Наиболее близким техническим решением к предлагаемому является устройство, содержащее регистры операндов, результата, сумматор, сдвигатель, блок управления. Сдвигатель предназначен для выдачи кода с выхода регистра первого операнда на входы сумматора без сдви га, либо со сдвигом элементов И и группы элементов ИЛИ. Выходы -i -X элементов И обеих гру подключены к входам i-го элемента ИЛИ. Первый вход 1 -го элемента И первой группы связан с выходом - -го разряда регистра первого операнда, а первый вход i-ro элемента И второ группы подключен ко входу (i-1) раз ряда регистра первого операнда. Таким образом, код с выхода регистра первого операнда передается на вход сумматора без сдвига через элементы И первой группы и со сдвигом влево через элементы И второй группы. К вторым входам элементов И первой группы подключена управляющая шина (Выдача кода) блока управления, а к втсрым входам элементов И второй группы подключены управляющая шина (Выдача кода и сдвиг) блока управления. Вычисление производится умножением .х. При этом множитель представляется с помощью цифр 4 О, l|; группы разрядов множителя вида О11...10, преобразуют в группы вида 10000...J, что позволяет уменьшить среднее число суммированийвычитаний. Для вычисления производится в среднем - операций 1 сдвига и - И операций суммированиявычитания 2. Недостатком известного устройства является низкое быстродействие. Время вычисления квадрата числа составляетt-n |tc-b {i где tc - время операции сдвига; fJ - время операции сложения. Цель изобретения - повышение быстродействия устройства. Поставленная цель достигается тем, что в устройство для вычисления квадрата числа, содержащее регистр аргумента, регистр результата, сумматор, первую и вторую группы элементов И, группу элементов ЖИ, генератор импульсов, первые входы -1 -х элементов ИЛИ группы (, п-2, где п разрядность аргумента) соединены с выходами i-X элементов И первой группы, вторые входы i-х элементов ИЛИ группы соединены с выходами 1 -X элементов И второй группы; выходы i-X элементов ИЖ группы соединены с входами (i+O-x разрядов первого слагаемого сумматора, разрядные выходы которого соединены соответственно с разрядными входами регистра результата -х разрядов которого (j 1, 2п-4) соединены, с входами (j+2)-x разрядов второго слагаемого сумматора, i -е разрядные выходы регистра агрумента соединены с первыми входами i -х элементов И первой группы, к. -е разрядные выходы регистра аргумента (iC 2,n-2) соединены с входами (п-1}-х элементов второй группы, выход п-го разряда регистра аргумента соединен с прямым входом h-2 элемента И второй группы дополнительно введены триггер, первый, второй и третий элементы И, элемент НЕ, элемент ИЛИ, счетчик циклов, счетчик задержки, выход переполнения которого соединен с первым входом первого элемента И, выход которого соединен с входом установки нуля счетчика задержки, тактовый вход которого соединен с вторым входом первого элемента И и выходом элемента НЕ, вход которого соединен с выходом генератора импульсов и пря мым входом второго элемента И, инвер сный вход которого соединен с первым входом третьего элемента И и выходом старшего разряда регистра аргумента, выход (n-l)-ro разряда которого соединен с инверсными входами элементов И второй группы, вторыми входами элементов И первой группы, входом первого слагаемого п-го разряда сумматора и вторым входом треть его элемента И, выход которого соединен со счетным входом триггера, выход которого соединен с входом первого слагаемого младшего разряда сумматора и входом вьщачи кода регистра аргумента, вход второго слагаемого младшего разряда сумматора соединен с выходом младшего разряда сумматора соединен с выходом младшего разряда регистра аргумента, вход сдвига информации регистра результата соединен с выходом второго элемента И и первым входом элемента ИЛИ, выход которого соединен с входом сдвига регистра аргумента, треть им входом третьего элемента И и счет ным входом счетчика циклов, вход записи кода регистра результата соединен с вторым входом элемента ИЛИ и выходом переполнения счетчика задержки. На чертеже представлена блок.схема устройства. Устройство для вычисления квад.рата числа содержит регистр 1 аргумента, первую группу элементов И 2, вторую группу элементов И 3, группу 0514 элементов ИЛИ 4, сумматор 5, регистр 6 результата, элемент И 7, триггер 8, генератор 9 импульсов, элемент . НЕ 10, счетчик 11 задержки, элемент И 12, элемент И 13, элемент ИЛИ 14, счетчик 15 циклов. В качестве регистра 1 аргумента используется сдвигающий регистр, имеющий цепь сдвига влево на один разряд. В регистре 1 аргумента предусмотрена вьщача прямого кода содержимого регистра 1 аргумента, если на цепь выдачи кода подается нулевой сигнал (триггер 8 в нулевом состоянии), и выдачи обратного кода, если на цепь выдачи кода подается единичный сцгнал с выхода триггера 8. Сумматор 5 содержит {2li-2) разрядов и может быть построен в виде комбинационного сумматора, причем, в двух младших и (п-2) старших раз- рядах можно использовать полусумматоры. Это связано с тем, что на входы, двух младших разрядов не подается в качестве второго слагаемого содержимое регистра 6 результата, а на входы (п-2) старших разрядов подается только одно слагаемое с выходов регистра 6 результата. Нужно заметить, что в качестве второго слагаемого для младшего разряда -сумматора 5 используется сигнал с выхода счетного триггера 8, но так как в младший разряд не подается сигнал переноса, то он также может быть реализован на основе полусумматора. Регистр 6 результата построен на основе триггеров с внутренней задержкой, прием информации в которые осуществляется только после окончания сигнала приема кода. В регистре 6 результата предусмотрена цепь сдвига кода результата на два разряда влево по управляющему сигналу с выхода элемента И 13. Счетчик 11 задержки представляет собой счетчик с коэффициентом пересчета, где 1сл время сложения в сумматоре 5; t(j - время сдвига кодов в регистре 1 аргумента и регистре 6 результата. Управляющий вход счетчика 11 задержки представляет собой цепь установки в О счетчика (сигналом с выхода элемента И 12). . S Счетчик 15 циклов представляет собой счетчик с коэффициентом перес чета К4 /2, ecjifi п- четное число или К п/2+0,5, если и нечетное число. Устройство предназначено для получения п старших разрядов z х. Вес младшего разряда результата равен 2 в том случае, если операнд целое п разрядное число. Устройство работает следующим образом. В исходном состоянии в регистре 1 аргумента находится исходное число х; регистр 6 результата, триггер 8, счетчик 11 задержки и счетчи 15 циклов обнулены. С началом вычислений на входы элементов И. 13 и элемента НЕ 10 поступают тактовые импульсы, период которых равен времени сдвига (t,) в регистрах 1 аргумента и результата 6. Операция возведения в квадрат числа Xпроизводится за н/2 тактов работы устройства, для четных И и за п/2+0,5 тактов для нечетныхп . В каждом такте анализируется содержимое старшего разряда регистра 1 аргумента. Если , 0, то на выходах элементов ИЛИ 14, И 13 появляются управляющие сигналы сдвига, которые поступают на цепи сдвига регистров 1 аргумента и результата Кроме того, этим тактовым импульсам (с элемента ИЛИ 14) осуществляется изменение состояния счетчика 15 цик лов на единицу. Содержимое регистра 1 аргумента сдвигается на один разряд, что равн сильно удвоению аргзгмента, а содержимое регистра 6 результата сдвигае ся на два разряда - учетверению результата. Никаких других действий в случае, когда а 0 не производится . В том случае, когда а„, 1 вычис ления производятся в зависимости от значения разряда a.i. Если же а,. (а. , а.1 0), то для ор ганизации вычислений (в цикле) используем формулу ()-2(2Пх,,,х Величина () должна быть просу мирована с учетверенным содержанием регистра 6 результата. 16 Содержимое регистра 1 аргумента передается на суьтматор 5 в прямом или обратном коде, в зависимости от состояния триггера 8. Если триггер-8 находится в нулевом состоянии, то через группу элементов И 3 на сумматор 5 передается содержимое регистра 1 аргумента в прямом коде. По единичному состоянию триггера 8 содержимое регистра 1 аргумента передается обратным кодом через группу элементов И 3 на сумматор 5, кроме этого в младший разряд сумматора 5 (по сигналу с триггера 8) прибавляется единица. Вычисление величины ( )производится схемным образом, т.е. на позицию п-2 разряда сумматора 5 через И-2 элемент группы элементов И 3 передается содержимое старшего п-1 разряда регистра 1 аргумента (это равносильно вычитанию единиць из -го разряда аргумента хО . I Например, если Х 1 ОХХХХХХ, тог,- (Х,--2)0 1 XX X X X X. В этом цикле в первом такте (цикл равен к тактов) срабатывает элемент НЕ 10 и запускается счетчик 11 задержки с коэффициентом пересчета К, на время суммирования величин регистра 1 аргумента и регистра 6 результата на сумматоре 5. По (с-му импульсу (по заднему фронту инверсного тактового импульса с выхода элемента НЕ 10) на выходе счетчика 1Т задержки появляется единичный потенциал (суммирование закончено). В этом такте происходит прием кода на регистр 6 результата с выходов сумматора 5 (по сигналу с выхода счетчика задержки), сдвиг содержимого регистра 1 аргумента (по сигналу с выхода элемента ИЛИ 14) на один разряд влево, а также к содержимому счетчика 15 циклов прибавляется единица. По заднему фронту к-го и}-1пульса происходит срабатывание элемента И 12, на выходе которого появляется единичный потенциал, который является управляющим сигналом -, для счетчика 11 задержки. Счетчик 11 задержки, сбрасывается в нулевое состояние, что влечет за собой отключение элемента И 12. Устройство переходит в след тощий цикл работы, т.е. готово производить вычисления в зависимости от следующих двух старших разрядов аргумента. 7 Если же старшие разряды аргументо применяем формулу x., 2.,-2iuf z-.:, к.учетверенному содержимому регист 6 результата необходимо прибавить величину ). Для получения величины (2x.-2) на выходы сумматора 5 передается через группу элементов И 2 со сдвигом на один разряд влево ., причем старший разряд содержимого регистра аргуме та Хд, игнорируется. Х. 1 1 X X X X, Z;., (2Х.,-2)0 1 X X X X Величина (2Х- -2) поступает на входы сумматора 5 в прямом коде,если триггер 8 находится в нулевом состоян или Bf обратном коде - триггер 8 находится в единичном состоянии. Кроме этого, если состояние триггера 8 единичное, на вход младшего разряда сумматора 5 поступает единичный потенциал с выхода этого триггера; это равносильно прибавлению единицы к обратному коду (2Хц-2). Таким образом формируется дополнение аргумента до числа 2. Также, как и в предыдущем случае (когда а„, aj,, 10), после окончания суммирования на сумматоре 5, происходит срабатывание счетчика 11 задержки с коэффициентом пересчета К к-му импульсу на вы ic518 . ходах счетчика 11 задержки и элемента ИЛИ 14 появляются сигналь приема кода на регистр 6 результата и сдвига кода регистра 1 аргумента, соответственно; счетчик 15 циклов переходит в следующее состояние, а триггер 8 переходит в противоположное состояние. Таким образом, в очередных циклах, до следующего срабатывания триггера 8, на выходы регистра 1 аргумента будет вьздаваться обратный код содержимого регистра 1 аргумента. После окончания rt/2 циклов (момент окончания вычислений определяется по содержимому счетчика циклов 15) в п старших разрядах регистра 6 результата находится искомый результат Время вычислений определяется l,-.1,(V.ilc.) Кроме того, уменьшается время вычислений в i () . MAb /btcA Пусть t 2tc; тогда введение трех элементов И, триггера, счетчика задержки, счетчика циклов, элемента ИЛИ позволяют увеличить быстродействие устройства в два раза.

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Квадратор | 1978 |

|

SU769537A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Самофанов К.Г., Корнейчук В.И | |||

| и Тарасенко В.П | |||

| Электронные цифровые вычислительные машины | |||

| Кие-в, Вища школа, 1976, рис | |||

| СПОСОБ ПОЛУЧЕНИЯ ЧИСТОГО ГЛИНОЗЕМА И ЕГО СОЛЕЙ ИЗ СИЛИКАТОВ ГЛИНОЗЕМА, ПРОСТЫХ ГЛИН И. Т.П. | 1915 |

|

SU280A1 |

Авторы

Даты

1984-09-23—Публикация

1983-06-01—Подача