мента И и- подключены к выходу сигнала конца умножения блока умножения, выход третьего элемента задержки блока управления соединен с первым входом обнуления регистра результата и подключен через пятый элемент задержки к второму входу первого элемента ИЛИ и первому входу разрешения записи первого коммутатора, третий и четвертый входы первого элемента ИЛИ соединены соответственно с выходом восьмого элемента И. и шестого элемента задержки, вход которого подключен к входу запуска устройства и к второму входу разрешения за писи первого коммутатора, выход шестого--элемента задержки объединен с вторым входом первого триггера и подключен к входу разрешения записи регистра показателя степени, вход которого соединен с входом показателя степени устройства, а выход - с входом дешифратора- нуля, выходы второго и четвертого элементов задержки подключены соответственно к первому и второму входам разрешения- записи второго коммутатора, первый информационный вход которого непосредственно, а второй через регистр сомножителя и информационный вход вспомогательного регистра подключены к вы- . ходу регистра результата, выход вспомогательного регистра подключен к первому информационному входу первого коммутатора и к входу первого сомножителя блока умножения, вход второго сомножителя которого соединен с выходом регистра основания, первый и второй управляющие входы которого подключены соответственно к выходу обнуления блока умножения и выходу пятого элемента ИЛИ блока управления, выходы четвертого элемента ИЛИ и элемента 2И-ИЛИ которого соединены соответственно с входом разрешения записи регистра сомножителя и выходом окончания операции устройства, выходы второго и первого коммутаторов соединены с информационными входами соответственно регистра основания и регистра результата, второй вход обнуления которого подключен к первому управляющему выходу блока умножения, второй управляющий выход которого соединен с третьим входом разрешения записи первого коммутатора, второй и третий информационные входы которого подключены соответственно к входу основания устройства и четвертому управляющему выходу блока умножения, пятый управляющий выход которого соединен с В ходом разрешения записи вспомогательного регистра.

2, Устройство по п. 1, о т л ичающееся тем, что блок ум ножения содержит цепочку из четырех

последовательно соединенных элементов задержки, блок памяти и триггер, единичный и нулевой входы КОТОРОГО соединены соответственно с выходами первого и третьего элементов задержки, а выход - с входом запуска блока памяти, вход первого и второго адресов которого являются входами соответственно первого и второго сомножителей блока умножения, а выход блока памяти соединен с четвертым управляющим выходом блока умножения, вход первого элемента задержки соединен с входом запуска блока умножения и является пятым управляющим выходом блока, а выходы- nepBofo, второго, третьего и четвертого элементов задержки подключены к первому, второму и третьему управляющим выходам и выходу сигнала конца умножения блока соответэтвенно,

3. Устройство для. возведения в степень, содержащее регистр основани вспомогательный регистр, блок управления и накапливающий сумматор, выход которого является выходом устройства, отличающееся тем, что, с целью повышения быстродействия, в него введены регистр сомножителя, регистр показателя степени, блок умножения, два коммутатора и дешифратор нуля, а блок управления содержит формирователь импульсов три триггера, девять элементов И, пять элементов ИЛИ, шесть элементов задержки, два элемента НЕ, элемент 2И-ИЛИ, причем инверсный выход первого триггера соединен с первыми .входами соответственно первого и второго элементов И, вторые входы которых подключены к выходу третьего элемента И, первый вход которого и первый вход четвертого элемента И подключены к входу сдвига регистра показателя степени и через формирователь импульсов к выходу первого элемента. ИЛИ, первый вход которого объединен с первым входом первого триггера и подключен к выходу пятого элемента И, первый вход которого через первый элемент задержки соединен с выходом первого элемента И и с первым входом элемента 2И-ИЛИ, второй и третий входы которого соединены с выходом дешифратора нуля и через первый элемент НЕ с вторым входом пятого и первым выходом шестого элементов И, второй вход которого и четвертый вход элемента 2И-ИЛИ подключены к. выходу седьмого элемента И, первый вход которого соединен с прямым выходом второго триггера, инверсный выход которого подключен к первому входу восьмого элемента И, второй вход которого и первый вход девятого элемента И соединены

соответственно с инверсным и прямым выходами третьего триггера, первый вход которого и первый вход второго элемента ИЛИ подключены к выходу второго элемента И, второй вход третьего элемента И соединен с выходом младшего разряда регистра пок зателя степени и fepea второй элемент НЕ с вторым входом четвертого элемента И, выход которого соединен с вторыми входами второго элемента ИЛИ и третьего триггера, третий вход которого объединен с первым входом третьего элемента ИЛИ и чере второй элемент задержки соединен с выходом.девятого элемента И и первым входом второго триггера, второй вход которого через третий элемент задержки соединен с выходом шестого элемента И и с первым входом четвертого элемента ИЛИ, вторым входом соединенного с выходом пятого элемента И, выход третьего элемента ИЛИ соединен с входом запуска блка умножения, выход второго элемента ИЛИ через четвертый элемент задержки соединен с вторым входом третьего элемента ИЛИ и непосредственно - с первым входом пятого элемента ИЛИ, вторым входом подключенного к выходу девятого элемента И, второ вход которого и третий вход восьмого элемента И объединены с вторым входом седьмого элемента И и подключены к выходу сигнала конца умножения блока умножения, выход третьего элемента задержки блока управления соединен с первым входом обнуления накапливающего сумматора и подключе через пятый элемент задержки к второму входу первого элемента ИЛИ и первому входу разрешения записи первого коммутатора, третий и четве тый входы первого элемента ИЛИ соединены соответственно с выходом восьмого элемента И и шестого элемента задержки, вход которого подключен к входу запуска устройства и к второму входу разрешения записи первого коммутатора, выход шестого элемента задержки объединен с вторым входом первого триггера и подключен к входу разрешения записи регистра показателя степени, вход которого соединен а входом показателя степени устройства, а выход с входом дешифратора нуля, выходы второго и четвертого элементов задержки подключены соответственно к первому и второму входам разрешения записи Второго коммутатора, первый информационный вход которого непосредственно, а второй через ре,гистр сомножителя и информационный вход вспомогательного регистра под ключены к выходу накапливающего сумматора, выход вспомогательного регистра подключен к первому информационному входу первого коммутатора, первый и второй управляющие входы регистра основания подключены соответственно к выходам циклического и однократного сдвига блока умножения, вход обнуления регистра основания соединен с выходом пятого элемента ИЛИ блока управления, выходы четвертого элемента ИЛИ и элемента 2И-ИЛИ которого соединены соответ ственно с входом разрешения записи регистра сомножителя и выходом окончания операции ус.тройства, выходы второго и первого Коммутаторов соединены с информационными входами регистра основания и накапливающего сумматора, второй вход обнуления и вход сложения которого подключены к первому и второму управляющим выходам блока умножения, третий ynpiaBляющий выход которого соединен с третьим входом разрешения записи первого коммутатора, второй и третий информационные входы которого подключены соответственно к входу основания устройства и выходу регистра основания, четвертый и пятый управляющие выходы блока умножения соединены с первым и вторым входами сдвига вспомогательного регистра, выход старшего разряда которого подключен к управляющему входу блока умножения первый и второй тактовые входы блока умножения соединены с соответствующими тактовыми входами устройства. 4. Устройство по п. 3, отличающееся тем, что блок умножения содержит счетчик по модулю, триггер, два элемента И и элемент задержки, вход которого соединен с. входом запуска блока умножения и четвертым управляющим выходом блока выход элемента задержки подключен к единичному входу триггера; к перво му управляющему выходу и выходу однократного сдвига блока, нулевой вход триггера соединен с выходом счетчика по модулю и явд1яется выходом сигнала конца умножения блока, счетный вход счетчика по модулю подключен к выходу первого элемента И, выходу циклического.сдвига и пятому управляющему выхЬд л блока, первый вход первого элемента И соединен с выходом триггера и первым входом второго элемента И, второй вход которого и второй вход первого элемента И подключены соответственно к первому и второму тактовым входам блока, третий вход второго элемента И соединен с управляющим входом блока, выход второго элемента И подключен к второму и третьему управляющим входсзм блока.

Изобретение относится к-цифровой вычислительнбй технике и может быть применено при аппаратной реализации операции возведения в степень в ЦВМ и системах управления и регулирования.

Известно устройство для возведения в степень, содержащее (N+2) регистра управления и (N-l) сумматоров (N - максимально допустимый для данного устройства показатель сте;пени) 1J .

Недостатком указанного устройства является большой расход оборудова ния.

Наиболее близким к предлагаемому является устройство для возведения в степень, содержащее регистр основа ния, вспомогательный регистр группы элементов И, элемент ИЛИ, блок управ ления, регистр результата и накапливающий сумматор,выход которого является выходом устройства 2 .

Однако известное устройство харак теризуется недостаточным быстродействием.

Цель изобретения - повышение быстродействия устройства.

Поставленная цель достигается тем что в устройство для возведения в степень по первому варианту, содержащее регистр основания, вспомогательный регистр, блок управления и регистр результата, выход которого является выходом устройства, введены регистр сомножителя, регистр показателя степени, блок умножения, два коммутатора и дешифратор нуля, а блок управления содержит формирователь импульсов, три триггера, девять элементов И, пять элементов ИЛИ шесть элементов задержки, два элемента НЕ, элемент 2И-ИЛИ, причем инверсный выход первого триггера соединен с первыми входами соответсттвенно первого и второго элементов И, вторые входы которых подключены к выходу третьего элемента И, первый вход которого и первый вход четвертого элемента И подключены к входу сдвига регистра показателя степени и через формирователь импульсов к выходу первого элемента ИЛИ, первый вход которого объединен с первым входом первого триггера и подключен к выходу пятого элемента И, первый вход которого через первый элемент задержки соединен с выходом первого элемента И и с первым входом элемента 2И-ИЛИ, второй и третий входы которого соединены с выходом дешифратора нуля и через первый элемент НЕ с вторым входом пятого и первым входом шестого элементов И, второй вход которого и четвертый вход элемента 2И-ИЛИ подключены к выходу седьмого элемента И, первый вход которого соединен с прямым выходом второго триггера, инверсный выход которого подключен к первому входу восьмого элемента И, второй вход которого и первый вход девятого элемента И соединены соответственно с инверсным и прямым выходами третьего триггера, первый вход которого и первый вход второго элемента ИЛИ подключены к выходу второго элемента И, второй вход третьего элемента И соединен с выходом младшего разряда регистра показателя степени и через второй элемент НЕ с вторым входом четвертого элемента И, выход которого соединен с вторыми .входами второго элемента или и третьего триггера, третий вход которого объединен с первым входом третьего элемента ИЛИ и через второй элемент задержки соединен с входом девятого элемента И и первым входом второго триггера, второй вход которого через третий элемент задержки соединен с выходом шестого элемента И и с первым входом четвертого элемента ИЛИ, вторым вхо дом соединенного с выходом пятого элемента И, выход третьего элемента ИЛИ соединен с входом запуска блока умножения, выход второго элемента ИЛИ через четвертый элемент задержки соединен с вторым входом третьего элемента ИЛИ и непосредственно - с первым входом пятого элемента ИЛИ, вторым входом подключенного-к выходу девятого элемента И, второй вход которого и третий вход восьмого элемента И объединены с вторым входом седьмого элемента. И и подключены к выходу сигнала конца умножения блока умножения, выход третьего элемента задержки блока управления соединен с первым входом обнуления регистра результата и подключен через пятый элемент задержки к второму входу первого элемента ИЛИ.и первому входу разрешения записи первого коммутатора, третий и четвертый входы первого элемента ИЛИ соединены соответственно с выходом восьмого элемента И и шестого элемента задержки, вход которого подключен к входу запуска устройства и к второму входу разрешения записи первого коммутатора, выход шестого элемента задержки объединен с вторым входом первого триггера и подключен к входу разрешения записи регистра показателя степени, вход которого соединен с входом показателя степени .устройства, а выход - с входом дешифратора нуля, выходы второго и четвертого элементов задержки подключены соответственно к первому и второму входам разрешения записи второго коммутатора, первый информационный вход которого непосредственно, а второй

через регистр сомножителя и информационный вход вспомогательного регист ра подключены к выходу регистра результата, выход вспомогательного регистра подключен к первому информационному входу первого коммутатора и к входу первого сомножителя блока умножения, вход второго сомножителя которого соединен с выходом регистра основания, первый и второй управляющие входы которого подключены ссютветственно к выходу обнуления блока умножения и выходу пятого элемента ИЛИ блока управления, выходы четвертого элемента ИЛИ и элемента 2И-ИЛИ которого соединены соответственно с входом разрешения записи регистра сомножителя и выходом окончания операции устройства, выходы второго и первого коммутаторов соединены с информационными вхо дами соответственно регистра основания и регистра результата, второй вход обнуления которого подключен к первому управляющему выходу блока умножения, второй управляющий выход которого соединен с третьим входом разрешения записи первого коммутатора, второй и третий информционные входы которого подключены соответственно к входу основания устройства и четвертому управляющему выходу блока умножения, пятый управляющий выход которого соединен с входом разрешения записи вспомогательного регистра.

Кроме того, блок умножения содержит цепочкуиз четырехпоследовательно соединенных элементов задержки, блок памяти и триггер, единичный и нулевой входы которого соединены соответственно с выходами первого и третьего элементов задержки, а выход - с входом запуска блока памяти, вход первого и второго адресов которого являются входами соответственно первого и второго сомножителей блока умножения, а выход блока памяти соединен с четвертым управляющим выходом блока умножения, вход первого элемента задержки соединен с входом запуска блока умножения и является пятым управляющим выходом блока, а выходы первого, второго, третьего и четвертого элементов задержки подключены к первому, второму и третьему управляющим выходам и выходу сигнала конца умножения блока соответственно.

Поставленная цель достигается тем, что в устройство для возведения в степень по второму варианту, содержащее регистр основания, вспомогательный регистр, блок управления и накапливающий сумматор, выход -которого является выходом устройства, введены регистр сомножит-еля, регистр показателя степени, блок умножения, два коммутатора и дешифратор нуля, а блок управления содержит формирователь импульсов, три триггера, девять элементов И, пять элементов ИЛН, шесть элементов задержки, два элемента НЕ, элемент 2И-ИЛИ, причем инверсный выход первого триггера соединен с первыми входами соответственно первого и второго элементов И, вторые входы которых подключены к выходу третьего элемента И, первый вход которого и первый вход четвертого элемента И подключены к входу сдвига регистра показателя степени и через формирователь импульсов к выходу первого элемента ИЛИ, первый вход которого объединен с первым входом первого триггера и подключен к выходу пятого эле- мента И, первый вход которого через первый элемент задержки соединен с выходом первого элемента И и с первым входом элемента 2И-ИЛИ, второй и третий входы которого соединены с выходом дешифратора нуля и через первый элемент НЕ с вторым входом пятого и первым входом шестого элемента И, второй вход которого и четвертый вход элемента 2И-ИЛИ подключены к выходу седьмого элемента И, первый вход которого соединен с прямым выходом второго триггера, инверсный выход которого подключен к первому входу восьмого элемента И, второй вход которого и первый вход девятого элемента И соединены соответственно с инверсным и прямым выходаили третьего триггера, первый вход которого и первый вход второго элемента ИЛИ подключены к выходу второго элемента И, второй вход третьего элемента И соединен с выходом младшего разряда регистра цоказателя степени и через второй элемент НЕ с вторым входом четвертого элемент та И, выход которого соединен с вторыми входами второго элемента ИЛИ и третьего триггера, третий вход которого объединен с первым входом третьего элемента ИЛИ и через второй элемент задержки соединен с выходом девятого элемента И и первым входом ВТОРОГО триггера, второй вход которого через третий элемент задержки соединен с выходом шестого элемента И и с первым входом четвертого элемента ИЛИ, вторым входом соединенного с выходом пятого элемента И, выход третьего элемента ИЛИ соединен с входом запуска блока умножения, выход второго элемента ИЛИ через четвертый элемент задержки соединен с вторым входом третьего элемента ИЛИ.и непосредственно - с первым входом пятого элемента ИЛИ, вторым входом подключенного к выходу девятого элемента И, второй вход

которого и третий вход восьмого элемента И объединены с вторым входом седьмого элемента Н и подключены к выходу сигнала конца умножения блока умножения, выход третьего элемента задержки блока управления соединен с первым входом обнуления накапливающего сумматора и подключен через пятый элемент задержки к второму входу первого элемента ИЛ и первому эходу резрешения записи первого коммутатора, третий и четветый входы первого элемента ИЛИ соединены соответственно с выходом восьмого элемента И и шестого элемента задержки, вход которого подключе к входу запуска устройства и к второму входу разрешения записи первого коммутатора, выход шестого эле. мента задержки объединен с вторым входом первого триггера и подключен к входу разрешения записи регистра показателя степени, вход которого соединен с входом показателя степени устройства, а выход - с входом дешифратора нуля, выходы второго и четвертого элементов задержки подключены соответственно к первому., и второму входам разрешения записи второго коммутатора, первый информационный вход которого непосредственно, а второй через регистр сомножителя и информационный вход вспомогательного регистра подключены к выходу накапливающего сумматора, выход вспомогательного регистра подключен к первому информационному входу первого коммутатора, первый и второй управляющие входы регистра основания подключены соответственно к выходам циклического и однократного сдвига блока умножения, вход обнуления регистра основания соединен с выходом пятого элемента ИЛИ блока управления, выходы четвертого элемента ИЛИ и эле-. 2И-ШШ которого соединены соответственно с входом разрешения записи регистра сомножителя и выходом окончания операции устройства выходы второго и первого коммутаторов соединены .с информационными входами регистра основания и накапливающего сумматора, второй вход обнуления и вход сложения которого подключены к первому и второму управляющим выходам блока умножения, третий управляющий выход которого соединен с третьим входом разрешения записи первого коммутатора, второй и трети информационные входы которого подклчены соответственно к входу основания устройства и выходу регистра основания, четвертый и пятый управлющие выходы блока умножения соединены с первым и вторым входами сдвига вспомога.тельного регистра, выход

старшего разряда которого подключен к управляющему входу блока умножения, первый и второй тактовые входы блока умножения соединены с соответствующими тактовыми входами устройства .

Кроме того, блок умножения содержит счетчик по модулю, триггер, два элемента И и элемент задержки, вход которого соединен с запуска блока умножения и четвертым управляющим выходом блока, выход элемента задержки подключен к единичному входу триггера, к первому управляющему выходу и выходу однократного сдвига блока, нулевой вход триггера соединен с выходом счетчика по модулю и является.выходом сигнала конца умножения блока, счетный вход счетчика по модулю подключен к выходу первого элемента И, выходу циклического сдвига и пятому управляющему выходу блока, первый вход первого элемента И соединен с выходом триггера и первым входом второго элемента И, второй вход КОТОРОГО и второй вход первого элемента И подключены соответственно к первому и второму тактовым входам блока, третий вход второго элемента И соединен с управляющим входом блока, выход второго элемент.а И подключен к второму и третьему управляющим входам блока.

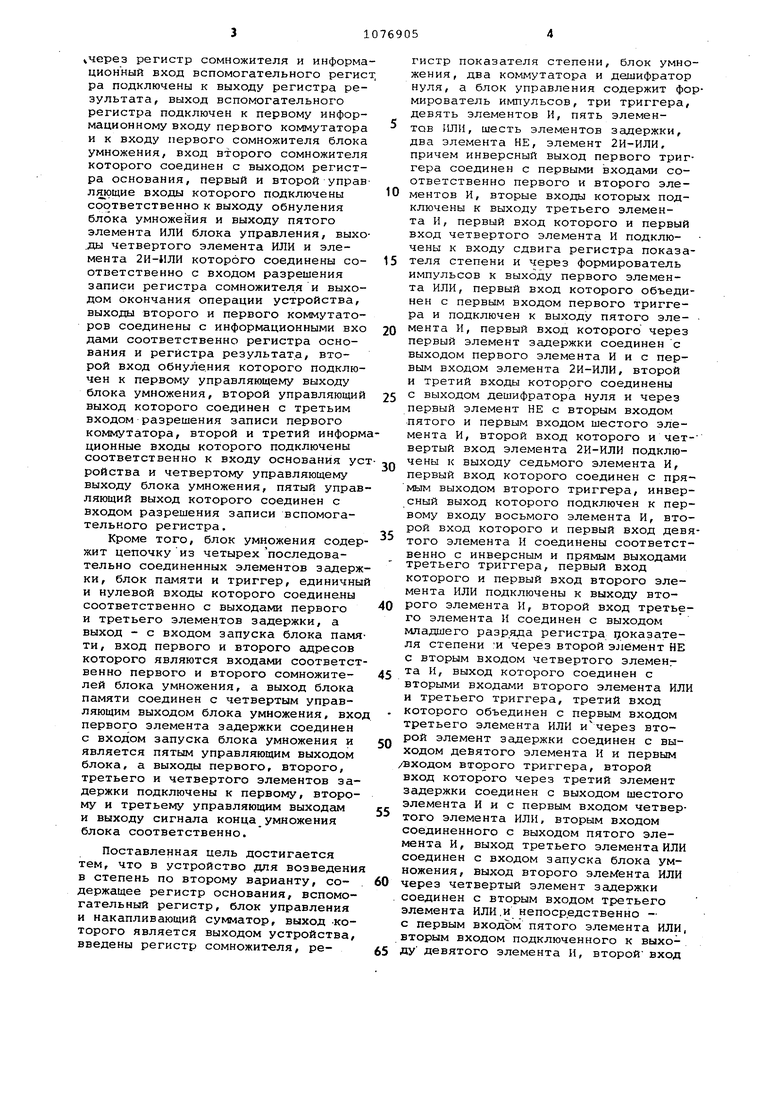

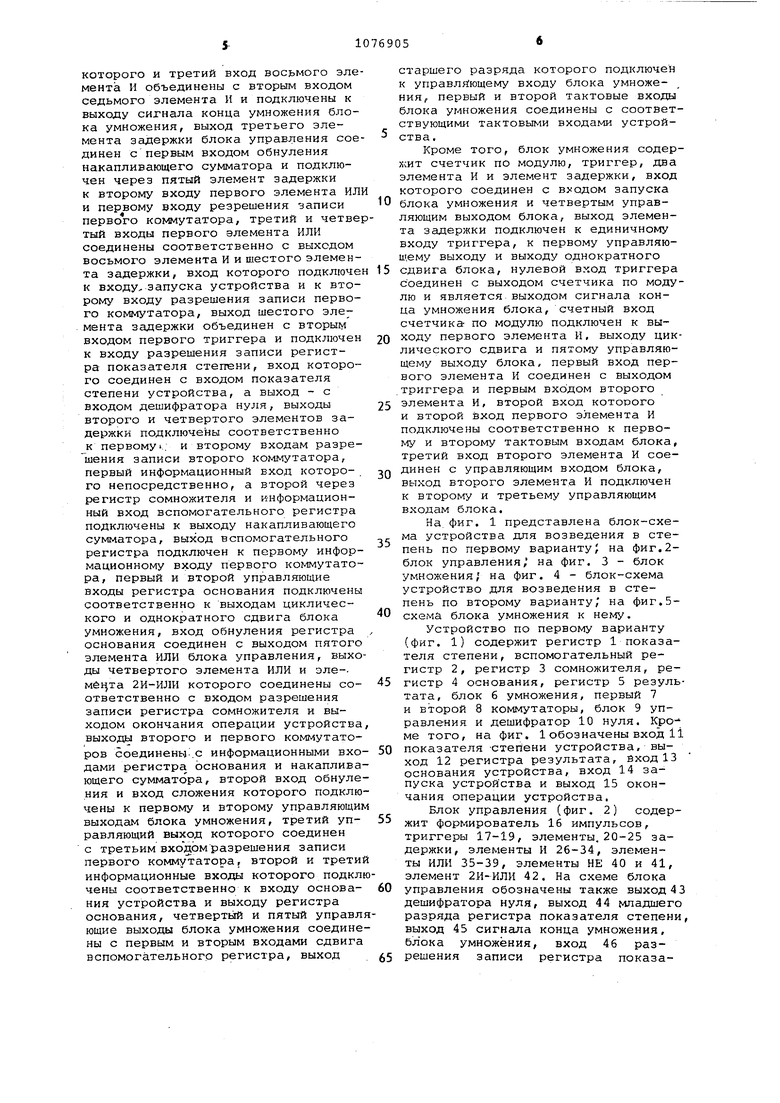

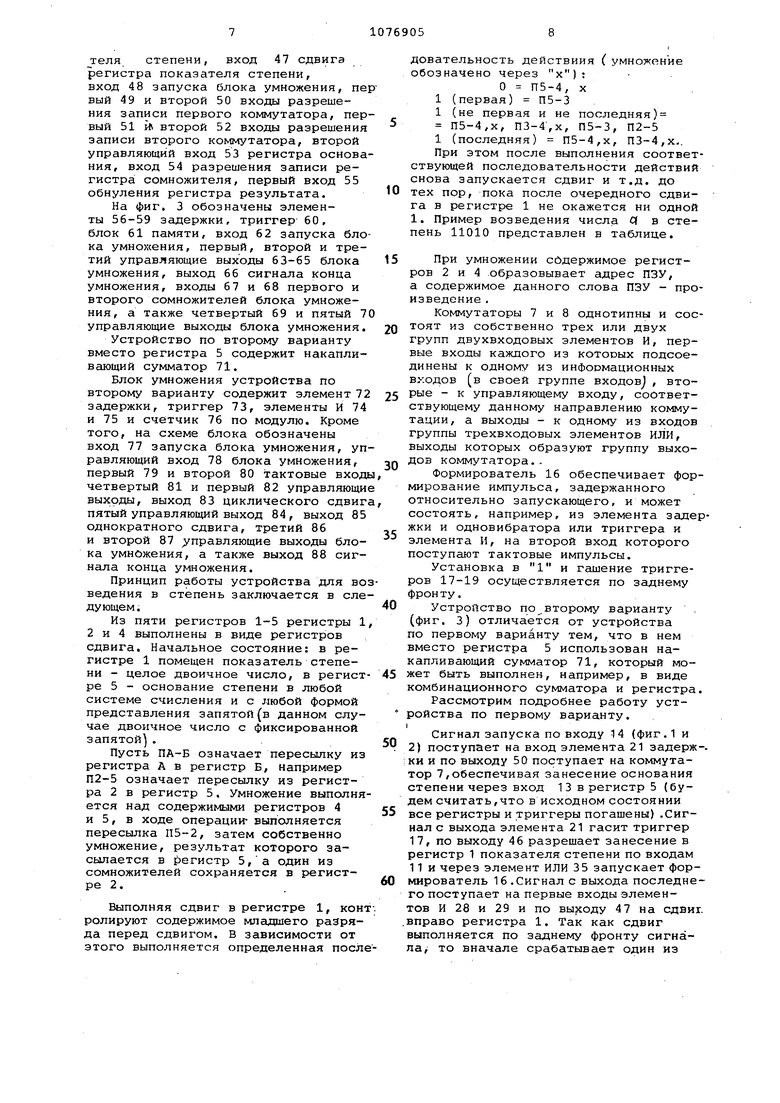

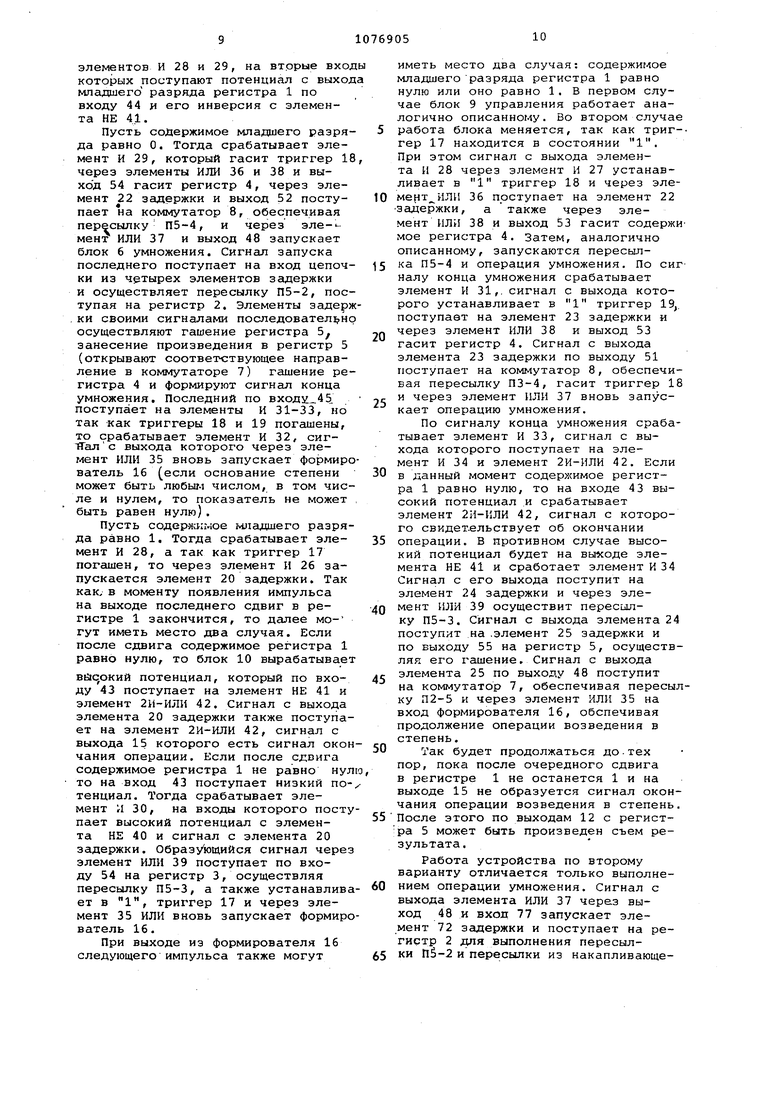

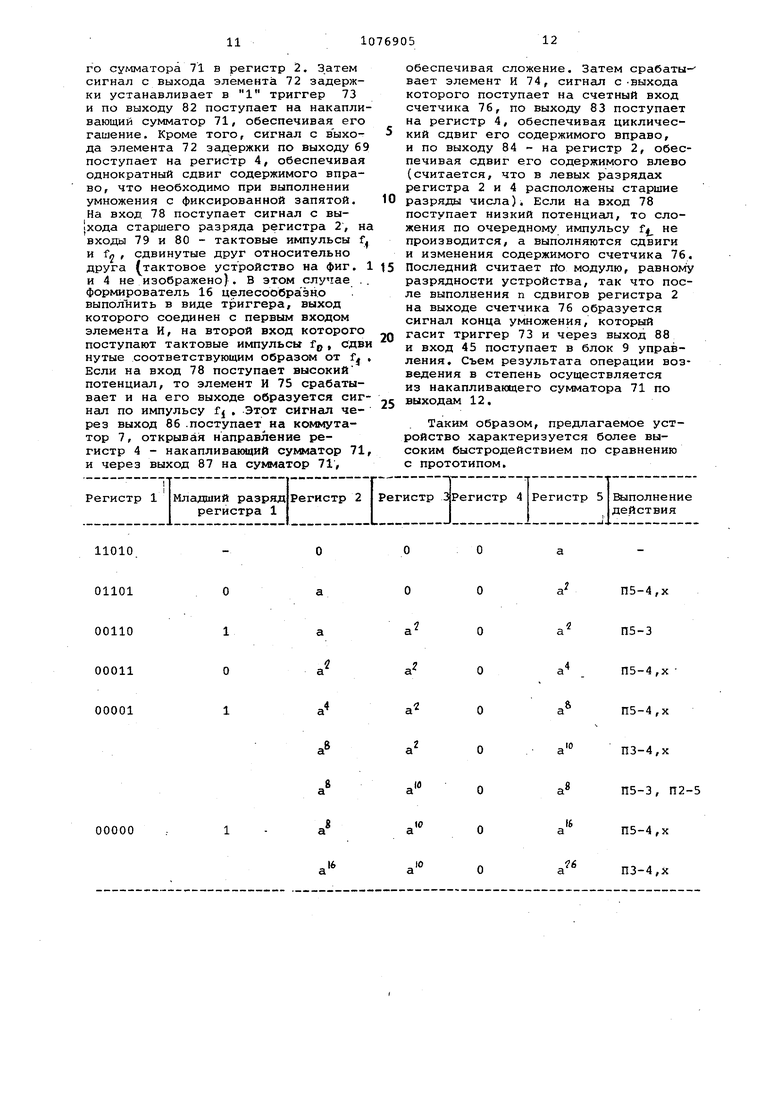

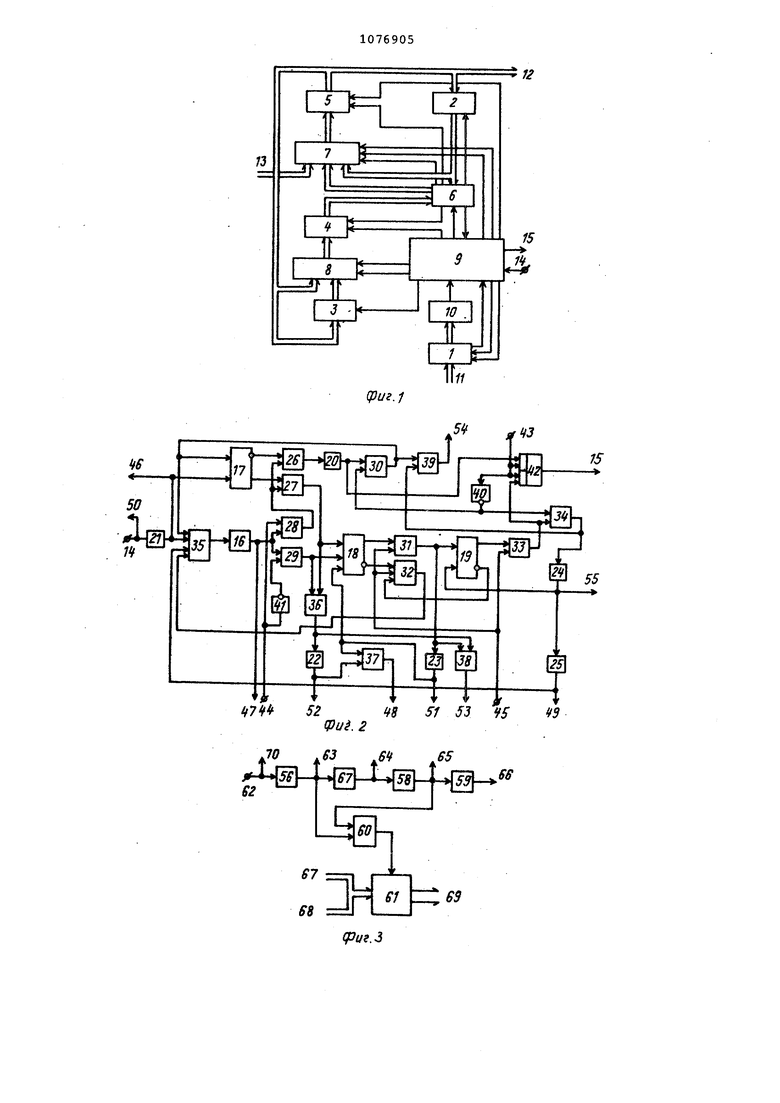

На. фиг. 1 представлена блок-схема устройства для возведения в степень по первому вариантуJ на фиг.2блок управления, на фиг. 3 - блок умножения; на фиг. 4 - блок-схема устройство для возведения в степень по второму варианту, на фиг.5схема блока умножения к нему.

Устройство по первому варианту (фиг. 1) содержит регистр 1 показателя степени, вспомогательный регистр 2, регистр 3 сомножителя, регистр 4 основания, регистр 5 результата, блок 6 умножения, первый 7 и второй 8 коммутаторы, блок 9 управления и дешифратор 10 нуля. Кроме того, на фиг. 1 обозначены вход 11 показателя -степени устройства, выход 12 регистра результата, вход 13 основания устройства, вход 14 запуска устройства и выход 15 окончания операции устройства,

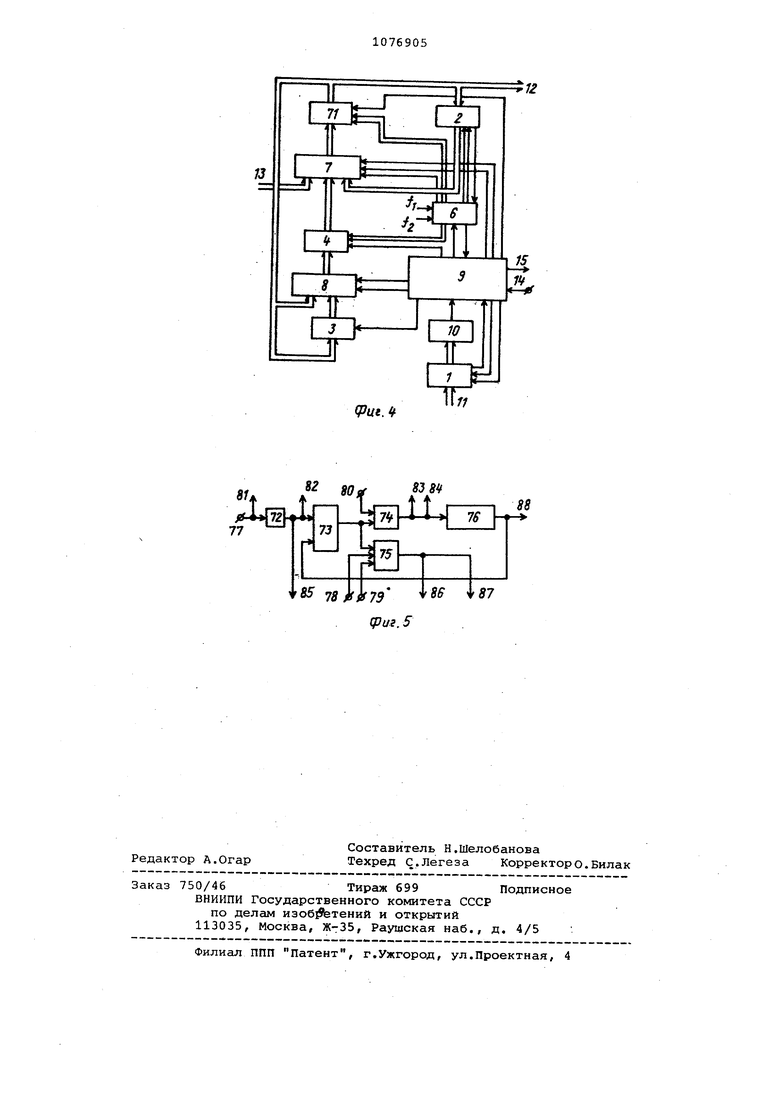

Блок управления (фиг. 2) содержит формирователь 16 импульсов, триггеры 17-19, элементы. 20-25 задержки, элементы И 26-34, элементы ИЛИ 35-39, элементы НЕ 40 и 41, элемент 2И-ИЛИ 42. На схеме блока управления обозначены также выход 43 дешифратора нуля, выход 44 младшего разряда регистра показателя степени вьзход 45 сигнала конца умножения, блЪка умножения, вход 46 разрешения записи регистра показателя степени, вход 47 сдвига регистра показателя степени, вход 48 запуска блока умножения, пе вый 49 и второй 50 входы разрешения записи первого коммутатора, пер вый 51 i второй 52 входы разрешения записи второго колмутатора, второй управляющий вход 53 регистра основа ния, вход 54 разрешения записи регистра сомножителя, первый вход 55 обнуления регистра результата. На фиг. 3 обозначены элементы 56-59 задержки, триггер 60, блок 61 памяти, вход 62 запуска бло ка умножения, первый, второй и третий управляющие выходы 63-65 блока умножения, выход 66 сигнала конца умножения, входы 67 и 68 первого и второго сомножителей блока умножения, а также четвертый 69 и пятый 7 управляющие выходы блока умножения. Устройство по второму варианту вместо регистра 5 содержит накапливающий сумматор 71. Блок умножения устройства по второму варианту содержит элемент 72 задержки, триггер 73, элементы И 74 и 75 и счетчик 76 по модулю. Кроме того, на схеме блока обозначены вход 77 запуска блока умножения, уп равляющий вход 78 блока умножения, первый 79 и второй 80 тактовые вход четвертый 81 и первый 82 управляющи выходы, выход 83 циклического сдвиг пятый управляющий выход 84, выход 85 однократного сдвига, третий 86 и второй 87 управляющие выходы блока умножения, а также выход 88 сигнала конца умножения. Принцип работы устройства для во ведения в степень заключается в сле дующем. Из пяти регистров 1-5 регистры 1 2 и 4 выполнены в виде регистров сдвига. Начальное состояние: в регистре 1 помещен показатель степени - целое двоичное число/ в регист ре 5 - основание степени в любой системе счисления и с любой формой представления запятой (в данном случае двоичное число с фиксированной запятой. Пусть ПА-Б означает пересылку из регистра А в регистр Б, например П2-5 означает пересылку из регистра 2 в регистр 5. Умножение выполня ется над содержимыми регистров 4 и 5, в ходе операции- выполняется пересылка П5-2, затем собственно умножение, результат которого засылается в регистр 5,а один из сомножителей сохраняется в регистре 2. Выполняя сдвиг в регистре 1, кон ролируют содержимое младшего разряда перед сдвигом. В зависимости от этого выполняется определенная посл довательность действиия ( умножение обозначено через х): О П5-4, X 1 (первая) П5-3 1 (не первая и не последняя) П5-4,х, П3-4,х, П5-3, П2-5 1 (последняя) П5-4,х, П3-4,х.. При этом после выполнения соответствующей последовательности действий снова запускается сдвиг и т.д. до тех пор, пока после очередного сдвига в регистре 1 не окажется ни одной 1. Пример возведения числа Of в степень 11010 представлен в таблице. При умножении содержимое регистров 2 и 4 образовывает адрес ПЗУ, а содержимое данного слова ПЗУ - произведение . Коммутаторы 7 и 8 однотипны и состоят из собственно трех или двух групп двухвходовых элементов И, первые входы каждого из КОТОРЫХ подсоединены к одному из информационных входов (в своей группе входов , вторые - к управляющему входу, соответствующему данному направлению коммутации, а выходы - к одному из входов группы трехвходовых элементов ИЛИ, выходы которых образуют группу выходов коммутатора.. Формирователь 16 обеспечивает формирование импульса, задержанного относительно запускающего, и может состоять, например, из элемента задержки и одновибратора или триггера и элемента И, на второй вход которого поступают тактовые импульсы. Установка в 1 и гашение триггеров 17-19 осуществляется по заднему фронту. Устройство полвторому варианту (фиг. 3) отличается от устройства по первому варианту тем, что в нем вместо регистра 5 использован накапливающий сумматор 71, который может быть выполнен, например, в виде комбинационного сумматора и регистра. Рассмотрим подробнее работу устройства по первому варианту. Сигнал запуска по входу 14 (фиг.1 и 2) поступает на вход элемента 21 задерж-ки и по выходу 50 поступает на коммутатор 7,обеспечивая занесение основания степени через вход 13 в регистр 5 (будем считать,что в исходном состоянии все регистры и триггеры погашены) .Сигнал с выхода элемента 21 гасит триггер 17, по выходу 46 разрешает занесение в регистр 1 показателя степени по входам 11 и через элемент ИЛИ 35 запускает формирователь 16.Сигнал с выхода последнего поступает на первые входы элементов И 28 и 29 и по выходу 47 на сдвиг вправо регистра 1. Так как сдвиг выполняется по заднему фронту сигнала, то вначале срабатывает один из элементов И 28 и 29, на вторые вхо которых поступают потенциал с выход младшего разряда регистра 1 по входу 44 ц его инверсия с элемента НЕ 41. Пусть содержимое младшего раэря да равно 0. Тогда срабатывает элемент И 29, который гасит триггер 1 через элементы ИЛИ 36 и 38 и выход 54 гасит регистр 4, через элемент 22 задержки и выход 52 поступает на коммутатор В, обеспечивая пересылку- П5-4, и через элемент ИЛИ 37 и выход 48 запускает блок 6 умножения. Сигнал запуска последнего поступает на вход цепочки из четырех элементов згвдержки и осуществляет пересылку П5-2, поступая на регистр 2. Элементы задерж . ки своими сигналами последовател.н осуществляют гашение регистра 5, занесение произведения в регистр 5 (открывают соответствующее направление в коммутаторе 7) гашение ре гистра 4 и формируют сигнал конца умножения. Последний по входм 45, поступает на элементы И 31-33, но так как триггеры 18 и 19 погашены, то срабатывает элемент И 32, сиг1Яал с выхода которого через элемент ИЛИ 35 вновь запускает формиро ватель 16 (если основание степени может быть любыг- числом, в том числе и нулем, то показатель не может быть равен нулю). Пусть содержимое млгщшего разряда равно 1. Тогда срабатывает элемент И 28, а так как триггер 17 погашен, то через элемент И 26 запускается элемент 20 задержки. Так как, в моменту появления импульса на выходе последнего сдвиг в регистре 1 закончится, то далее могут иметь место два случая. Если после сдвига содержимое регистра 1 равно нулю, то блок 10 вырабатывает вВ1цокий потенциал, который по входу 43 поступает на элемент НЕ 41 и элемент 2И-ИЛИ 42. Сигнал с выхода элемента 20 задержки также поступает на элемент 2И-ИЛИ 42, сигнал с выхода 15 которого есть сигнал окон чания операции. Если после сдвига содержимое регистра 1 не равно нул то на вход 43 поступает низкий потенциал. Тогда срабатывает элемент Л 30, на входы которого посту пает высокий потенциал с элемента НЕ 40 и сигнал с элемента 20 задержки. Образующийся сигнал через элемент ИЛИ 39 поступает по входу 54 на регистр 3, осуществляя пересылку П5-3, а также устанавлива ет в 1, триггер 17 и через элемент 35 ИЛИ вновь запускает формиро ватель 16. При выходе из формирователя 16 следующего импульса также могут иметь место два случая: содержимое младшего разряда регистра 1 равно нулю или оно равно 1. В первом случае блок 9 управления работает аналогично описанному. Во втором случае работа блока меняется, так как триг-гер 17 находится в состоянии 1. При этом сигнал с выхода элемента И 28 через элемент И 27 устанавливает в 1 триггер 18 и через элеме|1т ИЛИ 36 поступает на элемент 22 задержки, а также через элемент ИЛИ 38 и выход 53 гасит содержимое регистра 4. Затем, аналогично описанному, запускаются пересылка П5-4 и операция умножения. По сиг Налу конца умножения срабатывает элемент И 31,. сигнал с выхода которого устанавливает в 1 триггер 19,. поступает на элемент 23 задержки и через элемент ИЛИ 38 и выход 53 гасит регистр 4. Сигнал с выхода элемента 23 задержки по выходу 51 поступает на коммутатор 8, обеспечивая пересылку ПЗ-4, гасит триггер 18 и через элемент ИЛИ 37 вновь запускает операцию умножения. По сигналу конца умножения срабатывает элемент И 33, сигнал с выхода которого поступает на элемент И 34 и элемент 2И-ИЛИ 42. Если в данный момент содержимое регистра 1 равно нулю, то на входе 43 высокий потенциал и срабатывает элемент 2И-ИЛИ 42, сигнал с которого свидетельствует об окончании операции. В противном случае высокий потенциал будет на выходе элемента НЕ 41 и сработает элемент И 34 Сигнал с его выхода поступит на элемент 24 задержки и через элемент ИЛИ 39 осуществит пересылку П5-3. Сигнал с выхода элемента 24 поступит на .элемент 25 задержки и по выходу 55 на регистр 5, осуществляя его гашение. Сигнал с выхода элемента 25 по выходу 48 поступит на коммутатор 7, обеспечивая пересылку П2-5 и через элемент ИЛИ 35 на вход формирователя 16, обспечивая продолжение операции возведения в степень. Так будет продолжаться до.тех пор, пока после очередного сдвига в регистре 1 не останется 1 и на выходе 15 не образуется сигнал окончания операции возведения в степень. После этого по выходам 12с регистра 5 может быть произведен съем результата. Работа устройства по второму варианту отличается только выполнением операции умножения. Сигнал с выхода элемента ИЛИ 37 через выход 48 и вход 77 запускает элемент 72 задержки и поступает на регистр 2 для выполнения пересылки Пё-2 и пересылки из накапливающего сумматора 71 в регистр 2. Затем сигнал с выхода элемента 72 задержки устанавливает в 1 триггер 73 и по выходу 82 поступает на накапливающий сумматор 71, обеспечивая его гашение. Кроме того, сигнал с выхода элемента 72 задержки по выходу 69 поступает на регистр 4, обеспечивая однократный сдвиг содержимого вправо, что необходимо при выполнении умножения с фиксированной запятой. На вход 78 поступает сигнал с вы|хода старшего разряда регистра 2, на входы 79 и 80 - тактовые импульсы f и frt, сдвинутые друг относительно друга (тактовое устройство на фиг. и 4 не изображено). В этом случае . формирователь 16 целесообраэн.о выполнить в виде триггера, выход которого соединен с первым входом элемента И, на второй вход которого поступают тактовые импульсы fp, сдви нутые соответствующим образом от f Если на вход 78 поступает высокий потенциал, то элемент И 75 срабатывает и на его выходе образуется сигнал по импульсу f,j , Этот сигнал через выход 86 .поступает на коммутатор 7, открывая направление регистр 4 - накапливающий сумматор 71 и через выход 87 на сумматор 71, обеспечивая сложение. Затем срабаты- вает элемент И 74, сигнал с-выхода которого поступает на счетный вход счетчика 76, по выходу 83 поступает на регистр 4, обеспечивая циклический сдвиг его содержимого вправо, и по выходу 84 - на регистр 2, обеспечивая сдвиг его содержимого влево (считается, что в левых разрядах регистра 2 и 4 расположены старшие разряды числа). Если на вход 78 поступает низкий потенциал, то сложения по очередному импульсу f не производится, а выполняются сдвиги и изменения содержимого счетчика 76. Последний считает rto модулю, равному разрядности устройства, так что после выполнения п сдвигов регистра 2 на выходе счетчика 76 образуется сигнал конца умножения, который гасит триггер 73 и через выход 88 и вход 45 поступает в блок 9 управления. Съем результата операции возведения в степень осуществляется из накапливающего сумматора 71 по выходам 12. Таким образом, предлагаемое устройство характеризуется более высоким быстродействием по сравнению с прототипом.

| название | год | авторы | номер документа |

|---|---|---|---|

| СПОСОБ ЦИФРОВОЙ ОБРАБОТКИ СИГНАЛОВ И УСТРОЙСТВО ДЛЯ ЕГО ОСУЩЕСТВЛЕНИЯ | 2000 |

|

RU2163391C1 |

| Устройство для контроля параметров | 1990 |

|

SU1728869A1 |

| Устройство для деления чисел в модулярной системе счисления | 1990 |

|

SU1756887A1 |

| Вычислительное устройство | 1975 |

|

SU705478A1 |

| Преобразователь двоично-десятичного кода в двоичный | 1981 |

|

SU1013942A1 |

| Устройство для умножения двоичных чисел | 1980 |

|

SU981996A1 |

| Устройство вычисления сумм произведений | 1990 |

|

SU1718216A1 |

| Скалярный умножитель векторов | 1988 |

|

SU1619254A1 |

| Устройство для умножения | 1978 |

|

SU896617A2 |

| Устройство для умножения | 1990 |

|

SU1789981A1 |

.1. Устройство для возведения в степень, содержащее регистр основания, вспомогательный регистр, блок управления и регистр результата, выход которого является выходом устройства, отличающееся тем, что, с целью повышения быстродействия в него введены регистр сомножителя, регистр показателя степени, блок умножения, два коммутатора и дешифратор нуля, а блок управления содержит фйр;/ ирователь импульсов, три -триггера, девять элементов И, пять элементов ИЛИ, шесть элементов задержки, два элемента НЕ, элемент 2И-ИЛИ, причем инверсный выход первого триггера соединен с первыми входами соответственно первого и второго элементов И, вторые входы которых подключены к выходу третьего элемента И, первый вход которого и первый вход четвертого элемента И подключены к входу сдвига регистра показателя степени и через формирователь импульсов к выходу первого элемента ИЛИ, первый вход которого объединен i с первым входом первого триггера и подключен к выходу пятого элемента И, первый вход которого через первый элемент задержки соединен с выходом первого элемента И и с первым входом элемента 2И-ИЛИ, второй и третий вход которого соединены с выходом дешифратора нуля и через. первый элемент НЕ с вторым входом пятого и первым входом шестого элементов И, второй вход которого и четвертый вход элемента подключены к выходу седьмого элемента И, первый вход которого соединен с прямым выходом второго триггера,инверсный вход которого подключен к первому входу восьмого элемента И, второй вход которого и первый вход девятого элемента И соединены соответственно с инверсным и прямым выходакги третьего триггера, первый вход которого и первый вход второго элемента ИЛИ подключены к выходу второго элемента И, второй вход третьего элемента И соединен с вы- ходом младшего разряда регистра показателяг степени и через второй элемент НЕ со вторым входом четвертого элемента И, выход которого соединен с вторыми входами второго элемента ИЛИ и третьего триггера, третий вход которого объединен с первьлм входом третьего элемента ИЛИ и через второй элемент задержки соединен с выходом девятого элемента И и первым входом второго триггера, второй вход которого через третий элемент задержки соединен с выходом шестого элемента И и с первым вхоСЛ дом четвертого элемента ИЛИ, вторым входом соединенного с выходом пятого элемента И, выход третьего элемента ИЛИ соединен с входом запуска блока умножения, выход второго элемента ИЛИ через четвертый элемент задержки соединен с вторым входом третьего элемента ИЛИ и непосредственно - с первым входом пятого элемента ИЛИ, вторымвходом подключенного к выходу девятого элемента И, второй вход которого и третий вход восьмого элемента И объединены с вторым входом седьмого эле

01101 00110 00011 00001

00000

.16

П5-4,х П5-3 П5-4,х П5-4,х П3-4,х П5-3, П2-5 П5-4,х

6 П3-4,х 52f8 51 53 Pui. 2

15

jf fS

SS

12

« 90,

)

77 -

838

(риг. 5

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| УСТРОЙСТВО ДЛЯ ВО313ЕДЕНИЯ В СТЕПЕНЬ | 1972 |

|

SU425175A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Устройство для возведения в степень | 1976 |

|

SU656056A1 |

Авторы

Даты

1984-02-28—Публикация

1982-04-26—Подача