19

(Л

;о ;о

4

00

ЦЗиг.1

314

Изобретение относится к импульсной технике и может быть использовано для управления импульсно-кодовы- ми источниками сейсмических колебаний .

Цель изобретения - расширение функциональных возможностей и повышение надежности устройства в работе.

Рас иирение функциональных возможностей устройства достигается путем генерирования импульсных последовательностей, состоящих как из импульсов только одной полярности, так и из импульсов разной полярности, а также содержащие пропуски.

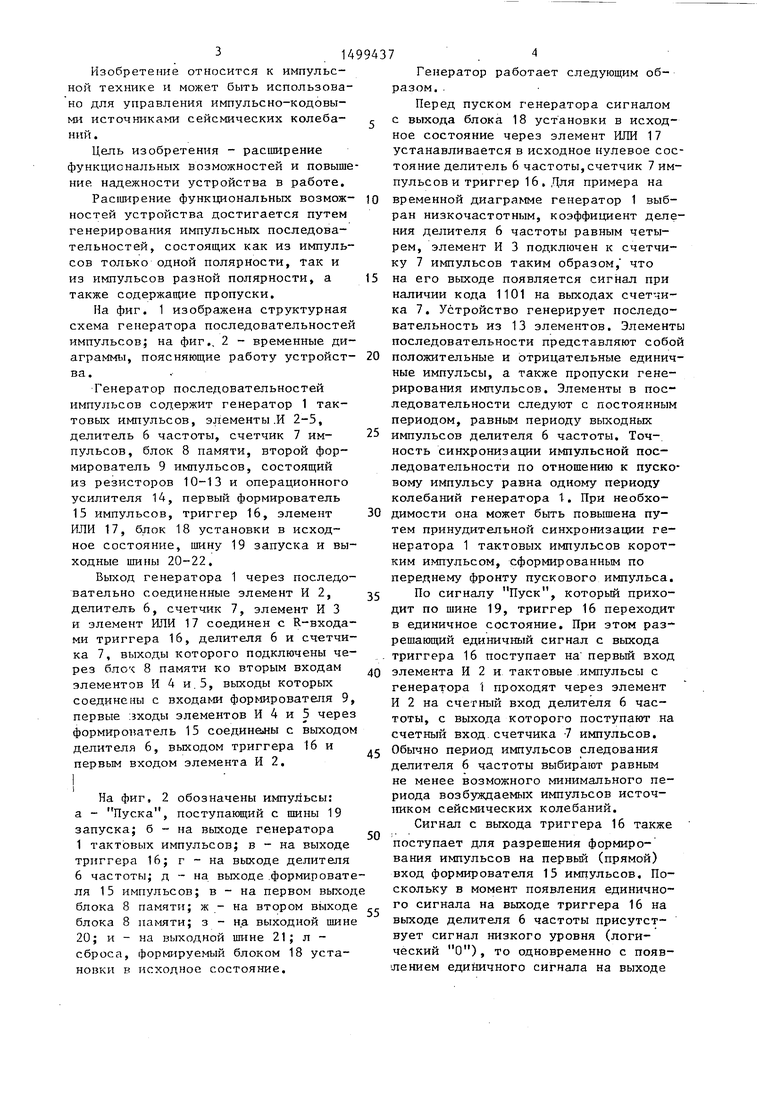

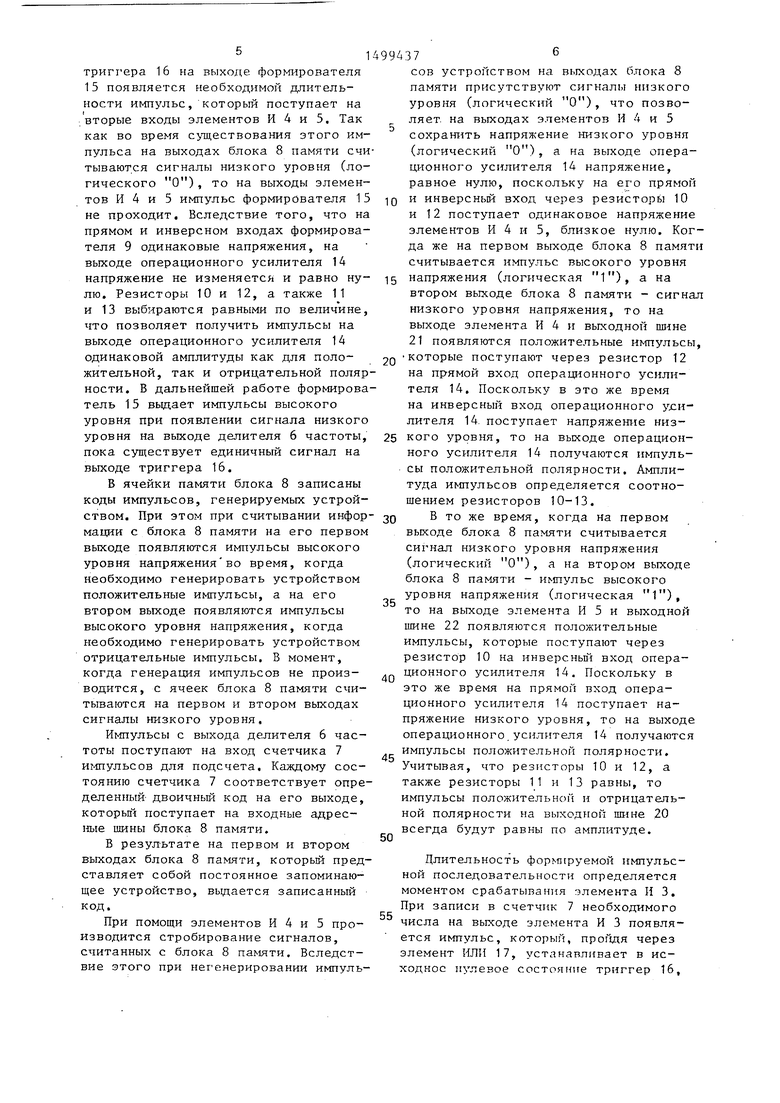

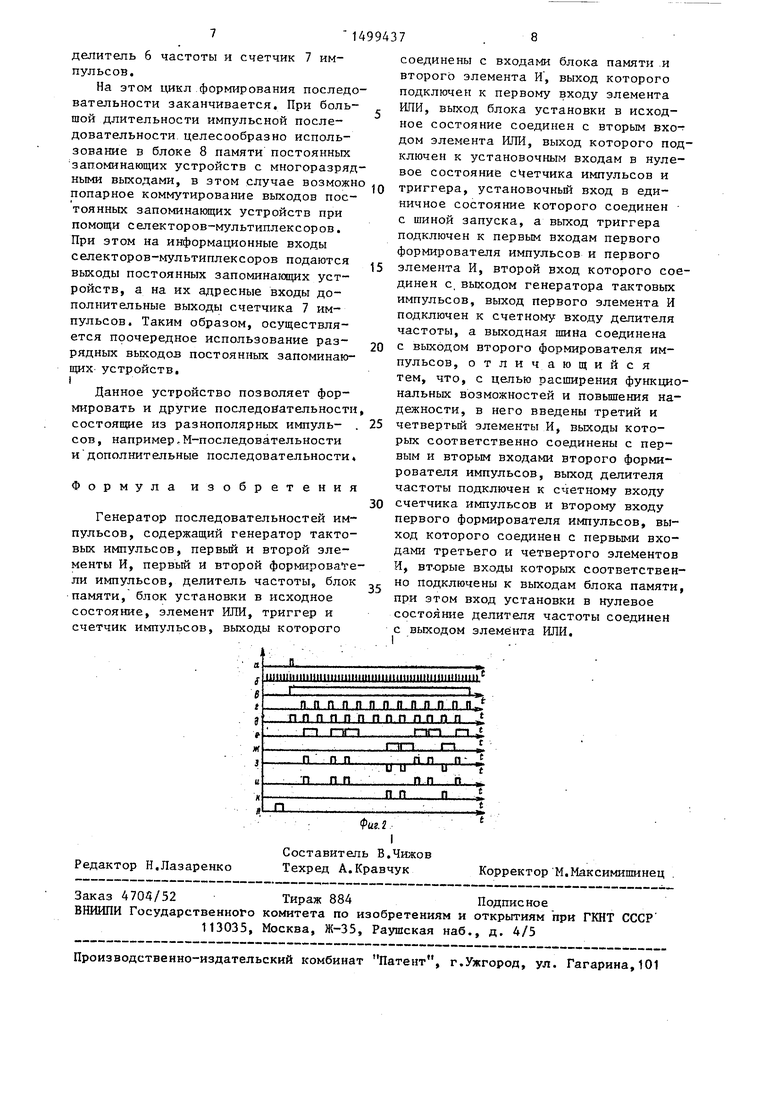

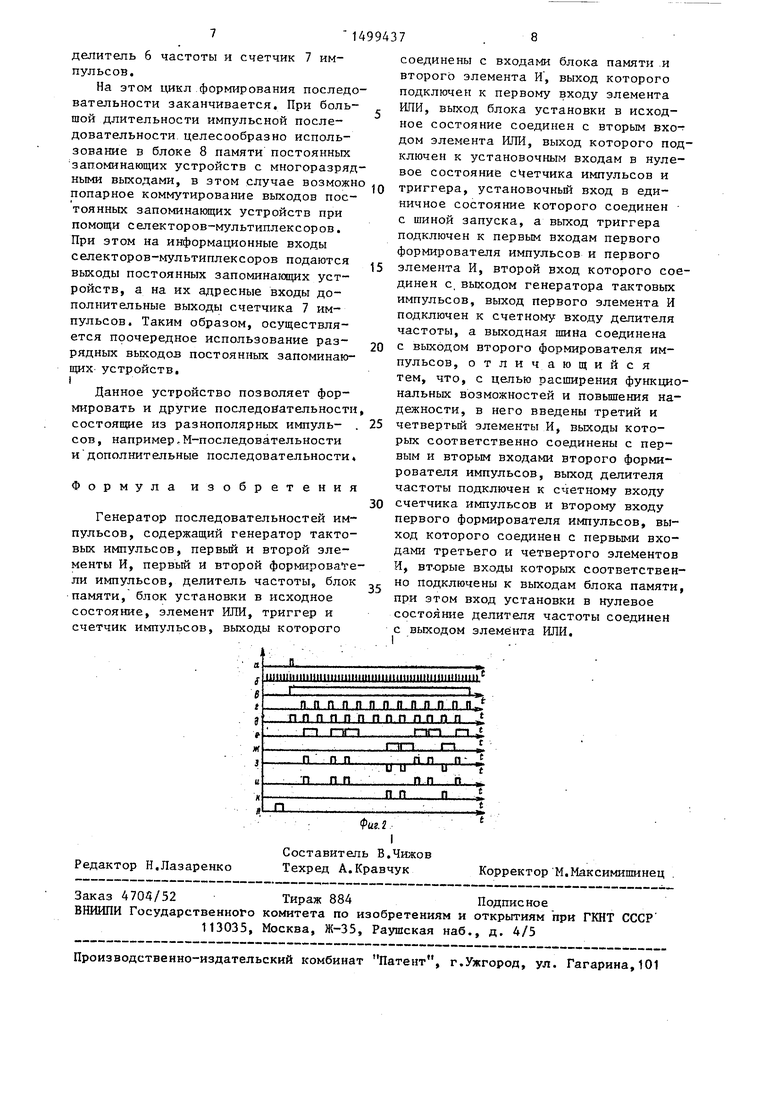

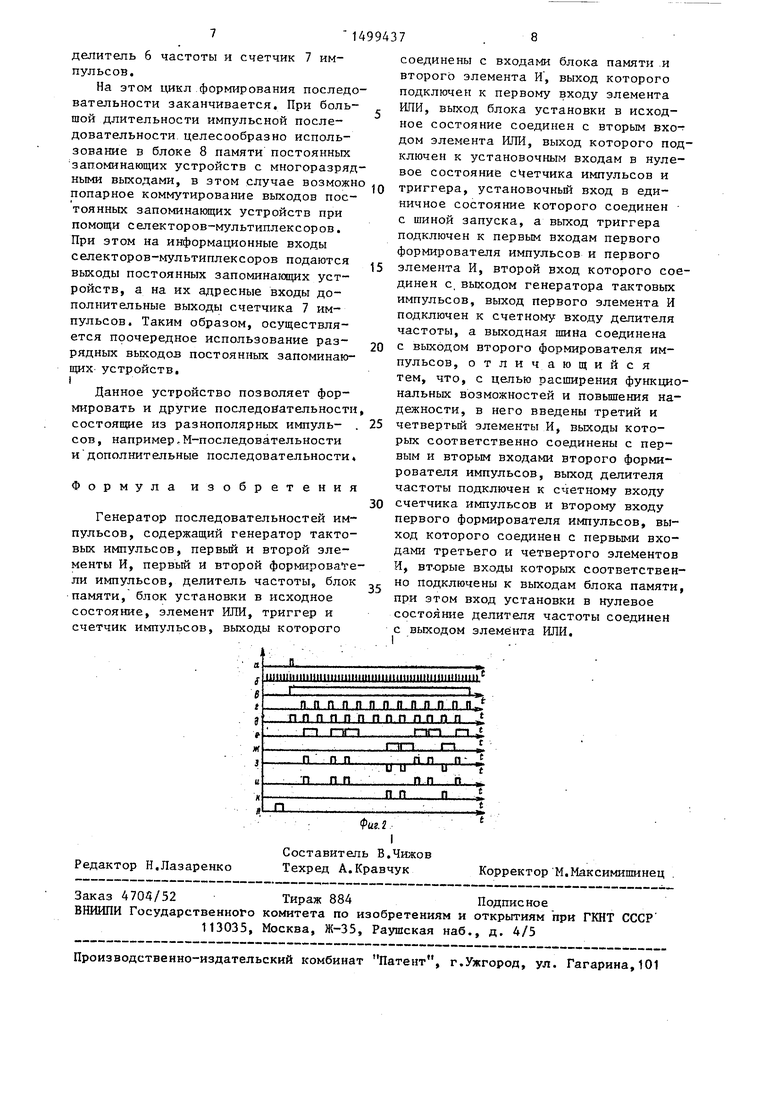

На фиг. 1 изображена структурная схема генератора последовательностей импульсов; на фиг., 2 - временные ди- arpaMMiii, поясняющие работу устройст- ва. .

Генератор последовательностей импульсов содержит генератор 1 тактовых импульсов, элементы .И 2-5, делитель 6 частоты, счетчик 7 импульсов, блок 8 памяти, второй формирователь 9 импульсов, состоящий из резисторов 10-13 и операционного усилителя 14, первый формирователь 15 импульсов, триггер 16, элемент ИЛИ 17, блок 18 установки в исходное состояние, шину 19 запуска и выходные шины 20-22.

Выход генератора 1 через последовательно соединенные элемент И 2, делитель 6, счетчик 7, элемент И 3 и элемент ИЛИ 17 соединен с R-входа- ми триггера 16, делителя 6 и счетчика 7, выходы которого подключены через блоч 8 памяти ко вторым входам элементов И 4 и.5, выходы которых соединены с входами формирователя 9, первые зходы элементов И 4 и 5 через формирователь 15 соединелы с выходом делителя 6, выходом триггера 16 и первым входом элемента И 2.

На фиг, 2 обозначены импульсы: а - Пуска, поступающий с шины 19 запуска; б - на выходе генератора 1 тактовых импульсов; в - на выходе триггера 16; г - на выходе делителя 6 частоты; д - на выходе .формирователя 15 импульсов; в - на первом выходе блока 8 памяти; ж - на втором выходе блока 8 памяти; з - на выходной шине 20; и - на выходной шине 21; л - сброса, формируемый блоком 18 установки в исходное состояние.

0

5

0

0

Генератор работает следующим образом. .

Перед пуском генератора сигналом с выхода блока 18 установки в исходное состояние через элемент ИЛИ 17 устанавливается в исходное нулевое состояние делитель 6 частоты,счетчик 7 импульсов и триггер 16, Для примера на временной диаграмме генератор 1 выбран низкочастотным, коэффициент деления делителя 6 частоты равным четырем, элемент И 3 подключен к счетчику 7 импульсов таким образом, что на его выходе появляется сигнал при наличии кода 1101 на выходах счетчика 7. Устройство генерирует последовательность из 13 элементов. Элементы последовательности представляют собой положительные и отрицательные единичные импульсы, а также пропуски генерирования импульсов. Элементы в последовательности следуют с постоянным периодом, равным периоду выходных импульсов делителя 6 частоты. Точность синхронизации импульсной последовательности по отношению к пусковому импульсу равна одному периоду колебаний генератора t, При необходимости она может быть повышена путем принудительной синхронизации генератора 1 тактовых импульсов коротким импульсом, сформированным по переднему фронту пускового импульса.

По сигналу Пуск, которьй приходит по шине 19, триггер 16 переходит в единичное состояние. При этом разрешающий единичный сигнал с выхода триггера 16 поступает на первый вход элемента И 2 и тактовые импульсы с генератора 1 проходят через элемент И 2 на счетный вход делителя 6 частоты, с выхода которого поступают на счетный вход, счетчика -7 импульсов, 5 Обычно период импульсов следования делителя 6 частоты выбирают равным не менее возможного минимального периода возбуждаемых импульсов источником сейсмических колебаний.

Сигнал с выхода триггера 16 также

поступает для разрешения формирования импульсов на первый (прямой) вход формирователя 15 импульсов. Поскольку в момент появления единичного сигнала на выходе триггера 16 на выходе делителя 6 частоты присутствует сигнал низкого уровня (логический О), то одновременно с появлением единичного сигнала на выходе

5

0

1

триггера 16 на выходе формирователя 15 появляется необходимой длительности импульс, который поступает на вторые входы элементов И 4 и 5. Так как во время с тдествования этого импульса на выходах блока 8 памяти считываются сигналы низкого уровня (логического О), то на выходы элементов И 4 и 5 импульс формирователя 15 не проходит. Вследствие того, что на прямом и инверсном входах формирователя 9 одинаковые напряжения, на выходе операционного усилителя 14 напряжение не изменяется и равно нулю. Резисторы 10 и 12, а также 11 и 13 выбираются равными по величине, что позволяет получить импульсы на выходе операционного усилителя 14 одинаковой амплитуды как для положительной, так и отрицательной полярности. В дальнейшей работе формирователь 15 выдает импульсы высокого уровня при появлении сигнала низкого уровня на выходе делителя 6 частоты, пока существует единичный сигнал на выходе триггера 16.

В ячейки памяти блока 8 записаны коды импульсов, генерируемых устройством. При этом при считывании информации с блока 8 памяти на его первом выходе появляются импульсы высокого уровня напряжения во время, когда необходимо генерировать устройством положительные импульсы, а на его втором выходе появляются импульсы высокого уровня напряжения, когда необходимо генерировать устройством отрицательные импульсы. В момент, когда генерация импульсов не производится, с ячеек блока 8 памяти считываются на первом и втором выходах сигналы низкого уровня.

Импульсы с выхода делителя 6 частоты поступают на вход счетчика 7 иг-шульсов для подсчета. Каждому состоянию счетчика 7 соответствует определенный двоичный код на его выходе, которьй поступает на входные адресные шины блока 8 памяти.

В результате на первом и втором выходах блока 8 памяти, который представляет собой постоянное запоминающее устройство, выдается записанный код.

При помощи элементов И 4 и 5 производится стробирование сигналов, считанных с блока 8 памяти. Вследствие этого при нет енерировании импуль99437

сов устройством на выходах блока 8 памяти присутствуют сигналы низкого уровня (логический О), что позволяет, на выходах элементов И 4 и 5 сохранить напряжение низкого уровня (логический О), а на выходе операционного усилителя 14 напряжение, равное нулю, поскольку на его прямой

10 и инверсньй вход через резисторь 10 и 12 поступает одинаковое напряжение элементов И 4 и 5, близкое нулю. Когда же на первом выходе блока 8 памяти считывается импульс высокого уровня

15 напряжения (логическая 1), а на

втором выходе блока 8 памяти - сигнал низкого уровня напряжения, то на выходе элемента И 4 и выходной nuiHe 21 появляются положительные импульсы,

2Q Которые поступают через резистор 12 на прямой вход операционного усилителя 14. Поскольку в это же время на инверсный вход операционного усилителя 14. поступает напряжение низ25 кого уровня, то на выходе операционного усилителя 14 получаются импульсы положительной полярности. Амплитуда импульсов определяется соотношением резисторов 10-13. 30 В то же время, когда на первом выходе блока 8 памяти считывается сигнал низкого уровня напряжения (логический О), а на втором выходе блока 8 памяти - импульс высокого уровня напряжения (логическая 1), то на выходе элемента И 5 и выходной шине 22 появляются положительные импульсы, которые поступают через резистор 10 на инверсньй вход операционного усилителя 14. Поскольку в

35

40

45

50

55

это же время на прямой вход операционного усилителя 14 поступает напряжение низкого уровня, то на выходе операционного,усилителя 14 получаются импульсы положительной полярности. Учитывая, что резисторы 10 и 12, а также резисторы 11 и 13 равны, то импульсы положительной и отрицательной полярности на выходной шине 20 всегда будут равны по амплитуде.

Длительность фop п pyeмoй импульсной последовательности определяется моментом срабатывания элемента ИЗ. При записи в счетчик 7 необходимого числа на выходе элемента И 3 появляется импульс, который, пройдя через элемент ИЛИ 17, устанавливает в исходное пулевое состояние триггер 16,

делитель 6 частоты и счетчик 7 импульсов.

На этом цикл формирования последовательности заканчивается. При большой длительности импульсной последовательности целесообразно использование в блоке 8 памяти постоянных запоминающих устройств с многоразрядными выходами, в этом случае возможн попарное коммутирование выходов постоянных запоминающих устройств при помощи селекторов-мультиплексоров. При этом на информационные входы селекторов-мультиплексоров подаются выходы постоянных запоминагацих устройств, а на их адресные входы дополнительные выходы счетчика 7 импульсов. Таким образом, осуществляется поочередное использование разрядных выходов постоянных запоминающих устройств.

i

Данное устройство позволяет формировать и другие последовательности состоящие из разнополярных импуль- . сов, например,М-последовательности и дополнительные последовательности«

Формула изобретения

Генератор последовательностей импульсов, содержащий генератор тактовых импульсов, первьм и второй элементы И, первьй и второй формирователи импульсов, делитель частоты, блок памяти, блок установки в исходное состояние, элемент ИЛИ, триггер и счетчик импульсов, выходы которого

соединены с входами блока памяти и второго элемента И, выход которого подключен к первому входу элемента

ИЛИ, выход блока установки в исходное состояние соединен с вторым входом элемента ИЛИ, выход которого подключен к установочным входам в нулевое состояние с4етчика импульсов и

триггера, установочный вход в единичное состояние которого соединен с шиной запуска, а выход триггера подключен к первым входам первого формирователя импульсов и первого

элемента И, второй вход которого соединен с, выходом генератора тактовых импульсов, выход первого элемента И подключен к счетному входу делителя частоты, а выходная шина соединена

с выходом второго формирователя импульсов, отличающийся тем, что, с целью расширения функциональных возможностей и повьппения надежности, в него введены третий и

четвертый элементы И, выходы которых соответственно соединены с первым и вторым входами второго формирователя импульсов, выход делителя частоты подключен к счетному входу

счетчика импульсов и второму входу первого формирователя импульсов, выход которого соединен с первыми входами третьего и четвертого элементов И, вторые входы которых соответствен-

но подключены к выходам блока памяти, при этом вход установки в нулевое состояние делителя частоты соединен с выходом элемента ИЛИ.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для автоматизированного контроля параметров реле | 1985 |

|

SU1265704A1 |

| Генератор спектрометрических импульсов | 1986 |

|

SU1325671A1 |

| Электропривод постоянного тока | 1986 |

|

SU1661951A1 |

| Программное временное устройство | 1987 |

|

SU1418654A1 |

| Цифровой измеритель температуры | 1986 |

|

SU1390516A1 |

| Система автоматического пожаротушения | 1987 |

|

SU1461486A1 |

| Устройство для цифрового измерения частоты | 1989 |

|

SU1666965A2 |

| ФОРМИРОВАТЕЛЬ ЦИФРОВОЙ ПОСЛЕДОВАТЕЛЬНОСТИ С РАВНОМЕРНЫМ РАСПРЕДЕЛЕНИЕМ | 2008 |

|

RU2417406C2 |

| СТЕНД ДЛЯ ИЗУЧЕНИЯ ЭЛЕКТРОННЫХ СРЕДСТВ АВТОМАТИЗАЦИИ | 2005 |

|

RU2279718C1 |

| СТЕНД ДЛЯ ИЗУЧЕНИЯ ГИБРИДНЫХ ЭЛЕКТРОННЫХ УСТРОЙСТВ | 2012 |

|

RU2493609C1 |

Изобретение может быть использовано для управления импульсно-кодовыми источниками сейсмических колебаний. Целью изобретения является расширение функциональных возможностей и повышение надежности генератора последовательностей импульсов. Устройство содержит генератор 1 тактовых импульсов, элементы И 2- 5 делитель 6 частоты, счетчик 7 импульсов, блок 8 памяти, формирователи 9, 15 импульсов, триггер 16, элемент ИЛИ 17 и блок 18 установки в исходное состояние. 2 ил.

Авторы

Даты

1989-08-07—Публикация

1988-01-25—Подача