4;

СО CD

05

4;

Изобретение относится к радаотех- нике и может Сыть использовано для селекции импульсных последовательностей с периодом следования импульсов, кратным заданной величине.

Цель изобретения - обеспечение возможности обнаружения импульсных последовательностей с периодами еле- дования импульсов, кратными заданной величине, при одновременном обеспечении заданной вероятности правильного обнаружения.

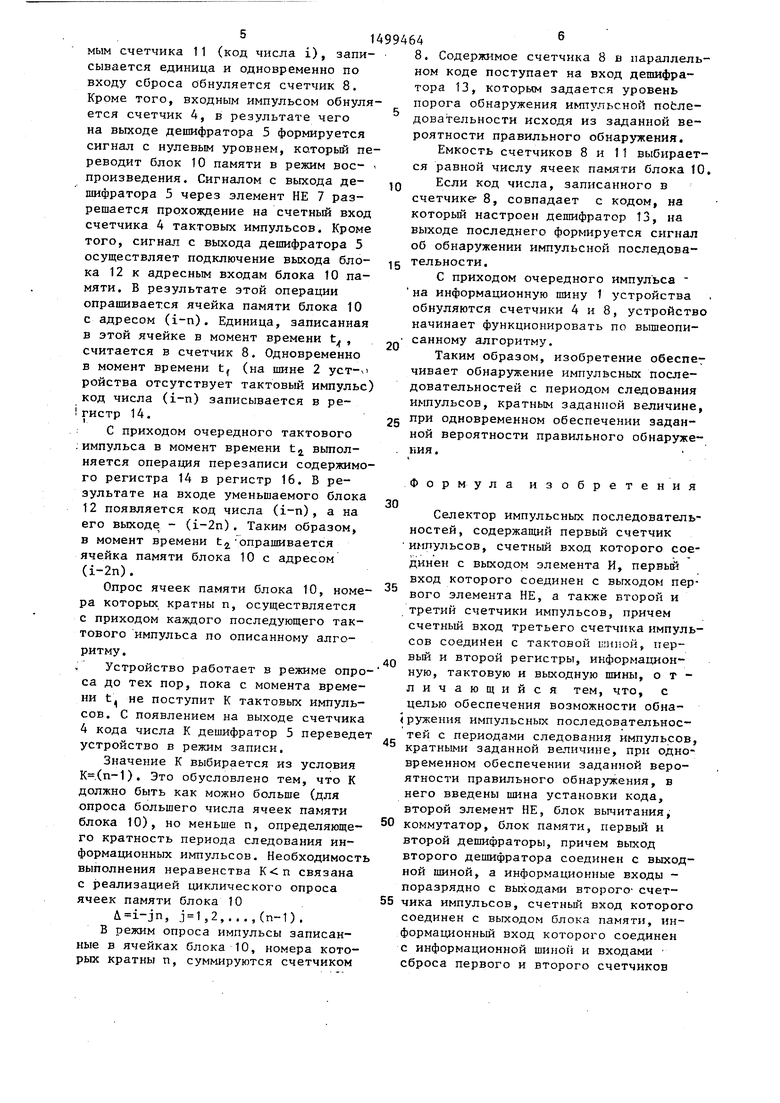

На чертеже показана, структурная

электрическая схема селектора.

Селектор импульсных последовательностей содержит информационную шину 1, тактовую шину 2, выходную шину 3. Шина 1 соединена с входом сброса первого счетчика 4 импульсов, выходы которого поразрядно соединены с информационными входами дешифратора 5,f а счетный вход - с выходом элемента И 6, первый вход которого соединен с выходом первого элемента НЕ 7, а i второй вход - с тактовой шиной 2. Шина 1 соединена с входом сброса второго счетчика 8 импульсов. Выход де-. шифратора 5 соединен с входом элемента НЕ 7 и входами управления коммутатора 9 и блока 10 памяти. Шина 2 соединена со счетным входом третьего счетчика 11 импульсов. Устройство также содержит блок 12 вычитания, второй дешифратор 13, первьй регистр 14, вход записи которого соединен с выходом второго элемента НЕ 15, а выходы - поразрядно с информационны- ми входами второго регистра 16. Входы группы входов вычитаемого блока 12 образуют шину 17 установки кода. Шина 1 соединена с информационным входом блока 10, адресные входы которого

соединены поразрядно с выходами ком- мутатора 9, а также поразрядно с информационными входами регистрэ 14. Входы первой группы входов коммутатора 9 поразрядно соединены с выходами, блока 12, а входы второй группы вхо- дов - с выходами счетчика 11 импульсов. Входы группы входов уменьшаемого блока 12 соединены поразрядно с выходами регистра 16, вход записи которого соединен с входом элемента НЕ 15 и шиной 2. Выход блока 10 соединен со счетным входом счетчика 8, выходы которого поразрядно соединены с информационными входами дешифратора 13, Q

5

0 5 Q .

5

5 0 5 выход которого соединен с выходной шиной 3.

Селектор работает следующим образом.

В исходном состоянии при включении питания на выходе; блока 5 формируется уровень логического нуля, так как содержимое счетчика 4 не соответствует кодовой комбинации дешифратора 5. Элемент И 6i iоткрыт по одному из входов сигналом уровня логической 1 с выхода элемента НЕ 7.

Тактовые импульсы с шины 2 поступают на счетный вход счетчика 11 и через элемент И 6 на счетный вход сч ётчика 4. Заполнение счетчика 4 осуществляется до совпадения с кодом числа К, определяемьм дешифратором 5. В результате этого на выходе дешифратора 5 формируется сигнал логической единицы, который через элемент НЕ 7 закрывает элемент И 6 для прохождения тактовых импульсов, разрешает прохождение через Коммутатор 9 кодовой комбинации с выхода счетчика 11 на адресный вход блока 10 памяти и одновременно переводит его по входу управления в режим записи.

Кроме того, содержимое счетчика 11 .поступает на информационные входы регистра 14.

При отсутствии тактового импульса на шине 2.устройства на выходе эле-: мента НЕ 15 формируется сигнал с уровнем логической единицы, разрешающий запись в регистр 14 содержимого счетчика 11.

При прохождении очередного тактового импульса содержимое регистра 14 переписывается в регистр 16. Изменения содержимого регистра 14 при этом не происходит, так как на его управляющем входе отсутствует сигнал разрешения записи, чем исключается сбойная ситуация при вьшЪлнении операции перезаписи.

Код числа i с выхода регистра 16 поступает на вход уменьшаемого блока 12, на вход вычитаемого которого поступает код числа п с пмны 17. Значение п определяется из априорно известной кратности периодов следования информационных импульсов.

На выходе блока 12 формируется код разности fc.i-n. Пусть в момент времени t на информационную шину 1 устройства поступает импульс. В результате в ячейку блока 10 памяти, адрес которой определяется содержи

5

мым счетчика 11 (код числа i), запи- сывается единица и одновременно по входу сброса обнуляется счетчик 8. Кроме того, входным импульсом обнуляется счетчик 4, в результате чего на выходе дешифратора 5 формируется сигнал с нулевым уровнем, который переводит блок 10 памяти в режим вое- произведения. Сигналом с выхода дешифратора 5 через элемент НЕ 7 разрешается прохождение на счетный вход счетчика 4 тактовых импульсов. Кроме того, сигнал с выхода дешифратора 5 осуществляет подключение выхода блока 12 к адресным входам блока 10 памяти. В результате этой операции опрашивается ячейка памяти блока 10 с адресом (i-n). Единица, записанная в этой ячейке в момент времени t , считается в счетчик 8. Одновременно

в момент времени t (на шине 2 ycт- ройства отсутствует тактовый импульс) код числа (i-n) записывается в ре- гистр 14.

С приходом очередного тактового импульса в момент времени t выполняется операция перезаписи содержимого регистра 14 в регистр 16. В результате на входе уменьшаемого блока 12 появляется код числа (i-n), а на его выходе - (i-2n). Таким образом, в момент времени 12. опрашивается ячейка памяти блока 10 с адресом (i-2n).

Опрос ячеек памяти блока 10, номера которых кратны п, осуществляется с приходом каждого последующего тактового импульса по описанному алгоритму.

Устройство работает в режиме опроса до тех пор, пока с момента времени t не поступит К тактовых импульсов. С появлением на выходе счетчика 4 кода числа К дешифратор 5 переведет устройство в режим записи.

Значение К выбирается из условия К.(п-1). Это обусловлено тем, что К должно быть как можно больше (для опроса большего числа ячеек памяти блока 10), но меньше п, определяющего кратность периода следования информационных импульсов. Необходимость выполнения неравенства связана с реализацией циклического опроса ячеек памяти блока 10

, ,2,...,(п-1). В режим опроса импульсы записанные в ячейках блока 10, номера которых кратны п, суммируются счетчиком

0

8

8. Содержимое счетчика В в паргшлель- ном коде поступает на вход дешифратора 13, которым задается уровень порога обнаружения импульсной поЬле- довательности исходя из заданной вероятности правильного обнаружения.

Емкость счетчиков 8 и 11 выбирается равной числу ячеек памяти блока 10.

Если код числа, записанного в счетчике 8, совпадает с кодом, на который настроен дешифратор 13, на выходе последнего формируется сигнал об обнаружении импульсной последовательности.

С приходом очередного импульса на информационную шину 1 устройства обнуляются счетчики 4 и 8, устройство начинает функционировать по вышеописанному алгоритму.

Таким образом, изобретение обеспе7 чивает обнаружение импульсных последовательностей с периодом следования импульсов, кратным заданной величине, 5 при одновременном обеспечении заданной вероятности правильного обнаруже- . ния.

5

0

Формула изобретения

5

0

0

Селектор импульсных последовательностей, содержащий первый счетчик

импульсов, счетный вход которого соединен с выходом элемента И, первый вход которого соединен с выходом первого элемента НЕ, а также второй и третий счетчики импульсов, причем счетный вход третьего счетчика импульсов соединен с тактовой шшюй, первый и второй регистры, информационную, тактовую и выходную шины, отличающийся тем, что, с целью обеспечения возможности обна ружения импульсных последовательностей с периодами следования импульсов, кратными заданной величине, при одновременном обеспечении заданной вероятности правильного обнаружения, в него введены шина установки кода, второй элемент НЕ, блок вычитания, коммутатор, блок памяти, первый и второй дешифраторы, причем выход второго дешифратора соединен с выходной шиной, а информационные входы - поразрядно с выходами второго- счет- 5 чика импульсов, счетный вход которого соединен с выходом блока памяти, информационный вход которого соединен с информационной шиной и входами сброса первого и второго счетчиков

5

0

7; 14994648

импульсов, причем выходы первбгоными входами второго регистра, вход счетчика импульсов поразрядно соеди- записи которого соединен с вторым нены с информационными входами перво-входом элемента И, входом второго го дешифратора, выход которого соеди-элемента НЕ и тактовой шиной, а вы- нен с входом первого элемента НЕ,,ходы - поразрядно с входами группы входом управления коммутатора и вхо-входов уменьшаемого блока вычитания, дом управления блока памяти, адресныевходы группы входов вычитаемого кото- входы которого поразрядно соединенырого образуют шину установки кода, с выходами коммутатора и также пораз- „а выходы - поразрядно с входами пер- рядно с информационными входами перво-вой группы входов ко1.1мутатора, входы го регистра, вход записи которого со-второй группы входрв которого пораз- Ъдинен с выходом второго элемента НЕ, рядно соединены с вызсодаМи третьего а выходы - поразрядно с информациг -счетчика импульсой.

| название | год | авторы | номер документа |

|---|---|---|---|

| СЕЛЕКТОР ИМПУЛЬСНЫХ ПОСЛЕДОВАТЕЛЬНОСТЕЙ | 1994 |

|

RU2085028C1 |

| Селектор импульсных последовательностей | 1988 |

|

SU1529435A1 |

| УСТРОЙСТВО СЕЛЕКЦИИ ДВУХ РЕТРАНСЛИРОВАННЫХ СИГНАЛОВ | 1996 |

|

RU2103811C1 |

| Селектор импульсов по длительности | 1990 |

|

SU1758866A2 |

| Устройство для сопряжения вычислительной машины с каналом связи | 1985 |

|

SU1291994A1 |

| Многоканальное устройство для сопряжения источников информации с вычислительной машиной | 1985 |

|

SU1259274A1 |

| СЕЛЕКТОР ИМПУЛЬСНЫХ ПОСЛЕДОВАТЕЛЬНОСТЕЙ | 1994 |

|

RU2078482C1 |

| Многоканальное устройство для обработки информации датчиков с частотным выходом | 1984 |

|

SU1196892A1 |

| Устройство для опроса информационных каналов | 1982 |

|

SU1062677A1 |

| МИКРОПРОГРАММНОЕ УСТРОЙСТВО УПРАВЛЕНИЯ | 1993 |

|

RU2079876C1 |

Изобретение относится к радиотехнике и может быть использовано для селекции импульсных последовательностей с периодом следования импульсов, кратным заданной величине. Цель изобретения - обеспечение возможности обнаружения импульсных последовательностей с периодами следования импульсов, кратными заданной величине, при одновременном обеспечении заданной вероятности правильного обнаружения. Селектор импульсных последовательностей содержит информационную шину 1, тактовую шину 2, выходную шину 3, счетчики 4, 8 и 11 импульсов, элемент И 6, элемент НЕ 7, регистры 14 и 16. Поставленная цель достигается введением дешифраторов 5 и 13, коммутатора 9, блока 10 памяти, блока 12 вычитания, элемента НЕ 15, шины 17 установки кода и вследствие образования новых функциональных связей. 1 ил.

| Селектор импульсных последовательностей | 1980 |

|

SU961127A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Селектор сигналов | 1987 |

|

SU1448403A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1989-08-07—Публикация

1987-11-12—Подача