ел

о о

CD СО

Изобретение относится к автоматизированным системам контроля и моет быть использовано для контроля цифреаналоговых, аналого-цифровых, г цифровых и аналоговых узлов радиоэлектронной аппаратуры.

Цель изобретения - расширение функциональных возможностей, системы за счет обеспечения возможности ис- 10 пользования системы для контроля последовательных цифровых кодов.

На фиг.1 приведена схема автоматизированной системы контроля параметров электронных на фиг.2-11 - 15 схемы отдельных блоков, входящих в систему контроля.

На схемах представлены блок 1 синхронизации-, управляющая вычислительная машина {уВМ) 2,блок 3 регист- 20 ров входной информации, блок 4 ре- . гистров выходной информации, блок 5 регистров адреса, первый коммутатор 6, блок 7 стимулирующих сигналов, блок 8 измерителей входных сигналов, 25 объект 9 контроля, блок 10 управления режимами, второй коммутатор 11, блок 12 задания эталонных сигналов, блок 13 ввода/вывода, пульт 14 оператора, третий коммутатор 15. 30

Блок 1 (фиг.2) состоит из п+1 одинаковых формирователей 16 управляющих сигналов (количество формирователей зависит от количества использованных в системе стандартных изме-. 35 рительных приборов, входящих в бло- ки 7 и 8, а также от разрядности регистров в блоках 3 и 4, разрядности информационной шины управляющей вычислительной машины), каждый из 40 которых содержит дешифратор 17, элемент ИЛИ 18 и узел 19 сигнала под-, тверххдения, включающий элементы И 20, резисторы 21 и конденсаторы 22. Блок 1 содержит также элемент 23 ЗАПРЕТ. 45

Блок 3 (фиг.З) содержит п одинаковых 16-разрядных регистров, каждый из которых состоит из шести 4-разряд- ных статических i регистров 24 и устройств-25 согласования.

Блок 4 (фиг.4) содержит два устройства 26 хранения цифровой информации, каждое из которых состоит из п одинаковых 16 разрядных регистров, состоящих из четырех 4-разрядных ре- j гистров 27 сдвига и устройства 28 со гла со вания.

В блок 5 (фиг.З) входят элемент И 29, регистры 30, устройство 31 .

согласования и узел 32 сигнала подтверждения .

Первый коммутатор 6 (фиг.6) состоит из релейных блоков 33, в состав которых входят реле 34 и 35, реле 36, соединителей 37, реле 38 - 40, объединенных в релейные блоки 41.

Блоки 7 и 8 (фиг.7) представляют собой набор стандартных измерительных приборов с цифровым дистанционным управлением, например вольтметр 42, частотомер 43 и осциллограф 44.

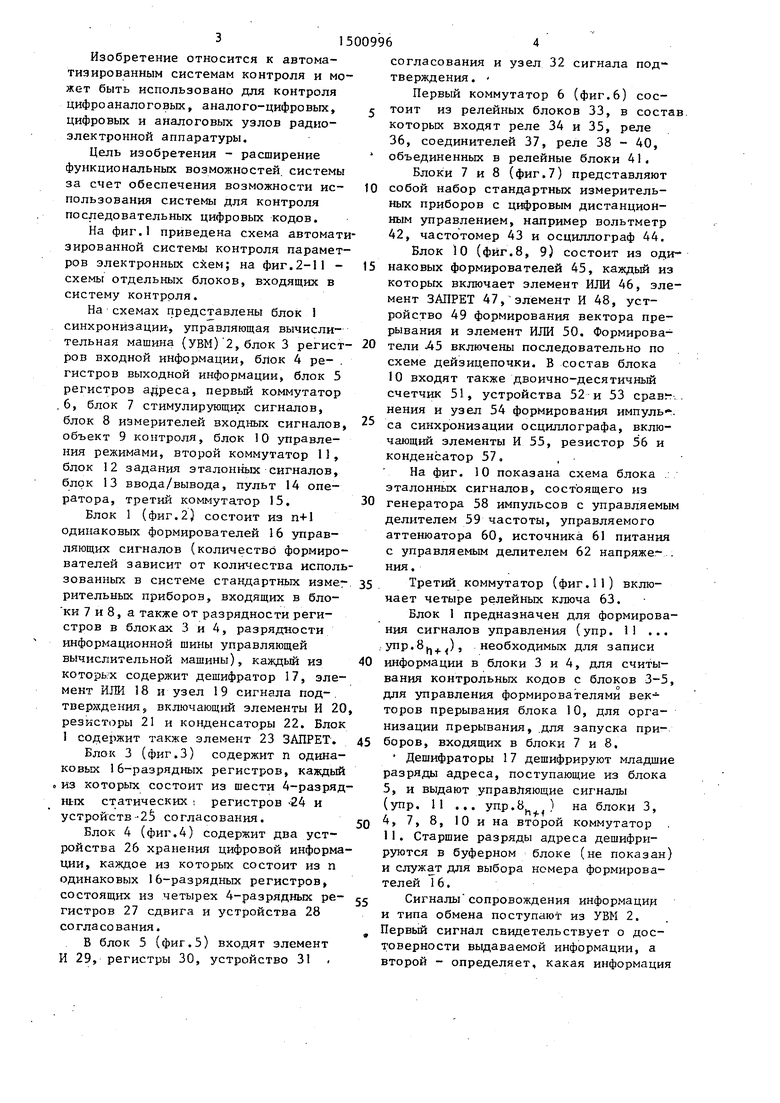

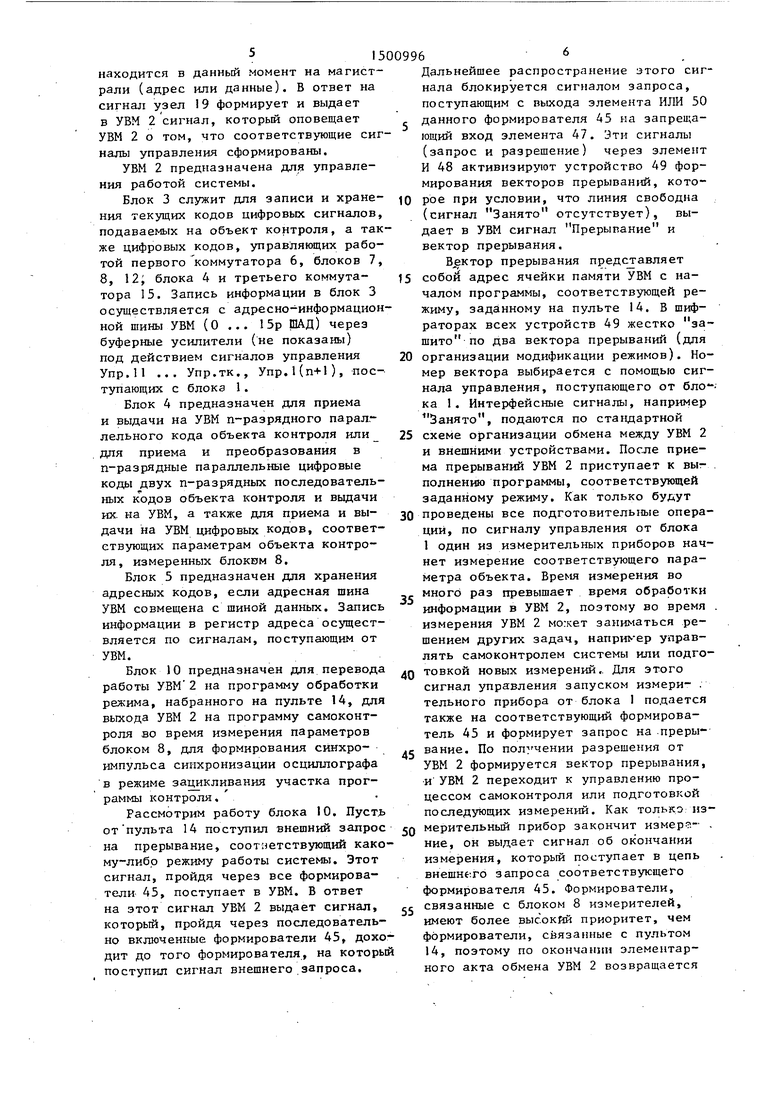

Блок 10 (фиг.8, 9) состоит из оди наковых формирователей 45, каждый из которых включает элемент ИЛИ 46, элемент ЗАПРЕТ 47, элемент И 48, устройство 49 формирования вектора прерывания и элемент ИЛИ 50. Формирователи А5 включены последовательно по схеме дейзицепочки. В состав блока 10 входят также двоично-десятичный счетчик 51, устройства 52 и 53 . нения и узел 54 формирования импуль. са синхронизации осциллографа, включающий элементы И 55, резистор 56 и конденсатор 57. ,

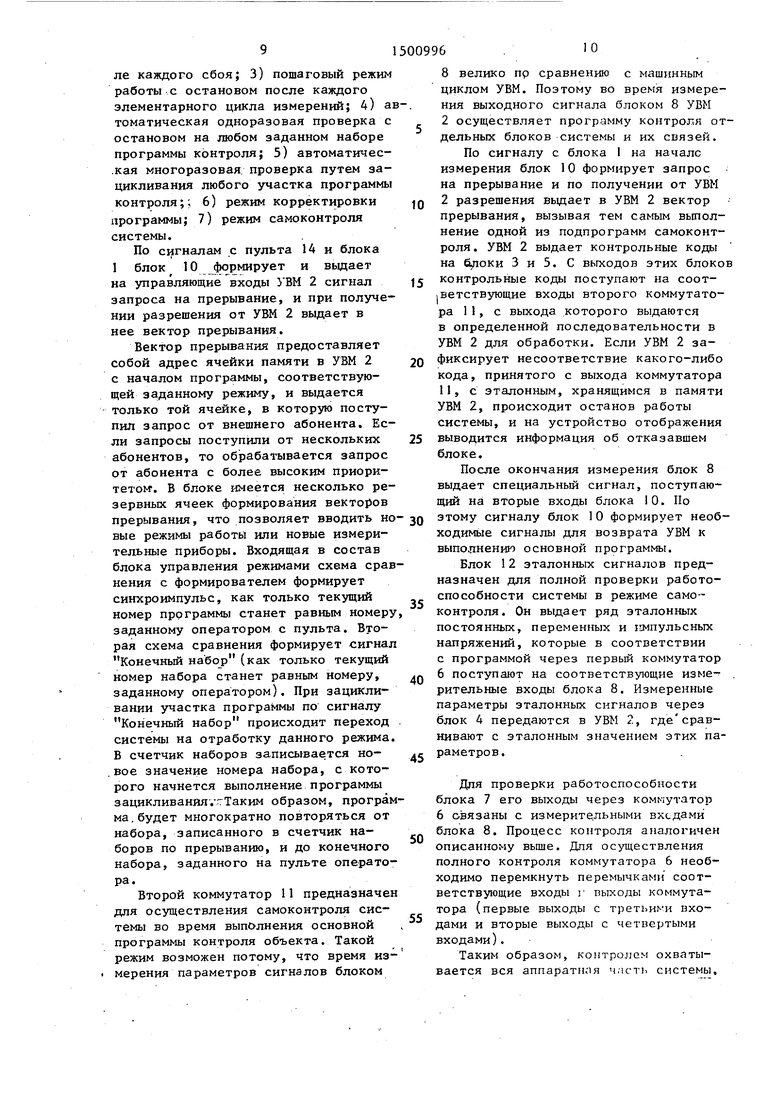

На фиг. 10 показана схема блока . эталонных сигналов, состоящего из генератора 58 импульсов с управляемым делителем 59 частоты, управляемого аттенюатора 60, источника 61 питания с управляемым делителем 62 напряже.- . ния.

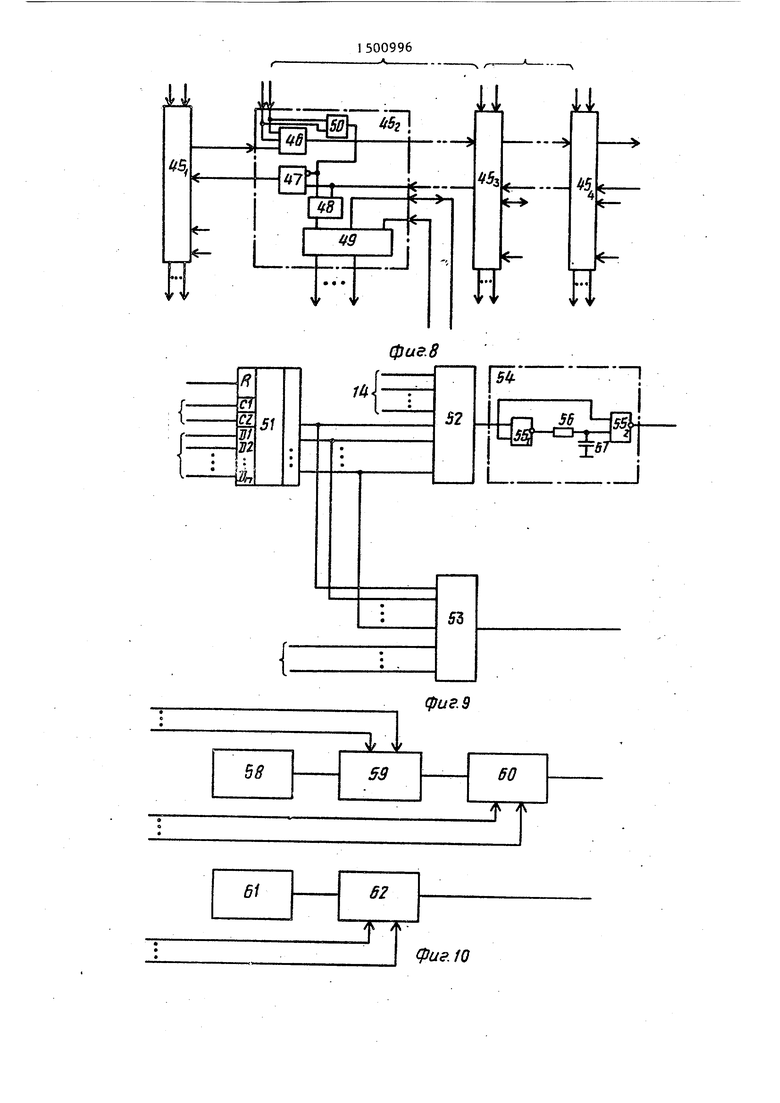

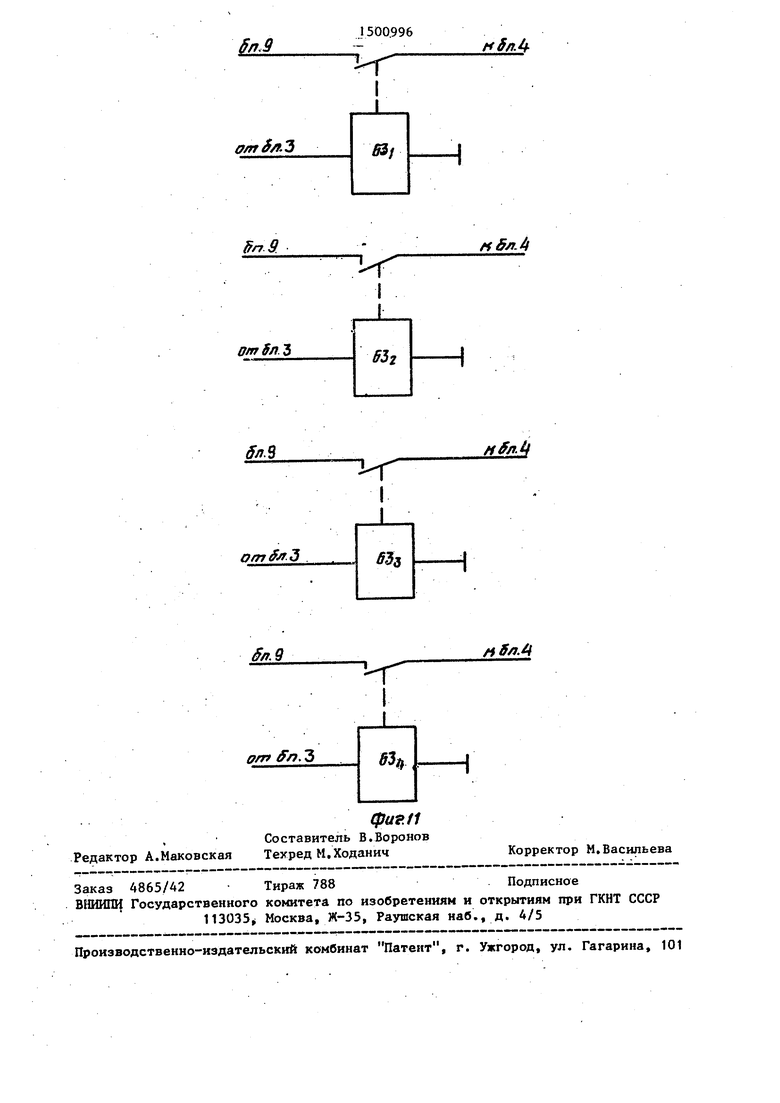

Третий коммутатор (фиг.11) включает четыре релейных ключа 63.

Блок 1 предназначен для формирования сигналов управления (упр. 11 ... упр.8), необходимых для записи информации в блоки 3 и 4, для считывания контрольных кодов с блоков 3-5,

о

для управления формирователями векторов прерывания блока 10, для организации прерывания, .для запуска приборов, входящих в блоки 7 и 8,

Дешифраторы 17 дешифрируют младшие разряды адреса, поступающие из блока 5, и выдают управляющие сигналы (упр. 11 ... упр.8 ) на блоки 3, 4, 7, 8, 10 и на второй коммутатор 11. Старшие разряды адреса дешифрируются в буферном блоке (не показан) и служат для выбора номера формирователей 16.

Сигналы сопровождения информации и типа обмена поступают из УВМ 2. Первый сигнал свидетельствует о достоверности выдаваемой информации, а второй - определяет, какая информация

находится в данньй момент на магистрали (адрес или данные). В ответ на сигнал узел 19 формирует и выдает в УВМ 2 сигнал, который оповещает УВМ 2 о том, что соответствующие сигналы управления сформированы.

УВМ 2 предназначена для управления работой системы.

Блок 3 служит для записи и хранения текущих кодов цифровых сигналов, подаваемых на объект контроля, а также цифровых кодов, управляющих работой первого коммутатора 6, блоков 7, 8, 12; блока 4 и третьего коммутатора 15. Запись информации в блок 3 осуществляется с адресно-информационной шины УВМ (О ... 1Зр ЩАД) через буферные усилители (не показаны) под действием сигналов управления Упр.11 ... Упр.тк., Упр.1(п+1), поступающих с блока 1.

Блок 4 предназначен для приема и выдачи на УВМ п-разрядного парал,- лельного кода объекта контроля или для приема и преобразования в п-разрядные параллельные цифровые коды двух п-разрядных последовательных к одов объекта контроля и выдачи их. на УЕМ, а также для приема и выдачи на УВМ цифровых кодов, соответствующих параметрам объекта контроля, измеренных блоквм 8.

Блок 5 предназначен для хранения адресных кодов, если адресная шина УВМ совмещена с шиной данных. Запись информации в регистр адреса осуществляется по сигналам, поступающим от УВМ.

Блок 10 предназначен для перевода работы УВМ 2 на программу обработки режима, набранного на пульте 14, для выхода УВМ 2 на программу самоконтроля во время измерения параметров блоком 8, для формирования синхроимпульса синхронизации осциллографа в режиме зацикливания участка программы контроля.

Рассмотрим работу блока 10. Пусть от пульта 14 поступил внешний запрос на прерывание, соответствующий какому-либо режиму работы системы. Этот сигнал, пройдя через все формирователи 45, поступает в УВМ. В ответ на этот сигнал УВМ 2 выдает сигнал, который, пройдя через последовательно включенные формирователи 45, доходит до того формирователя, на которы поступил сигнал внешнего запроса.

0

5

Дальнейшее распространение этого сигнала блокируется сигналом запроса, поступающим с выхода элемента ИЛИ 50 данного формирователя 45 на запрещающий вход элемента 47. Эти сигналы (запрос и разрещение) через элемент И 48 активизируют устройство 49 формирования векторов прерываний, которое при условии, что линия свободна (сигнал Занято отсутствует), выдает в УВМ сигнал Прерывание и вектор прерывания.

Виктор прерывания представляет

5 собой адрес ячейки памяти УВМ с началом программы, соответствующей режиму, заданному на пульте 14. В шифраторах всех устройств 49 жестко за шито по два вектора прерываний (для

0 организации модификации режимов). Номер вектора выбирается с помощью си1- нала управления, поступающего от бло-. ка 1. Интерфейсные сигналы, например Занято, подаются по ставдартной схеме организации обмена между УВМ 2 и внешними устройствами. После приема прерываний УВМ 2 приступает к вы- , полнению программы, соответствующей заданному режиму. Как только будут проведены все подготовительные операций, по сигналу управления от блока 1 один из измерительных приборов начнет измерение соответствующего параметра объекта. Время измерения во много раз превышает время обработки информации в УВМ 2, поэтому во время . измерения УВМ 2 может заниматься решением других задач, aanpin- ep управлять самоконтролем системы или подготовкой новых измерений.. Для этого сигнал управления запуском измери- . тельного прибора от блока 1 подается также на соответствующий формирователь 45 и формирует запрос на прерывание. По получении разрешения от УВМ 2 формируется вектор прерывания, и УВМ 2 переходит к управлению процессом самоконтроля или подготовкой последующих измерений. Как только измерительный прибор закончит измер.- , ние, он выдает сигнал об окончании измерения, который поступает в цепь внешне.го запроса соответствующего формирователя 45. Формирователи, связанные с блоком 8 измерителей, имеют более высокий приоритет, чем формирователи, С1зязанные с пультом 14, поэтому по окончании элементарного акта обмена УВМ 2 возвращается

0

5

0

5

0

5

10

15

20

25

к выполнению основной программы, т.е. принимает информацию от измерительного прибора, обрабатывает ее, выдает в случае необходимости результат, переходит к выполению следующего набора программы.

Для организации режимов Останов на заданном наборе, Зацикливание участка программы, а также для синхронизации осциллографа любым набором в режиме Зациклинивание в блок 10 входит двоично-десятичный счетчик 51 наборов.

На .устройство 53 с переключателя пульта 14 подается двоично-десятичный код номера набора, с которого необходимо осуществлять возврат к нужному набору программь. Как только текущий номер набора в счетчике 51 совпадет с номером, набранным на пульте 14 оператора, устройство 53 выдает сигнал запроса, поступающий в линию формирователя 45 (фиг.8). Далее осуществляется стандартная процедура формирования прерывания, УВМ 2 переходит к обработке режима зацик- линивания. При этом счетчик 51 по сигналу управления, подаваемому на , вход от блока 1, записывает номер набора, с которого необходимо начать повторение программы. Далее счетчик 51 осуществляет двоично-десятичный счет по сигналу, подаваемому от блока 1, и считает вновь до того же набора и т.д. При этом, как только текущий номер набора в счетчике 51 совпадает с номером, набрАнным на пульте 14, устройство 52 и узел 54 вырабатывают синхроимпульс, кото-, рым можно синхронизировать осциллограф 44, входящий в блок 8. Таким образои, на экране осциллографа можно наблюдать устойчивую картину, выделяя любое место программы. Аналогично ргализуется режим Останов на заданном наборе. Здесь также осу- ществляется переход к подпрограмме, результатом выполнения которой является останов.. .

Блок 12 предназначен для организации самоконтроля системы.

Источник 61 питания с управляемым делителем 62 напряжения.предназначены для проверки вольтметра 42 посто- янного тока. В блок могут входить и другие датчики в зависимости от состава блока 8.

30

35

40

45

0

5

0

5

0

5

0

5

В процессе эксплуатации системы блок 12 периодически проверяется.

Устройство работает следующим образом.

Информация, хранимая в запоминающем устройстве УВМ 2, в соответствии с программой контроля, хранимой там же, передается на информационные входы коммутатора 6, куда записывается по сигналам управления от УВМ, поступающим на управляющие входы блока 5.

Информация с выхода блока 5 поступает на входы блока 1, где дешифрируется. По управляющим сигналам с выходов блока 1 информация записывается в блок 3, предназначенный для выдачи цифровых сигналов через первый коммутатор 6 на объект 9 контроля , для задания рабочих режимов блока 7, выбора пределов и характера измерений блока 8, управления первым коммутатором 6, для выбора режима работы блока 12, управления режимом работы блока 4 регистров выходной информации ..

Цифровые данные с выхода объекта 9 контроля через первый коммутатор 6 и третий коммутатор 15 поступают соответственно на первый и четвертые входы блока 4, с выхода которого они поступают в УВМ 2 для обработки в со- ответствий с программой контроля.

Блок 7 через первьй коммутатор 6 выдает необходимые аналоговые ;Ьигналы на аналоговые входы объекта 9 контроля. Ответные сигналы с анало- говых выходов объекта 9 контроля через первый коммутатор 6 поступают на измерительные входы блока 8, где измеряются в соответствии с программбй контроля. В блоке 8 результаты измерений преобразуются в цифровую форму и с его первых .выходов поступают на вторые входы блока 4, с выходов которого передаются в УВМ 2 для обработки.

Блок 1 вырабатывает в соответствии с программой управляющие сигналы, предназначенные для синхронной работы всех блоков системы.

Блок 10 предназначен для организации следующих режимов работы системы: 1) автоматическая одноразовая проверка с фиксацией результатов проверки на выходном устройстве без останова при наличии сбоев в объекте контроля; 2) то же, с остановом пос10

15

20

25

91500996

ле каждого сбоя; 3) пошаговый режим работы с остановом после каждого элементарного цикла измерений; 4) автоматическая одноразовая проверка с остановом на любом заданном наборе программы контроля; 5) автоматичес- .кая многоразовая проверка путем зацикливания любого участка программы контроля;; 6) режим корректировки программы; 7) режим самоконтроля системы.

По сигналам с пульта 14 и блока 1 блок 10 рмирует и вьодает на управляющие входы УВМ 2 сигнал запроса на прерывание, и при получении разрешения от УВМ 2 выдает в нее вектор прерывания.

Вектор прерывания предоставляет собой адрес ячейки памяти в УВМ 2 с началом программы, соответствующей заданному режиму, и выдается только той ячейке, в которую поступил запрос от внешнего абонента. Если запросы поступили от нескольких абонентов, то обрабатывается запрос от абонента с более высоким приоритетом . В блоке имеется несколько резервных ячеек формирования векторов прерывания, что позволяет вводить но- jg вые режимы работы или новые измерительные приборы. Входящая в состав блока управления режимами схема сравнения с формирователем формирует синхроимпульс, как только текущий номер программы станет равным номеру, заданному оператором с пульта. Вторая схема сравнения формирует сигнал Конечный набор (как только текущий номер набора станет равным номеру, заданному оператором). При зацикливании участка программы по сигналу Конечный набор происходит переход системы на отработку данного режима. В счетчик наборов записывается но- вое значение номера набора, с которого начнется выполнение программы зацикливания.Таким образом, программа, будет многократно повторяться от набора, записанного в счетчик наборов по прерыванию, и до конечного набора, заданного на пульте оператора.

Второй коммутатор I1 предназначен для осуществления самоконтроля системы во время вып&лнения основной программы контроля объекта. Такой режим возможен потому, что время измерения параметров сигналов блоком

35

40

45

50

55

н п н н ко .в ра в УВ фи ко УВ си вы бл

вы щи эт хо вы

на сп ко по на с 6 ри па бл нн ра

бл 6 бл оп по хо ве то да вх

ва

10

15

20

25

0996

g

35

0

5

0

5

10

8 велико пр сравнению с машинным циклом УВМ. Поэтому во время измерения выходного сигнала блоком 8 УВМ 2 осуществляет программу контроля отдельных блоков системы и их связен.

По сигналу с блока 1 на начале измерения блок 10 формирует запрос на прерывание и по получении от УВМ 2 разрешения выдает в УВМ 2 вектор прерывания, вызывая тем самым выполнение одной из подпрограмм самоконтроля. УВМ 2 выдает контрольные коды на блоки 3 и 5. С выходов этих блоков контрольные коды поступают на соот- .ветствующие входы второго коммутатора 11, с выхода которого выдаются в определенной последовательности в УВМ 2 для обработки. Если УВМ 2 зафиксирует несоответствие какого-либо кода, принятого с выхода коммутатора 11, с эталонным, хранящимся в памяти УВМ 2, происходит останов работы системы, и на устройство отображения выводится информация об отказавшем блоке.

После окончания измерения блок 8 выдает специальный сигнал, поступающий на вторые входы блока 10. По этому сигналу блок 1 О формирует необ- ходимь1е сигналы для возврата УВМ к выполнению основной программы.

Блок 12 эталонных сигналов предназначен для полной проверки работоспособности системы в режиме самоконтроля. Он выдает ряд эталонных постоянных, переменных и мпульсньгх напряжений, которые в соответствии с программой через первый коммутатор 6 поступают на соответствующие изме- . рительные входы блока 8. Измеренные параметры эталонных сигналов через блок 4 передаются в УВМ 2, где срав ннвают с эталонным значением этих параметров.

Дпя проверки работоспособности блока 7 его выходы через коммутатор 6 связаны с измерительными вхсдами блока 8. Процесс контроля аналогичен описанному Bbmie. Для осуществления полного контроля коммутатора 6 необходимо перемкнуть перемычками соответствующие входы г выходы коммутатора (первые выходы с гретыми входами и вторые выходы с четвертыми входами).

Таким образом, контролем охватывается вся аппаратнля часть системы.

что значительно повьшает достоверность проводимых ею измерений.

Формула изобретения

Автоматизированная система контроля параметрбв электронных схем, со-- ., держащая пульт оператора, блок ввода- вывода, блок регистраторов адреса, блок управления режимами, блок синхронизации, сострящий их элемента ЗАЛРЕТ и п формирователей управляющих сигналов, каждый из которых содержит дешифратор, элемент ИЛИ, узел задания сигналов подтверждения, выход которого соединен с выходом формирователя управляющих сигналов, а вход -. с выходом элемента ИЛИ, входы коТо- J рого связаны с выходами дешифратора, , служащими управляющими входами формирователя управляющих сигнало,в, входы дешифратора подключены к входам младших разрядов адреса, выбора и разрешения формирования формирователя управляющих сигналов, входы младших разрядов адреса всех формирователей управляющих сигналов, соединенные между собой поразрядно, и входы выбора формирователя управляющих сигналов связаны с первыми входами блока синхронизации, а входы разрешения .формирования через элемент ЗАПРЕТ - с вторыми входами блока синхронизации, управляющие выходы формирователей управляющих сигналов - с первыми выходами блока синхрониза-: ции, а выходы подтверждения - с вторым выходом блока синхронизации, блок регистров входной информации, состоящий из п устройств согласования и п 16-разрядных регистров, информационные, объединенные поразрядно, и управляющие входы которых соединехш соответственно с первыми информационными и вторыми управляющими входами блока регистров вход- ной информации, а выходы - с входами соответствующего устройства сбгласо- вания, выходы каждого из которых связаны с первыми выходами блока регистров входной информации, блок задания эталонных сигналов, блок ре- . гистров выходной информации, состоящий из двух устройств согласования и двух одинаковых п-разрядных устройств хранения цифровой информации, информационные параллельные входы первого из которьк подключены к пер- .

0

5

0

5

0

5

0

5

0

5

вым информационным входам блока регистров выходной информации, второго - к третьим информационным входам блока регистров выходной инфор- ,. мации, управляющие входы записи параллельной цифровой информации обоих устройств хранения цифровой информации соединены с управляющими ми блока регистров выходной информации, а выходы - с входами своих устройств согласования, входы разрешения считывания информации которых связаны с третьими информационными входами блока регистров выходной информации, а выходы, объединенные поразрядно, с выходами блока регистров выходной информации, блок стиму- лирующих сигналов, блок измерителей вкодных сигналов, первый и второй коммутаторы и управляющую вычислительную машину, первые информахщон- ные выходы которой соединены с первыми информационными вх одами блока регистров адреса и с первыми информационными входами блока регистров вход, ной информации, первые информационные входы - с информационными выходами блока регистров выходной информации, с выходами второго коммутатора и с первыми информационными выходами блока управления режимами, вторые информационные входы и рыходы управля- ющей вычислительной машины связаны с вторыми информационными выходами и входами блока регистров адреса и с первыми выходами и входами блока синхронизации, вторые выходы которого подключены к управляющим входам второго коммутатора, к первым управляющим входам блока управления й°жима- ми, К первым входам блока стимулирую-, щих сигналов, к первым входам блока измерителей входных -сигналов, к вторым информационным входам блока регистров входной информации и к вторым информационным входам блока регистров выходной информации, управляющие входы которого связаны с первыми выходами блока регистров входной информации, которые также связаны с первыми информационными входами первого коммутатора и вторыми входами блока стимулирующих сигналов, выходы которого подключены к вторым информационным вхолай первого коммуатато- ра, первые выходы которого связаны с выходами цифровых сигналов системы, вторые выходы - с выходами аналотовых сигналов системы, третьи информационные входы - с входами цифровых сигналов системы, четвертые информационные входы - с входами ана логовых сигналов системы, а третьи выходы соединены с третьими входами блока измерителей входных сигналов, вторые выходы которого связаны с вторыми управляющими входами блока управления режимаш1, третьи управляющие входы которог подключены к выходам пульта оператора, четвертые управляющие входы и вторые управляющие выходы - соответственно к управляющим выходам и уп- равляющим входам управляющей вычислительной машины, третьи информационные входы и третьи информационные выходы управляющей вычислительной машины связаны с входами и выходами блока ввода-вывода, вторые выходы блока регистров входной информации соединены с первыми информационными входами второго коммутатора, с входами блока задания эталонных сигналов, с управляющими входами первого коммутатора, пятые информационные входы которого связаны с выходом блока задания эталонньк сигналов, а четвертые выходы - с первыми информацион- ными входами блока регистров выходной информации, выходы блока регистров адреса подключены к вторым информаци- оннфм входам второго коммутатора и к первым входам блока синхронизации, четвертьш вход блока измерителей входных сигналов соединен с третьим управляющим выходом блока управления режимами, отличающаяся

тем, что, G целью расширения функциональных возможностей системы за счет кон-троля последовательных цифровых кодов, в нее введен третий . коммутатор, содержащий четыре ключа, управляющие входы каждого из которых соединены с управляющими . входами третьего коммутатора, информационные входы - с информационными входами третьего комуутатора, а информационные выходы подключены .к выходам третьего коммутатора, в блок синхронизации введен п+1 -и формирователь управляющих сигналов,

- , /. )0 о 5 20 25эп

35

40

45

50

вход разрешения формирования котррог го соединен с выходом элемента ЗАПРЕТ, входы младших регистров адреса и выбора формирователя управляющих сигналов связаны с первыми входами блока синхронизации, а выход подтверждения - с вторым выходом блока синхронизации, в блок регистров входной информации введены согласующее устройство и два 4-разрядных регистра, управляющий .и информационный входы которых соединены соответственно с третьим информационным и с первыми информационными входами блока регистров входной информации, а ВЫХОДЕ - с входами соответствующего согласующего устройства, два первых выхода которого связаны соответственно с третььим и четвертым выходами .блока регистров входной информации, а четыре выхода - с вторыми выходами блока регистров входной информации, а в блоке регистров выходной информации каждое из устройств хранения цифровой информации выполнено на регистрах сдвига, стробирующие входы которых и информационные входы первых регистров обоих устройств соединены с четвертыми информационными входами блока регистров выходной информации, входы п-го регистра - со старшими выходными разрядами своего (n-l)-ro регистра, а управляющие входы обоих устройств связаны с пятым информационным и шестым информационным входами блока регистров выходной информации соответственно, третий выход блока синхронизации подключен к. управляющему входу блока регистров входной информации, третий и четвертый выходы которого соединены соответственно с пятым информационным и шестым информационным входами блока регистров выходной информации,а вторые выходы - с управляющими входами третьего коммутатора, информационные входы которого связаны с входами циф - ровых сигналов системы, а выхо- 1цы - с четвертыми информационны- ми входами блока регистров выход- ной информации.

If

гр

Ър

| название | год | авторы | номер документа |

|---|---|---|---|

| АВТОМАТИЗИРОВАННАЯ СИСТЕМА КОНТРОЛЯ ПАРАМЕТРОВ ЭЛЕКТРОННЫХ СХЕМ | 1991 |

|

RU2106677C1 |

| Автоматизированная система контроля параметров электронных схем | 1981 |

|

SU1010602A1 |

| Устройство для контроля параметров | 1988 |

|

SU1513418A1 |

| Устройство контроля параметров | 1990 |

|

SU1800447A1 |

| Система автоматического контроля параметров электронных схем | 1989 |

|

SU1700538A1 |

| Автоматизированная система контроля | 1989 |

|

SU1695269A1 |

| Устройство для контроля электронных изделий | 1978 |

|

SU951323A1 |

| Устройство для обмена информацией управляющей вычислительной машины с объектами управления | 1982 |

|

SU1030792A1 |

| Устройство для контроля интегральных схем | 1980 |

|

SU966699A1 |

| Устройство для сопряжения управляющей вычислительной машины с периферийными устройствами | 1983 |

|

SU1201841A1 |

Изобретение относится к системам контроля и может быть использовано для контроля узлов радиоэлектронной аппаратуры. Цель изобретения - расширение функциональных возможностей системы. Система содержит блок 1 синхронизации, блоки 3 и 4 регистров входной и регистров выходной информации соответственно, блок 5 регистров адреса, блок 7 стимулирующих сигналов, блок 8 измерителей входных сигналов, блок 10 управления режимами, блок 12 задания эталонных сигналов, блок 13 ввода-вывода, управляющую вычислительную машину 2, коммутаторы 6, 11, 15 и пульт 14 оператора. Изобретение обеспечивает контроль как параллельных, так и последовательных кодов, поступающих с электронных схем. 11 ил.

.Ор(1} 15р(1}

о

Ор(} iBp(ff )

Opfff l

фиг.Ъ

(риг 5

I

33) I

f

iri I

36

,

II .

L...l

фиг

-4

I

vr

ffO

h

.,j

I

u

T

I

41/3 r-h

-П.j

d/«5

«3

И

u

tSi

«5

n

фие.8

фиг.9

| Система автоматического контроля параметров | 1977 |

|

SU746435A1 |

| Кипятильник для воды | 1921 |

|

SU5A1 |

| Автоматизированная система контроля параметров электронных схем | 1981 |

|

SU1010602A1 |

| Кипятильник для воды | 1921 |

|

SU5A1 |

Авторы

Даты

1989-08-15—Публикация

1987-07-06—Подача