(21) 47 8307М

(22)11,10.89

(А6) 23.12.91. Бюл. №

(72) Л.С.Флейш и Л.В.Бартоломей

(53) 621.396(088.8)

(56)Авторское свидетельство СССР 1Г 302717, кл. G 06 F 11/00, 1969.

Авторское свидетельство СССР N 98576, кл. G 05 В 23/02, 1981 (прототип).

(51) СИСТЕМА АВТОМАТИЧЕСКОГО КОНТРОЛЯ ПАРАМЕТРОВ ЭЛЕКТРОННЫХ СХЕМ

(57)Изобретение относится к вычислительной технике и может быть использовано в системах автоматического контроля параметров полупроводниковых приборов, интегральных схем,

функциональных узлов, субблоков и других электронных устройств. Цель изобретения - повышение достоверности результатов контроля за счет проверки параметров сигналов объекта контроля на рабочей частоте. Система автоматического контроля параметров электронных схем содержит управляющую вычислительную машину, измерительные станции, рабочие посты. Система позволяет формировать на каждый входной контакт контролируемого устройства требуемые стимулирующие воздействия по программе, записанной для каждого входного контакта в ОЗУ тестовых комбинаций. 2 з.п.ф-лы, 10 ил.

i (Л

| название | год | авторы | номер документа |

|---|---|---|---|

| Система автоматического контроля параметров электронных схем | 1981 |

|

SU985764A1 |

| Система для автоматического контроля параметров интегральных схем | 1978 |

|

SU746443A1 |

| Автоматизированная система контроля | 1989 |

|

SU1695269A1 |

| Устройство для контроля монтажа | 1986 |

|

SU1312616A1 |

| Автоматизированная система контроля параметров электронных схем | 1987 |

|

SU1500996A1 |

| Устройство для контроля монтажных соединений | 1988 |

|

SU1606978A1 |

| АВТОМАТИЗИРОВАННАЯ СИСТЕМА КОНТРОЛЯ ПАРАМЕТРОВ ЭЛЕКТРОННЫХ СХЕМ | 1991 |

|

RU2106677C1 |

| УСТРОЙСТВО ДЛЯ КОНТРОЛЯ УПРАВЛЯЮЩЕЙ ВЫЧИСЛИТЕЛЬНОЙ МАШИНЫ | 1995 |

|

RU2094842C1 |

| Устройство для обнаружения и локализации неисправностей цифровых блоков | 1982 |

|

SU1067507A1 |

| Устройство для задания тестов | 1983 |

|

SU1141379A2 |

Изобретение относится к вычислительной технике и может быть использовано в системах автоматического контроля параметров полупроводниковых приборов, интегральных схем, БИС, функциональных узлов, субблоков и других электронных устройств.

Цель изобретения - повышение достоверности результатов контроля за счет проверки параметров сигналов контролируемого устройства на рабочей частоте.

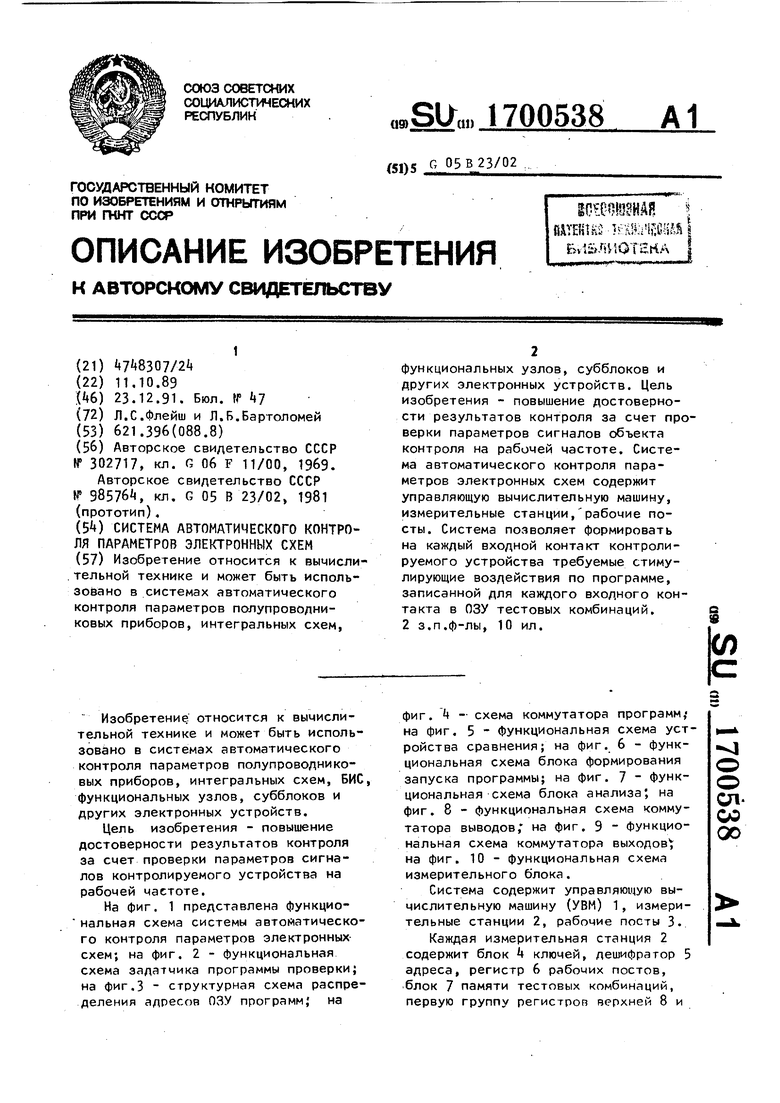

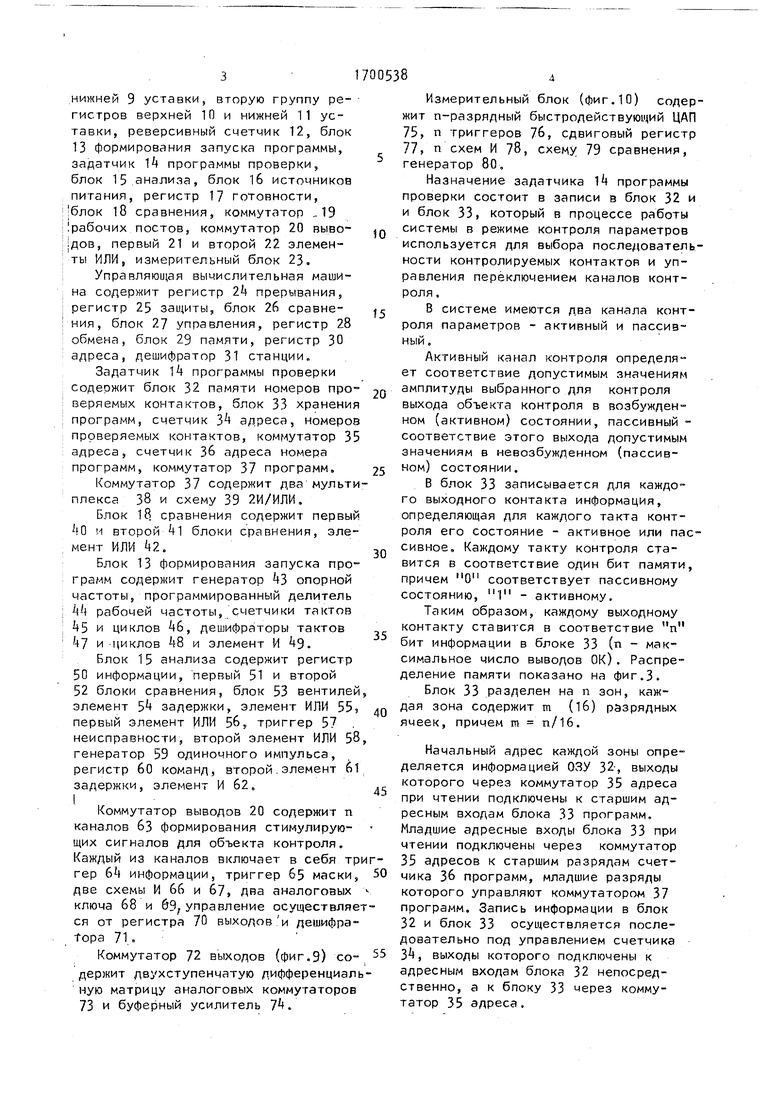

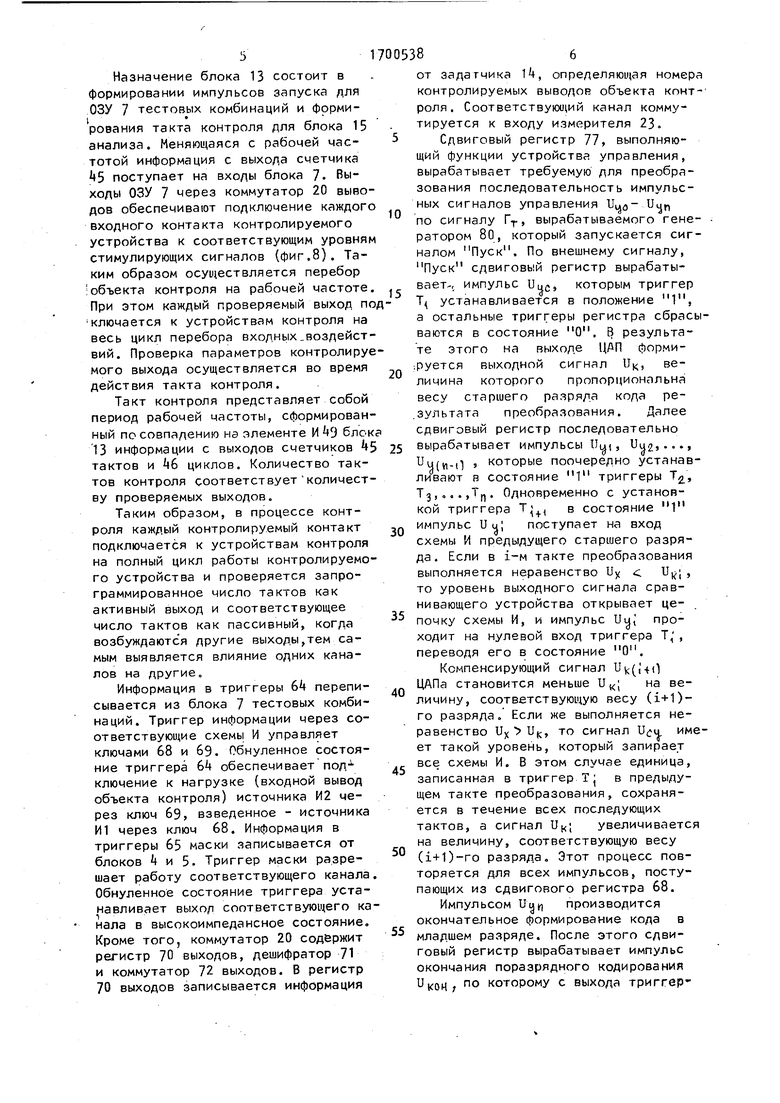

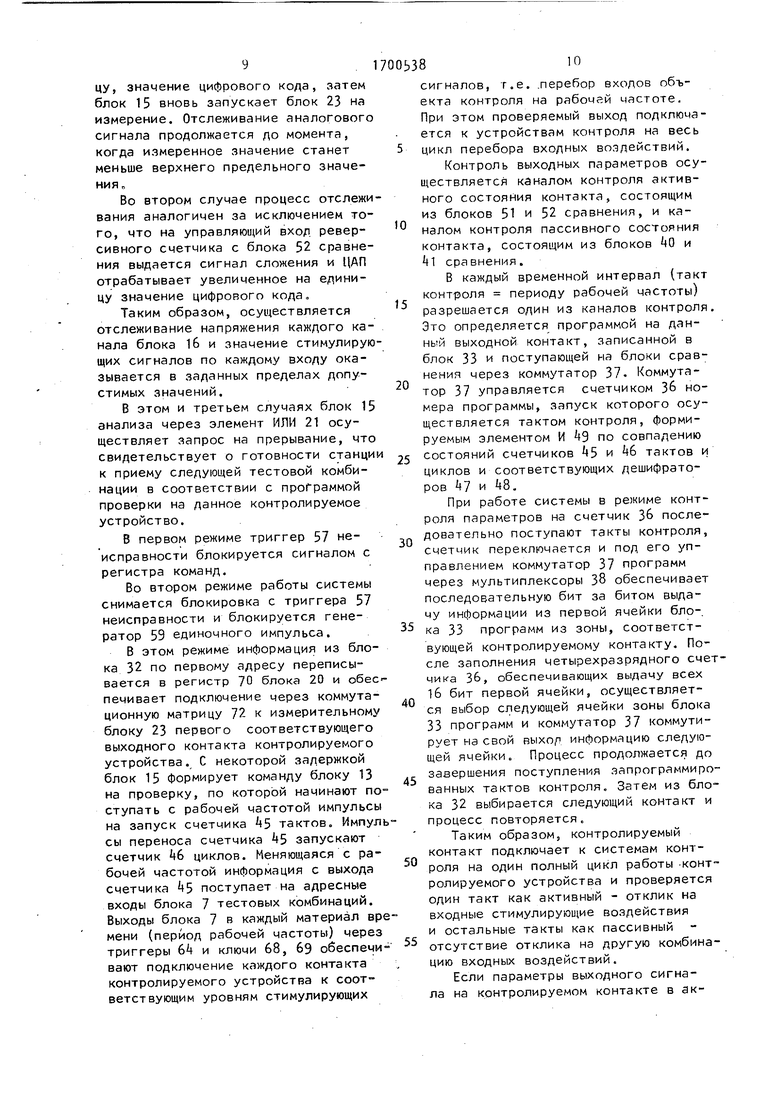

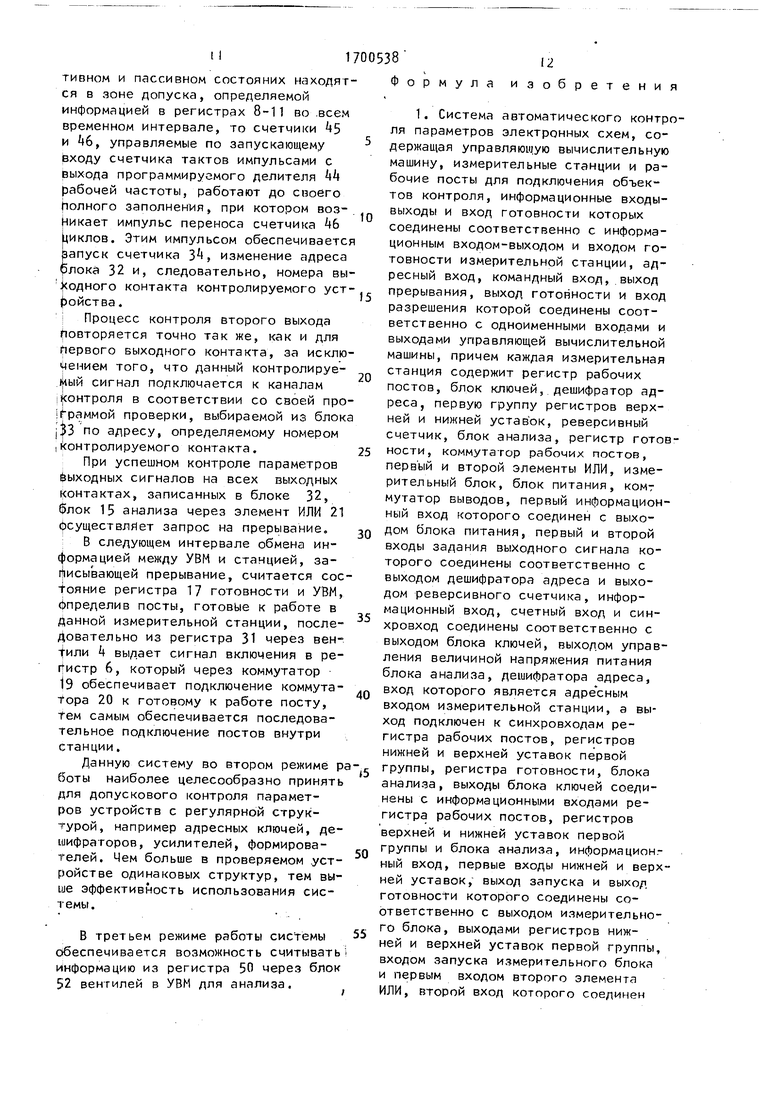

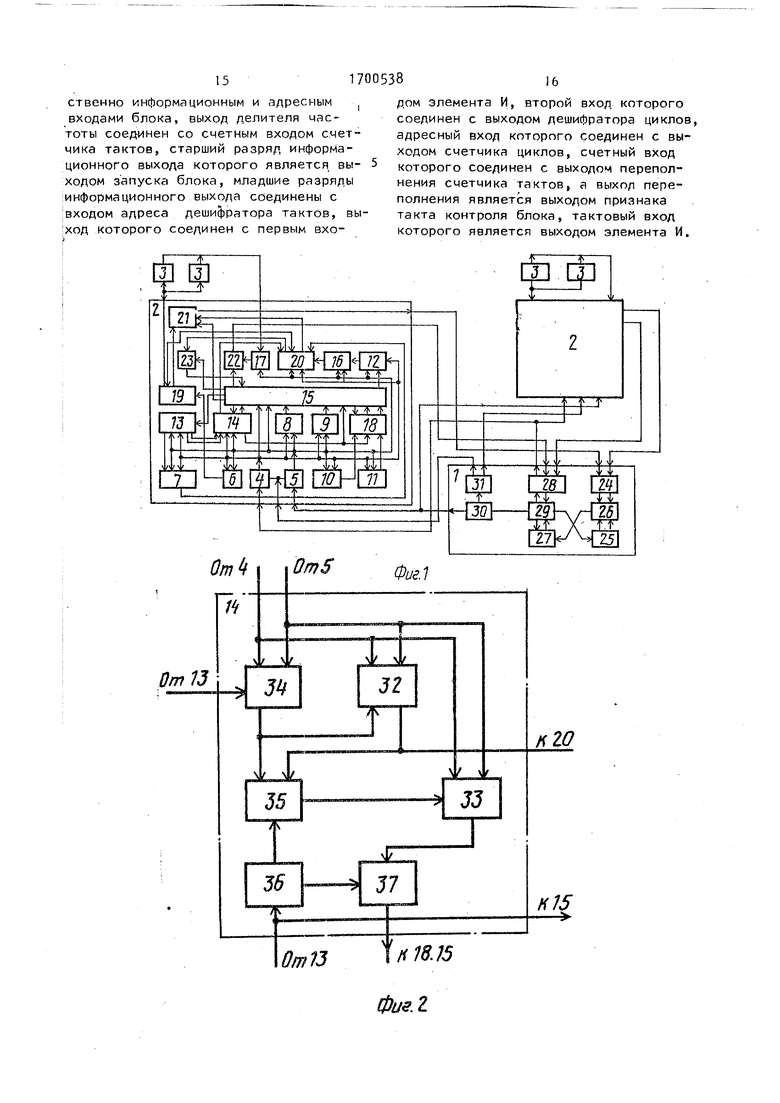

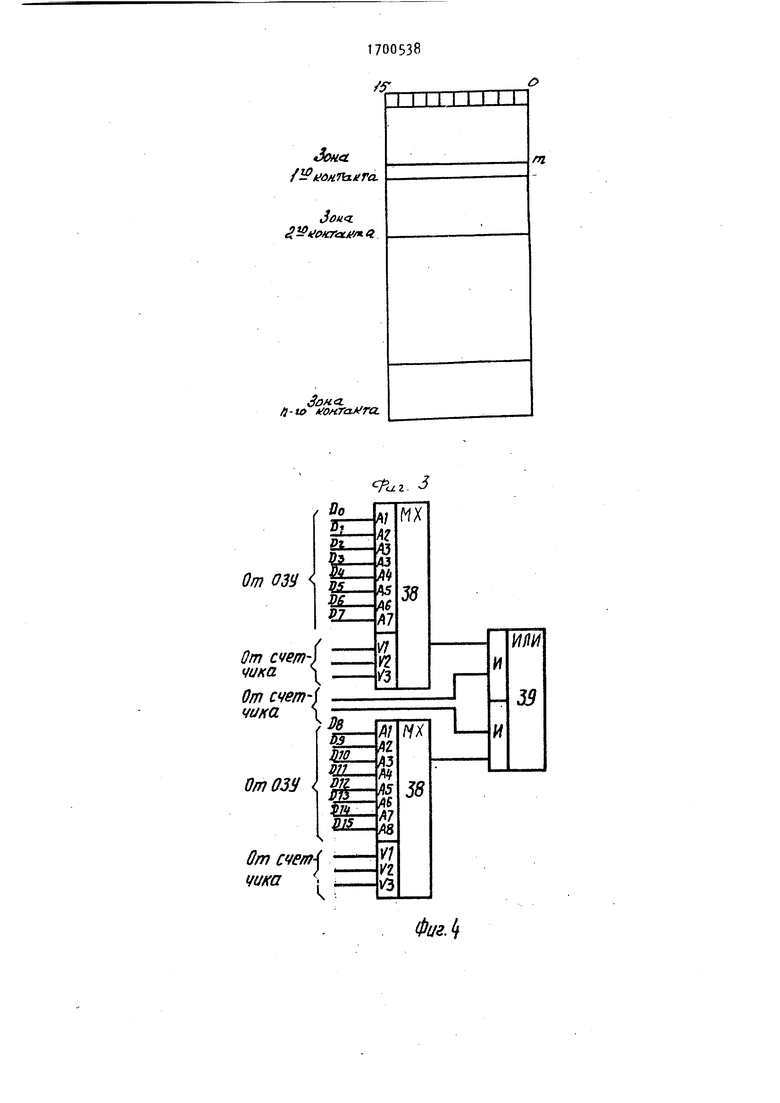

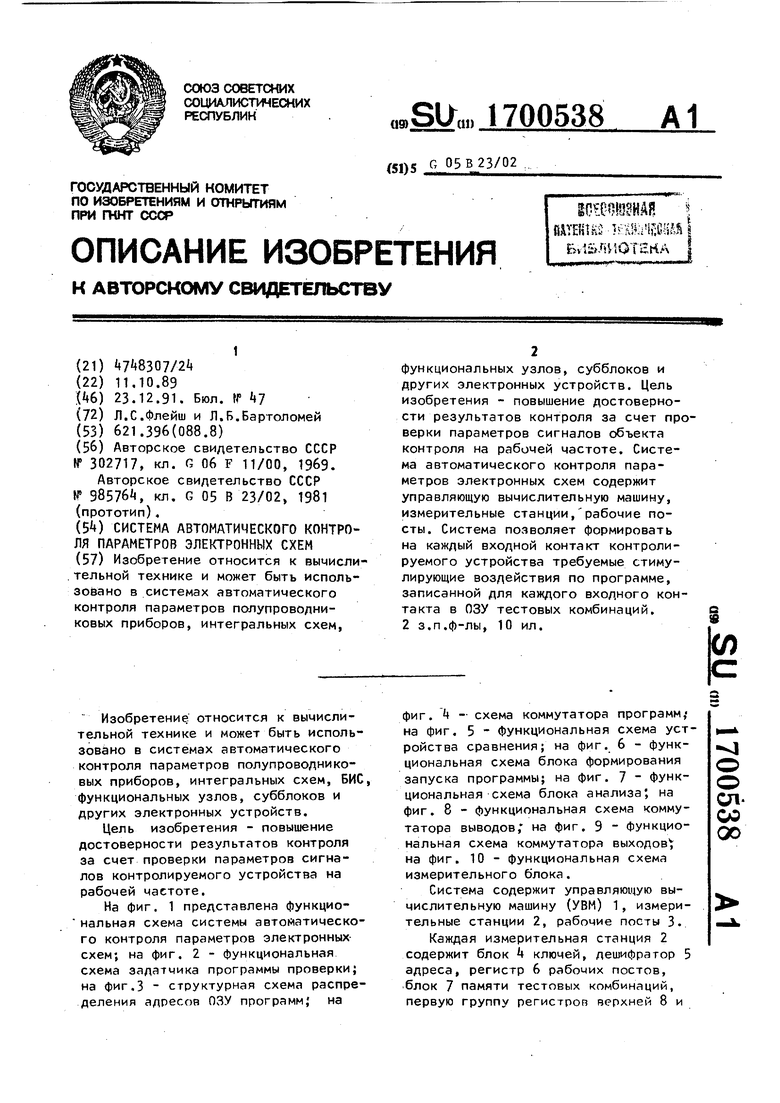

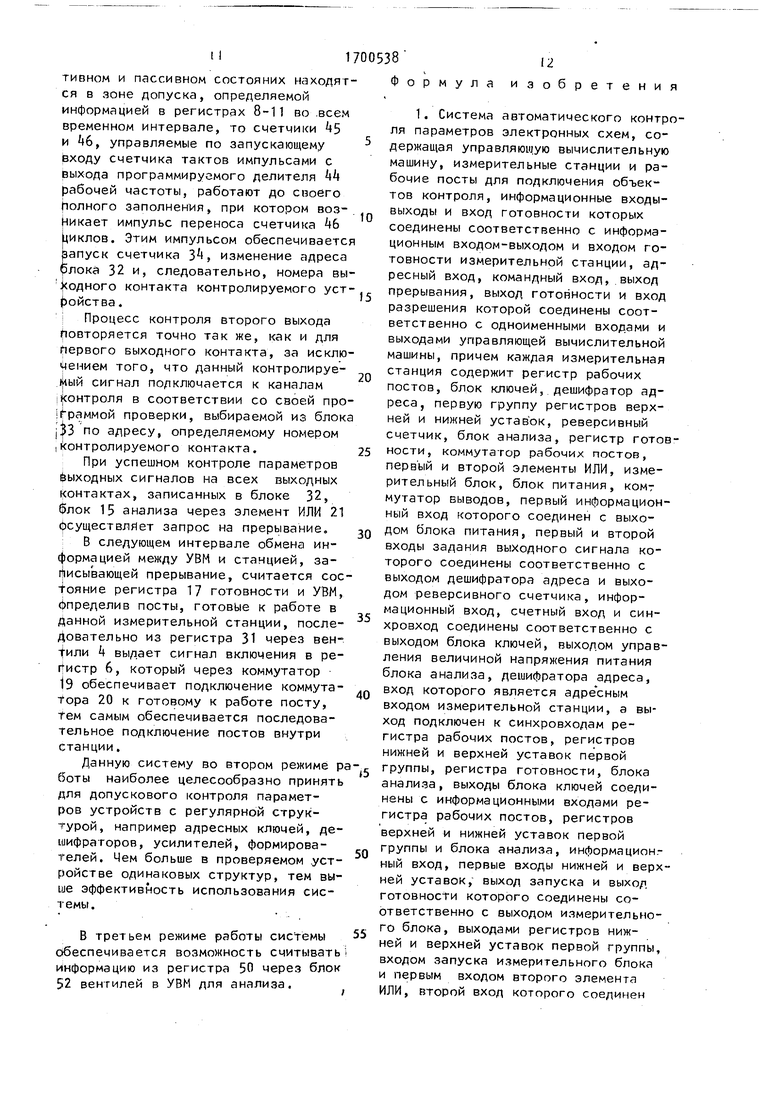

На фиг. 1 представлена функцио- нальная схема системы автоматического контроля параметров электронных схем; на фиг. 2 - функциональная схема задатчика программы проверки; на фиг.З - структурная схема распределения адресов ОЗУ программ, на

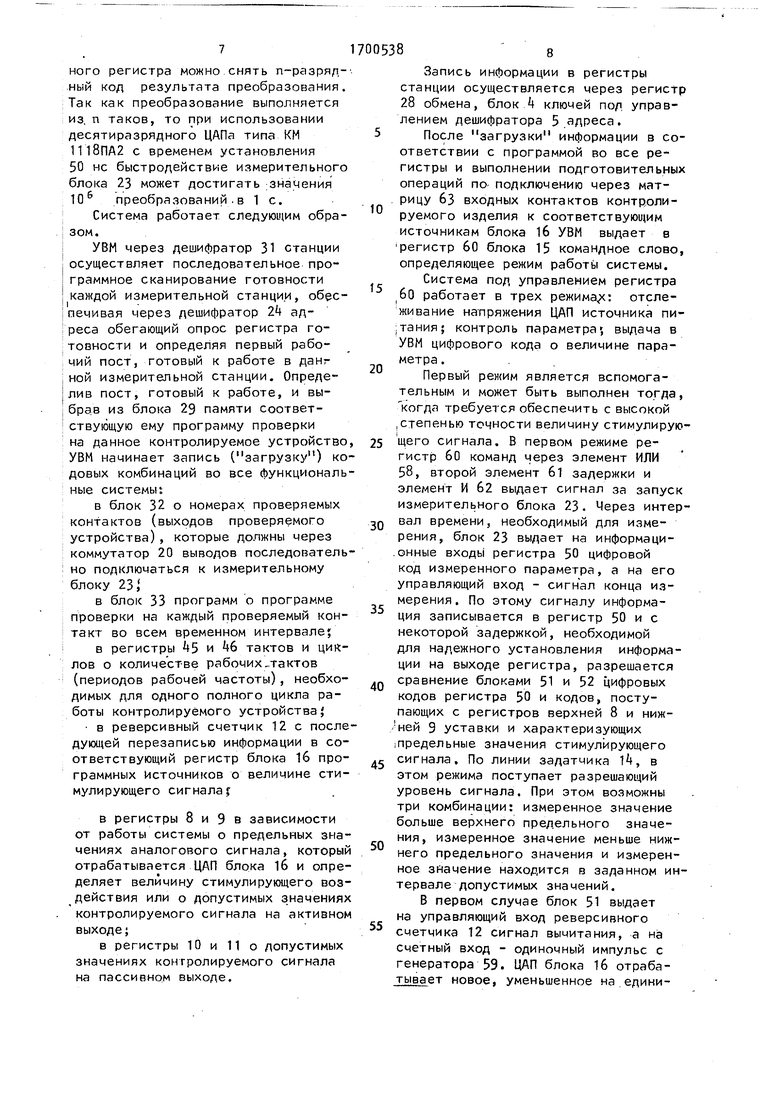

фиг. k - схема коммутатора программ/ на фиг. 5 - функциональная схема устройства сравнения; на фиг. 6 - функциональная схема блока формирования запуска программы; на фиг. 7 - функциональная схема блока анализа; на фиг. 8 - функциональная схема коммутатора выводов, на фиг. 9 - функциональная схема коммутатора выходов на фиг. 10 - функциональная схема измерительного блока.

Система содержит управляющую вычислительную машину (УВМ) 1, измерительные станции 2, рабочие посты 3.

Каждая измерительная станция 2 содержит блок k ключей, дешифратор 5 адреса, регистр 6 рабочих постов, блок 7 памяти тестовых комбинаций, первую группу регистров верхней 8 и

сл

оэ

00

нижней 9 уставки, вторую группу регистров верхней 10 и нижней 11 уставки, реверсивный счетчик 12, блок 13 формирования запуска программы, задатчик 14 программы проверки, блок 15 анализа, блок 16 источников питания, регистр 17 готовности, блок 18 сравнения, коммутатор „19 рабочих постов, коммутатор 20 выво- .дов, первый 21 и второй 22 элементы ИЛИ, измерительный блок 23.

Управляющая вычислительная машина содержит регистр 24 прерывания, регистр 25 защиты, блок 26 сравнения, блок 27 управления, регистр 28 обмена, блок 29 памяти, регистр 30 адреса, дешифратор 31 станции.

Задатчик 14 программы проверки содеожит блок 32 памяти номеров проверяемых контактов, блок 33 хранения программ, счетчик 34 адреса, номеров проверяемых контактов, коммутатор 35 адреса, счетчик 36 адреса номера программ, коммутатор 37 программ.

Коммутатор 37 содержит два мульти плекса 38 и схему 39 2И/ИЛИ.

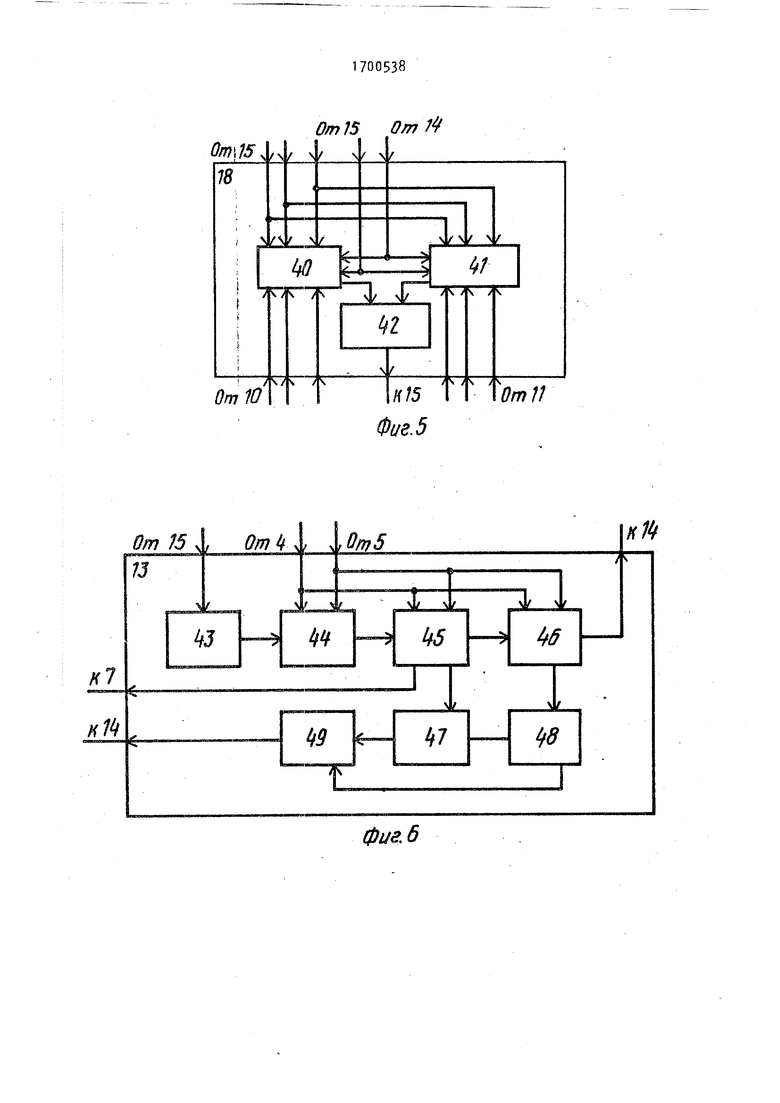

Блок 18 сравнения содержит первый 40 ч второй 41 блоки сравнения, элемент ИЛИ 42.

Блок 13 формирования запуска программ содержит генератор 43 опорной частоты, программированный делитель

44рабочей частоты, счетчики тактов

45и циклов 46, дешифраторы тактов 47 и циклов 48 и элемент И 49.

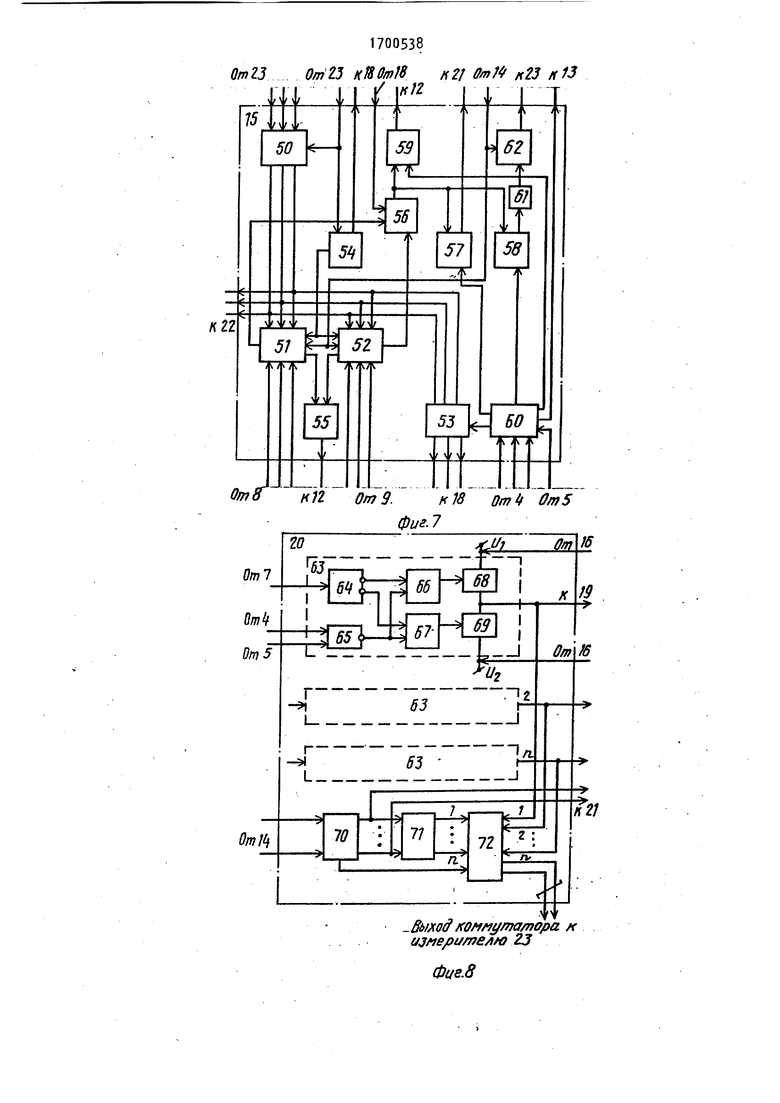

Блок 15 анализа содержит регистр 50 информации, первый 51 и второй 52 блоки сравнения, блок 53 вентилей элемент 54 задержки, элемент ИЛИ 55, первый элемент ИЛИ 56, триггер 57 неисправности, второй элемент ИЛИ 58 генератор 59 одиночного импульса, регистр 60 команд, второй элемент 61 задержки, элемент И 62.

Коммутатор выводов 20 содержит п каналов 63 формирования стимулирующих сигналов для объекта контроля. Каждый из каналов включает в себя триггер 64 информации, триггер 65 маски, 50 две схемы И 66 и 67, два аналоговых ключа 68 и 69, управление осуществляется от регистра 70 выходов и дешифратора 71 .

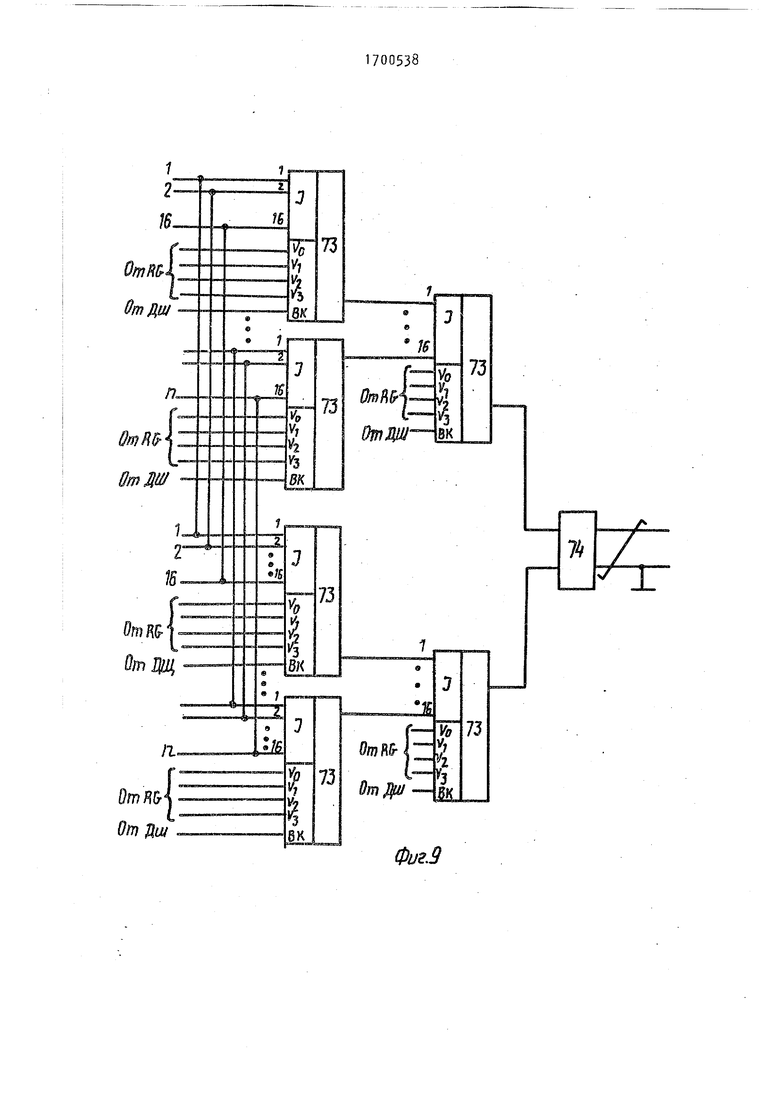

Коммутатор 72 выходов (фиг.9) со- 55 держит двухступенчатую дифференциальную матрицу аналоговых коммутаторов 73 и буферный усилитель 74.

10

00538,1

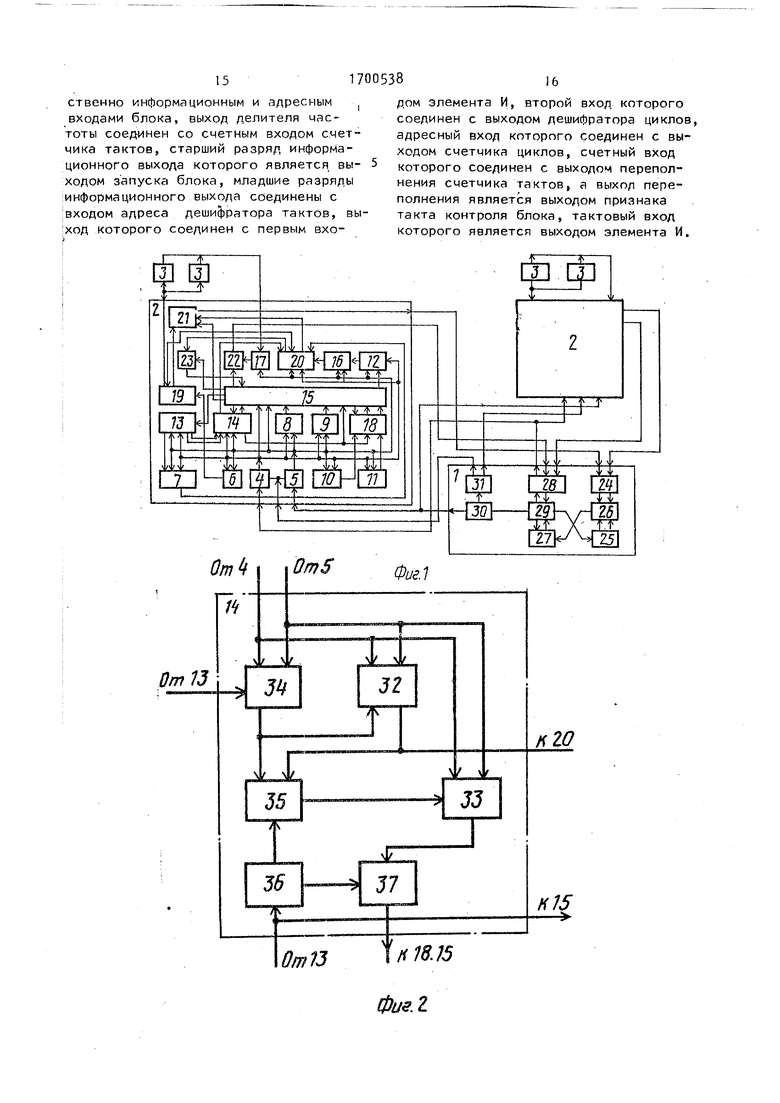

Измерительный блок (фиг.10) содержит n-разрядный быстродействующий ЦАП 75, п триггеров 76, сдвиговый регистр 77, п схем И 78, схему 79 сравнения, генератор 80.

Назначение задатчика 14 программы проверки состоит в записи в блок 32 и и блок 33, который в процессе работы системы в режиме контроля параметров используется для выбора последовательности контролируемых контактов и управления переключением каналов контроля .

В системе имеются два канала контроля параметров - активный и пассивный.

Активный канал контроля определяет соответствие допустимым значениям амплитуды выбранного для контроля выхода объекта контроля в возбужденном (активном) состоянии, пассивный - соответствие этого выхода допустимым значениям в невозбужденном (пассивном) состоянии.

В блок 33 записывается для каждого выходного контакта информация, определяющая для каждого такта контроля его состояние - активное или пассивное. Каждому такту контроля ставится в соответствие один бит памяти,

15

20

25

30

5

0

5

0

5

соответствует пассивному п in

причем О

состоянию, I - активному.

Таким образом, каждому выходному контакту ставится в соответствие п бит информации в блоке 33 (п - максимальное число выводов ОК). Распределение памяти показано на фиг.З.

Блок 33 разделен на п зон, каждая зона содержит m (16) разрядных ячеек, причем m n/16.

Начальный адрес каждой зоны определяется информацией ОЗУ 32-, выходы которого через коммутатор 35 адреса при чтении подключены к старшим адресным входам блока 33 программ. Младшие адресные входы блока 33 при чтении подключены через коммутатор 35 адресов к старшим разрядам счетчика 36 программ, младшие разряды которого управляют коммутатором 37 программ. Запись информации в блок 32 и блок 33 осуществляется последовательно под управлением счетчика 34, выходы которого подключены к адресным входам блока 32 непосредственно, а к блоку 33 через коммутатор 35 адреса.

Назначение блока 13 состоит в формировании импульсов запуска для ОЗУ 7 тестовых комбинаций и формирования такта контроля для блока 15 анализа. Меняющаяся с рабочей частотой информация с выхода счетчика 5 поступает на входы блока 7. Выходы ОЗУ 7 через коммутатор 20 выводов обеспечивают подключение каждого входного контакта контролируемого устройства к соответствующим уровням стимулирующих сигналов (фиг,8). Таким образом осуществляется перебор объекта контроля на рабочей частоте. При этом каждый проверяемый выход по ключается к устройствам контроля на весь цикл перебора входных.воздействий. Проверка параметров контролируемого выхода осуществляется во время действия такта контроля.

Такт контроля представляет собой период рабочей частоты, сформированный по совпадению нэ элементе И 49 блок 13 информации с выходов счетчиков 45 тактов и 46 циклов. Количество тактов контроля соответствует количеству проверяемых выходов.

Таким образом, в процессе контроля каждый контролируемый контакт подключается к устройствам контроля на полный цикл работы контролируемого устройства и проверяется запрограммированное число тактов как активный выход и соответствующее число тактов как пассивный, когда возбуждаются другие выходы,тем самым выявляется влияние одних каналов на другие.

Информация в триггеры 64 переписывается из блока 7 тестовых комбинаций. Триггер информации через соответствующие схемы И управляет ключами 68 и 69. Обнуленное состояние триггера 64 обеспечивает под-1 ключение к нагрузке (входной вывод объекта контроля) источника И2 через ключ 69, взведенное - источника И1 через ключ 68. Информация в триггеры 65 маски записывается от блоков I и 5. Триггер маски разрешает работу соответствующего канала. Обнуленное состояние триггера устанавливает выход соответствующего канала в высокоимпедансное состояние. Кроме того, коммутатор 20 содержит регистр 70 выходов, дешифратор 71 и коммутатор 72 выходов. В регистр 70 выходов записывается информация

0

5

0

5

0

5

0

5

0

5

от задатчика 14, определяющая номера контролируемых выводов объекта контроля. Соответствующий канал коммутируется к входу измерителя 23.

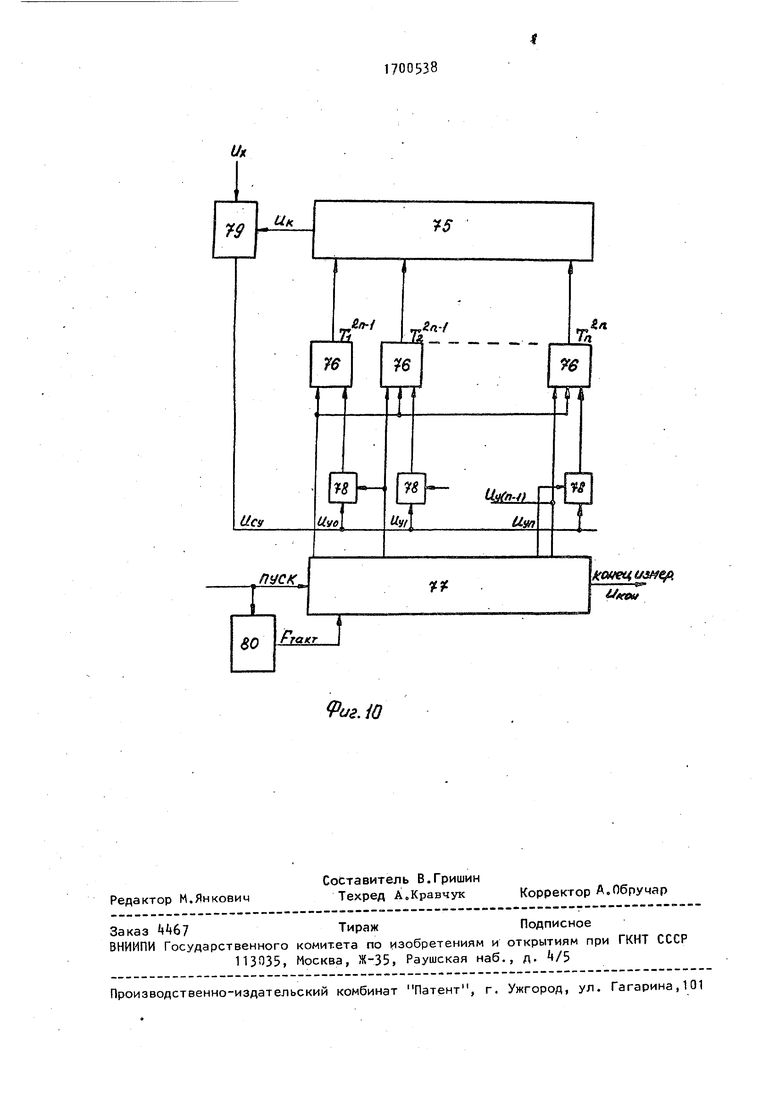

Сдвиговый регистр 77, выполняющий функции устройства управления, вырабатывает требуемую для преобразования последовательность импульсных сигналов управления Vuo Uun по сигналу Гт, вырабатываемого гене- ратором 80, который запускается сигналом Пуск. По внешнему сигналу, Пуск сдвиговый регистр вырабатывает-, импульс ULIC, которым триггер Т устанавливается в положение 1, а остальные триггеры регистра сбрасываются в состояние О. В результате этого на выходе ЦАП форми- .руется выходной сигнал UK, величина которого пропорциональна весу старшего разряда кода результата преобразования. Далее сдвиговый регистр последовательно вырабатывает импульсы Um , Uug,..., T4(n-il s которые поочередно устанавливают в состояние 1 триггеры Т),...,ТП. Одновременно с установкой триггера Т + ( в состояние 1м импульс U и; поступает на вход схемы И предыдущего старшего разряда. Если в i-м такте преобразования выполняется неравенство Uy c Uk; , то уровень выходного сигнала сравнивающего устройства открывает цепочку схемы И, и импульс Uu, проходит на нулевой вход триггера Т, , переводя его в состояние О.

Компенсирующий сигнал 11(0 ЦАПа становится меньше UK; на величину, соответствующую весу (i+1)- го разряда. Если же выполняется неравенство U) UK, то сигнал и™ имеет такой уровень, который запирает все схемы И. В этом случае единица, записанная в триггер Tj в предыдущем такте преобразования, сохраняется в течение всех последующих тактов, а сигнал U«; увеличивается на величину, соответствующую весу (i+1)-ro разряда. Этот процесс повторяется для всех импульсов, поступающих из сдвигового регистра 68.

Импульсом Uqfl производится окончательное формирование кода в младшем разряде. После этого сдвиговый регистр вырабатывает импульс окончания поразрядного кодирования икоц; п° которому с выхода триггер

71

ного регистра можно снять п разряд- ый код результата преобразования. ак как преобразование выполняется з п таков, то при использовании есятиразрядного ЦАПа типа КМ 1118ПА2 с временем установления 50 не быстродействие измерительного блока 23 может достигать значения 10 6 преобразований в 1 с.

Система работает следующим образом.

УВМ через дешифратор 31 станции осуществляет последовательное программное сканирование готовности каждой измерительной станции, обесечивая через дешифратор 2k адреса обегающий опрос регистра гоовности и определяя первый рабочий пост, готовый к работе в данг ной измерительной станции. Опреде- лив пост, готовый к работе, и выбрав из блока 29 памяти соответствующую ему программу проверки на данное контролируемое устройство, УВМ начинает запись (загрузку) кодовых комбинаций во все Функциональные системы;

в блок 32 о номерах проверяемых контактов (выходов проверяемого устройства), которые допжны через коммутатор 20 выводов последовательно подключаться к измерительному блоку 23 j

в блок 33 программ о программе проверки на каждый проверяемый контакт во всем временном интервале;

в регистры 5 и А6 тактов и циклов о количестве рабочих тактов (периодов рабочей частоты), необходимых для одного полного цикла работы контролируемого устройстваJ

в реверсивный счетчик 12 с последующей перезаписью информации в соответствующий регистр блока 16 программных Источников о величине стимулирующего сигнала Ј

в регистры 8 и 9 в зависимости от работы системы о предельных значениях аналогового сигнала, который отрабатывается ЦАП блока 16 и определяет величину стимулирующего воздействия или о допустимых значениях контролируемого сигнала на активном выходе;

в регистры 10 и 11 о допустимых значениях контролируемого сигнала на пассивном выходе.

10

20

25

00538в

Запись информации в регистры станции осуществляется через регистр 28 обмена, блок 4 ключей под управлением дешифратора 5 адреса. 5 После загрузки информации в соответствии с программой во все регистры и выполнении подготовительных операций по подключению через матрицу 63 входных контактов контролируемого изделия к соответствующим источникам блока 16 УВМ выдает в

регистр 60 блока 15 командное слово, определяющее режим работы системы. Система под управлением регистра

(60 работает в трех режима : отслеживание напряжения ЦАП источника пи,тания; контроль параметра; выдача в УВМ цифрового кода о величине параметра .

Первый режим является вспомогательным и может быть выполнен тогда, когда требует ся обеспечить с высокой степенью точности величину стимулирующего сигнала. В первом режиме регистр 60 команд через элемент ИЛИ 58, второй элемент 61 задержки и элемент И 62 выдает сигнал за запуск измерительного блока 23. Через интервал времени, необходимый для измерения, блок 23 выдает на информационные входы регистра 50 цифровой код измеренного параметра, а на его управляющий вход - сигнал конца измерения. По этому сигналу информация записывается в регистр 50 и с некоторой задержкой, необходимой для надежного установления информации на выходе регистра, разрешается сравнение блоками 51 и 52 цифровых кодов регистра 50 и кодов, поступающих с регистров верхней 8 и ниж ней 9 уставки и характеризующих предельные значения стимулирующего 45 сигнала. По линии задатчика 14, в этом режима поступает разрешающий уровень сигнала. При этом возможны три комбинации: измеренное значение больше верхнего предельного значения, измеренное значение меньше нижнего предельного значения и измеренное значение находится в заданном интервале допустимых значений.

В первом случае блок 51 выдает на управляющий вход реверсивного счетчика 12 сигнал вычитания, а на счетный вход - одиночный импульс с генератора 59. ЦАП блока 16 отраба- тывает новое, уменьшенное на едини30

35

40

50

55

9

цу, значение цифрового кода, затем блок 15 вновь запускает блок 23 на измерение. Отслеживание аналогового сигнала продолжается до момента, когда измеренное значение станет меньше верхнего предельного значения.

Во втором случае процесс отслеживания аналогичен за исключением того, что на управляющий вход реверсивного счетчика с блока 52 сравнения выдается сигнал сложения и ЦАП отрабатывает увеличенное на единицу значение цифрового кода,

Таким образом, осуществляется отслеживание напряжения каждого канала блока 16 и значение стимулирующих сигналов по каждому входу оказывается в заданных пределах допустимых значений.

В этом и третьем случаях блок 15 анализа через элемент ИЛИ 21 осуществляет запрос на прерывание, что свидетельствует о готовности станци к приему следующей тестовой комбинации в соответствии с программой проверки на данное контролируемое устройство.

В первом режиме триггер 57 неисправности блокируется сигналом с регистра команд.

Во втором режиме работы системы снимается блокировка с триггера 57 неисправности и блокируется генератор 59 единочного импульса.

В этом режиме информация из блока 32 по первому адресу переписывается в регистр 70 блока 20 и обеспечивает подключение через коммутационную матрицу 72 к измерительному блоку 23 первого соответствующего выходного контакта контролируемого устройства. С некоторой задержкой блок 15 Формирует команду блоку 13 на проверку, по которой начинают поступать с рабочей частотой импульсы на запуск счетчика k$ тактов. Импул сы переноса счетчика 45 запускают счетчик 46 циклов. Меняющаяся с рабочей частотой информация с выхода счетчика 45 поступает на адресные входы блока 7 тестовых комбинаций. Выходы блока 7 в каждый материал вр мени (период рабочей частоты) через триггеры 64 и ключи 68, 69 обеспечивают подключение каждого контакта контролируемого устройства к соответствующим уровням стимулирующих

10

15

00538Ю

сигналов, г.е. перебор входов объекта контроля на рабочей частоте. При этом проверяемый выход подключается к устройствам контроля на весь

5 цикл перебора входных воздействий.

Контроль выходных параметров осуществляется каналом контроля активного состояния контакта, состоящим из блоков 51 и 52 сравнения, и каналом контроля пассивного состояния контакта, состоящим из блоков 40 и 41 сравнения.

В каждый временной интервал (такт контроля периоду рабочей частоты) разрешается один из каналов контроля. Это определяется программой на дан- нь й выходной контакт, записанной в блок 33 и поступающей на блоки сравнения через коммутатор 37. Коммутатор 37 управляется счетчиком 36 номера программы, запуск которого осуществляется тактом контроля, формируемым элементом И 49 по совпадению

25 состояний счетчиков 45 и 46 тактов и циклов и соответствующих дешифраторов 47 и 48.

При работе системы в режиме контроля параметров на счетчик 36 последовательно поступают такты контроля, счетчик переключается и под его уп- правлением коммутатор 37 программ через мультиплексоры 38 обеспечивает последовательную бит за битом выдачу информации из первой ячейки бло35 «а 33 программ из зоны, соответствующей контролируемому контакту. После заполнения четырехразрядного счетчика 36, обеспечивающих выдачу всех 16 бит первой ячейки, осуществляет40

ся выбор следующей ячейки зоны блока

5

33 программ и коммутатор 37 коммутирует на свой выхор информацию следующей ячейки. Процесс продолжается до завершения поступления запрограммированных тактов контроля. Затем из блока 32 выбирается следующий контакт и процесс повторяется.

Таким образом, контролируемый

контакт подключает к системам конч 0 с

роля на один полный цикл работы контролируемого устройства и проверяется один такт как активный - отклик на входные стимулирующие воздействия и остальные такты как пассивный

отсутствие отклика на другую комбинацию входных воздействий.

Если параметры выходного сигнала на контролируемом контакте в а ктивном и пассивном состояних находятся в зоне допуска, определяемой информацией в регистрах 8-11 во всем временном интервале, то счетчики 5 и 6, управляемые по запускающему входу счетчика тактов импульсами с выхода программируемого делителя kk рабочей частоты, работают до своего (полного заполнения, при котором воз- (никает импульс переноса счетчика 6 Ьиклов. Этим импульсом обеспечивается запуск счетчика 3, изменение адреса рлока 32 и, следовательно, номера выходного контакта контролируемого устройства .

Процесс контроля второго выхода повторяется точно так же, как и для первого выходного контакта, за исключением того, что данный контролируе- (( сигнал подключается к каналам онтроля в соответствии со своей про- граммой проверки, выбираемой из блока 1$3 по адресу, определяемому номером Контролируемого контакта.

При успешном контроле параметров выходных сигналов на всех выходных контактах, записанных в блоке 32, блок 15 анализа через элемент ИЛИ 21 Осуществляет запрос на прерывание.

В следующем интервале обмена информацией между УВМ и станцией, записывающей прерывание, считается состояние регистра 17 готовности и УВМ, Определив посты, готовые к работе в Данной измерительной станции, последовательно из регистра 31 через вентили 4 выдает сигнал включения в регистр 6, который через коммутатор 19 обеспечивает подключение коммута- fopa 20 к готовому к работе посту, тем самым обеспечивается последовательное подключение постов внутри станции.

Данную систему во втором режиме р боты наиболее целесообразно принять для допускового контроля параметров устройств с регулярной структурой, например адресных ключей, дешифраторов, усилителей, формирователей. Чем больше в проверяемом устройстве одинаковых структур, тем выше эффективность использования системы.

В третьем режиме работы системы 5 обеспечивается возможность считывать информацию из регистра 50 через блок 52 вентилей в УВМ для анализа.

0

5

0

5

0

5

0

Формула изобретения

с выходом регистра готовности, а выход является выходом готовности измерительной станции, выход регистра рабочих постов соединен с адресным входом коммутатора рабочих постов, первые и вторые информационные входы-выходы, выход прерывания которого соединен соответственно с информационным входом-выходом измерительной станции, выходом коммутатора выводов, первым входом первого элемента ИЛИ, второй, третий входы и выход которого соединены соответствен- tно с выходами прерывания коммутатора выводов, блока анализа, выходом прерывания измерительной станции, выход коммутатора выводов соединен с информационным входом измерительного блока, информационный вход регистра готовности соединен с входом готовности, информационный вход блока ключей - с входом разрешения, а управляющий вход блока ключей и вход блокировки дешифратора адреса - с командным входом данной измерительной станции, отличаю-щая- с я тем, что, с целью повышения достоверности результатов контроля за счет проверки параметров сигналов объекта контроля на рабочей частоте, каждая измерительная станция содержит вторую группу регистров верхней и нижней уставок, задатчик программы проверки, блок запуска программы, блок памяти тестовых комбинаций и блок сравнения, первый, второй, третий информационные входы, выход, синхровход и вход разрешения которого соединены соответственно с выходами регистров верхней и нижней уставок второй группы, информационным выходом блока анализа, входом признака нахождения параметра в зоне допуска блока анализа, информационным выходом задатчика программы проверки, выходом признака конца такта блока анализа, первый выход разрешения которого соединен с входом разрешения блока запуска программы, адресный выход, выход признака такта контроля и тактовый выход которого соединены соответственно с первым адресным входом блока памяти тестовых комбинаций, первым счетным входом, вторым счетным входом задатчика программы проверки, соединенного с тактовым входом блока анализа, информационные и ад0

5

0

0

5

0

5

0

5

ресные входы блока задания програм- мы проверки соединены с одноименными входами блока памяти тестовых комбинаций, блока запуска программы, коммутатора выводов и подклю- чены соответственно к выходам блока ключей и дешифратора адреса.

Фие.1

ЗОНА /У ИйнПИГа.

2Уч0кгл#/ 4

.

fl-U HOHTaJSra.

, Do

От ОЗУ

От счет-) чика

От сче/л-t чика.

От ОЗУ

От счет чика |

/Ј

TT I I I I I I I

m

cfa-Z. 3

Фиг4

OmlS Omtt

фиг. 6

1700538 Qm23 Om23 K2J ОтМ к23 к13

От8 кП От 9 к 18 От4 От5

фиг.7

1

-Выход коммута/пора к измерителю 23

Фце.8

8Ј$OOZt

w

UK

6

П

асу

ttye

. ЛУС K

SO

raxr

Фиг. Ю

5

9TV

3&

г/г-/

Лп

П

6

Utfn-H

Uyf

Uyn

ft

Конец tt&iep.

Авторы

Даты

1991-12-23—Публикация

1989-10-11—Подача