(54) УСТРОЙСТВО ДЛЯ КОНТРОЛЯ ИНТЕГРАЛЬНЫХ СХЕМ

| название | год | авторы | номер документа |

|---|---|---|---|

| Тестер для контроля цифровых блоков | 1986 |

|

SU1555704A1 |

| АВТОМАТИЗИРОВАННАЯ СИСТЕМА КОНТРОЛЯ ПАРАМЕТРОВ ЭЛЕКТРОННЫХ СХЕМ | 1991 |

|

RU2106677C1 |

| Устройство для автоматического контроля больших интегральных схем | 1986 |

|

SU1529220A1 |

| Устройство для контроля цифровых интегральных схем | 1978 |

|

SU943747A1 |

| Устройство для контроля цифровых объектов | 1983 |

|

SU1160373A1 |

| Автоматизированная система контроля параметров электронных схем | 1981 |

|

SU1010602A1 |

| Система для контроля электрических параметров цифровых узлов | 1979 |

|

SU873247A2 |

| УСТРОЙСТВО ДЛЯ КОНТРОЛЯ И ВОССТАНОВЛЕНИЯ ТЕХНИЧЕСКИХ СРЕДСТВ МЕДИЦИНСКОГО НАЗНАЧЕНИЯ | 1992 |

|

RU2072788C1 |

| Устройство контроля параметров | 1990 |

|

SU1800447A1 |

| УСТРОЙСТВО ДЛЯ КОНТРОЛЯ УПРАВЛЯЮЩЕЙ ВЫЧИСЛИТЕЛЬНОЙ МАШИНЫ | 1995 |

|

RU2094842C1 |

Изобретение относится к автоматике и вычислительной технике и может быть использовано для контроля электрических параметров интегралЬных схем.

Известны устройства для контроля электронных устройств,сопрягаемые с ЦВМ и содержащие тактовый генератор, блок сравнения, счетчик, сдвиговый регистр и распределитель импульсов 1.

Недостаток этих устройств состоит в низкой производительности.

Наиболее близким к предлагаемому является устройство для комплексного контроля, содержащее генератор тестов,,j генератор слов, блок управления, подключенный -двухсторонними связями через блок сопряжения к вычислительной машине, а первым выходом к первым входам блока накопления результатов, 20 блойа компараторов, блока формирователей временных параметров сигналов и блока формирователей, вторым выходом - к первым входам блока согласования и распределения выводов интегральной схемы, блока цифро-аналогового преобразования и через блок задающих генераторов к второму входу блока формирования временных параметров.сигнала, выход которогосоединен с вторыми входами блока накопления результатов, блока компараторов vi блока формирователей, третьи входы которых

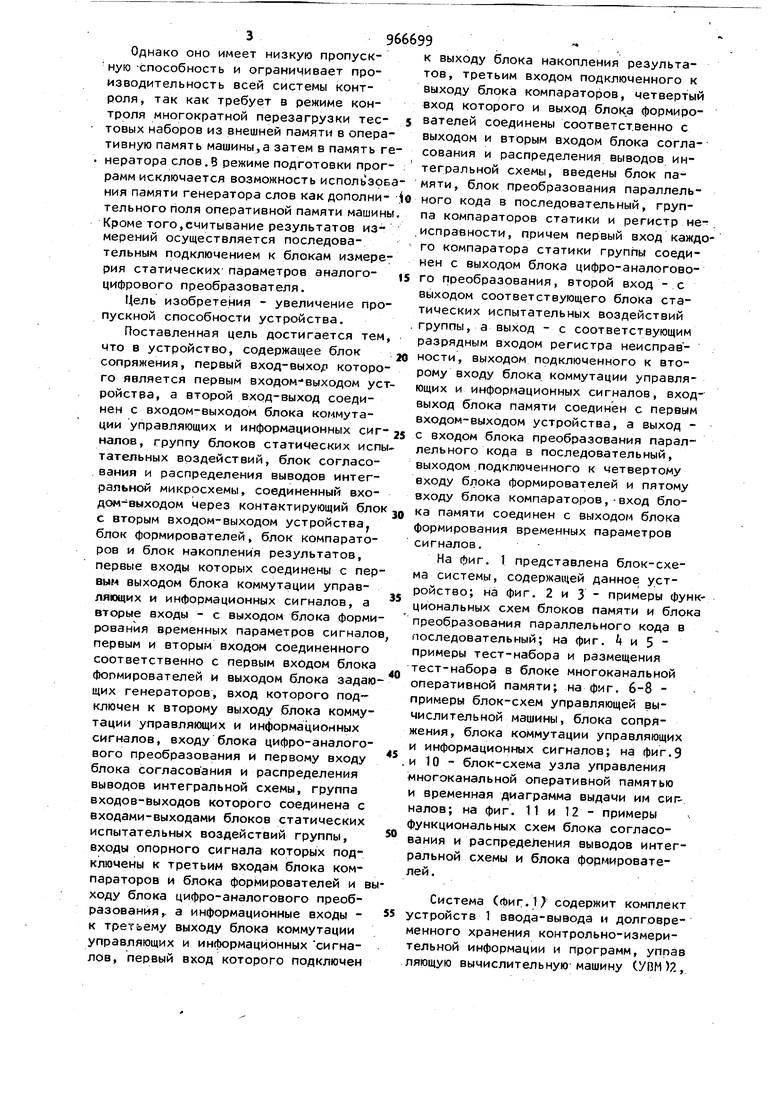

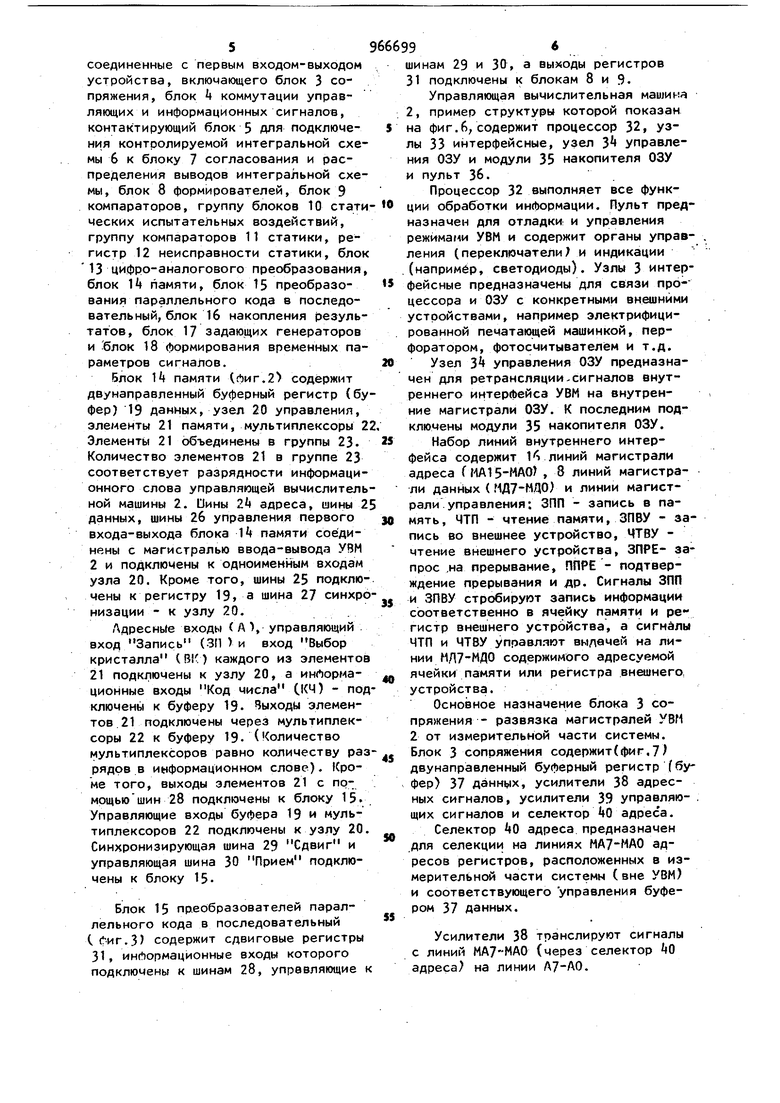

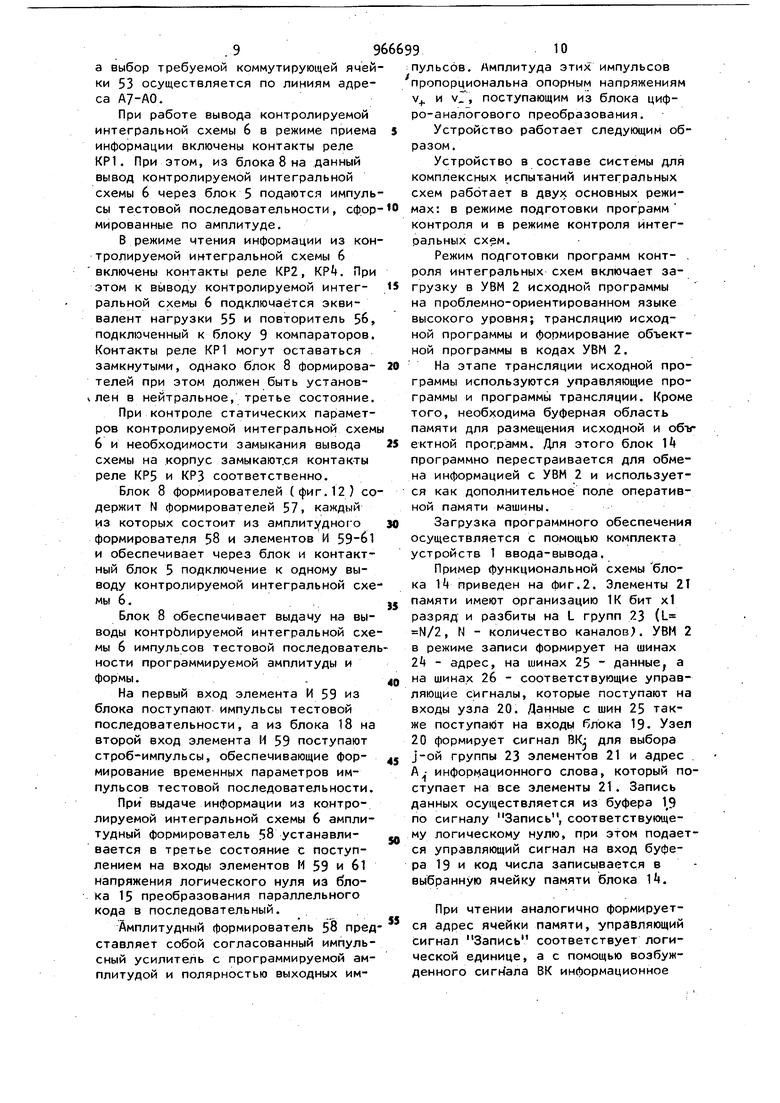

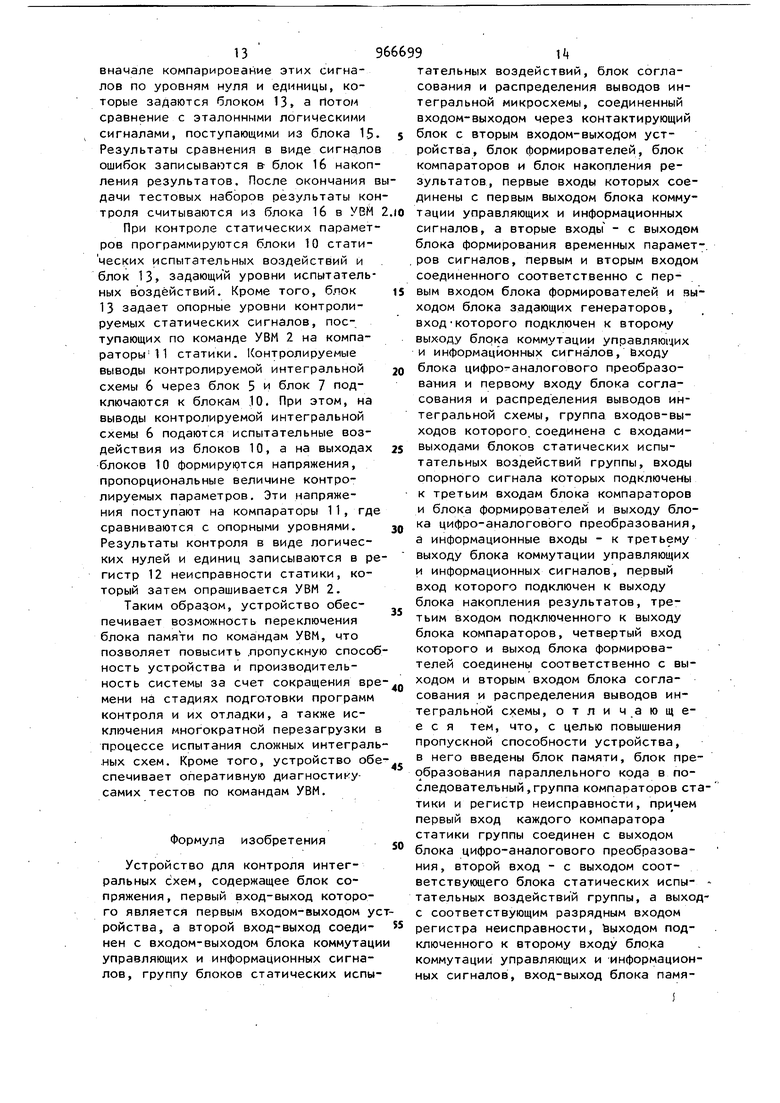

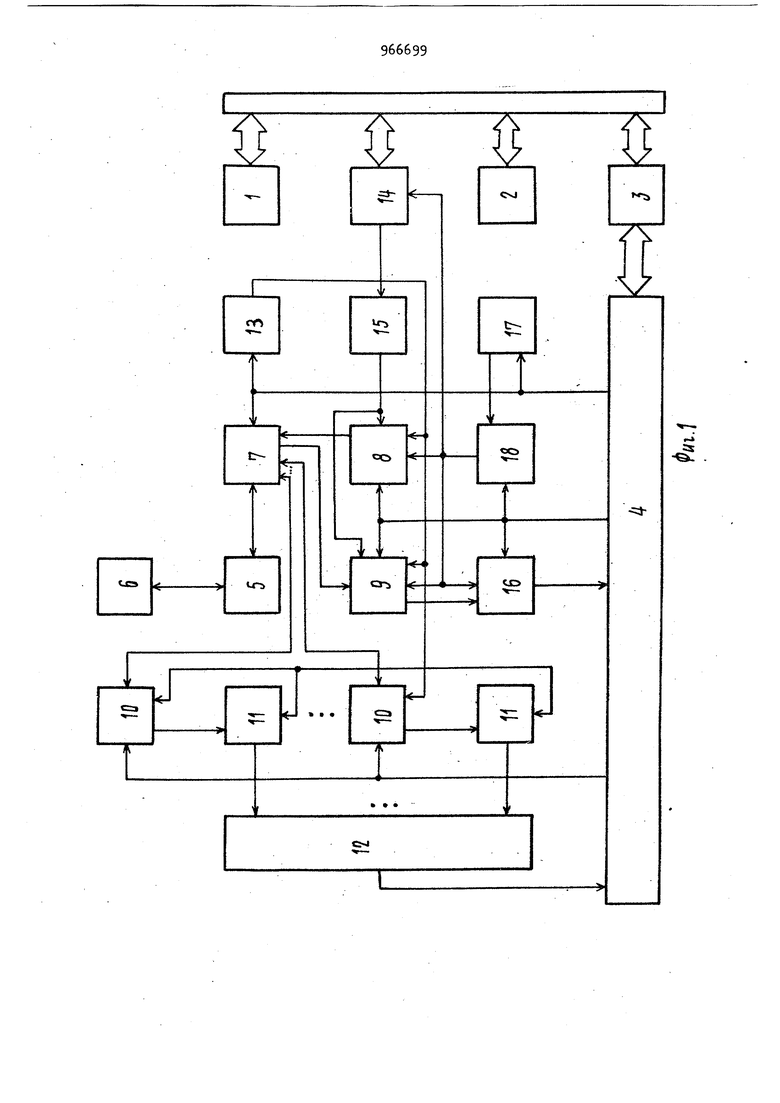

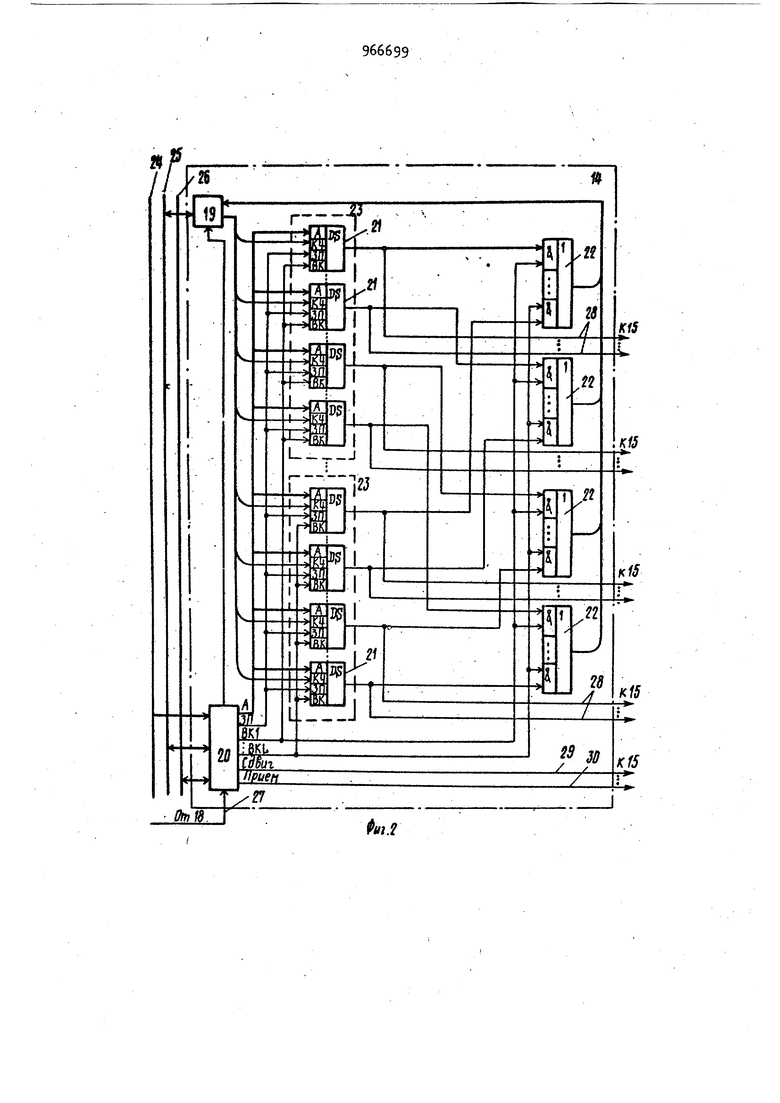

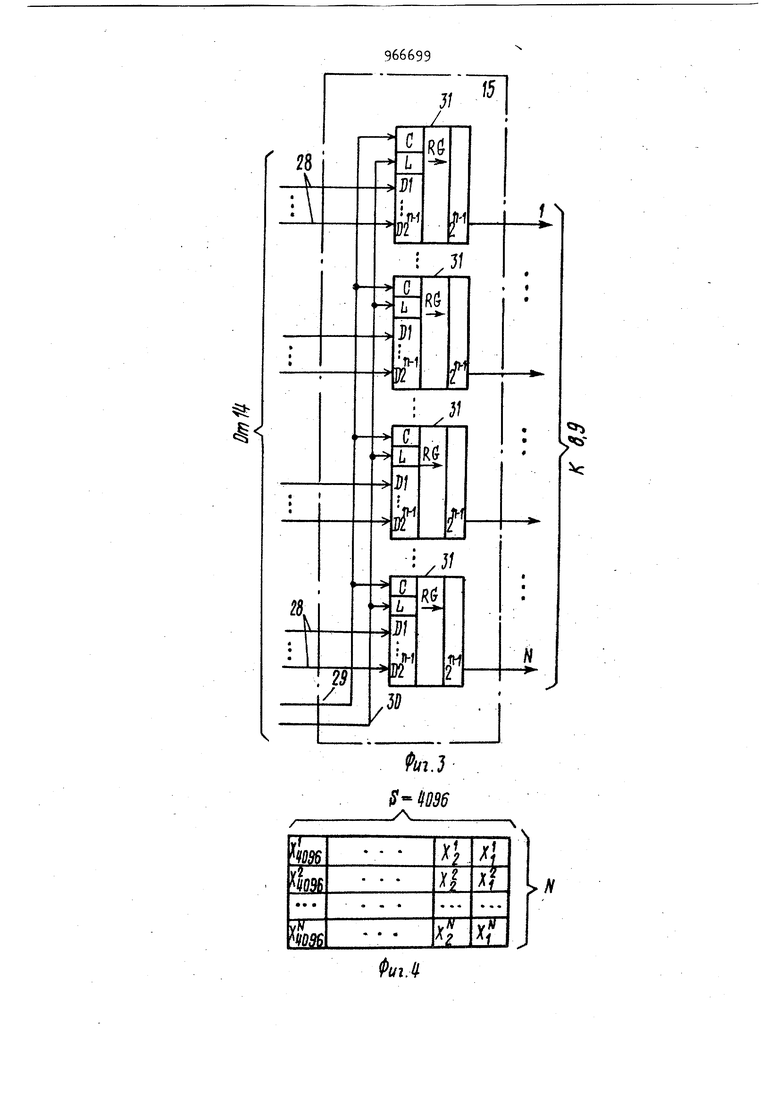

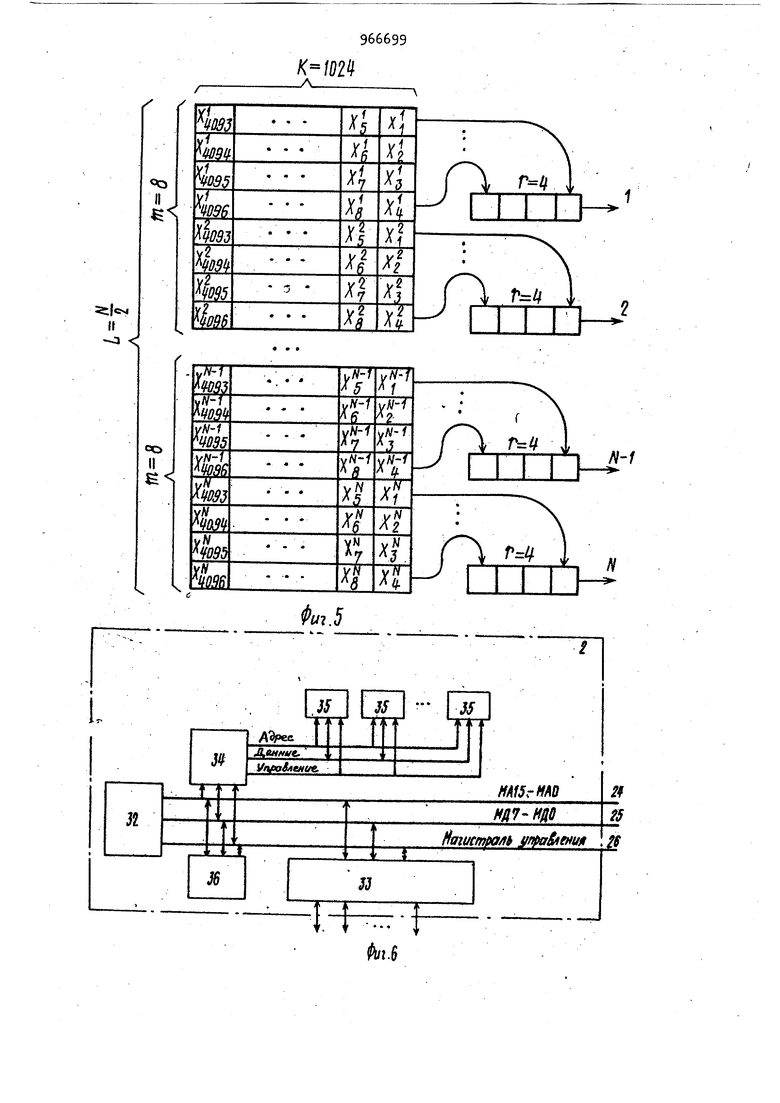

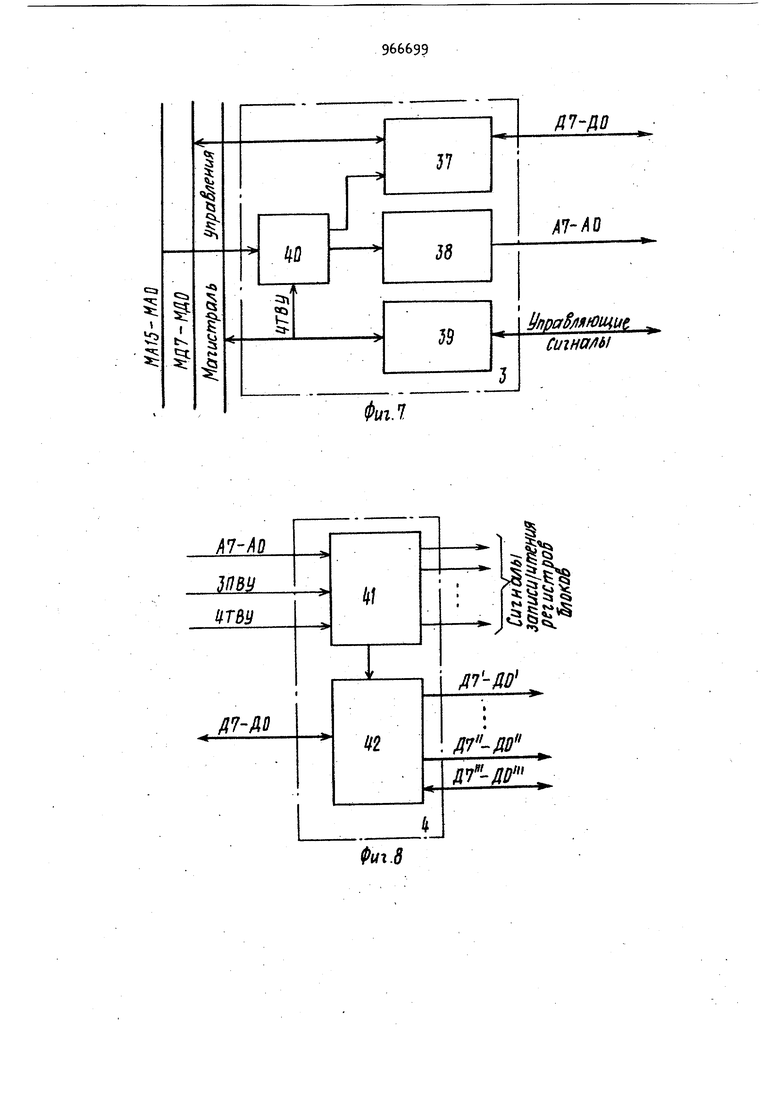

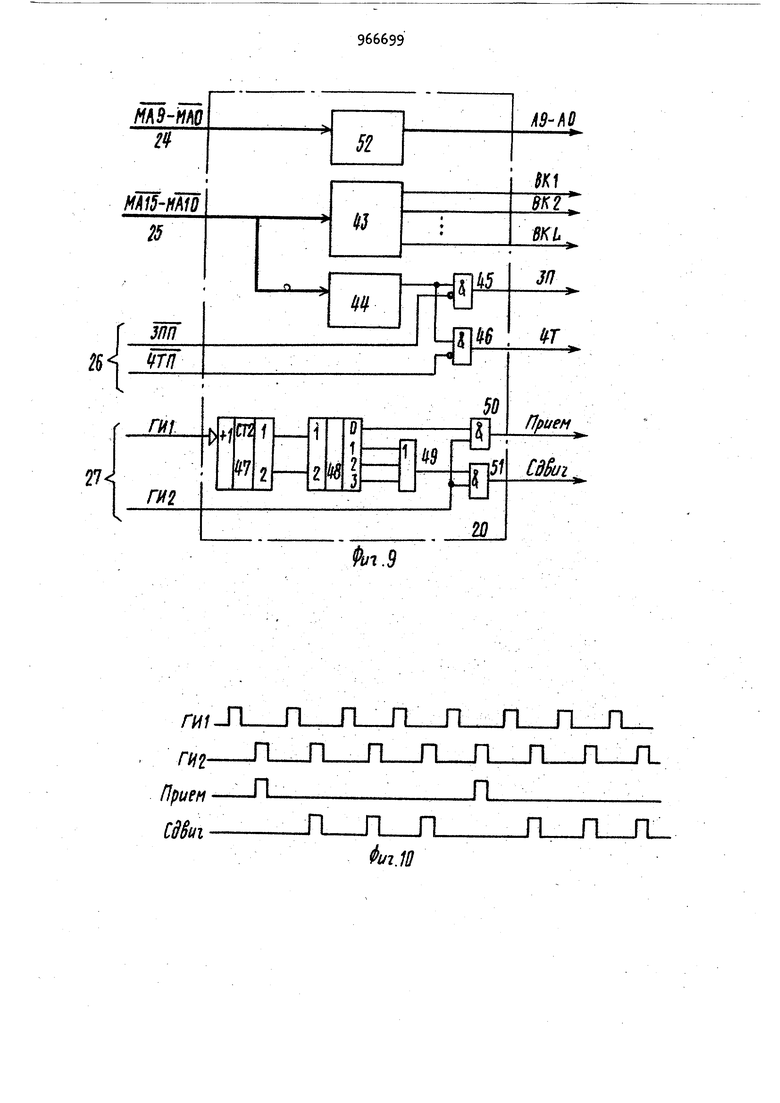

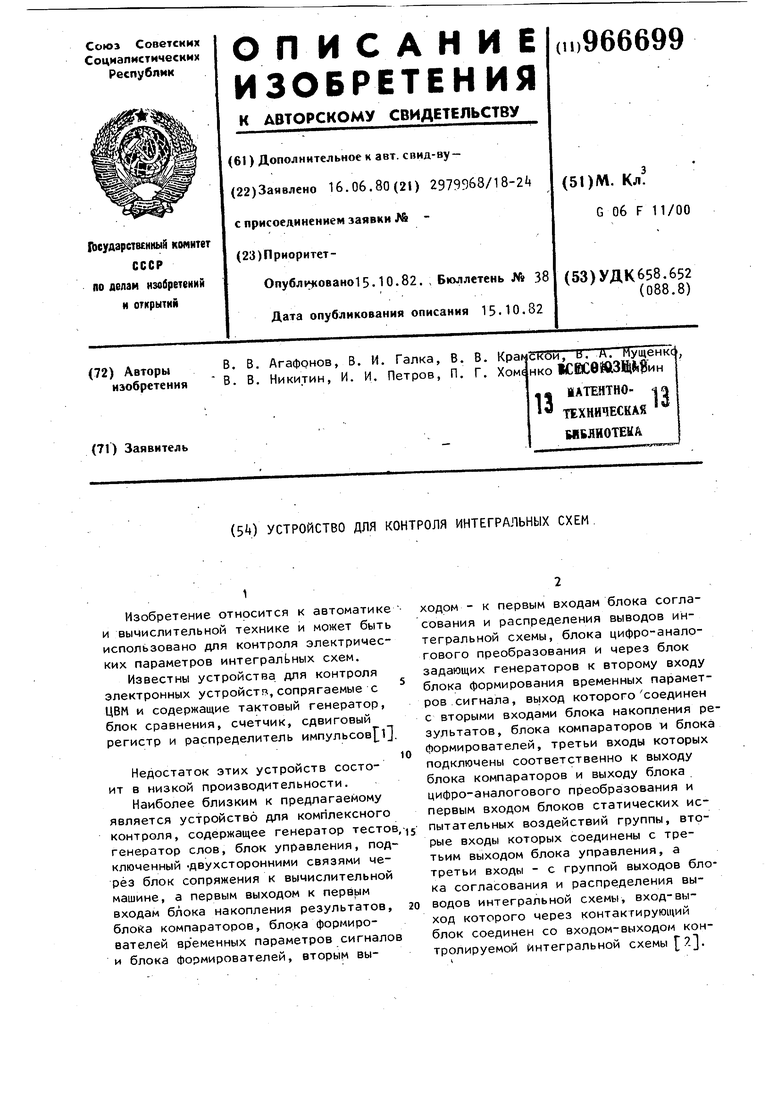

10 подключены соответственно к выходу блока компараторов и выходу блока цифро-аналогового преобразования и первым входом блоков статических испытательных воздействий группы, вторые входы которых соединены с третьим выходом блока управления, а третьи входы - с группой выходов блока согласования и распределения выводов интегральной схемы, вход-выход которого через контактирующий блок соединен со входом-выходом контролируемой интегральной схемы .. Однако оно имеет низкую пропуск-ную -способность и ограничивает производительность всей системы контроля, так как требует в режиме контроля многократной перезагрузки тестовых наборов из внешней памяти в опера тивную память машины,а затем в память г нератора слов,В режиме подготовки прог рамм исключается возможность использов ния памяти генератора слов как дополнительного поля оперативной памяти машин Кроме того,считывание результатов измерений осуществляется последовательным подключением к блокам измере рия статических параметров аналогоцифрового преобразователя. Цель изобретения - увеличение про пускной способности устройства. Поставленная цель достигается тем что в устройство, содержащее блок сопряжения, первый вход-выхор которо го является первым входом выходом ус ройства, а второй вход-выход соединен с входом-выходом блока коммутации управляющих и информационных сиг налов, группу блоков статических исп тательных воздействий, блок согласования и распределения выводов интегральной микросхемы, соединенный входом-выходом через контактирующий бло с вторым входом-выходом устройства блок формирователей, блок компараторов и блок накопления результатов, первые входы которых соединены с пер вым выходом блока коммутации управляющих и информационных сигналов, а вторые входы - с выходом блока форми рования временных параметров сигнало первым и вторым входом соединенного соответственно с первым входом блока формирователей и выходом блока задаю щих генераторов, вход которого подключен к второму выходу блока коммутации управляющих и информационных сигналов, входу блока цифро-аналогового преобразования и первому входу блока согласования и распределения выводов интегральной схемы, группа входов-быходов которого соединена с входами-выходами блоков статических испытательных воздействий группы, входы опорного сигнала которых подключены к третьим входам блока компараторов и блока формирователей и в ходу блока цифро-аналогового преобразования,, а информационные входы к третьему выходу блока коммутации управляющих и информационных сигналов, первый вход которого подключен К выходу блока накопления результатов, третьим входом подключенного к выходу блока компараторов, четвертый вход которого и выход блока формирователей соединены соответственно с выходом и вторым входом блока согласования и распределения выводов интегральной схемы, введены блок памяти, блок преобразования параллельного кода в последовательный, группа компараторов статики и регистр неисправности, причем первый вход каждого компаратора статики группы соединен с выходом блока цифро-аналогового преобразования, второй вход - с вь1ходом соответствующего блока статических испытательных воздействий группы, а выход - с соответствующим разрядным входом регистра неисправности, выходом подключенного к второму входу блока/коммутации управляющих и информационных сигналов, входвыход блока памяти соединен с первым входом-выходом устройства, а выход с входом блока преобразования параллельного кода в последовательный, выходом подключенного к четвертому ВХОДУ блока формирователей и пятому входу блока компараторов,-вход блока памяти соединен с выходом блока формирования временных параметров сигналов. На фиг. 1 представлена блок-схема системы, содержащей данное устройство; на фиг, 2 и 3 - примеры функциональных схем блоков памяти и блока преобразования параллельного кода в последовательный; на фиг. 4 и 5 примеры тест-набора и размещения тест-набора в блоке многоканальной оперативной памяти; на фиг. 6-8 примеры блок-схем управляющей вычислительной машины, блока сопряжения, блока коммутации управляющих и информационных сигналов; на фиг.9 и 10 - блок-схема узла управления многоканальной оперативной памятью и временная диаграмма выдачи им сирналов; на фиг, 11 и 12 - примеры функциональных схем блока согласования и распределения выводов интегральной схемы и блока формирователей. Система ((Ъиг.1 содержит комплект устройств 1 ввода-вывода и долговременного хранения контрольно-измерительной информации и программ, управ ляющую вычислительную машину СУВМ),, соединенные с первым входом-выходом устройства, включающего блок 3 сопряжения, блок коммутации управляющих и информационных сигналов, контактирующий блок 5 для подключения контролируемой интегральной схе мы 6 к блоку 7 согласования и распределения выводов интегральной схемы, блок 8 формирователей, блок 9 компараторов, группу блоков 10 стати ческих испытательных воздействий, группу компараторов 11 статики, регистр 12 неисправности статики, блок 13 цифро-аналогового преобразования блок 1 памяти, блок 15 преобразования параллельного кода в последовательный, блок 16 накопления результатов, блок 17 задающих генераторов и блок 18 формирования временных параметров сигналов. Блок 14 памяти (фиг.2) содержит двунаправленный буферный регистр (бу фер) 19 данных, узел 20 управления, элементы 21 памяти, мультиплексоры 2 Элементы 21 объединены в группы 23. Количество элементов 21 в группе 23 соответствует разрядности информационного слова управляющей вычислитель ной машины 2. Оины 2 адреса, шины 2 данных, шины 26 управления первого входа-выхода блока И памяти соединены с магистралью ввода-вывода УВМ 2 и подключены к одноименным входам узла 20. Кроме того, шины 25 подключены к регистру 19, а шина 27 синхро низации - к узлу 20, Лдреснь е входы ( А , управляющий вход Запись (ЗП и вход Выбор кристалла (ВК) каждого из элементов 21 подключены к узлу 20, а инЛормационные входы Код числа (КЧ) - под ключены к буферу 19. Выходы элементов 21 подключены через мультиплексоры 22 к буферу 19. (Количество мультиплексоров равно количеству раз рядов в информационном слове). Кроме того, выходы элементов 21 с помощью шин 28 подключены к блоку 15. Управляющие входы буфера 19 и мультиплексоров 22 подключены к узлу 20. Синхронизирующая шина 29 Сдвиг и управляющая шина 30 Прием подключены к блоку 15. Блок 15 преобразователей параллельного кода в последовательный (фиг.З) содержит сдвиговые регистры 31, информационные входы которого подключены к шинам 28, управляющие к шинам 29 и 30, а выходы регистров 31 подключены к блокам 8 и 9. Управляющая вычислительная машиыа 2, пример структуры которой показан на фиг.6, содержит процессор 32, узлы 33 интерфейсные, узел 3 управления ОЗУ и модули 35 накопителя ОЗУ и пульт 36. Процессор 32 выполняет все функции обработки информации. Пульт предназначен для отладки: и управления режимами УВМ и содержит органы управления (переключатели 7 и индикации (например, светодиоды). Узлы 3 интерфейсные предназначены для связи процессора и ОЗУ с конкретными внешними устройствами, например электрифицированной печатаю|цей машинкой, перфоратором, фотосчитывателём и т.д. Узел 3 управления ОЗУ предназначен для ретрансляции-сигналов внутреннего интерфейса УВМ на внутренние магистрали ОЗУ. К последним подключены модули 35 накопителя ОЗУ. Набор линий внутреннего интерфейса содержит Т линий магистрали адреса fMA15-MAOJ , 8 линий магистрали данных ( МД7-МДО) и линии магистрали .управления: ЗПП - запись в память, ЧТП - чтение памяти, ЗПВУ - запись во внешнее устройство, ЧТВУ чтение внешнего устройства, ЗПРЕ- запрос ,на прерывание, ППРЕ - подтверждение прерывания и др. Сигналы ЗПП и ЗПВУ стробируот запись информации соответственно в ячейку памяти и регистр внешнего устройства, а сигналы ЧТП и ЧТВУ управляют вылвчей на линии МД7-МДО содержимого адресуемой ячейки памяти или регистра внешнего, устройства. Основное назначение блока 3 сопряжения - развязка магистралей УВМ 2 от измерительной части системы. Блок 3 сопряжения содержит(фиг,7) двунаправленный буферный регистр (буфер) 37 даннмх, усилители 38 адресных сигналов, усилители 39 управляющих сигналов и селектор 0 адреса. Селектор 0 адреса предназначен для селекции на линиях адресов регистров, расположенных в измерительной части системы (вне УВМ) и соответствующего управления буфером 37 данных. Усилители 38 транслируют сигналы с линий (через селектор ЦО адреса) на линии А7-АО. 7966699 Усилител14 39 управляющих сигна- бора лов-принимают с магистрали управления сигналы ЧТВУ, ЗПВУ, ППРЕ и др и выдают их в измерительную часть системы принимают от нее сигнал ЗПРЕ и выЙают его в УВН. Буфер 37 данных передает сигналы с линий МД7-МДО УВМ на линии Д7-ДО измерительной части во всех случаях, кроме Чтения, располо хенного в этой части регистра, f этом случае сигналы передаются с линий Д7-ДО на МД7МДО. блок коммутации управляющих и информационных сигналов предназначен для размножения магистрали данных Д7-Д.О по измерительной части системы и формирования по адресу на линиях А7-АО и управляющим сигналом ЗПВУ и ЧТВУ сигналов записи или чтения конкретных регист-ров. Блок k содержит (фиг.8) дешифратор 41 адреса и коммутатор 42 линий данных. Зыходы дешифратора 1 подключаются в системе непосредственно на стробирующие входы программируемых регистров. Коммутатор +2 линий данных транслирует сигналы с линий на juecT групп однонаправленных линий (Д7-ДО (.Д7 - до). А также в зависимости от выполняемой операции (записи или чте ния) передает данные с линий Д7-ДО на двунаправленные линии Д7 - ДО или наоборот. Однонаправленные лини (Д7 - до ) - ( ДО) подключены ГЛ7 - лп - ( лп nnni ninuoui-i к информационным входам программируемых регистров блоков, а двунаправленные линии подключены к тем блокам устройства, которые имеют двунаправленные информаци онные выводы. Узел 20 управления предназначен для управления элементами 21 памяти и мультиплексорами 22 блока Il памяти. Узел 20 содержит (фиг.9 дешифратор адреса, селектор hk адреса, элементы И и , двоичный сч чик 47, дешифратор , элемент ИЛИ элементы И 50 и 51 и усилители 52. Усилители 52 принимают с линий МА9-НАО 10 - разрядный код адреса. инвертируют его и выдают непосредственно -на адресные входы элементов 21 памяти. Дешифратор kj по старшим шести разрядам кода адреса на линиях МА15 МА 10 формирует один из сигналов вы 8 ВК1-ВК. Линии ВК1.-ВК подключены ко входам Выбора кристалла элементов 21 памяти. Селектор адреса подает на элементы М kS и k6 разрешающий потенциал, если на магистрали адреса находится адрес одной из ячеек блока памяти. Для этого достаточно проанализировать 6 старших разрядов адреса на линиях МА15-МА10. Если элемент И kS открыт, то сигнал ЗПП через этот элемент И подается на. входы записи всех элементов 21 памяти. Если открыт элемент И k6, то сигнал ЧТП подается на вхбд буфера 19 данных для переключения его на прием данных от мультиплексоров 22 и выдачу их на магистраль 25 данных. Счетчик kj, дешифратор 8, элементы ИЛИ 9 и И .SO и 51 предназначены для формирования сигналов Прием и Сдвиг, временная диаграмма Которых показана на фиг.10. Эти сиг- налы формируются от сигналов ГИ1 и ГИ2 ( И - главные импульсы), поступающие от блока 18. По .сигналу Прием происходит запись информации .с элементов 21 памяти в «-разрядные сдвиговые регистры 31, а по сигналам Сдвиг - эта информация сдвигается в регистрах 31. Таким образом, в каждом рабочем такте выдачи тестнабора, определяемом сигналами ГИ2 на выходе каждого сдвигового регистpa 31 появляется один из четырех одновременно считанных бит в канале. Блок 7 согласования и распределения выводов интегральной схемы содержит (Фиг,11) группу одинаковых коммутирующих ячеек 53, каждая из которых состоит из регистра 5 управления реле, эквивалента нагрузки 55, повторителя 56, ряда коммутирующих реле КР...КР5. Количество коммутирующих ячеек 53 соответствует количеству выводов контролируемой интегральной схемы 6. Каждая коммутирующая ячейка 53 подключает к одному выводу контролируемой интегральной схемы выход ампплитудного формирователя блока о через контакты реле КР1, повторитель 5б - через контакты реле КР2, корпус - через контакты реле КРЗ, эквивалент нагрузки 55 через контакты реле КР4 и блок 10 - через контакты реле КР5. Команды управления реле записываются в регистры с линии Д7 - ДО,

а выбор требуемой коммутирующей ячейки 53 осуществляется по линиям адреса А7-АО.

При работе вывода контролируемой интегральной схемы 6 в режиме приема информации включены контакты реле КР1, При этом, из блока 8 на данный вывод контролируемой интегральной схемы 6 через блок 5 подаются импульсы тестовой последовательности, сфор мированные по амплитуде, В режиме чтения информации из кон тролируемой интегральной схемы 6 включены контакты реле КР2, КР, При этом к вь1воду контролируемой интегральной схемы 6 подключается эквивалент нагрузки 55 и повторитель 5б, подключенный к блоку 9 компараторов. Контакты реле КР1 могут оставаться замкнутыми, однако блок 8 формирователей при этом должен быть установчлен в нейтральное, третье состояние. При контроле статических параметров контролируемой интегральной схем 6 и необходимости замыкания вывода схемы на .корпус замыкаются контак-ты реле КР5 и КРЗ соответственно. Блок 8 формирователей ( фиг,12 ) со держит N формирователей 57, каждый из которых состоит из амплитудного формировате/1Я 58 и элементов И и обеспечивает через блок и контактный блок 5 подключение к одному выводу контролируемой интегральной схе мы 6.. Блок 8 обеспечивает выдачу на выводы контрЬлируемой интегральной схе мы 6 импульсов тестовой последовател ности программируемой амплитуды и формы.. На первый вход элемента И 59 из блока поступают импульсы тестовой последовательности, а из блока 18 на второй вход элемента И 59 поступают строб-импульсы, обеспечивающие формирование временных параметров импульсов тестовой последовательности. При выдаче информации из контролируемой интегральной схемы 6 амплитудный формирователь 58 устанавливается в третье состояние с поступлением на входы элементов М 59 и 61 напряжения логического нуля из блока 15 преобразования параллельного кода в последовательный. Амплитудный формирователь 58 пред ставляет собой согласованный импульсный усилитель с программируемой амплитудой и полярностью выходных импульсов. Амплитуда этих импульсов пропорциональна опорным напряжениям v и уГ, поступающим из блока цифро-аналогового преобразования.

Устройство работает следующим образом.

Устройство в составе системы для комплексных испытаний интегральных схем работает в двух основных режимах: в режиме подготовки программ контроля и а режиме контроля ральных схем. Режим подготовки программ конт- , роля интегральных схем включает загрузку в УВМ 2 исходной программы на проблемно-ориентированном языке высокого уровня; трансляцию исходной программы и формирование объектной программы в кодах УВМ 2. На этапе трансляции исходной программы используются управляющие программы и программы трансляции. Кроме того, необходима буферная область памяти для размещения исходной и объектной программ. Для этого блок 1 программно перестраивается для обмена информацией с УВМ 2 и используется как дополнительное поле оперативной памяти машины. Загрузка программного обеспечения осуществляется с помощью комплекта устройств 1 ввода-вывода. Пример функциональной схемы блока приведен на фиг.2, Элементы 2Т памяти имеют организацию 1К бит х1 разряд и разбиты на L групп 23 (L N/2, N - количество каналов, УВМ 2 в режиме записи формирует на шинах 2 - адрес, на шинах 25 - данные, а на шинах 26 - соответствующие управляющие сигналы, которые поступают на входы узла 20, Данные с шин 25 также поступает на входы блока 19- Узел 20 формирует сигнал ВК: для выбора j-ой группы 23 элементов 21 и адрес информационного слова, который поступает на все элементы 21. Запись данных осуществляется из буфера по сигналу Запись, соответствующему логическому нулю, при этом подается управляющий сигнал на вход буфера 19 и код числа записывается в выбранную ячейку памяти блока 1. При чтении аналогично формируется адрес ячейки памяти, управляющий сигнал Запись соответствует логической единице, а с помощью возбужденного ВК информационное слово с выходов элементов 21 через соответствующие входы мультиплексоров 22 поступает на вход блока 19. Управляющий сигнал с узла 20 разрешает прохождение информации с блока 19 на шину 25, которая подключена к УВМ 2. Обмен информацией между УВМ 2 и блоками Н осуществляется на час тоте работы УВМ 2. . После завершения трансляции в памяти УВМ 2 формируется объектная программа, готовая к исполнению, а в блоке Ц памяти - тестовые наборы для контроля функционирования интегральной схемы. Если этап подготовки и трансляции программы контроля был выполнен ранее, то объектная программа и тестовые наборы загружаются с устройств 1 ввода-вывода или устройства долговременного хранения программ и контрольно-измерительной информации в память УВМ 2 и в блок k памяти соответственно. Тестовые наборы (фиг.4) должны записываться в блок 14 памяти так,. как показано на фиг..5. Приведенное распределение памяти блока соответствует т.8, , (S длина тест-наборов). Разрядность г сдвиговых регистров блока 15 равна четырем. Работа устройства в режиме контро ля интегральных схем осуществляется следующим образом. Программа контроля включает тесты контроля функционирования и тесты контроля статических параметров. Кон троль функционирования производится в реальном масштабе времени (на рабо чей частоте иопытуемой интегральной схемы , с возмомсностью совмещения во времени функционального контроля с динамическим, а также позволяет контролировать уровни логического нуля и логической единицы в процессе контроля функционального контроля с динамическим, а также позволяет контроливать уровни логического нуля и логической единицы в процессе контроля функционирования. В тестах контроля функционирования программируют ся параметры задающих генераторов бл ка 17, определяющие рабочую частоту контролируемой схемы 6, формирователей временных параметров блока 18, задающих задержку и длительность вхо ных (Сигналов и определяющих моменты 9 91.2 сравнения выходных сигналов с эталонными, цифро-аналоговых преобразователей блока 31, формирователей блока 8 и компараторов блока 9, которые задают уровни входных и уров.ни компарирования выходных сигналов. Кроме того, задается режим выдачи тестовых наборов из блока Ц и структура данных блока 16. Затем программмруется блок 7 согласования и распределения выводов, который подключает через контактирующий блок 5 входы контролируемой схемы 6 к блоку 8, а вь1ходы - к блоку 9. Для контроля функционирования испытуемой микросхемы t УВМ 2 выдает команду через шины 25 блоку 1 на выдачу тестовых наборов. Эта команда поступает в узел 20 и инициирует его работу на тактовой частоте, задаваемой блоком 18. Синхронизирующие сигналы поступают на узел 20 через шину 27, При этом узел 20 выдает параллельно сигналы ВК1,ВК2..., BKL и сигнал Чтение на элементы 21 памяти. Информация, записанная в этих элементах по адресу А, считывается одновременно на шины 28 и записывается в сдвиговые регистры 31 блока:Поскольку разрядность сдвиговых регистров эавна г, то в течение первого такта выполняется запись в сдвиговые-регистры, а в течение остальных г-1 тактов происходит сдвиг информации на один разряд в каждом такте. Во время сдвига информации в регистрах узел 20 В1-гдает сигналы на чтение следующих слов тест-наборов. Благодаря совмещению операций Сдвига и Чтение информации из элементов памяти максимальная частота выдачи тест-наборов определяется величинойТц/V, где Тц - время цикла чтения элементов 21 памяти. С выходов регистров 31 информация в виде словс тест-набора считывается на рабочей частоте контролируемой интегральной схемы 6.задаваемой сигналом на шине 29, и поступает на входы блоков 8 и 9. В блоке 8 формируются сигналы, уровни которых задаются блоком 13, временные параметры - блоком 18, а логические значения - блоком 15. Эти сигналы через блок 7 подаются на входы контролируемой интегральной схемы 6, выходные сигналы с которой поступают в блок 9,. где происходит вначале компарирование этих сигналов по уровням нуля и единицы, которые задаются блоком 13, а Потом сравнение с эталонными логическими сигналами, поступающими из блока 15. Результаты сравнения в виде сигналов ошибок записываются в- блок 16 накопления результатов. После окончания выдачи тестовых наборов результаты контроля считываются из блока 16 в УЕМ 2.1 При контроле статических парамет ров программируются блоки 10 статических испытательных воздействий и блок 13, задающий уровни испытатель ных воздействий. Кроме того, блок 13 задает опорные уровни контролируемых статических сигналов, поступающих по команде УВМ 2 на компараторы 11 статики. Контролируемые выводы контролируемой интегральной схемы 6 через блок 5 и блок 7 подключаются к блокам 10. При этом, на выводы контролируемой интегральной схемы 6 подаются испытательные воздействия из блоков 10, а на выходах блоков 10 формируются напряжения, пропорциональные величине контролируемых параметров. Эти напряжения поступают на компараторы 11, гд сравниваются с опорными уровнями. Результаты контроля в виде логических нулей и единиц записываются в р гистр 12 неисправности статики, который затем опрашивается УВМ 2. Таким образом, устройство обеспечивает возможность переключения блока памяти по командам УВМ, что позволяет повысить .пропускную спосо ность устройства и производительность системы за счет сокращения вр мени на стадиях подготовки программ контроля и их отладки, а также исключения многократной перезагрузки процессе испытания сложных интеграл ных схем. Кроме того, устройство об спечивает оперативную диагностикусамих тестов по командам УВМ. Формула изобретения Устройство для контроля интегральных схем, содержащее блок сопряжения, первый вход-выход которого является первым входом-выходом у ройства, а второй вход-выход соединен с входом-выходом блока коммутац управляющих и информационных сигналов, группу блоков статических испы 966 9и тательных воздействий, блок согласования и распределения выводов интегральной микросхемы, соединенный входом-выходом через контактирующий блок с вторым входом-выходом устройства, блок формирователей, блок компараторов и блок накопления результатов, первые входы которых соединены с первым выходом блока коммутации управляющих и информационных сигналов, а вторые входы - с выходом блока формирования временных парамет-. ров сигналов, первым и вторым входом соединенного соответственно с первым входом блока формирователей и выходом блока задающих генераторов, вход-которого подключен к второму выходу блока коммутации управляющих и информационных сигналов, бходу блока цифро-аналогового преобразова 1ия и первому входу блока согласования и распределения выводов интегральной схемы, группа входов-выходов которого соединена с входамивыходами блоков статических испытательных воздействий группы, входы опорного сигнала которых подключены к третьим входам блока компараторов и блока формирователей и выходу блока цифро-аналогового преобразования, а информационные входы - к третьему выходу блока коммутации управляющих и информационных сигналов, первый вход которого подключен к выходу блока накопления результатов, третьим входом подключенного к выходу блока компараторов, четвертый вход которого и выход блока формирователей соединень соответственно с выходом и вторым входом блока согласования и распределения выводов интегральной схемы, отли чающееся тем, что, с целью повышения пропускной способности устройства, в него введены блок памяти, блок преобразования параллельного кода в последовательный , группа компараторов статики и регистр неисправности, прижмем первый вход каждого компаратора статики группы соединен с выходом блока цифро-аналогового преобразования , второй вход - с выходом соответствующего блока статических испы- тательных воздействии группы, а выходс соответствующим разрядным входом регистра неисправности, выходом подключенного к второму входу блока коммутации управляющих и информационных сигналов, вход-выход блока памяти соединен с первым входом-выходом устройства, а выход - с входом блока преобразования параллельного,кода в последовательный, выходом подключенного к четвертому входу блока формирователей и пятому входу блока компараторов, вход блока памяти соединен с выходом блока формирования временных параметров сигналов.

Источники информации, принятые во внимание при экспертизе.

И. Авторское свидетельство ССС ff 37988, кл. G 01 R 31/28, 1972 (прототип).

ФигЛ

II

;

ablest И

Ь00 II

yv-f

-t

24

HMSrMM

W7- HRS

fS

aiucmt a/t jffiptfStwufi

Jf

.8

Риг. 9

/JpuPM -Jl -

Л

Й/7./

Авторы

Даты

1982-10-15—Публикация

1980-06-16—Подача