Изобретение относится к телемеханике и может быть использовано для передачи сигналов по проводным каналам связи.

Цель изобретения - упрощение устройства.

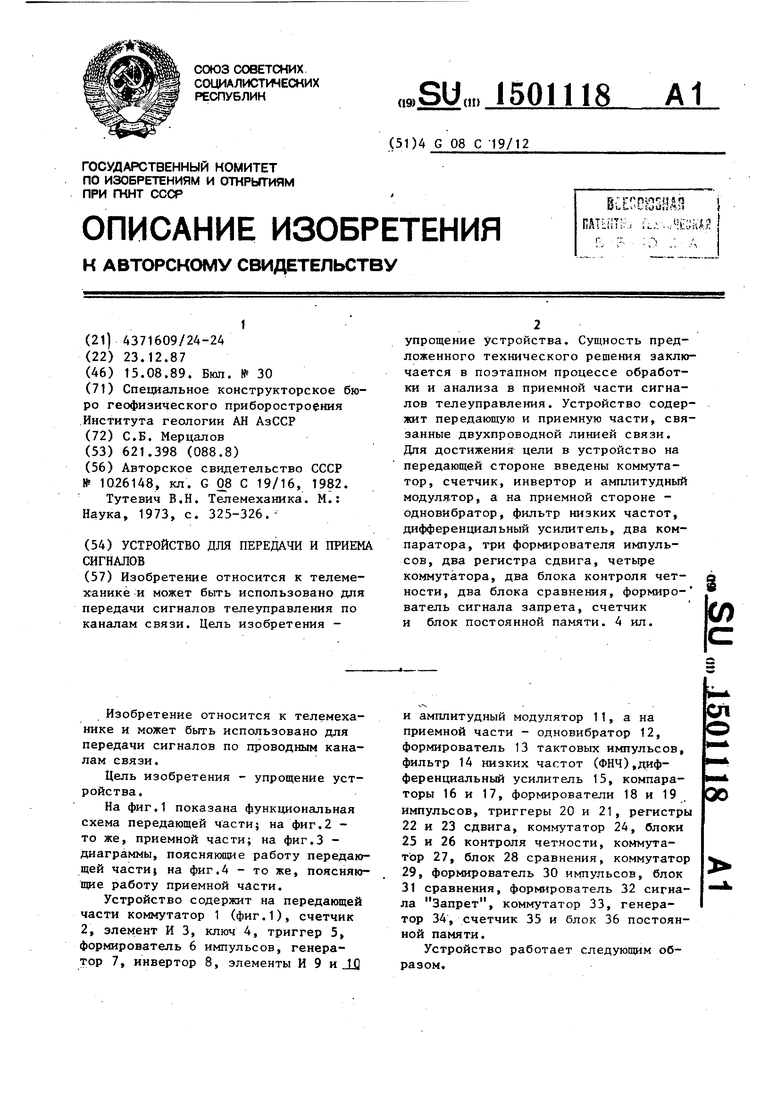

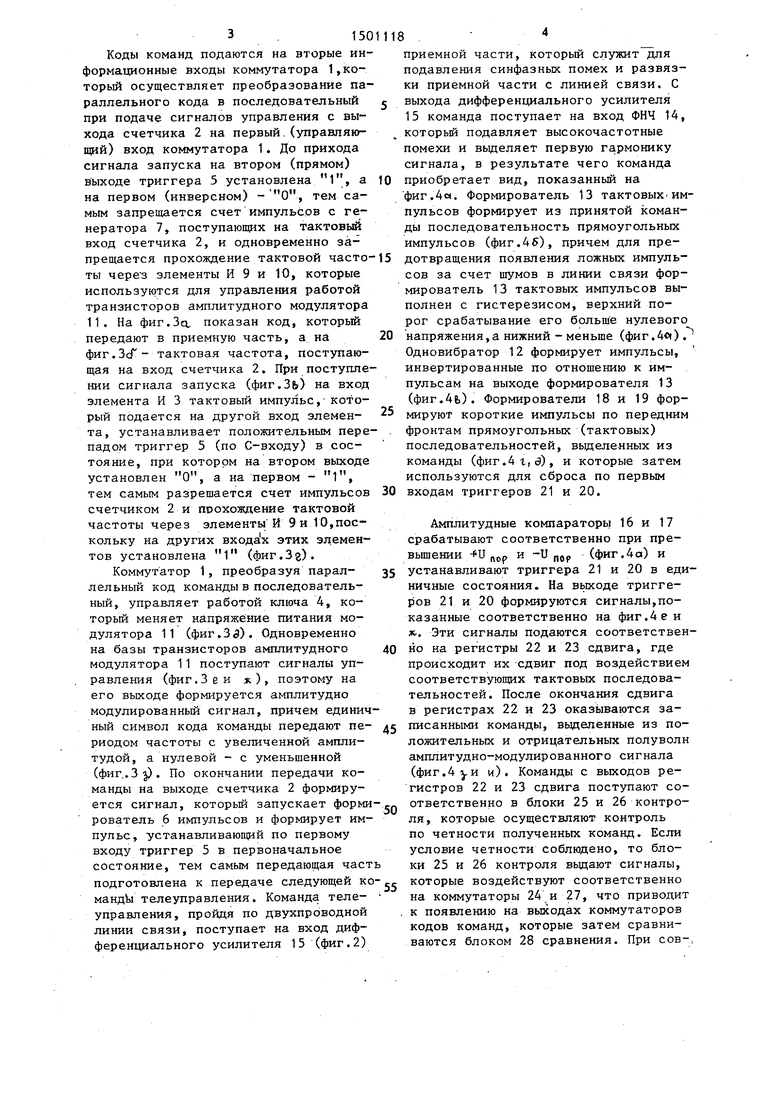

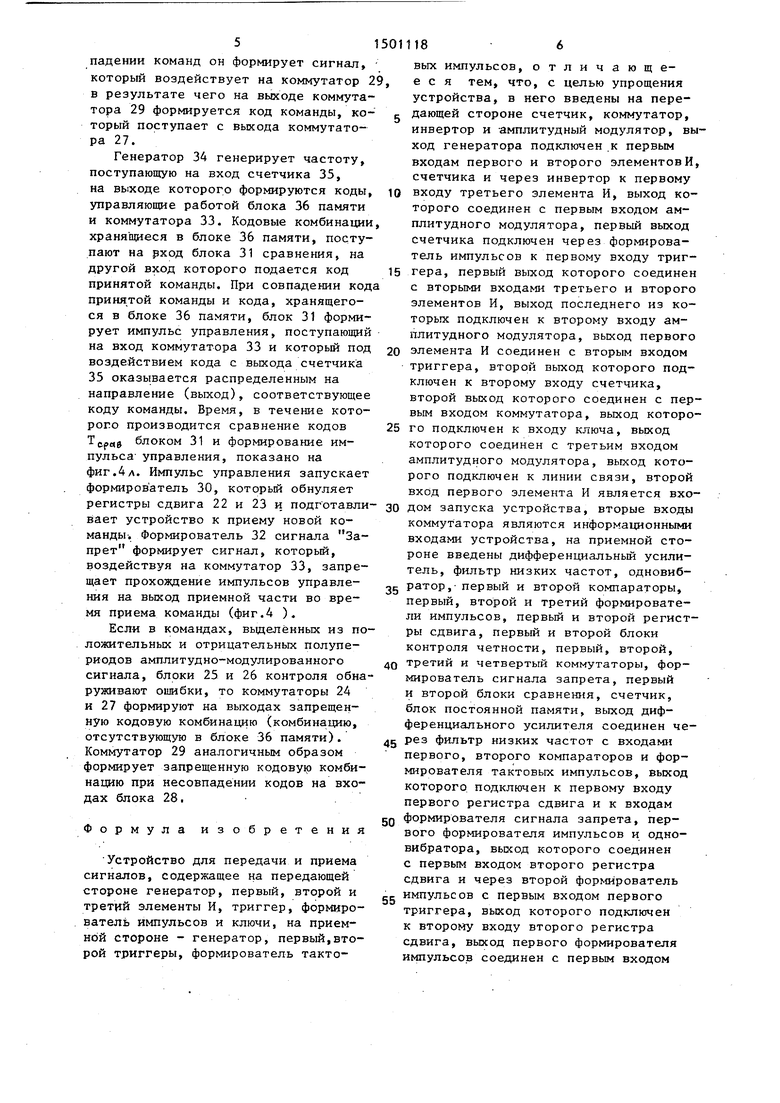

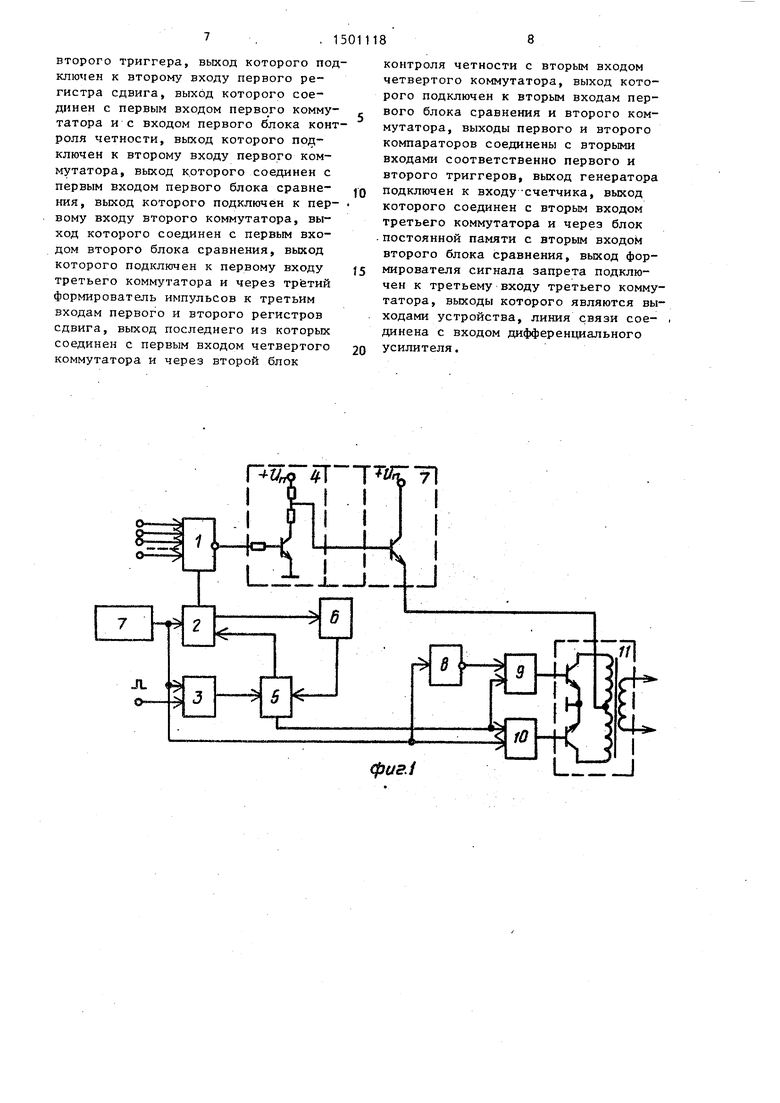

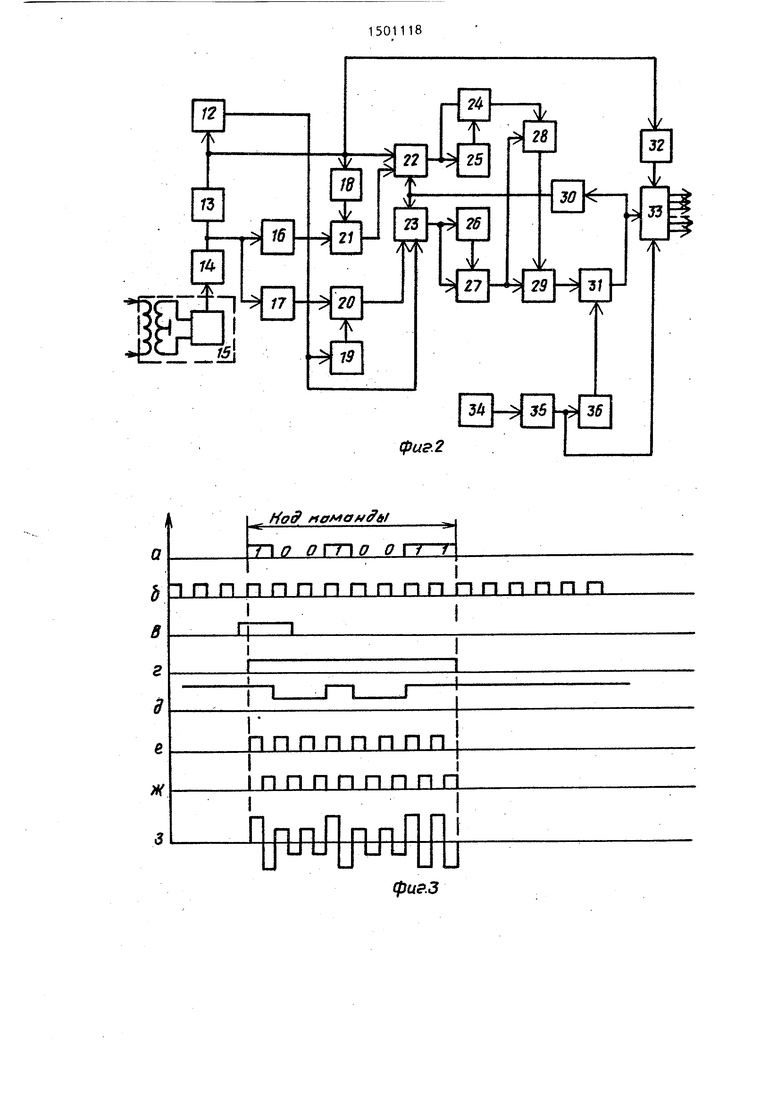

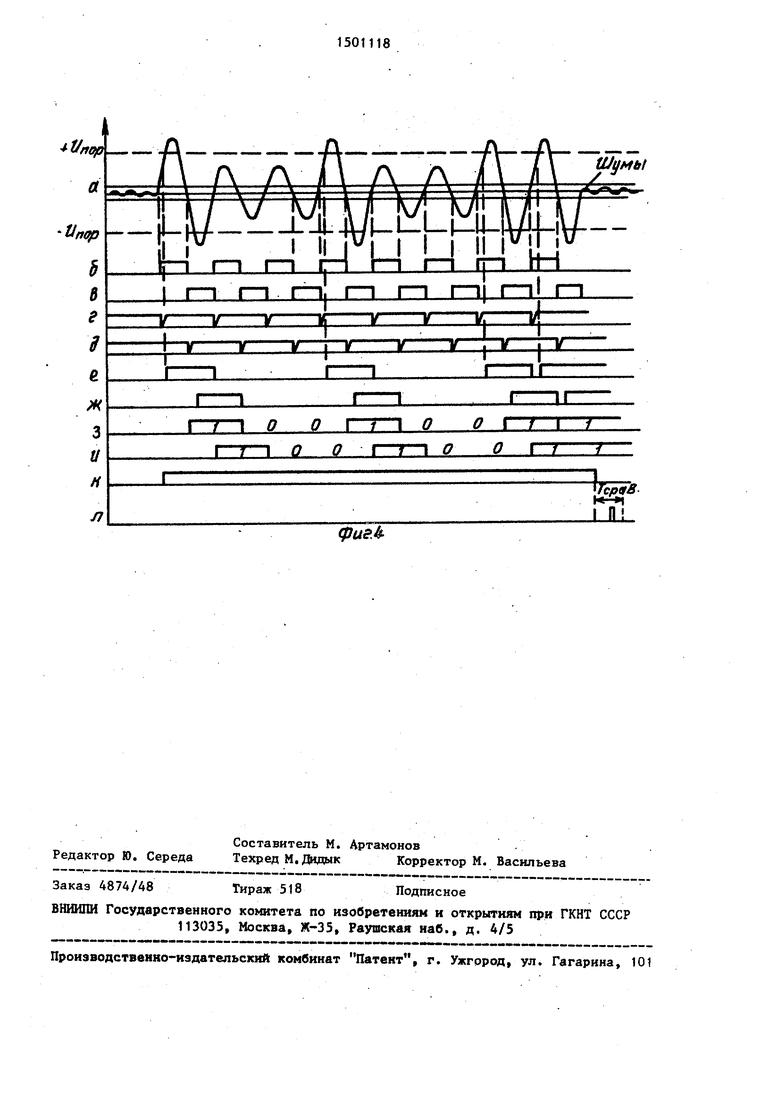

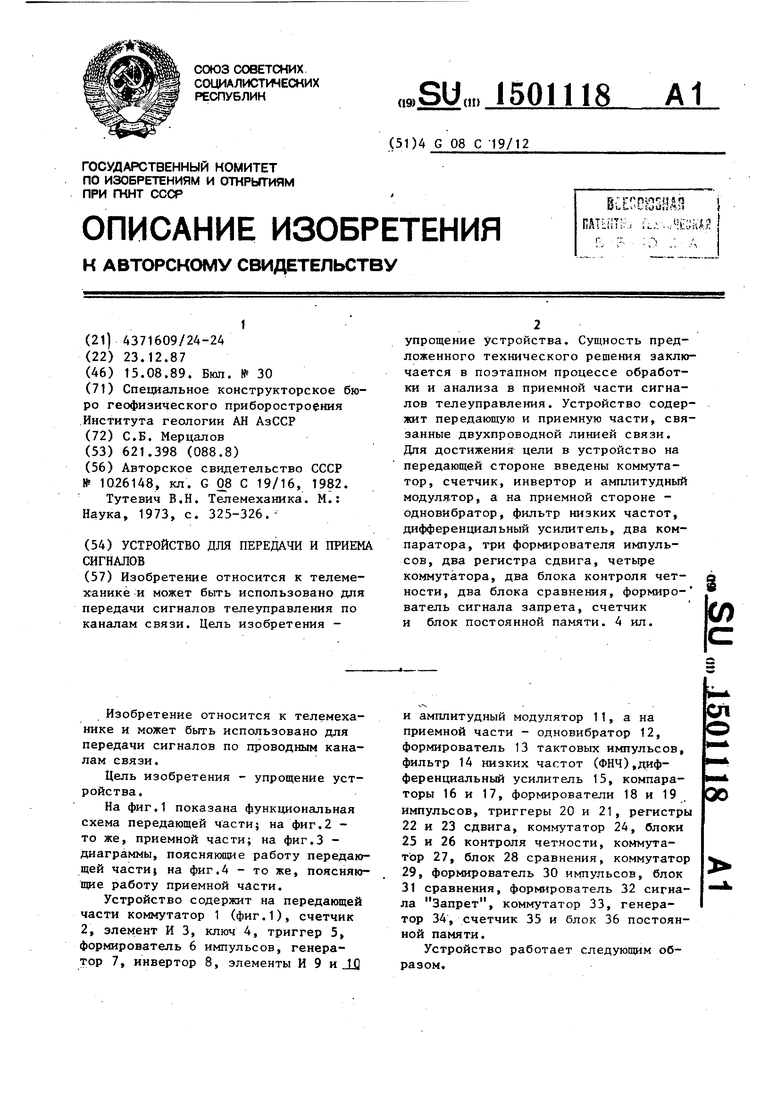

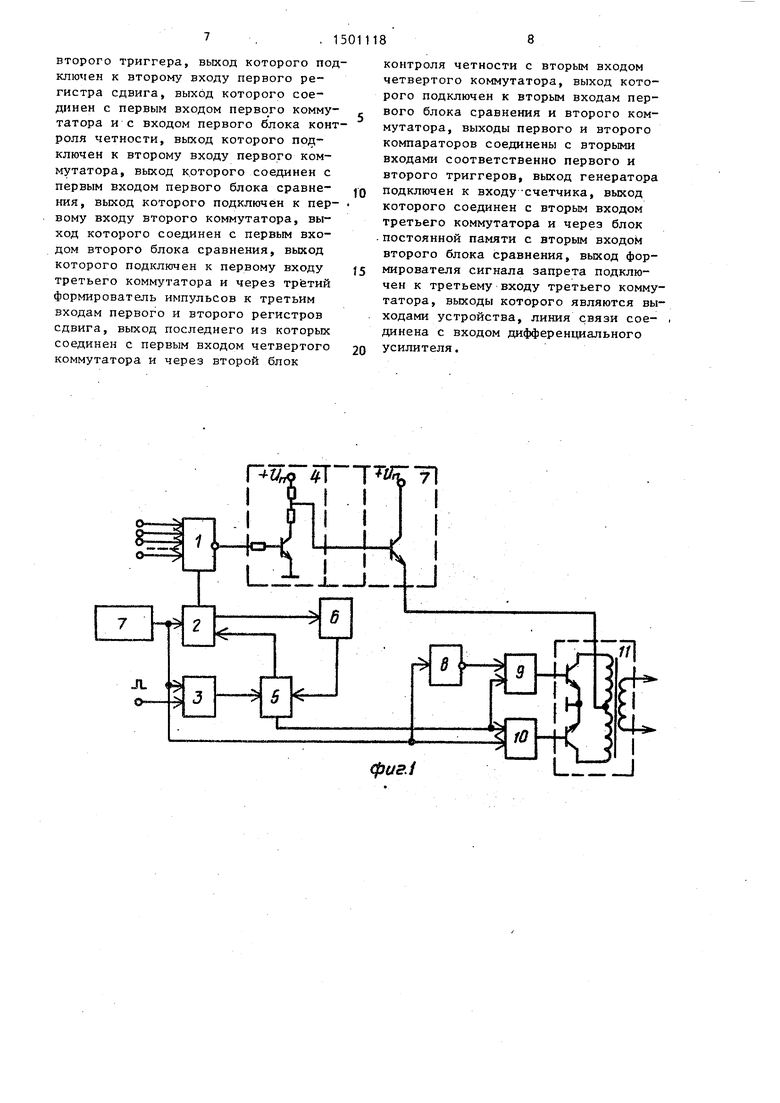

На фиг.1 показана функциональная схема передающей части; на фиг.2 - то же, приемной части; на фиг.З - диаграммы, поясняющие работу передающей частиJ на фиг.4 - то же, поясняющие работу приемной части.

Устройство содержит на передающей части коммутатор 1 (фиг.1), счетчик 2, элемент И 3, ключ 4, триггер 5, формирователь 6 импульсов, генератор 7, инвертор 8, элементы И 9 и 1Q

и амплитудный модулятор 11, а на приемной части - одновибратор 12, формирователь 13 тактовых импульсов, фильтр 14 низких частот (ФНЧ),дифференциальный усилитель 15, компараторы 16 и 17, формирователи 18 и 19 импульсов, триггеры 20 и 21, регистры 22 и 23 сдвига, коммутатор 24, блоки 25 и 26 контроля четности, коммутатор 27, блок 28 сравнения, коммутатор 29, формирователь 30 импульсов, блок 31 сравнения, формирователь 32 сигнала Запрет, коммутатор 33, генератор 34, счетчик 35 и блок 36 постоянной памяти.

Устройство работает следующим образом.

СП

00

Коды команд подаются на вторые информационные входы коммутатора 1,который осуществляет преобразование параллельного кода в последовательный при подаче сигналов управления с выхода счетчика 2 на первый.(управляющий) вход коммутатора 1. До прихода сигнала запуска на втором (прямом) выходе триггера 5 установлена 1, а на первом (инверсном) - , тем самым запрещается счет импульсов с генератора 7, поступающих на тактовый вход счетчика 2, и одновременно заприемной части, который служит для подавления синфазных помех и развязки приемной части с линией связи. С выхода дифференциального усилителя 15 команда поступает на вход ФНЧ 14, который подавляет высокочастотные помехи и вьщеляет первую гармонику сигнала, в результате чего команда приобретает вид, показанный на фиг.4«. Формирователь 13 тактовыХ импульсов формирует из принятой команды последовательность прямоугольных импульсов (фиг.45), причем для пре

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для сопряжения цифровой вычислительной машины с магнитофоном | 1984 |

|

SU1188745A1 |

| Устройство для сопряжения цифровой вычислительной машины с магнитофоном звукозаписи | 1985 |

|

SU1260969A2 |

| УСТРОЙСТВО ДЛЯ ПЕРЕДАЧИ РАДИОТЕЛЕМЕТРИЧЕСКИХ СИГНАЛОВ | 1994 |

|

RU2126139C1 |

| УСТРОЙСТВО ИЗБИРАТЕЛЬНОГО ВЫЗОВА | 2005 |

|

RU2299525C1 |

| Вычислительное устройство для реализации логических функций | 1983 |

|

SU1269130A1 |

| Устройство для передачи геофизической информации | 1987 |

|

SU1564579A1 |

| ЦИФРОВАЯ СИСТЕМА РАДИОВЕЩАНИЯ | 1992 |

|

RU2048704C1 |

| СИСТЕМА ЦИФРОВОГО СТЕРЕОФОНИЧЕСКОГО РАДИОВЕЩАНИЯ | 1991 |

|

RU2019041C1 |

| ПРИЕМНИК ПОСЛЕДОВАТЕЛЬНЫХ МНОГОЧАСТОТНЫХ СИГНАЛОВ | 1999 |

|

RU2169993C1 |

| ЦИФРОВОЙ РАДИОТЕЛЕФОН | 1994 |

|

RU2093960C1 |

Изобретение относится к телемеханике и может быть использовано для передачи сигналов телеуправления по каналам связи. Цель изобретения - упрощение устройства. Сущность предложенного технического решения заключается в поэтапном процессе обработки и анализа в приемной части сигналов телеуправления. Устройство содержит передающую и приемную части, связанные двухпроводной линией связи. Для достижения цели в устройство на передающей стороне введены коммутатор, счетчик, инвертор и амплитудный модулятор, а на приемной стороне - одновибратор, фильтр низких частот, дифференциальный усилитель, два компаратора, три формирователя импульсов, два регистра сдвига, четыре коммутатора, два блока контроля четности, два блока сравнения, формирователь сигнала запрета, счетчик и блок постоянной памяти. 4 ил.

прещается прохождение тактовой часто-15 дотвращения появления ложных импуль- ты чере з элементы И 9 и 10, которые сов за счет шумов в линии связи формирователь 13 тактовых импульсов выполнен с гистерезисом, верхний порог срабатывание его больше нулевого 20 напряжения, а нижний - меньше (фиг. 4«i) . Одновибратор 12 формирует импульсы, инвертированные по отношению к импульсам на выходе формирователя 13 (фиг.4ь). Формирователи 18 и 19 формируют короткие импульсы по передним фронтам прямоугольных (тактовых) последовательностей, вьщеленных из

используются для управления работой транзисторов амплитудного модулятора 11. На фиг.3с1, показан код, который передают в приемную часть, а на фиг.ЗсГ - тактовая частота, поступающая на вход счетчика 2, При поступлении сигнала запуска (фиг.Зь) на вход

элемента И 3 тактовый импульс,- кото «;рыи подается на другой вход элемен-

та, устанавливает положительным перепадом триггер 5 (по С-входу) в состояние, при котором на втором выходе установлен О, а на первом - 1, тем самым разрешается счет импульсов счетчиком 2 и прохождение тактовой частоты через элементы И 9 и 10,поскольку на других входа1х этих элементов установлена 1 (фиг.З).

Коммутатор 1, преобразуя параллельный код команды в последовательный, управляет работой ключа 4, кокоманды (фиг.4 г, (Э), и которые затем используются для сброса по первым 30 входам триггеров 21 и 20.

Амплитудные компараторы 16 и 17 срабатывают соответственно при превышении „рр и -и „jp (фиг.4а) и 35 устанавливают триггера 21 и 20 в единичные состояния. На вькоде триггеров 21 и 20 формируются сигналы,показанные соответственно на фиг.4еи Ж-. Эти сигналы подаются соответственно на регистры 22 и 23 сдвига, где происходит их сдвиг под воздействием соответствующих тактовых последовательностей. После окончания сдвига в регистрах 22 и 23 оказываются заАмплитудные компараторы 16 и 17 срабатывают соответственно при превышении „рр и -и „jp (фиг.4а) и 35 устанавливают триггера 21 и 20 в еди ничные состояния. На вькоде триггеров 21 и 20 формируются сигналы,показанные соответственно на фиг.4еи Ж-. Эти сигналы подаются соответствен но на регистры 22 и 23 сдвига, где происходит их сдвиг под воздействием соответствующих тактовых последовательностей. После окончания сдвига в регистрах 22 и 23 оказываются за40

торый меняет напряжение питания модулятора 11 (фиг.35). Одновременно на базы транзисторов амплитудного модулятора 11 поступают сигналы управления (фиг.Зеи ж), поэтому на его выходе формируется амплитудно модулированный сигнал, причем единичный символ кода команды передают пе- д5 писанными команды, выделенные из по- риодом частоты с увеличенной ампли- ложительных и отрицательных полуволн тудой, а нулевой - с уменьшенной амплитудно-модулированного сигнала (фиг..З. По окончании передачи ко- (фиг. и). Команды с выходов ре- манды на выходе счетчика 2 формиру- гистров 22 и 23 сдвига поступают со- ется сигнал, который запускает форми-- ответственно в блоки 25 и 26 контро- рователь 6 импульсов и формирует импульс, устанавливающий по первому входу триггер 5 в первоначальное состояние, тем самым передающая часть подготовлена к передаче следующей ко-„ которые воздействуют соответственно телеуправления. Команда теле- на коммутаторы 24 и 27, что приводит управления, пройдя по двухпроводной линии связи, поступает на вход дифференциального усилителя 15 (фиг.2)

ля, которые осуществляют контроль по четности полученных команд. Если условие четности соблюдено, то блоки 25 и 26 контроля вьщают сигналы.

к появлению на выходах коммутаторов кодов команд, которые затем сравниваются блоком 28 сравнения. При совкоманды (фиг.4 г, (Э), и которые затем используются для сброса по первым 30 входам триггеров 21 и 20.

Амплитудные компараторы 16 и 17 срабатывают соответственно при превышении „рр и -и „jp (фиг.4а) и устанавливают триггера 21 и 20 в единичные состояния. На вькоде триггеров 21 и 20 формируются сигналы,показанные соответственно на фиг.4еи Ж-. Эти сигналы подаются соответственно на регистры 22 и 23 сдвига, где происходит их сдвиг под воздействием соответствующих тактовых последовательностей. После окончания сдвига в регистрах 22 и 23 оказываются за

писанными команды, выделенные из по- ложительных и отрицательных полуволн амплитудно-модулированного сигнала (фиг. и). Команды с выходов ре- гистров 22 и 23 сдвига поступают со- ответственно в блоки 25 и 26 контро- которые воздействуют соответственно на коммутаторы 24 и 27, что приводит

писанными команды, выделенные из по- ложительных и отрицательных полуволн амплитудно-модулированного сигнала (фиг. и). Команды с выходов ре- гистров 22 и 23 сдвига поступают со- ответственно в блоки 25 и 26 контро- которые воздействуют соответственно на коммутаторы 24 и 27, что приводит

ля, которые осуществляют контроль по четности полученных команд. Если условие четности соблюдено, то блоки 25 и 26 контроля вьщают сигналы.

писанными команды, выделенные из по- ложительных и отрицательных полуволн амплитудно-модулированного сигнала (фиг. и). Команды с выходов ре- гистров 22 и 23 сдвига поступают со- ответственно в блоки 25 и 26 контро- которые воздействуют соответственно на коммутаторы 24 и 27, что приводит

к появлению на выходах коммутаторов кодов команд, которые затем сравниваются блоком 28 сравнения. При сов5

падении команд он формирует сигнал, который воздействует на коммутатор 2 в результате чего на выходе коммутатора 29 формируется код команды, ко- торый поступает с выхода коммутатора 27.

Генератор 34 генерирует частоту, поступающую на вход счетчика 35, на выходе которого формируются коды, управляющие работой блока 36 памяти и коммутатора 33. Кодовые комбинации хранящиеся в блоке 36 памяти, поступают на рход блока 31 сравнения, на другой вход которого подается код принятой команды. При совпадении код принятой команды и кода, хранящегося в блоке 36 памяти, блок 31 формирует импульс управления, поступающий на вход коммутатора 33 и который под воздействием кода с выхода счетчика 35 оказывается распределенным на направление (выход), соответствующее коду команды. Время, в течение которого производится сравнение кодов Т дан блоком 31 и формирование импульса управления, показано на фиг.4л. Импульс управления запускает формирователь 30, который обнуляет регистры сдвига 22 и 23 и подготавли- вает устройство к приему новой команды-. Формирователь 32 сигнала Запрет формирует сигнал, который, воздействуя на коммутатор 33, запрещает прохождение импульсов управления на выход приемной части во время приема команды (фиг.4 ).

Если в командах, вьщелённых из положительных и отрицательных полупериодов амплитудно-модулированного сигнала, блоки 25 и 26 контроля обнаруживают ошибки, то коммутаторы 24 и 27 формируют на выходах запрещенную кодовую комбинацию (комбинацию, отсутствующую в блоке 36 памяти). Коммутатор 29 аналогичным образом формирует запрещенную кодову1р комбинацию при несовпадении кодов на входах блока 28.

Формула изобретения

Устройство для передачи и приема сигналов, содержащее на передающей стороне генератор, первый, второй и третий элементы И, триггер, формирователь импульсов и ключи, на приемной стороне - генератор, первый,второй триггеры, формирователь такто

с

5 0 5 о

JQ

0

5

1186

вых импульсов, отличающееся тем, что, с целью упрощения устройства, в него введены на передающей стороне счетчик, коммутатор, инвертор и -амплитудный модулятор, выход генератора подключен .к первым входам первого и второго элементов И, счетчика и через инвертор к первому входу третьего элемента И, выход которого соединен с первым входом амплитудного модулятора, первый выход счетчика подключен через формирователь импульсов к первому входу триггера, первый выход которого соединен с вторыми входами третьего и второго элементов И, выход последнего из которых подключен к второму входу амплитудного модулятора, выход первого элемента И соединен с вторым входом триггера, второй выход которого подключен к второму входу счетчика, второй выход которого соединен с первым входом коммутатора, выход которого подключен к входу ключа, выход которого соединен с третьим входом амплитудного модулятора, выход которого подключен к линии связи, второй вход первого элемента И является входом запуска устройства, вторые входы коммутатора являются информационными входами устройства, на приемной стороне введены дифференциальный усилитель, фильтр низких частот, одновиб- ратор,- первый и второй компараторы, первый, второй и третий формирователи импульсов, первый и второй регистры сдвига, первый и второй блоки контроля четности, первый, второй, третий и четвертый коммутаторы, формирователь сигнала запрета, первый и второй блоки сравнения, счетчик, блок постоянной памяти, выход дифференциального усилителя соединен через фильтр низких частот с входами первого, второго компараторов и формирователя тактовых импульсов, выход которого подключен к первому входу первого регистра сдвига и к входам формирователя сигнала запрета, первого формирователя импульсов и одно- вибратора, выход которого соединен с первым входом второго регистра сдвига и через второй формирователь импульсов с первым входом первого триггера, выход которого подключен к второму входу второго регистра сдвига, выход первого формирователя импульсов соединен с первым входом

второго триггера, выход которого подключен к второму входу первого регистра сдвига, выход которого соединен с первым входом первого коммутатора НС входом первого блока контроля четности, выход которого подключен к второму входу первого коммутатора, выход которого соединен с первым входом первого блока сравнения, выход которого подключен к пер- вому входу второго коммутатора, выход которого соединен с первым входом второго блока сравнения, выход которого подключен к первому входу третьего коммутатора и через третий формирователь импульсов к третьим входам первого и второго регистров сдвига, выход последнего из которых соединен с первым входом четвертого коммутатора и через второй блок

контроля четности с вторым входом четвертого коммутатора, выход которого подключен к вторым входам первого блока сравнения и второго коммутатора, выходы первого и второго компараторов соединены с вторьми входами соответственно первого и второго триггеров, выход генератора

подключен к входу-счетчика, выход

которого соединен с вторым входом

третьего коммутатора и через блок

.постоянной памяти с вторым входом

второго блока сравнения, выход формирователя сигнала запрета подключен к третьему входу третьего коммутатора, выходы которого являются выходами устройства, линия связи сое- i динена с входом дифференциального

усилителя.

(pusА

cpuB.2

фигЗ

tfrtl

о 0

I fig.

фиёЛ

Шумы

0 i f

о г-т

ffiop I П

| Система телемеханики | 1982 |

|

SU1026148A1 |

| Топка с несколькими решетками для твердого топлива | 1918 |

|

SU8A1 |

| Тутевич В.Н | |||

| Телемеханика | |||

| М.: Наука, 1973, с | |||

| Водяной двигатель | 1921 |

|

SU325A1 |

Авторы

Даты

1989-08-15—Публикация

1987-12-23—Подача