ел

to

00

-fm

Изобретение относится к радиотехнике и связи и может быть использовано в измерительной технике.

Цель изобретения - расширение диапазона модулирующих частот и уменьшение уровня интермодуляционных составляющих в спектре выходного сигнала.

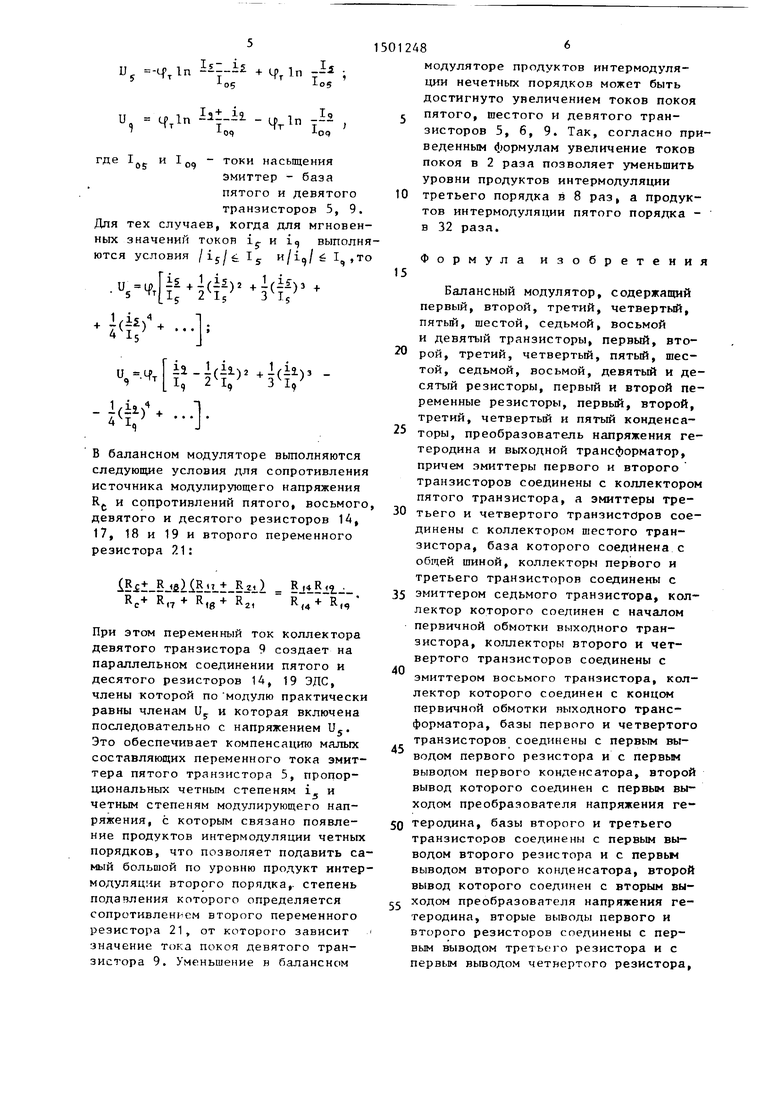

На чертеже представлена структурная электрическая схема балансного модулятора.

Балансный модулятор содержит первый, второй, третий, четвертый, пятьп1, шестой, седьмой, восьмой и девятый транзисторы 1-9, первый, второй, третий, четвертый, пятый, шестой, седьмой, восьмой, девятый и десятый резисторы 10-19, первый и второй переменные резисторы 20 и 21, первый, второй, третий, четвертый и пятый конденсаторы 22-26, преобразователь 27 напряжения ГРТР- родина и выходной трансформатор 28.

Балансный модулятор работает следующим образом.

Первый и второй транзисторы 1 и 2 периодически с частотой модулируемого .сигнала переключают выходной ток пятого транзистора 5. Седьмой и восьмой транзисторы 7, 8 необходимы для уменьшения инерционности пере-- ключения первого, второго, третьего и четвертого транзисторов 1-А и позволяют уменьшить влияние полного сопротивления нагрузки на работу баланс нбго модулятора. Выходной трансфор- матор 28 обеспечивает получение балансной модуляции. Подавление составляющих выходного напряжения с частотой модулируемого напряжения выполняется с помощью третьего и четвертого транзисторов 3 и 4, переключающих ток коллектора шестого транзистора 6, подстройка тока покоя которого (с целью достижения минимального уровня составляющей выходного напряжения с частотой модулируемого напряжения) обеспечивается с помощью первого переменного резистора 20. Девятый транзистор 9, структура проводимости которого противоположна структуре проводимости пятого транзистора 5, является элементом цепи коррекции нелинейности пятого транзистора 5. Первый и второй резисторы 10, 11 обеспечивают подачу на базы первого, второго, третьего и четвертого транзисторов 1-4 постоянног

напряжения, полученного путем деления напряжения первой шины питания с помощью третьего и четвертого резис- торов 12, 13, Постоянное напряжение на базы седьмого и восьмого транзисторов 7, 8 поступает из точки соединения шестого и седьмого резисторов 15, 16. Третий конденсатор 24 блоки- рует седьмой резистор 16 по переменному току. Восьмой резистор 17 и первый переменный резистор 21 обеспечивают стабилизацию тока покоя девятого транзистора 9, причем с помощью первого переменного резистора 21 значение этого тока покоя устанавливается близким к значению тока покоя пятого транзистора 5. Девятый резистор 18 является элементом цепи коррекции нелинейности, его сопротивление определяет ее коэффициент преобразования в переменную составляющую тока коллектора девятого транзистора 9. Десятый резистор 19 обеспечивает подачу на коллектор девятого Транзистора 9 постоянного напряжения с второй шины питания и является частью полного сошзотивления наг,- рузки девятого транзистора 9 по пе- ременному току. Первый и второй конденсаторы 22, 23, а также четвертый и пятый конденсаторы 25, 26 являются разделительными. Их реактивные сопротивления должны быть малыми во всем рабочем диапазоне частот. Преобразователь 27 с парафазным выходом используется для получения прямоугольного напряжения с частотой гетеродина и скважностью Q 2.: Под действием модулирующего напряжения и,, через девятый резистор 18, сопротивление которого больше входного сопротивления девятого транзистора 9, протекает переменный ток этого транзистора - связи с тем, что сопротивления пятого и десятого резисторов 14, 19 много больше, чем входное сопротивление пятого транзистора 5, через эмиттер пятого транзистора 5 протекает переменный ток ig i(i« Так как через р- п-пере- хо№1 пятого и девятого транзисторов 5, 9 протекают постоянные токи эмиттеров Ij и I. и соответственно пере- менные токи i и 1 то значения сос- таЕшяющих напряжений эмиттер - база пягого и девятого транзисторов 5, 9, связанных с токами ij и i, опреде- пяются выражениями

и, -cf..c,,in-I, и ц,1п 1, 12 ,

где 1 и I од - токи насыщения эмиттер - база пятого и девятого транзисторов 5, 9.

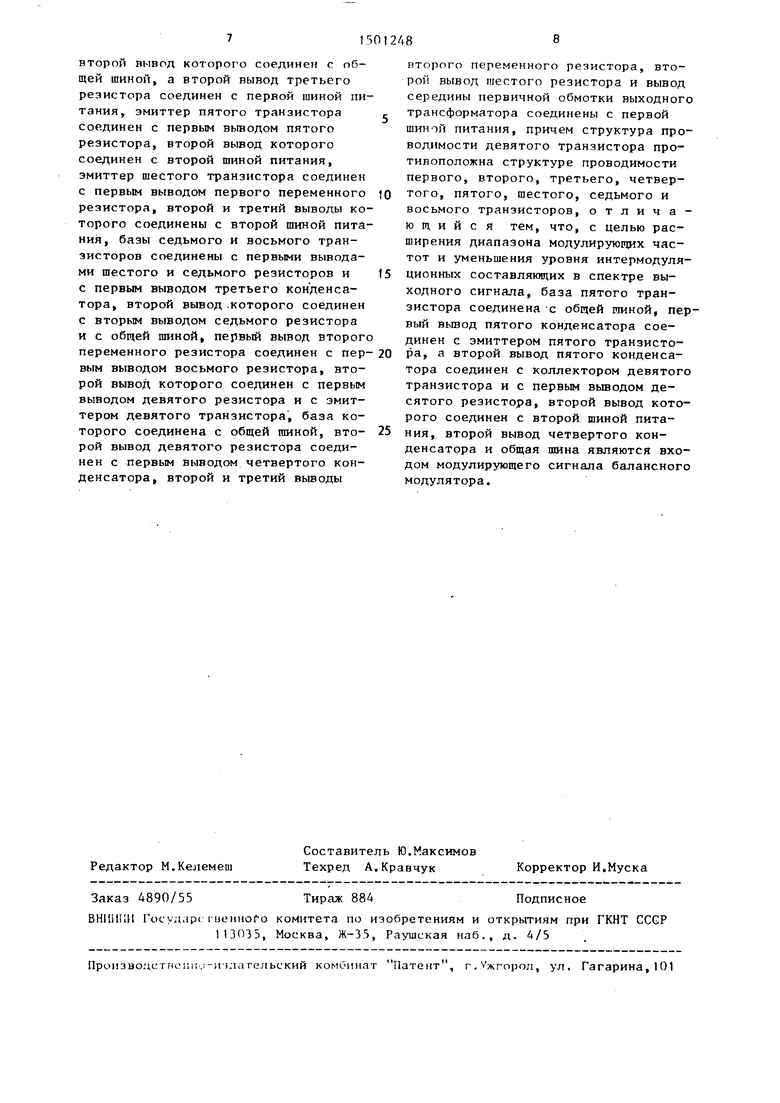

Для тех случаев, когда для мгновенных значений TOKOR ij- и iq выполняются условия и/1д/ё1,то

.„.,ii.i(ij, .i(k,.,

i(|V ...1;

41

и u ia -i(i2.)2 +i(ii)3 - , 24, 34/

-1ф)

- IqJ

В балансном модуляторе выполняются следующие условия для сопротивления источника модулирующего напряжения R и сопротивлений пятого, восьмого девятого и десятого резисторов 14, 17, 18 и 19 и второго переменного резистора 21:

i5i± 5j5li5lLl E i) - Bjt5ll

RC+ R,7+ R.e 21

+ R(q

При этом переменный ток коллектора девятого транзистора 9 создает на параллельном соединении пятого и десятого резисторов 14, 19 ЭДС, члены которой по модулю практически равны членам U и которая включена последовательно с напряжением Uj. Это обеспечивает компенсацию малых составляющих переменного тока эмиттера пятого транзистора 5, пропорциональных четным степеням i и четным степеням модулирующего напряжения, с которым связано появление продуктов интермодуляции четных порядков, что позволяет подавить самый большой по уровню продукт интер- модуляцни второго порядка,, степень подавления которого определяется сопротивлением второго переменного резистора 21, от которого зависит значение тока покоя девятого транзистора 9. Уменьшение н балансном

0

5

0

5

0

5

0

5

0

5

модуляторе продуктов интермодуляции нечетных порядков может быть достигнуто увеличением токов покоя пятого, шестого и девятого транзисторов 5, б, 9. Так, согласно приведенным формулам увеличение токов покоя в 2 раза позволяет уменьшить уровни продуктов интермодуляции третьего порядка в 8 раз, а продуктов интермодуляции пятого порядка - в 32 раза.

Формула изобретения

Балансный модулятор, содержащий первый, второй, третий, четвертый, пятьй, щестой, седьмой, восьмой и девятый транзисторы, первый, второй, третий, четвертый, пятый, шестой, седьмой, восьмой, девятый и десятый резисторы, первый и второй переменные резисторы, первый, второй, третий, четвертый и пятый конденсаторы, преобразователь напряжения гетеродина и выходной трансформатор, причем эмиттеры первого и второго транзисторов соединены с коллектором пятого транзистора, а эмиттеры третьего и четвертого транзисторов соединены с коллектором шестого транзистора, база которого соединена с общей шиной, коллекторы первого и третьего транзисторов соединены с эмиттером седьмого транзистора, коллектор которого соединен с началом первичной обмотки выходного транзистора, коллекторы второго и четвертого транзисторов соединены с эмиттером восьмого транзистора, коллектор которого соединен с концом первичной обмотки выходного трансформатора, базы первого и четвертого транзисторов соединены с первым выводом первого резистора и с первым выводом первого конденсатора, второй вывод которого соединен с первым выходом преобразователя напряжения гетеродина, базы второго и третьего транзисторов соединены с первым выводом второго резистора и с первый выводом второго конденсатора, второй вывод которого соединен с вторым выходом преобразователя напряжения гетеродина, вторые выводы первого и второго резисторов соединены с первым выводом третьего резистора и с первым вьшодом четвертого резистора.

второй вывод которого соединен с общей шиной, а второй вывод третьего резистора соединен с первой шиной питания, эмиттер пятого транзистора соединен с первым выводом пятого резистора, второй вывод которого соединен с второй шиной питания, эмиттер шестого транзистора соединен с первым выводом первого переменного резистора, второй и третий выводы которого соединены с второй шиной питания, базы седьмого и восьмого транзисторов соединены с первыми выводами шестого и седьмого резисторов и с первь1м выводом третьего конденсатора, второй вывод .которого соединен с вторым выводом седьмого резистора и с общей шиной, первый вывод второго переменного резистора соединен с пер- вым выводом восьмого резистора, второй вывод которого соединен с первым выводом девятого резистора и с эмиттером девятого транзистора, база которого соединена с общей шиной, вто- рой вывод девятого резистора соединен с первым выводом четвертого конденсатора, второй и третий выводы

второго переменного резистора, второй вывод шестого резистора и вывод середины первичной обмотки выходного трансформатора соединены с первой шиной питания, причем структура проводимости девятого транзистора противоположна структуре проводимости первого, второго, третьего, четвертого, пятого, шестого, седьмого и восьмого транзисторов, отличающийся тем, что, с целью расширения диапазона модулирующих частот и уменьшения уровня интермодуляционных составляющих в спектре выходного сигнала, база пятого транзистора соединена с общей гаиной, первый вьгоод пятого конденсатора соединен с эмиттером пятого транзистора, а второй вывод пятого конденсатора соединен с коллектором девятого транзистора и с первым вьшодом десятого резистора, второй вывод которого соединен с второй шиной питания, второй вывод четвертого конденсатора и общая шина являются входом модулирующего сигнала балансного модулятора.

| название | год | авторы | номер документа |

|---|---|---|---|

| Балансный модулятор | 1987 |

|

SU1649636A1 |

| Балансный модулятор | 1986 |

|

SU1437962A1 |

| Двойной балансный модулятор | 1984 |

|

SU1195411A1 |

| Усилитель мощности | 1991 |

|

SU1807551A1 |

| МОДУЛЯТОР АМПЛИТУДНО-МОДУЛИРОВАННЫХ СИГНАЛОВ | 2022 |

|

RU2783621C1 |

| ПРЕДВАРИТЕЛЬНЫЙ УСИЛИТЕЛЬ ПРОМЕЖУТОЧНОЙ ЧАСТОТЫ | 2006 |

|

RU2316890C1 |

| Балансный модулятор | 1980 |

|

SU907765A1 |

| Устройство для интегрирования произведения двух сигналов | 1984 |

|

SU1211764A1 |

| ГЕНЕРАТОР, УПРАВЛЯЕМЫЙ НАПРЯЖЕНИЕМ | 1991 |

|

RU2060576C1 |

| Входное устройство схемы сравнения токов | 1988 |

|

SU1554128A1 |

Изобретение относится к радиотехнике и связи и может быть использовано в измерительной технике. Цель изобретения - расширение диапазона модулирующих частот и уменьшение уровня интермодуляционных составляющих в спектре выходного сигнала. Балансный модулятор содержит девять транзисторов 1-9, десять резисторов 10-19, два переменных резистора 20,21, пять конд-ров 22-26, преобразователь 27 напряжения гетеродина и выходной трансформатор 28. Поставленная цель достигается за счет применения новой цепи коррекции нелинейности. Степень подавления продуктов интермодуляции второго порядка определяется сопротивлением резистора 21, от которого зависит значение тока покоя транзистора 9. Уменьшение продуктов интермодуляции нечетных порядков может быть достигнуто увеличением токов покоя транзисторов 5,6,9. Увеличение токов покоя в 2 раза позволяет уменьшить уровни продуктов интермодуляции третьего порядка в 8 раз, а пятого порядка в 32 раза. 1 ил.

| Устройство для возведения в степень | 1983 |

|

SU1265803A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Способ модулирования или манипулирования токов высокой частоты в сети | 1922 |

|

SU1437A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1989-08-15—Публикация

1987-11-16—Подача