121

торов, коллекторы третьего, пятого, седьмого, девятого, одиннадцатого, тринадцатого и пятнадцатого усшти- тельных транзисторов соединены с пер вьм выводом первого резистора смещения и с второй шиной питания, базы одиннадцатого и тринадцатого усилительных транзисторов объединены, подключены к первым выводам седьмого и восьмого резисторов смещения и являются первой шиной второго сигнала-сомножителя устройства, базы девятого и пятнадцатого усилительных транзисторов объединены, подключены к первым выводам девятого и десятого резисторов смещения и являются второй входной шиной второго сигнала-сомножителя устройства, базы десятого, двенадцатого, четырнадцатого и шестнадцатого усилительных транзисторов подключены к второму выводу первого резистора смещения и к первому выводу второго резистора смещения, вторые выводы второго, четвертого, шестого, седьмого и девятого резисторов смещения соединены с шиной нулевого потенциала, вторые выводы восьмого и десятого резисторов смещения подключены к второй шине питания, коллекторы десятого и четырнадцатого усилительных транзисторов соединены с первой обкладкой первого накопительного конденсатора и через первый ключ подключе-

1

Изобретение относится к интегрирующим усилительным устройствам и может быть использовано в аналоговых вычислительных машинах.

Целью изобретения является расширение полосы пропускания.

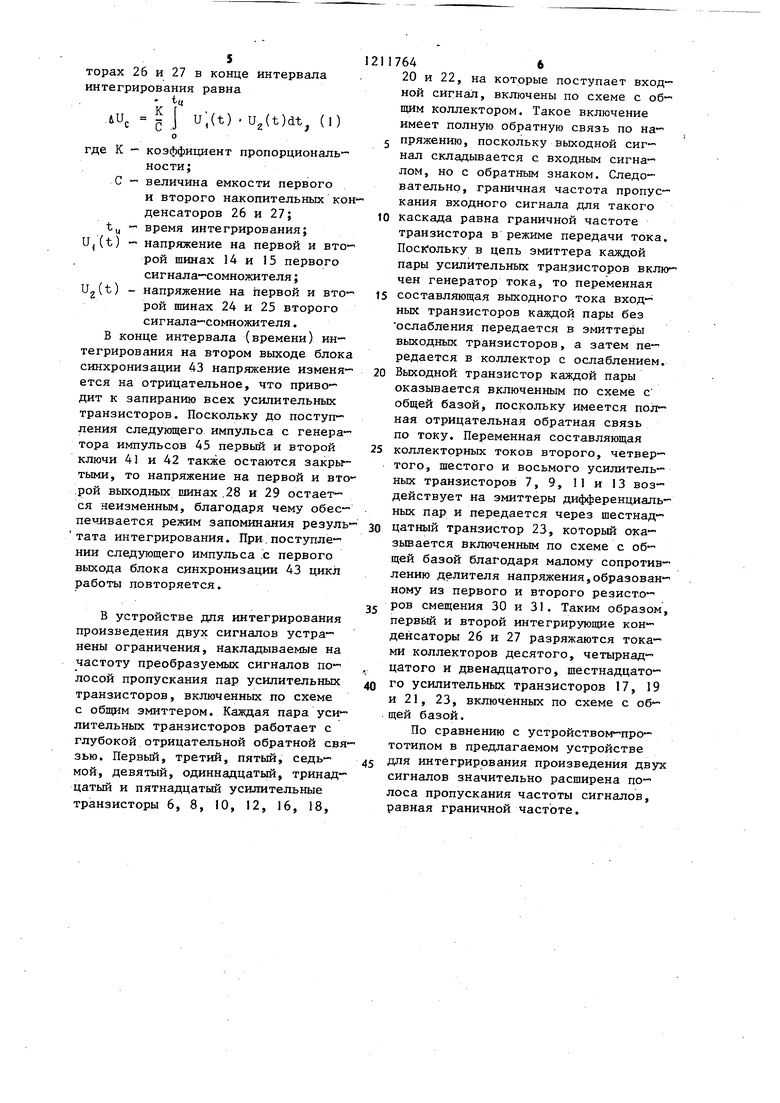

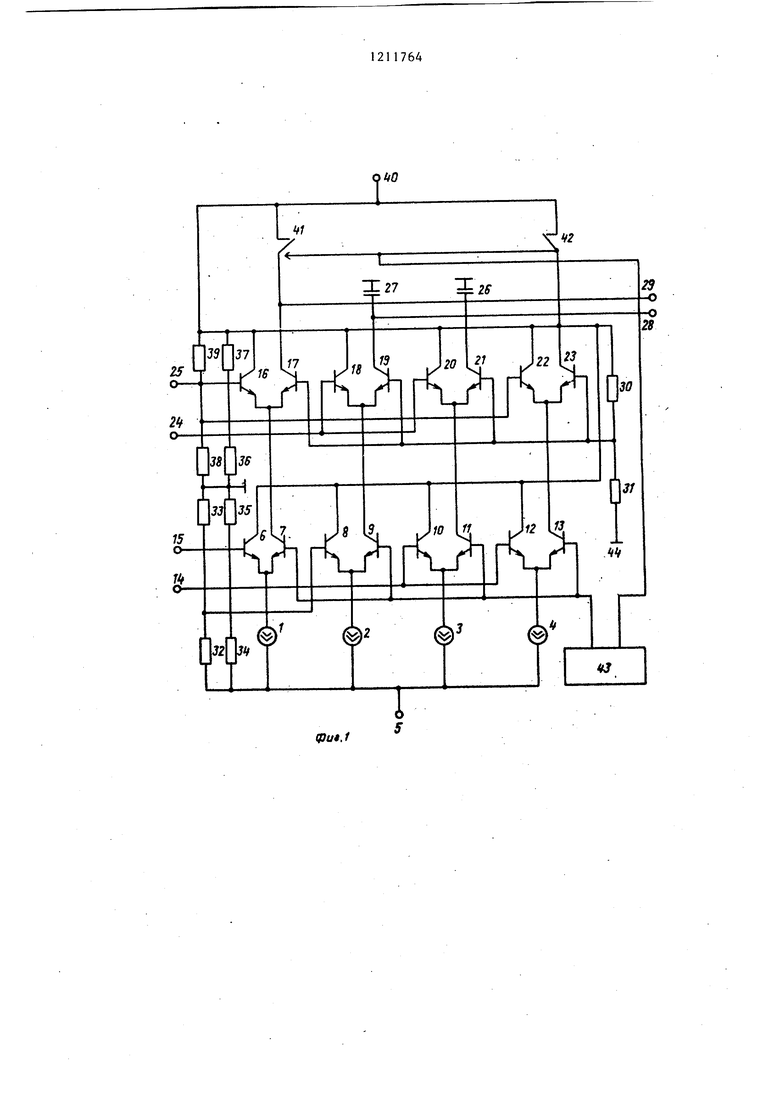

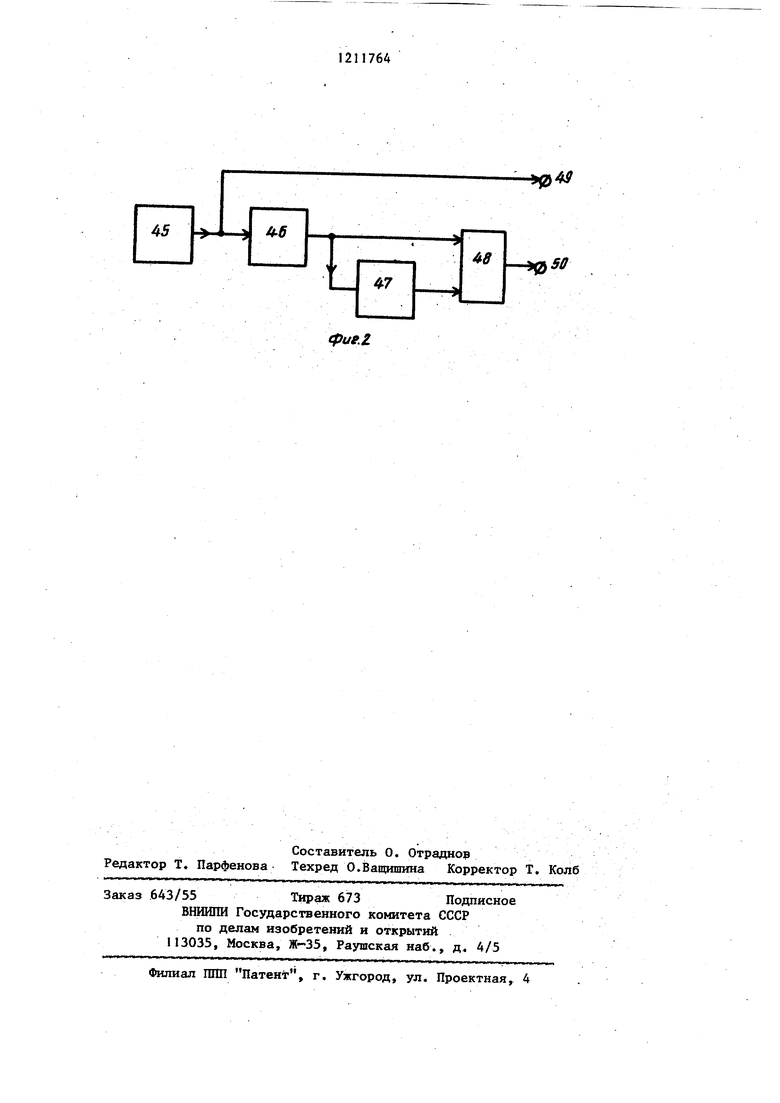

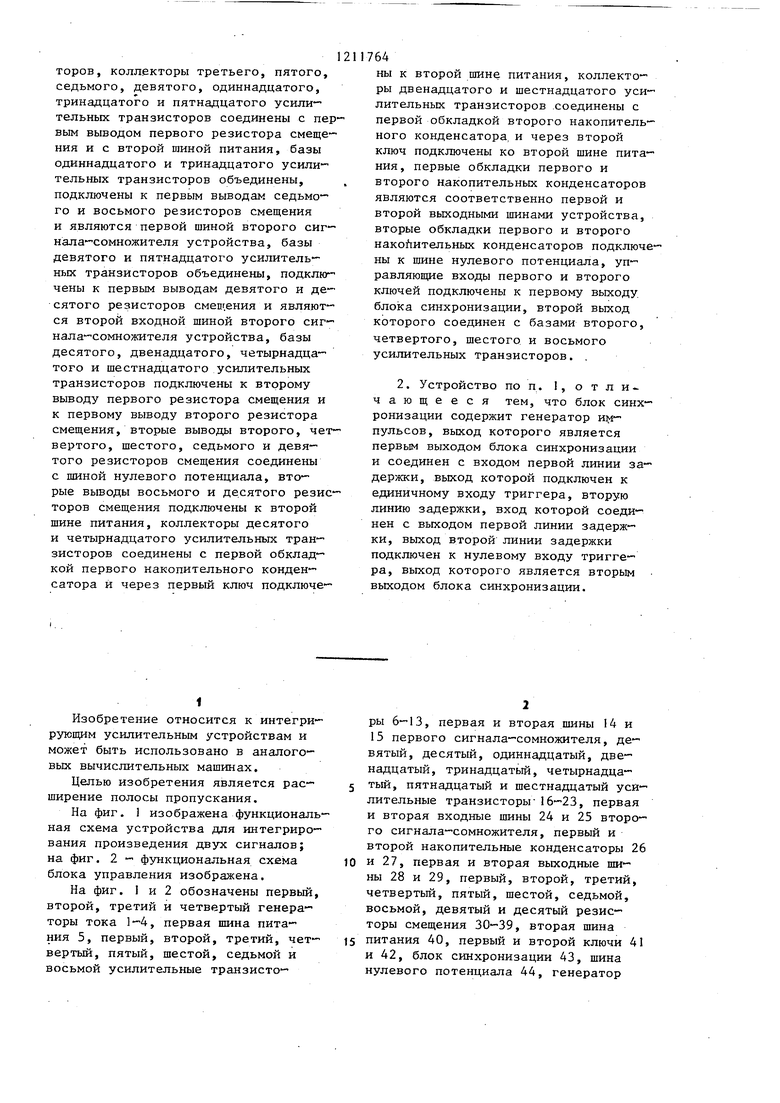

На фиг. 1 изображена функциональная схема устройства для интегрирования произведения двух сигналов; на фиг. 2 - функциональная схема блока управления изображена.

На фиг. I и 2 обозначены первый, второй, третий и четвертый генераторы тока 1-4, первая шина питания 5, первый, второй, третий, четвертый, пятый, шестой, седьмой и восьмой усилительные транзисто64

ны к второй шине питания, коллекторы двенадцатого и шестнадцатого у си- лительных транзисторов соединены с первой обкладкой второго накопительного конденсатора, и через второй ключ подключены ко второй шине питания, первые обкладки первого и второго накопительных конденсаторов являются соответственно первой и второй выходными шинами устройства, вторые обкладки первого и второго накопительных конденсаторов подключены к шине нулевого потенциала, управляющие входы первого и второго ключей подключены к первому выходу, блока синхронизации, второй выход которого соединен с базами второго, четвертого, шестого и восьмого усилительных транзисторов. .

2. Устройство по п. 1, о т л и чающееся тем, что блок синхронизации содержит генератор импульсов, выход которого является первым выходом блока синхронизации и соединен с входом первой линии задержки, выход которой подключен к единичному входу триггера, вторую линию задержки, вход которой соединен с выходом первой линии задержки, выход второй линии задержки подключен к нулевому входу триггера, выход которого является вторым выходом блока синхронизации.

ры 6-13, первая и вторая шины 14 и 15 первого сигнала-сомножителя, девятый, десятый, одиннадцатый, двенадцатый, тринадцатый, четырнадцатый, пятнадцатый и шестнадцатый усилительные транзисторы 16-23, первая и вторая входные шины 24 и 25 второго сигнала-сомножителя, первый и второй накопительные конденсаторы 26

и 27, первая и вторая вькодные шины 28 и 29, первый, второй, третий, четвертый, пятый, шестой, седьмой, восьмой, девятый и десятый резисторы смещения 30-39, вторая шина

питания 40, первый и второй ключи 41 и 42, блок синхронизации 43, шина нулевого потенциала 44, генератор

импульсов 45, первая и вторая линии задержки 46 и 47, триггер 48, первый и второй выходы блока синхронизации 49 и 50.

Устройство для интегрирования произведения двух сигналов работает следующим образом.

В первом такте производится установка в исходное состояние, а во втором такте.выполняются операции умножения и интегрирования, причем длительность второго такта задает время интегрирования. Длительность первого такта равна длительности выходного импульса генератора импульсов 45 в блоке синхронизации 43 С первого выхода блока синхронизации 43 импульс генератора 45 воздействует на управляющие входы первого и второго ключей 41 и 42 и вы- зьшает их замыкание. На интервале времени действия-импульса генератора 45 на втором выходе блока 43 существует отрицательное напряжение, величина которого равна напряжению питания с первой шины питания 5, второй, четвертьш, шестой и вось- |мой Усилительные транзисторы 7, 9, 11 и 13 оказьшаются запертыми, что приводит также к запиранию всех ос- ;тальных усилительных транзисторов

следствие отсутствия эмиттерных токов. За время замкнутого состояния первого и второго ключей 41 и 42 первый и второй накопительные конденсаторы 26 и 27 заряжаются до напряжения источника со второй шины питания 40.

Длительность задержки первой линии задержки 46 в блоке синхронизации 43 больше длительности импульса генератора импульсов 45. Поэтому изменение напряжения на втором выходе блока синхронизации 43 с отрицательного, равного напряжению эмиттерного питания, на положительное, равное напряжению на первой и второй входных шинах 14 и 15, при отсутствии входного сигнала произойдет после запирания первого и второго ключей 41, 42. Положительное напряжение на втором выходе при отсутствии сигнала на первой и второй входных шинах 15 и 14 вследствие идентичности транзисторных пар вызывает переключение половины эмиттерного тока, первого, третьего, пятого и седьмого усилитель- иых транзисторов 6, 8, 10 и 12 в

Р

211764

эмиттеры второго, четвертого, шестого и восьмого усилительных транзисторов 7, 9, 11 и 13, что приводит также к открьшанию девятого,

5 десятого, одиннадцатого, двенадцатого, тринадцатого, четьфнадцато- го, пятнадцатого и шестнадцатого усилительиых транзисторов 16-23. Если сигнал на первой и второй

to шинах 24 и 25 второго сигнала-со- множителя отсутствует, то коллекторные токи усилительных транзисторов равны. Сигнал с первой и второй шин 14 и 15 первого сигнала

5 сомножителя усиливается по току эмиттерными повторителями, образованными первым, третьим, пятым и седьмым усилительными транзисторами 6, 8, 10 и 12, и поступает на

20 эмиттеры в.торого, четвертого, шестого и восьмого усилительных транзисторов 7, 9, 11 и 13, включенных по схеме с общей базой, поскольку сопротивление второго выхода блока

25 управления 43 мало.

Усиленные по току сигналы модулируют величину тока эмиттеров девятого, десятого, одиннадцатого, двенадцатого , тринадцатого, четырнад-

цатого, пятнадцатого и шестнадцато-

го усилительных транзисторов 16-23, изменяя крутизну десятого, двенадцатого, четырнадцатого и шестнадцатого усилительных транзисторов 17, 19, 21 и 23. Таким образом, коллекторные токи десятого и четырнадцатого усилительных транзисторов 17 и 21 представляют собой ток разряда пер вого накопительного конденсатора 26, а коллекторнь е токи двенадцатого и шестнадцатого усилительных транзисторов 19 и 23 - ток разряда второго накопительного конденсатора 27 Разность токов разряда первого и второго накопительных конденсаторов 26 и 27 пропор1щонапьна в каждый момент времени на интервале интегрирования произведению мгновенных значений напряжений на первой, второй входных шинах 14 и 15 и на первой

и второй шинах 24 и 25 второго сигнала-сомножителя. Поэтому разность зарядов первого и второго накопительных конденсаторов 26 и 27 в каждый момент времени пропорцио-

нальна интегралу от произведения напряжений иа входных шинах.

Разность напряжений на первом и втором накопительных конденса-

5

торах 26 и 27 в конце интервала интегрирования равна Ц

&UP u;(t) U2(t)dt, (1)

о

где К коэффициент пропорциональ-

ности; С - величина емкости первого

и второго накопительных кон денсаторов 26 и 27; ty время интегрирования; U((t) - напряжение на первой и второй шинах 14 и 15 первого сигнала-сомножителя; Ug(t) - напряжение на первой и вто рой шинах 24 и 25 второго сигнала-сомножителя. В конце интервала (времени) интегрирования на втором выходе блока синхронизации 43 напряжение изменяется на отрицательное, что приводит к запиранию всех усилительных транзисторов. Поскольку до поступления следующего импульса с генератора импульсов 45 первый и второй ключи 41 и 42 также остаются закрытыми, то напряжение на первой и вто .рой выходных шинах ,28 и 29 остается неизменным, благодаря чему обеспечивается режим запоминания результата интегрирования. При.поступлении следующего импульса .с первого выхода блока синхронизации 43 цикл работы повторяется.

В устройстве для интегрирования произведения двух сигналов устранены ограничения, накладываемые на частоту преобразуемых сигналов полосой пропускания пар усилительных транзисторов, включенных по схеме с общим эмиттером. Каждая пара усилительных транзисторов работает с глубокой отрицательной обратной связью. Первый, третий, пятый, седьмой, девятый, одиннадцатый, тринадцатый и пятнадцатый усилительные транзисторы 6, 8, 10, 12, 16, 18,

117646

20 и 22, на которые поступает входной сигнал, включены по схеме с общим коллектором. Такое включение имеет полную обратную связь по на- 5 пряжению, поскольку выходной сигнал складывается с входным сигналом, но с обратным знаком. Следовательно, граничная частота пропускания входного сигнала для такого

10 каскада равна граничной частоте транзистора в режиме передачи тока. Поск ольку в цепь эмиттера каждой пары усилительных транзисторов включен генератор тока, то переменная

15 составляющая выходного тока входных транзисторов каждой пары без ослабления передается в эмиттеры выходных транзисторов, а затем передается в коллектор с ослаблением.

20 Выходной транзистор каждой пары оказывается включенным по схеме с общей базой, поскольку имеется полная отрицательная обратная связь по току. Переменная составляющая

5 коллекторных токов второго, четвертого, шестого и восьмого усилительных транзисторов 7, 9, 11 и 13 воздействует на эмиттеры дифференциальных пар и передается через шестнад-

0 цатный транзистор 23, который ока- зьшается включенным по схеме с общей базой благодаря малому сопротивлению делителя напряжения,образованному из первого и второго резисто- 2 ров смещения 30 и 31. Таким образом, первый и второй интегрирующие конденсаторы 26 и 27 разряжаются токами коллекторов десятого, четырнадцатого и двенадцатого, шестнадцато- 0 го усилительных транзисторов 17, 19 и 21, 23, включенных по схеме с общей базой.

По сравнению с устройством-прототипом в предлагаемом устройстве 5 для интегрирования произведения двух сигналов значительно расширена полоса пропускания частоты сигналов, равная граничной частоте.

и

I

«О

42

Х27in

г

o

% k, J я. 4L J

члгЧл

29

23

D

JO

J/

f«

H

| название | год | авторы | номер документа |

|---|---|---|---|

| Программируемый приемник сигналов для коммутационных сред | 1988 |

|

SU1718236A1 |

| Аналоговый четырехквадрантный перемножитель | 1988 |

|

SU1504655A1 |

| Балансный модулятор | 1980 |

|

SU907765A1 |

| Аналоговый четырехквадрантный перемножитель | 1987 |

|

SU1478230A1 |

| Аналоговый четырехквадратный умножитель | 1987 |

|

SU1474685A1 |

| Формирователь сигналов записи и считывания | 1983 |

|

SU1113852A1 |

| МАЛОШУМЯЩИЙ КВАРЦЕВЫЙ ГЕНЕРАТОР С АВТОМАТИЧЕСКОЙ РЕГУЛИРОВКОЙ УСИЛЕНИЯ | 2012 |

|

RU2498498C1 |

| Формирователь адресных сигналов | 1982 |

|

SU1049967A1 |

| Устройство для выделения тактовой частоты при воспроизведении цифрового сигнала | 1991 |

|

SU1770985A1 |

| Балансный модулятор | 1980 |

|

SU904197A1 |

m

Si2

45

)

4tf

фиг. I

4ff

| Патент США № 3689752, кл | |||

| Упругая металлическая шина для велосипедных колес | 1921 |

|

SU235A1 |

| Контрольный висячий замок в разъемном футляре | 1922 |

|

SU1972A1 |

| Приспособление для автоматической односторонней разгрузки железнодорожных платформ | 1921 |

|

SU48A1 |

| Бесколесный шариковый ход для железнодорожных вагонов | 1917 |

|

SU97A1 |

| Приспособление для склейки фанер в стыках | 1924 |

|

SU1973A1 |

Авторы

Даты

1986-02-15—Публикация

1984-05-11—Подача