(5) БАЛАНСНЬ Й МОДУЛЯТОР

| название | год | авторы | номер документа |

|---|---|---|---|

| Балансный модулятор | 1980 |

|

SU904197A1 |

| Устройство для интегрирования произведения двух сигналов | 1984 |

|

SU1211764A1 |

| Программируемый приемник сигналов для коммутационных сред | 1988 |

|

SU1718236A1 |

| Стереодекодер для системы стереофонического радиовещания с полярной модуляцией | 1991 |

|

SU1748269A1 |

| Формирователь сигналов записи и считывания | 1983 |

|

SU1113852A1 |

| Интегральный усилитель мощности для магнитофона | 1979 |

|

SU902205A1 |

| Устройство подсвета луча электронно-лучевой трубки | 1981 |

|

SU1002971A2 |

| Интегральный преобразователь индикатора магнитофона | 1979 |

|

SU1003140A1 |

| Устройство управления записью-считыванием информации для полупроводникового запоминающего устройства | 1986 |

|

SU1367040A1 |

| Триггер | 1983 |

|

SU1132343A1 |

I

Изобретение относится к аналоговой вычислительной технике и может быть использовано в электронной аппаратуре различного назначения, в частности в радиоприемных устройствах.

Известен балансный модулятор, содержащий первый и второй усилительные транзисторы, базы которых объединены и соединены с первым выходом первого дифференциального источника входного напряжения, третий и четвертый усилительные транзисторы, базы которых объединены и соединены со вторым выходом первого дифференциального источника входного напряжения, причем объединенные коллекторы первого и четвертого усилительных транзисторов и объединенные коллекторы второго и третьего усилительных транзисторов, являющиеся дифференциальными выходами модулятора через соответственно первый и второй нагрузочные резисторы подключены к источнику напряжения питания, причем эмиттеры первоГО и третьего усилительных тракзисторов объединены и подключены к первому выходу первого дифференциального усилительного каскада, а эмиттеры второго и четвертого усилительных транзисторов объединены и подключены ко второму выходу первого дифференциального усилительного каскада. Перемножаемые сигналы подаются между объединенными базами первого и второго усили10тельных транзисторов и объединенными базами третьего и четвертого усилительных транзисторов, а также на входы первого дифференциального усилительного каскада flj.

15

Линейность такого балансного модулятора по входному сигналу, подаваемому на входы дифференциального усилительного каскада,при больших входных сигналах резко ухудшается вследствие невозможности получить от дифференциального каскада выходной ток, превышающий его режимный ток, что значительно снижает динамический- диапазон выходных сигналов. Увеличение динамического диапазона выходных сигналов сопряжено с повышением режимного тока устройства и, следовательно, шума и потребляемой им мощности.

Наиболее близким к предложенному является балансный модулятор, содержащий дифференциальный источник входного напряжения, источник входного тока, два нагрузочных резистора, восемь компенсационных и шестнадцать Дсилительных транзисторов, четыре ис точника постоянного тока, первого и второго усилительных транзисторов объединены и подключены к первому выходу дифференциального источника входного напряжения, базы третьего и четвертого усилительных транзисторов объединены и подключены к второму выходу дифференциального источника входного напряжения, объединенные коллекторы первого и четвертого усилительных транзисторов и объединенные коллекторы второго и третьего усилительных транзисторов являются дифференциальными выходами балансного модулятора и подключены соответственно через первый и второй нагрузочные резисторы к входу источника напряжения питания, эмиттер первого усилительного транзистора подключен к эмиттеру пятого усилительного транзистора и к эмиттеру первого компенсационного транзистора, змиттер третьего усилительного транзистора подключен к эмиттеру шестого усилительного транзистора и к эмиттеру второго компенсационного транзистора, базы пятого усилительного транзистора и второго компенсационного транзистора объединены и подключены к коллектору второго компенсационного транзистора, базы шестого усилительного транзистора и первого компенсационного транзистора объединены и подключены к коллектору первого компенсационного транзистора, эмиттер второго усилительного транзистора подключен к эмиттеру восьмого усилительного транзис: тора и к эмиттеру третьего компенсационного транзистора, эмиттер четвертого усилительного транзистора подключен к эмиттеру четвертого компенсационного транзистора и к эмиттеру седьмого усилительного транзистора,

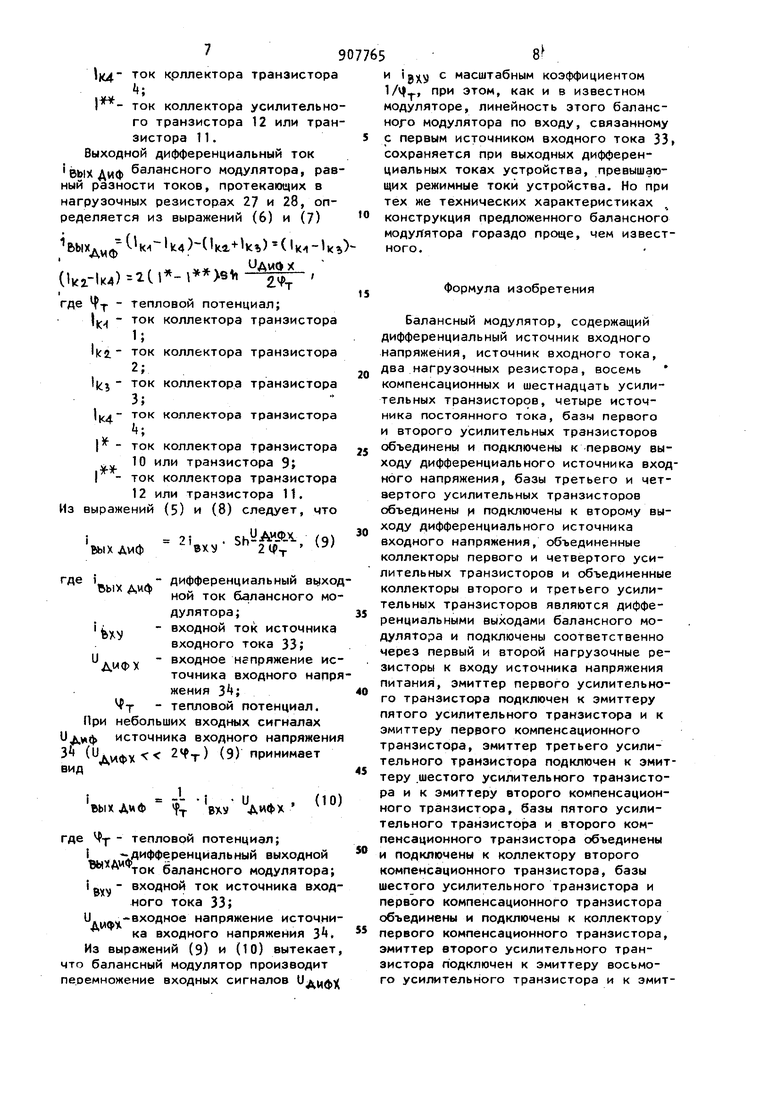

базы седьмого усилительного транзистора и третьего компенсационного транзистора объединены и подключены к

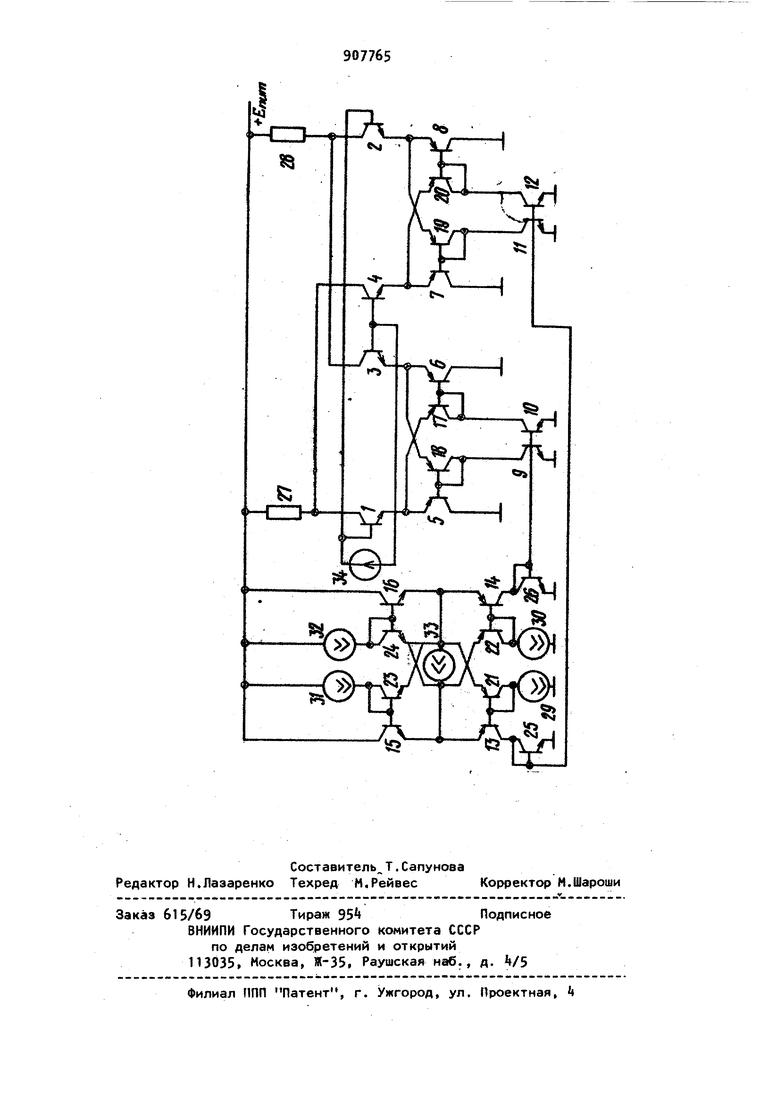

коллектору третьего компенсационного транзистора, базы восьмого усилительного транзистора и четвертого компенсационного транзисторов объединены и подключены к коллектору четвертого компенсационного транзистора, коллекторы пятого,шестого, седьмого и восьмого усилительных транзисторов подключены к общей шине, коллекторы первого, второго, третьего и четвертого компенсационных транзисторов соответственно подключены к коллекторам девятого, десятого, одиннадцатого и двенадцатого усилительных транзисторов, базы девятого, десятого, одиннадцатого и двенадцатого транзисторов попарно объединены, эмиттеры тринадцатого усилительного и шестого компенсационного транзисторов объединены, базы тринадцатого усилительного и пятого компенсационного транзисторов объединены и подключены к коллектору пятого компенсационного транзистора и к первому выходу первого источника постоянного тока, эмиттеры пятого компенсационного и четырнадцатого усилительного транзисторов объединены, баз.ы четырнадцатого усилительного и шестого компенсационного транзисторов объединены и подключены к коллектору шестого компенсационного транзистора и к первому выходу второго источника постоянного тока, вторые выходы первого и второго источников постоянного тока подключены к общей шине, эмиттеры пятнадцатого усилительного и восьмого компенсационного транзисторов объединены, базы пятнадцатого усилительного и седьмого компенсационного транзисторов объединены и подключены к коллектору седьмого компенсационного транзистора и х первому выходу третьего источника постоянного тока, эмиттеры шестнадцатого усилительного и седьмого компенсационного транзисторов объединены, базы шестнадцатого усилительного и восьмого компенсационного транзисторов объединены и подключены к коллектору восьмого компенсационного транзистора и к первому выходу четвертого источника постоянного тока, вторые выходы третьего и четвертого источников постоянного тока и коллекторы пятнадцатого и шестнадцатого усилительных транзисторов объединены и подключены ко входу источника напряжения питания 2, 59 Недостатком этого модулятора явля ется сложность его конструкции. Цель изобретения - упрощение устройства. Поставленная цель достигается тем, что в балансный модулятор введе ны девятый и десятый компенсационные транзисторы, эмиттеры которых подклю чены к общей шине, база и коллектор девятого компенсационного транзистора объединены и подключены к коллектору тринадцатого усилительного тран зистора и к базе одиннадцатого усили тельного транзистора, база и коллек,тор десятого компенсационного тран зистора объединены и подключены к ,коллектору четырнадцатого усилительного транзистора и к базе девятого усилительного транзистора, эмиттеры девятого, десятого, одиннадцатого и двенадцатого усилительных транзисторов подключены к общей шине, первый выход источника входного тока подклю чен к эмиттерам пятнадцатого и тринадцатого усилительных транзисторов, а второй выход - к эмиттерам четырнадцатого и шестнадцатого усилительных транзисторов. На чертеже представлена принципиальная электрическая схема балансного модулятора. Балансный модулятор содержит усилительные транзисторы 1-16, компенсационные транзисторы 17 2б, два нагрузочных резистора 27 и 28, четыре источника постоянного тока 29 32, источник входного тока 33 и источник входного напряжения 3. Предлагаемое устройство умножения с переменной крутизной работает еледующим образом. Входной ток , от первого источ ника входного сигнгпа - источника входного тока 33 - поступает на тран зисторы 13-16, 21-26 и источники пос тоянного тока 29-32. При этом через компенсационные транзисторы 25 и 26 8 диодном включении протекают соответственно токи 1к.2 и IKZS равные I iMi-t : iMx.. (1) ка«- 2 - V 1 :ift ±-T/lwx t.ilJJi-:.{2) К25 2 где ov - величина режимного тока,, задаваемого каждым из источников .постоянного тока 29-32. Коллекторные токи IKIU и fц. усилительных транзи-.торов 10 и 9, идентичных компенсационному транзистору 26, равны току, протекающему через транзистор 26, а коллекторные токи и усилительных транзисторов 11 и 12, идентичных компенсационному транзистору 25, равны току, протекающему через транзистор 25- Обозначив равные токи коллекторов транзисторов 10 и Э символом 1, а равные токи коллекторов транзисторов 11 и 12 символом I можно записать, следуя формулам (1) и (2) 5xV 4l y kiolc9 jf + Visxy- - gy K-n x-ia где loji - величина режимного тока, задаваемого каждым из источников постоянного тока .29-32. ри этом|, из формул (3) и () следут , что . , ;° /,. I IBXV(5) Дифференциальное напряжение Цлмфу т второго источника входного сигнаа - источника напряжения З - приладывается между базами усилительых транзисторов 1 и 3 и вызывает ротекание через их коллекторы токов, азность между которыми подчиняется ависимости 1,,-|,, 2|.5нУА«- -, де 4 тепловой потенциал; lk ток коллектора транзистора кз ° коллектора транзистора 3; I - ток коллектора усилительного транзистора 10 или транзистора 9. Аналогичным образом дифференциальое напряжение U протеание через коллекторы усилительных ранзисторов 2 и i токов, разность ежду которыми определяется как I I .(7) IKI fcA - о л е 4j - тепловой потенциал; f- ток коллектора транзистора 2; К4 крллектора транзистора ток коллектора усилительного транзистора 12 или транзистора 11. Выходной дифференциальный ток ВЫХ АиФ балансного модулятора, равный разности токов, протекающих в нагрузочных резисторах 27 и 28, определяется из выражений (6) и (7) ЬЫХдцф )П|са- - с%) ( JAVIOX ркг-1м)--гС1 - -2 где - тепловой потенциал; || - ток коллектора транзистора ki ток коллектора транзистора 2; ki тох коллектора транзистора ток коллектора транзистора ток коллектора транзистора 10 или транзистора 9 ( - ток коллектора транзистора 12 или транзистора 11, выражений (5) и (8) следует, что - . (9) -exvj Вых Лмф дифференциальный выход Пых ди()| ной ток балансного модулятора;входной ток источника входного тока 33; входное непряжение источника входного напря жения Т - тепловой потенциал. При небольших входных сигналах дцф источника входного напряжения З ( ) (9) принимает вид Bxv АИФХ еы X Avt Ф где Ч-|- - тепловой потенциал; 1 дифференциальный выходной ток балансного модулятора; i - входной ток источника входного тока 33; и.. ,-.,-входное напряжение источниЛИФX.I ка входного напряжения 34 Из выражений (Э) и (10) вытекает что балансный модулятор производит перемножение входных сигналов идц И igxv) масштабным коэффициентом 1/, при этом, как и в известном модуляторе, линейность этого балансного модулятора по входу, связанному с первым источником входного тока 33, сохраняется при выходных дифференциальных токах устройства, превышающих режимные токи устройства. Но при тех же технических характеристиках конструкция предложенного балансного модулятора гораздо проще, чем известного. Формула изобретения Балансный модулятор, содержащий дифференциальный источник входного напряжения, источник входного тока, два нагрузочных резистора, восемь компенсационных и шестнадцать усилительных транзисторсэв, четыре источника постоянного тока, базы первого и второго усилительных транзисторов объединены и подключены к первому выходу дифференциального источника входного напряжения, базы третьего и четвертого усилительных транзисторов объединены и подключены к второму выходу дифференциального источника входного напряжения, объединенные коллекторы первого и четвертого усилительных транзисторов и объединенные коллекторы второго и третьего усилительных транзисторов являются дифференциальными выходами балансного модулятора и подключены соответственно через первый и второй нагрузочные резисторы к входу источника напряжения питания, эмиттер первого усилительного транзистора подключен к эмиттеру пятого усилительного транзистора и к эмиттеру первого компенсационного транзистора, эмиттер третьего усилительного транзистора подключен к эмиттеру .шестого усилительного транзистора и к эмиттеру второго компенсационного транзистора, базы пятого усилительного транзистора и второго компенсационного транзистора объединены и подключены к коллектору второго компенсационного транзистора, базы шестого усилительного транзистора и первого компенсационного транзистора объединены и подключены к коллектору первого компенсационного транзистора, эмиттер второго усилительного транзистора подключен к эмиттеру восьмого усилительного транзистора и к змиттеру третьего компенсационного транзистора, эмиттер четвертого усилительного транзистора подключен к эми теру четвертого компенсационного транзистора и к эмиттеру седьмого усилительного транзистора, базы седь мого усилительного транзистора и третьего компенсационного транзистора объединены и подключены к коллектору третьего компенсационного транзистора, базы восьмого усилительного транзистора и четвертого компенсационного транзисторов объединены и под ключены к коллектору четвертого компенсационного транзистора, коллекторы пятого, шестого, седьмого и восьмого усилительных транзисторов подключены к общей шине, коллекторы первого, второго, третьего и четвертого компенсационных транзисторов соответ ственно подключены к коллекторам девятого, десятого, одиннадцатого и двенадцатого усилительных транзисторов, базы девятого, десятого, одиннадцатого и двенадцатого транзисторов попарно объединены, эмиттеры три надцатого усилительного и шестого компенсационного транзисторов объеди нены, базы тринадцатого усилительного и пятого компенсационного транзис торов объединены и подключены к коллектору пятого компенсационного тран зистора и к первому выходу первого источника постоянного тока, эмиттеры пятого компенсационного и четырнадцатого усилительного транзисторов объединены, базы четырнадцатого усилительного и шестого компенсационного транзисторов объединены и подключены к коллектору шестого компенсационного транзистора и к первому выходу второго источника постоянного тока, вторые выходы первого и второго источников постоянного тока подключены к общей шине, эмиттеры пятнадцатого усилительного и восьмого компенсационного транзисторов объеди нены, базы пятнадцатого усилительного и седьмого компенсационного транзисторов объединены и подключены к коллектору седьмого компенсационного транзистора и к первому выходу третьего источника постоянного тока, эмиттеры шестнадцатого усилительного и седьмого компенсационного транзисторов объединены, базы шестнадцатого усилительного и восьмого компенсационного транзисторов объединены и подключены к коллектору восьмого компенсационного транзистора и к первому выходу четвертого источника постоянного тока, вторые выходы третьего и четвертого источников постоянного тока и коллекторы пятнадцатого и шестнадцатого усилительных транзисторов объединены и подключены ко входу источника напряжения питания, отличающийся тем, что, с целью упрощения модулятора, в него введены девятый и десятый компенсационные транзисторы, эмиттеры которых подключены к общей шине, база и коллектор девятого компенсационного транзистора объединены и подключены к коллектору тринадцатого усилительного транзистора и к базе одиннадцатого усилительного транзистора, база и коллектор десятого компенсационного транзистора объединены и подключены к коллектору четырнадцатого усилительного транзистора и к базе девятого усилительного транзистора, эмиттеры девятого, десятого, одиннадцатого и двенадцатого усилительных транзисторов подключены-К общей шине, первый выход источника входного тока подключен к эмиттерам пятнадцатого и тринадцатого усилительных транзисторов, а второй выход - к эмиттерам четырнадцатого и шестнадцатого усилительных транзисторов. Источники информации, принятые во внимание при экспертизе 1.Гребен А.Б. Проектирование аналоговых интегральных схем. М., Энергия, 197.6, t. 144, рис. 7-3 (прототип). 2.Авторское свидетельство СССР по заявке № 2952945/18-24, кл. Н 03 С 1/54, G Об G 7/16, 30.06,80 (прототип).

Авторы

Даты

1982-02-23—Публикация

1980-07-04—Подача