Изобретение относится к импульсно технике и может быть использовано в аналого-цифровых преобразователях и в цифровых измерительных приборах.

Цель изобретения - повышение быстродействия путем снижения сопротивления базовых цепей входных транзисторов и повышения перегрузочной способности входного каскада.

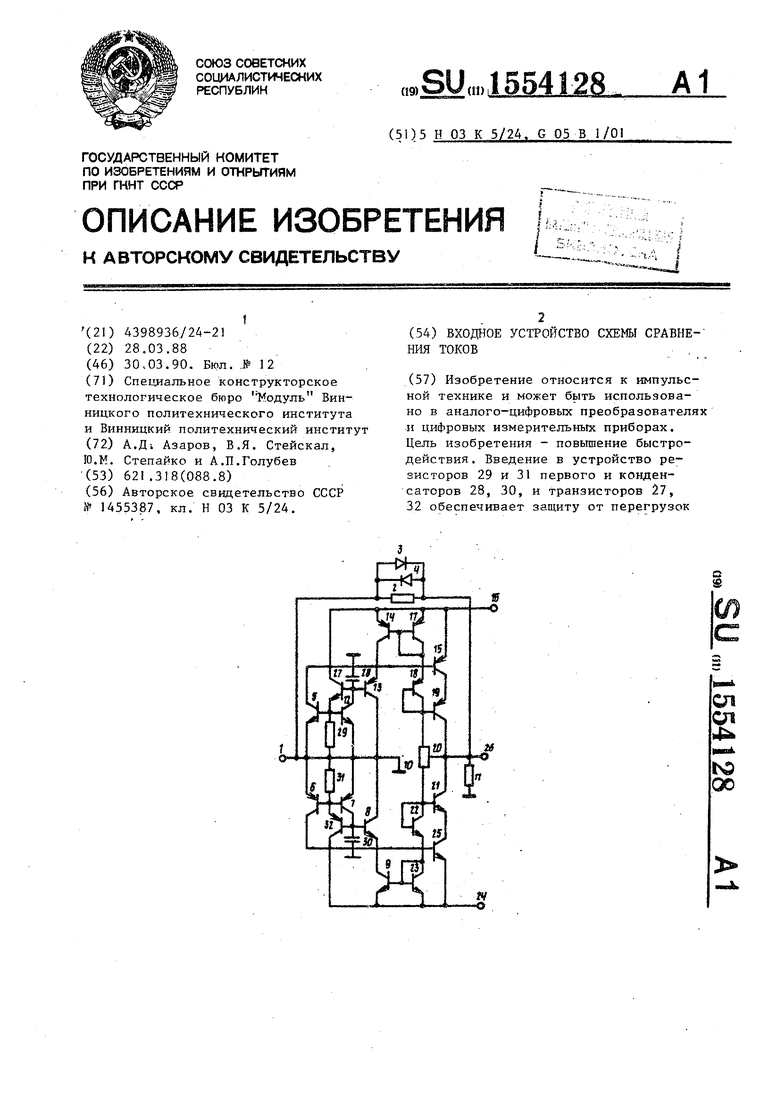

На чертеже представлена принципиальная схема входного устройства схемы сравнения токов,.

Входное устройство схемы сравнения токов содержит входную шину 1, к которой подключены первые выводы первого резистора 2 и двух встречно включенных диодов 3 и 4, эмиттер первого транзистора 5, эмиттер второго транзистора 6, база которого соединена с базой третьего транзистора 7, коллектор которого соединен с базой четвертого транзистора 8, эмиттер которого соединен с коллектором пятого транзистора 9, а коллектор - с шиной 10 нулевого потенциала , первым выводом второго резистора 1 3 с эмиттером третьего 7 и шестого 12 транзисторов и с коллектором седьмого транзистора 13, эмиттер которого соединен с коллектором восьмого транзистора 14, а база - с коллектором шестого транзистора 12, база которого соединена с базой первого транзистора 5, коллектор которого соединен с базой девятого транзистора 15, эмиттер которого соединен, с шиной 16 положительного напряжения, с эмиттером десятого транзистора 17 и эмиттером восьмого транзистора 14. База«последнего соединена с коллектором и базой десятого транзистора 17 и эмиттером одиннадцатого транзистора 18, коллектор и база которого соединены между собой, с базой двенадцатого транэистора 19 и первым выводом третьего резистора 20, второй вывод которого соединен с базой тринадцатого тран

0

0

5

0

5

0

5

зистора 21,-коллектором и базой четырнадцатого транзистора 22. Эмиттер последнего соединен с коллектором и базой пятнадцатого транзистора 23, базой пятого транзистора 9. Эмиттер последнего соединен с шиной 24 отрицательного напряжения, с эмиттером пятнадцатого транзистора 23 и эмиттером шестнадцатого транзистора 25, база которого соединена с коллектором второго транзистора 6, а коллектор - с эмиттером тринадцатого транзистора 21. Коллектор последнего соединен с выходной шиной 26, вторыми выводами двух встречно включенных диодов 3 и 4, первого 2 и второго 11 резисторов и коллектором двенадцатого транзистора 19. Эмиттер последнего соединен с коллектором девятого транзистора 15. Коллектор восемнадцатого транзистора 27 соединен с шиной 16 положительного напряжения, база - с коллектором шестого транзистора 12 и первым выводом первого конденсатора 28, а эмиттер - с базой первого транзистора 5 и первым выводом четвертого резистора 29. Второй вывод резистора 29 соединен с шиной 10 нулевого потенциала, вторыми выводами первого 28 и второго 30 конденсаторов и первым выводом пятого резистора 31, второй вывод которого соединен с базой второго транзистора 6 и эмиттером семнадцатого транзистора 32. База последнего соединена с коллектором третьего транзистора 7 и первым выводом второго конденсатора 30, а коллектор - с шиной 24 отрицательного напряжения.

Входное устройство схемы сравнения токов.состоит из каскада смещения, задающего токи покоя всей схемы и реализованного на резисторе 20, на двух отражателях тока (транзисторы 17 и 14) и (транзисторы 23 и 9) ; входного каскада, содержащего эмит- терные повторители на транзисторах

515

27 и 32, повышающих нагрузочную способность датчиков токов на транзисторах 12 и 7, которые задают ток покоя входных транзисторов 5 и 6, включенных по схеме с общей базой каскада усиления тока, состоящего из транзисторов 15 и 25, включенных по схеме с общим эмиттером выходного каскада на транзисторах 19 и 21, вклю- ченных по схеме с общей базой.

Входное устройство работает следующим образом.

При включении питания через резистор 20 смещения и транзисторы 17, 18, 22, 23, включенных в диодном режиме, протекает ток смещения (Гс/и), равный

I U-пит - 2 Ь 6э 17. 18.22,23 . смЕ20

где u;nur,

U-niJT - напряжения питания положительного и отрицательного источника питания соответственно;ZUfol7,18,

22,23 - сумма напряжений U $э транзисторов 17, 18, 22, 23; R20 - значение резистора 20. С целью минимизации аддитивной погрешности предлагаемое устройство необходимо реализовать на парах транзисторов, выполненных в интегральном исполнении. Это позволяет коэффициент отражения токовых зеркал на транзисторах 14, 17, 9, 23, 5, 12 и 6,7 практически сделать равным единице. По этой же причине транзисторы 13 и 15; 8 и 25 также должны быть с идентичными параметрами. Следовательно, через транзисторы 14 и 9, являющиеся источником и тоководом тока соответственно, протекает ток, также равный Геж. Этот же ток протекает через транзисторы 13 и 8, включенные по схеме с общей базой. Базовый ток этих транзисторов в Раз меньше Т см протекает через транзисторы 27, 12, 7, 32. Транзисторы 12 и 7 являются датчиками токовых зеркал на транзисторах 12, 5 и 7,6 соответственно. Следовательно, через входной каскад на транзисторах 5 и 6 протекает ток, равный , который в свою очередь является базовым током транзисторов 15 и 25. Учитывая, что эти транзисторы являются вторыми транзисто

Q

5

286

рами интегральных пар, первыми транзисторами которых являются транзисторы 13 и 8 соответственно, через них протекает ток практически равный I ctt . Этот же ток протекает и через выходной каскад на транзисторах 19 и 2. Ток через дополнительно введенные транзисторы 27 и 32 определяется напряжением U6j транзисторов 12 и 7 и значением соответствующих резисторов 29 и 3J.

Работа предлагаемого устройства при входных импульсных токах менее 0,5 мА полностью аналогична прототипу. При этом коэффициент усиления по току К jс разомкнутой петлей обратной связи равен

У /У 1Э+ «:Рг5

К

Чу

ft ср i

где, о(19,

коэффициенты усиления по току схем с общей базой соответствующих транзисторов. Они практически равны между собой и близки к единице,1

PfS P is коэФФиЦиенты усиления по току схем с общим эмиттером па соответствующих транзисторахJ ftcp среднее арифметическое значение коэффициентов p-n-р и п-р-п транзисторов. Дополнительно введены транзисторы 27 и 32, предназначенные для уменьшения времени восстановления устройства после перегрузки по входу токовыми импульсами, превышающими 0,5-0,7 мА. Это позволяет не только уменьшить сопротивления базовых цепей входных транзисторов, но и эффективно отрабатывать импульсные изменения базовых токов транзисторов 5 и 6 без перегрузки транзисторов 12 и 7. Для дополнительной стабилизации в этом случае потенциалов баз транзисторов 27 и 32 служат конденсаторы 28 и 30, емкость которых определяется величиной времени проникновения входного тока в базу.

Таким образом видно, что применение указанных мер защиты от перегрузок входного каскада улучшает динамические характеристики предлагаемой схемы устройства.

10

15

20

ормула изобретения Входное устройство схемы сравнения токов, содержащее три резистора, ва встречно включенных диода, шестнадцать транзисторов, шину нулевого потенциала, шину положительного питания, шину отрицательного питания, выходную шину, входную шину, к которой подключены первые выводы первого резистора и двух встречно вклюенных диодов, эмиттер первого транзистора и эмиттер второго транзистора, база которого соединена с базой третьего транзистора, коллектор которого соединен с базой четверто- го транзистора, эмиттер которого соединен с коллектором пятого транзистора, а коллектор - с шиной нулевого потенциала, первым выводом второго резистора, эмичтером третьего транзистора, эмиттером шестого транзистора и с коллектором седьмого транзистора, эмиттер которого соединен с коллектором восьмого транзисто- 25 ра, а база - с коллектором шестого транзистора, база которого соединена с базой первого транзистора, коллектор которого соединен с базой девятого транзистора, эмиттер которого соединен с шиной положительного напряжения, с эмиттером десятого транзистора и эмиттером восьмого транзистора, база которого соединена с кол- лектором и базой десятого транзистора и эмиттером одиннадцатого транзистора, коллектор и база которого соединены между собой, с базой двенадцатого транзистора и первым выводом третьего резистора, второй вывод которого соединен г базой тринадцатого транзистора, коллектором и ба30

35

40

0

5

0

5

30

35

40

зон четырнадцатого транзистора, эмиттер которого соединен с коллектором и базой пятнадцатого транзистора, базой пятого транзистора, эмиттер которого соединен с шиной отрицательного напряжения, с эмиттером пятнадцатого транзистора и эмиттером шестнадцатого транзистора, база которого соединена с коллектором второго транзистора, а коллектор - с эмиттером тринадцатого транзистора, коллектор которого соединен-с выходной шиной, вторыми выводами двух встречно включенных диодов, первого и второго резисторов и коллектором двенадцатого транзистора, эмиттер которого соединен с коллектором девятого транзистора, отличающееся тем, что, с целью повышения быстродействия, в него введены четвертый и пятый резисторы, первый и второй конденсаторы, семнадцатый транзистор, восемнадцатый транзистор, коллектор которого соединен с шиной положительного напряжения, база - с коллектором шестого транзистора и первым выводом первого конденсатора, а эмиттер - с базой первого транзистора и первым выводом четвертого резистора, второй вывод которого соединен с шиной нулевого потенциала, вторыми выводами первого и второго конденсаторов и первым выводом пятого резистора, второй вывод которого соединен с базой второго транзистора и эмиттером семнадцатого транзистора, база которого соединена с коллектором третьего транзистора и первым выводом второго конденсатора, а коллектор - с шиной отрицательного напряжения.

| название | год | авторы | номер документа |

|---|---|---|---|

| Входное устройство схемы сравнения токов | 1989 |

|

SU1626360A1 |

| Входное устройство схемы сравнения токов | 1988 |

|

SU1529434A1 |

| Формирователь импульсов управления | 1985 |

|

SU1290501A1 |

| ТТЛ-вентиль | 1985 |

|

SU1324103A1 |

| Устройство управления записью-считыванием информации для полупроводникового запоминающего устройства | 1986 |

|

SU1367040A1 |

| ТТЛ-вентиль | 1985 |

|

SU1324104A1 |

| ПРЕОБРАЗОВАТЕЛЬ ПОСТОЯННОГО НАПРЯЖЕНИЯ | 2003 |

|

RU2249905C2 |

| РЕЛЕ ПРОМЕЖУТОЧНОЕ (ВАРИАНТЫ) | 2004 |

|

RU2263366C1 |

| ТТЛ-инвертор | 1984 |

|

SU1269252A1 |

| Устройство для интегрирования произведения двух сигналов | 1984 |

|

SU1211764A1 |

Изобретение относится к импульсной технике и может быть использовано в аналого-цифровых преобразователях и цифровых измерительных приборах. Цель изобретения - повышение быстродействия. Введение в устройство резисторов 29 и 31, конденсаторов 28, 30, и транзисторов 27, 32 обеспечивает защиту от перегрузок входного каскада, чему способствует снижение сопротивления базовых цепей транзисторов 5, 6, 12, 7, и повышает быстродействие. Устройство содержит также входную шину 1, резисторы 2, 11, 20, два встречно включенных диода 3, 4, транзисторы 8, 9, шину 10 нулевого потенциала, транзисторы 13 - 15, 17 - 19, 21 - 23, 25, шину 16 положительного напряжения, шину 24 отрицательного напряжения и выходную шину 26. 1 ил.

| Входное устройство схемы сравнения токов | 1987 |

|

SU1455387A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1990-03-30—Публикация

1988-03-28—Подача