31303

Изобретение относится к радиотехнике, в частности к устройствам согласованной фнльтра1Ц 1и сигналов, и может быть использовано в системах передач.информации при приеме сложны шумоподобных сигналов - радиочастотных колебаний с различными несущими частотами.

Цель изобретения - повышение ка- чества фильтрации за счет сглаживания шумов аналого-цифровых преобразователей ,

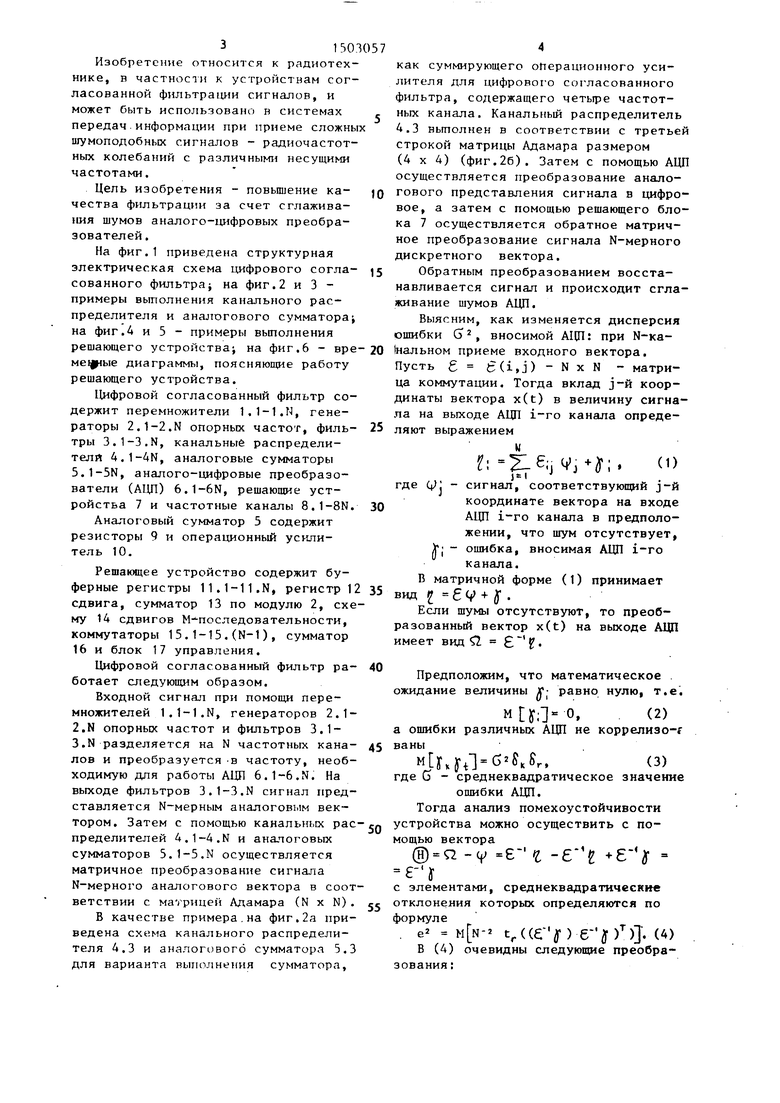

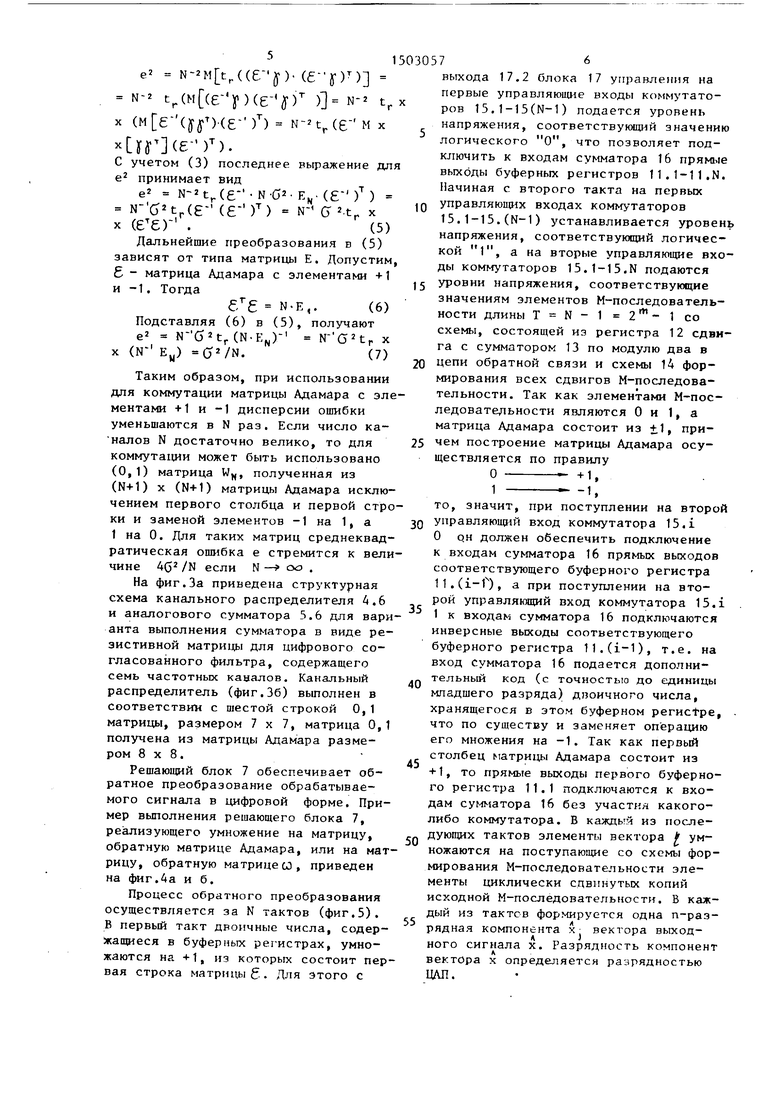

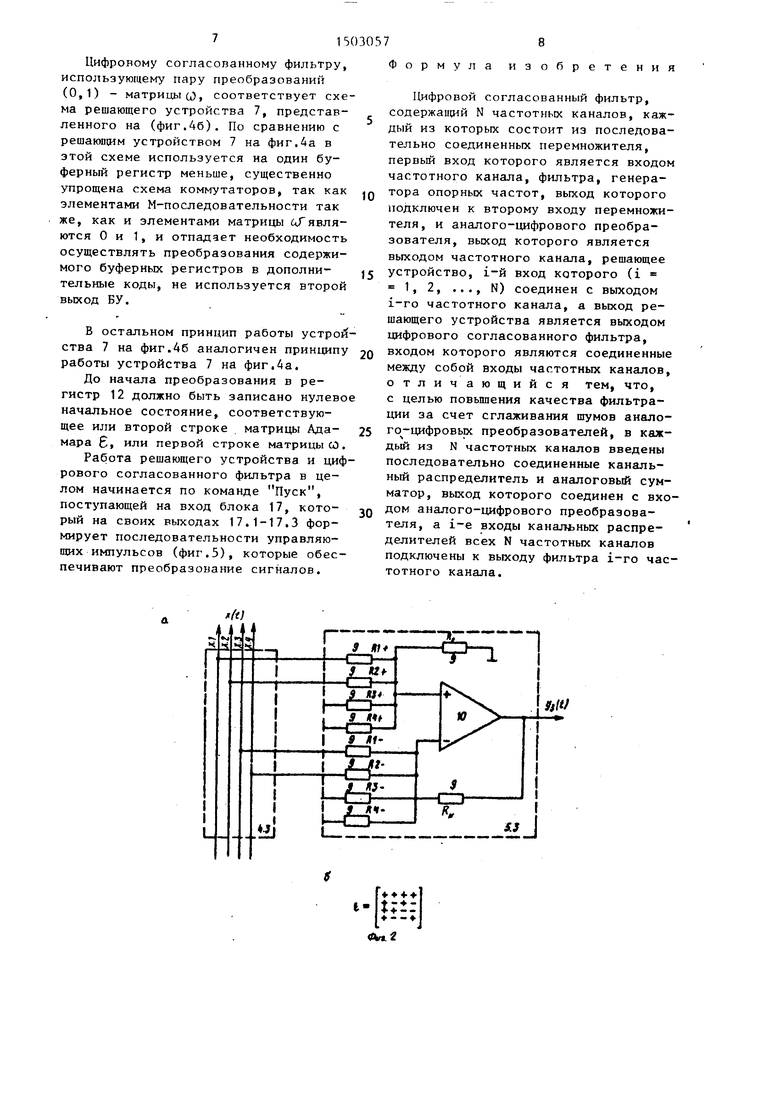

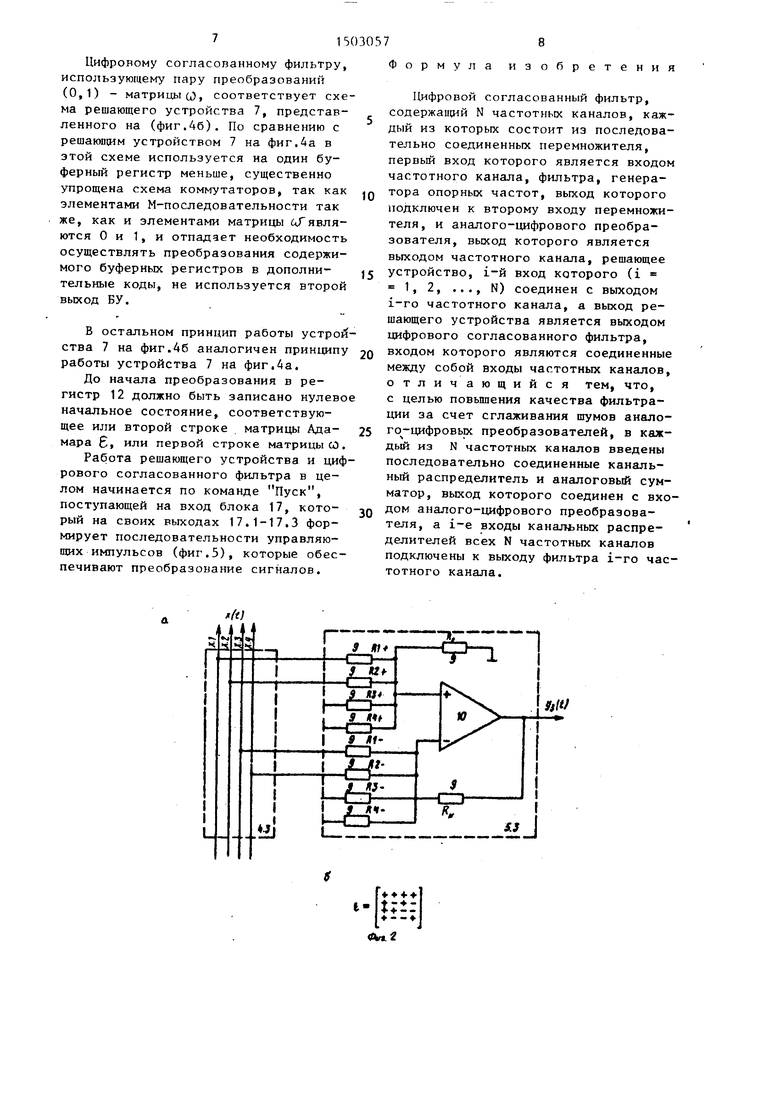

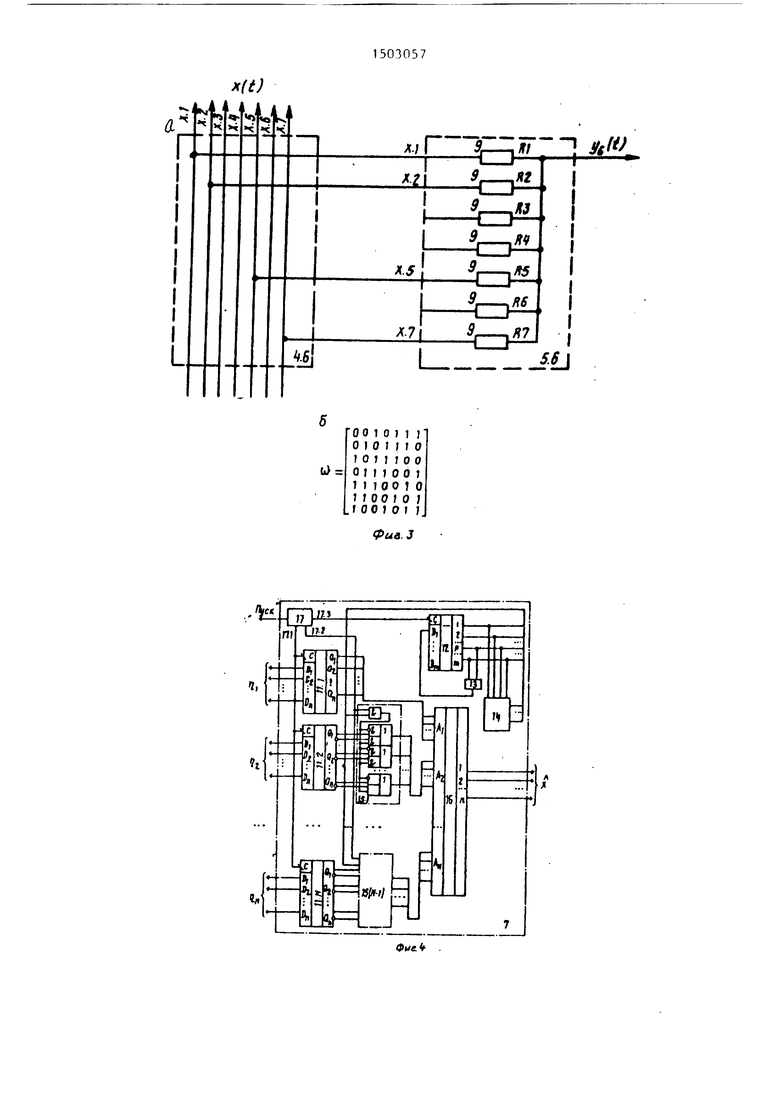

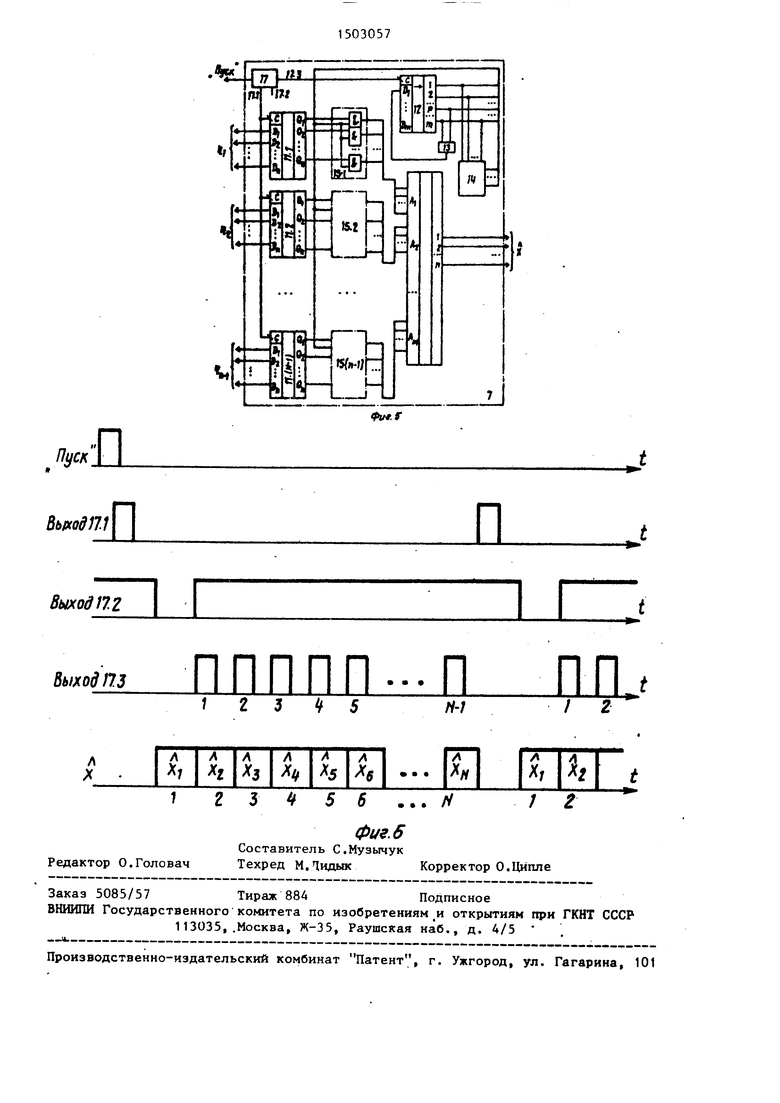

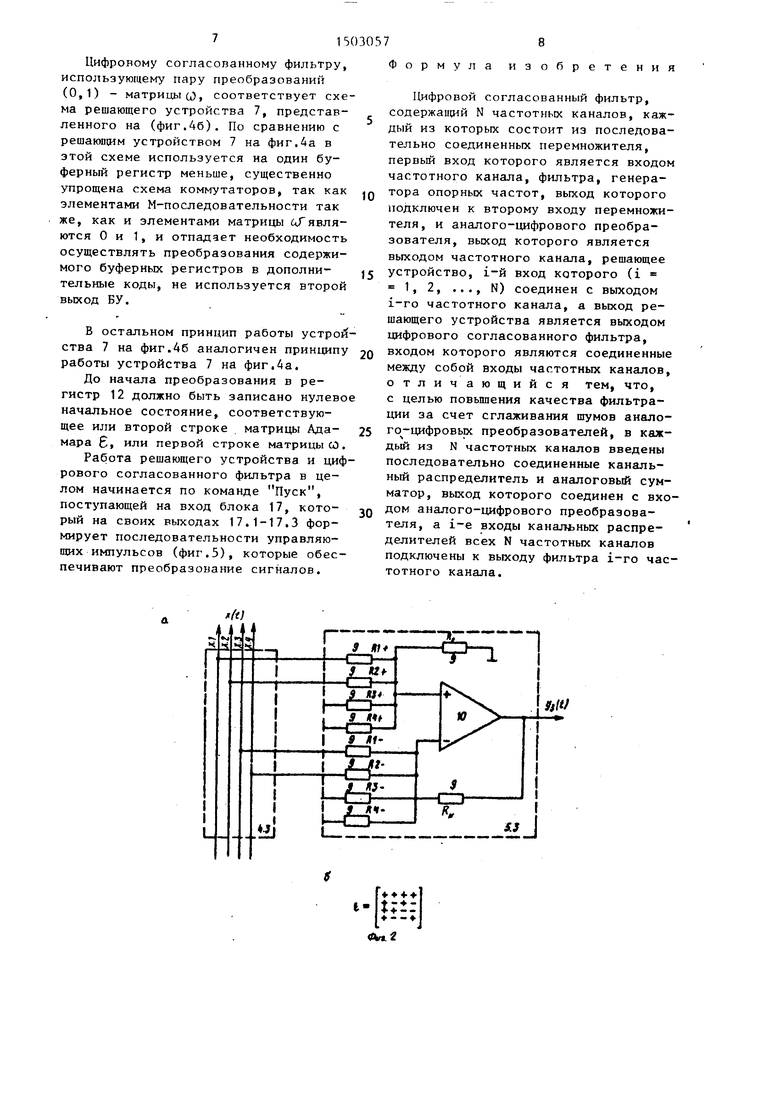

На фиг.1 приведена структурная электрическая схема цифрового согла- сованного фильтраi на фиг.2 и 3 - примеры вьтолнения канального распределителя и аналогового сумматораj на фиг.4 и 5 - примеры выполнения решающего устройства; на фиг.6 - аре ме1|ные диаграммы, поясняющие работу решающего устройства.

Цифровой согласованный фильтр содержит перемножители 1.1-1.N, генераторы 2.1-2.N опорных частот, филь- тры 3.1-3.N, канальные распределители 4.1-4N, аналоговые сумматоры 5.1-5N, аналого-цифровые преобразователи (А1ДП) 6.1-6N, решающие устройства 7 и частотные каналы 8.1-8N.

Аналоговый сумматор 5 содержит резисторы 9 и операционный усилитель 10.

Решающее устройство содержит буферные регистры 11.1-11.N, регистр 12 сдвига, сумматор 13 по модулю 2, схему 14 сдвигов Непоследовательности, коммутаторы 15.1-15.(N-1), сумматор 16 и блок 17 управления.

Цифровой согласованный фильтр ра- ботает следующим образом.

Входной сигнал при помощи перемножителей 1.1-1.N, генераторов 2.1- 2.N опорных частот и фильтров 3.1- 3.N разделяется на N частотных кана- лов и преобразуется -в частоту, необходимую для работы АЦП 6.1-6.N. На выходе фильтров 3.1-3.N сигнал представляется N-мерным аналоговым вектором. Затем с помощью канальных рас пределителей 4.1-4.N и аналоговых сумматоров 5.1-5.N осуществляется матричное преобразование сигнала N-мерного аналогового вектора в соответствии с матрицей Адамара (N х N).

В качестве примера,на фиг.2а приведена схема канального распределителя 4.3 и аналогового сумматора 5.3 для варианта выполнения сумматора.

как суммирующего операционного усилителя для цифрового согласованного фильтра, содержащего четыре частотных канала. Канальный распределитель 4.3 выполнен в соответствии с третьей строкой матрицы Адамара размером (4 X 4) (фиг.2б). Затем с помощью АЦЦ осуществляется преобразование аналогового представления сигнала в цифровое, а затем с помощью решающего блока 7 осуществляется обратное матричное преобразование сигнала N-мерного дискретного вектора.

Обратным преобразованием восстанавливается сигнал и происходит сглаживание щумов АЦП.

Выясним, как изменяется дисперсия ошибки G, вносимой АЦП: при N-xa- 1нальном приеме входного вектора. Пусть fc(i,j)-NxN - матрица коммутации. Тогда вклад j-й координаты вектора x(t) в величину сигнала на выходе АЦП i-ro канала определяют выражением

4i-7L i,. (1) 1

где ( - сигнал, соответствующий j-й координате вектора на входе АЦП i-ro канала в предположении, что шум отсутствует, if; - ошибка, вносимая АЦП i-rc

канала. В матричной форме (1) принимает

вид f б ( + У .

Если шумы отсутствуют, то преобразованный вектор x(t) на вьжоде АЦП имеет вид Q .

Предположим, что математическое . ожидание величины У равно нулю, т.е.

, (2) а ошибки различных АЦП не коррелизо-f ваны

.5,, (3)

где G - среднеквадратическое значение

ошибки АЦП.

Тогда анализ помехоустойчивости устройства можно осуществить с помощью вектора

(н) а -( е-Ч -6

8-f

с элементами, среднеквадратические

отклонения которых определяются по

формуле

. е t((e p (

В (4) очевидны следующие преобразования :

51503057

eZ ((E- К) (б)Г))1 выхода 17.2 блока 17 управления на

первые управляющие входы коммутаторов 15.1-15(N-1) подается уровень напряжения, соответствующий значени логического О, что позволяет подключить к входам сумматора 16 пряка. выходы буферных регистров 11.1-11.N Начиная с второго такта на первых управляющих входах коммутаторов 15.1-15.(N-1) устанавливается урове напряжения, соответствующий логичес кой 1, а на вторые управляющие вх ды коммутаторов 15.1-15.N подаются

N-z t(M(e- y)(e-7) ) N- t,

X (()(- ) ) М X

4УГ(е- )).

с учетом (3) последнее выражение для е

принимает вид

е N-2t(-. N-G2 Е. (- ) ) ,(e- (- ) ) N- G.t X X ()- .(5)

Дальнейшие преобразования в (5) зависят от типа матрицы Е. Допустим, - матрица Адамара с элементами +1 и -1. Тогда

б б N-E,. (6)

Подставляя (6) в (5), получают

е2 N- 62tr (N-E)- х X (N E) C;Z/N,(7)

Таким образом, при использовании для коммутации матрицы Адамара с элементами +1 и -1 дисперсии ошибки уменьшаются в N раз. Если число ка- налов N достаточно велико, то для коммутации может быть использовано (0,1) матрица Wj,, полученная из (N+1) X (N+1) матрицы Адамара исключением первого столбца и первой строки и заменой элементов -1 на 1, а 1 на 0. Для таких матриц среднеквад- ратическая ошибка е стремится к величине 4G /N если N - схэ .

На фиг.За приведена структурная схема канального распределителя А.6 и аналогового сумматора 5.6 для варианта выполнения сумматора в виде ре- эистивной матрицы для цифрового согласованного фильтра, содержащего семь частотных каналов. Канальный распределитель (фиг.Зб) выполнен в Соответствии с шестой строкой О,1 матрицы, размером 7x7, матрица 0,1 получена из матрицы Адамара размером 8x8.

Решающий блок 7 обеспечивает обратное преобразование обрабатываемого сигнала в цифровой форме. Пример выполнения решающего блока 7, реализующего умножение на матрицу, обратную матрице Адамара, или на матрицу, обратную матрице со, приведен на фиг.Да и б.

Процесс обратного преобразования осуществляется за N тактов (фиг.5). В первый такт двоичные числа, содержащиеся в буферных регистрах, умножаются на +1, из которых состоит первая строка матрицы 6. Для этого с

0

первые управляющие входы коммутаторов 15.1-15(N-1) подается уровень напряжения, соответствующий значению логического О, что позволяет подключить к входам сумматора 16 пряка.1е выходы буферных регистров 11.1-11.N. Начиная с второго такта на первых управляющих входах коммутаторов 15.1-15.(N-1) устанавливается уровень напряжения, соответствующий логической 1, а на вторые управляющие входы коммутаторов 15.1-15.N подаются

5 уровни напряжения, соответствующие значениям элементов М-последователь- ности длины T схемы, состоящей из регистра 12 сдвига с сумматором 13 по модулю два в

0 цепи обратной связи и схемы 14 формирования всех сдвигов М-последова- тельности. Так как элементами М-пос- ледовательности являются О и 1, а матрица Адамара состоит из ±1, при5 чем построение матрицы Адамара осуществляется по правилу

0 - +1,

1 -1,

то, значит, при поступлении на второй 0 управляющий вход коммутатора 15.1

0QH должен обеспечить подключение к входам сумматора 16 прямых выходов соответствующего буферного регистра 11.(1-Г), а при поступлении на второй управляющий вход коммутатора 15.i

1к входам сумматора 16 подключаются инверсные выходы соответствующего буферного регистра ll.(i-l), т.е. на вход сумматора 16 подается дополнительный код (с точностью до единицы младшего разряда) двоичного числа, хранящегося в этом буферном регисФре, что по существу и заменяет операцию его множения на -1. Так как первый столбец матрицы Адамара состоит из +1, то прямые выходы первого буферного регистра 11.1 подключаются к входам сумматора 16 без участил какого- либо коммутатора. В каждый из последующих тактов элементы вектора умножаются на поступающие со схемы формирования М-последовательности элементы циклически сдвинутых копий исходной М-последовательности. В каждый из тактов формируется одна п-раз5

рядная компонента Х вектора выходного сигнала х. Разрядность компонент вектора х определяется разрядностью ЦАП.

5

0

5

0

Цифровому согласованному фильтру, использующему пару преобразований (0,1) - матрицы (J, соответствует схема решающего устройства 7, представленного на (фиг.46). По сравнению с решаюиоим устройством 7 на фиг.4а в этой схеме используется на один буферный регистр меньше, существенно упрощена схема коммутаторов, так как элементами М-последовательности так же, как и элементами матрицы хГявляются О и 1, и отпадает необходимость осуществлять преобразования содержимого буферных регистров в дополнительные коды, не используется второй выход БУ.

В остальном принцип работы устройства 7 на фиг.Аб аналогичен принципу работы устройства 7 на фиг.4а.

До начала преобразования в регистр 12 должно быть записано нулевое начальное состояние, соответствующее или второй строке матрицы Ада- мара в, или первой строке матрицы со,

Работа решающего устройства и цифрового согласованного фильтра в целом начинается по команде Пуск, поступающей на вход блока 17, кото- рый на своих выходах 17.1-17.3 формирует последовательности управляющих импульсов (фиг.5), которые обеспечивают преобразование сигналов.

0

5

0

5

п

Формула изобретения

Цифровой согласованный фильтр, содержаиа1Й N частотных каналов, каждый из которых состоит из последовательно соединенных перемножителя, первый вход которого является входом частотного канала, фильтра, генератора опорных частот, выход которого подключен к второму входу перемножителя, и аналого-цифрового преобразователя, выход которого является выходом частотного канала, решающее устройство, 1-й вход которого (i 1, 2, ..., N) соединен с выходом i-ro частотного канала, а выход решающего устройства является выходом цифрового согласованного фильтра, входом которого являются соединенные между собой входы частотных каналов, отличающийся тем, что, с целью повышения качества фильтрации за счет сглаживания шумов анало- го-цифровьрс преобразователей, в каждый из N частотных каналов введены последовательно соединенные канальный распределитель и аналоговый сумматор, выход которого соединен с входом аналого-цифрового преобразователя, а i-e входы канальных распределителей всех N частотных каналов подключены к выходу фильтра i-ro частотного канала.

| название | год | авторы | номер документа |

|---|---|---|---|

| ЦИФРОВОЙ СОГЛАСОВАННЫЙ ФИЛЬТР СИГНАЛОВ С ДИСКРЕТНОЙ ЧАСТОТНОЙ МАНИПУЛЯЦИЕЙ | 1992 |

|

RU2114514C1 |

| Устройство формирования и обработки широкополосных сигналов | 2018 |

|

RU2691733C1 |

| РАДИОПРИЕМНОЕ УСТРОЙСТВО МНОГОЧАСТОТНЫХ СИГНАЛОВ | 2005 |

|

RU2310992C2 |

| ПРИЕМНИК ЦИФРОВЫХ СИГНАЛОВ | 2010 |

|

RU2423794C1 |

| Многоканальное устройство приема сложных сигналов | 1989 |

|

SU1786664A1 |

| Адаптивный фильтр | 1983 |

|

SU1116537A1 |

| АДАПТИВНОЕ УСТРОЙСТВО ПОИСКА ПСЕВДОСЛУЧАЙНОЙ ПОСЛЕДОВАТЕЛЬНОСТИ | 1983 |

|

SU1840275A1 |

| РЕЦИРКУЛЯЦИОННЫЙ КОРРЕЛЯТОР РАЗРЕШЕНИЯ ФАЗОКОДОМАНИПУЛИРОВАННЫХ СИГНАЛОВ | 2005 |

|

RU2283541C1 |

| МНОГОКАНАЛЬНЫЙ ПЕРЕПРОГРАММИРУЕМЫЙ ЦИФРОВОЙ ПРИЕМНЫЙ ТРАКТ | 2004 |

|

RU2289202C2 |

| СПОСОБ ПЕРЕДАЧИ ИНФОРМАЦИИ С ИСПОЛЬЗОВАНИЕМ СХЕМЫ MIMO В ГИПЕРКОМПЛЕКСНОМ ПРОСТРАНСТВЕ | 2023 |

|

RU2809479C1 |

Изобретение относится к радиотехнике и позволяет повысить качество фильтрации. Цифровой согласованный фильтр содержит частотные каналы 8, состоящие каждый из перемножителя 1, генератора 2 опорных частот, фильтра 3, канального распределителя 4, аналогового сумматора 5 и АЦП 6, а также решающее устройство 7. Цель достигается за счет обеспечения сглаживания шумов АЦП 6 в каждом частотном канале 8 с помощью введенных распределителя 4 и сумматора 5, которые осуществляют матричное преобразование сигнала N - мерного аналогового вектора в соответствии с матрицей Адамара. 5 ил.

a

b

nt

ML

M

.Я9

55J

0010 j 1 j

0 I 0 I M 0 0 J M 0 0 OM 1 00 J n 100 0

M 00 J 0 ;

r 00 J 0 J. Фил.З

Пуск

ВыходШ

Выход П.З

ППППП...П ПП

.f

| Беляев B.C | |||

| Цифровой согласованный фильтр для обработки составного частотно-манипулированного сигнала.- Радиотехника, 1984, N 3, с | |||

| Экономайзер | 0 |

|

SU94A1 |

Авторы

Даты

1989-08-23—Публикация

1987-06-22—Подача