Предлагаемое устройство относится к системам радиосвязи и может найти применение в широкополосных системах радиосвязи на основе расширения спектра.

Наиболее близким по технической сущности к заявляемому устройству является устройство передачи и приема дискретной информации с использованием широкополосных сигналов при кодовом разделении каналов, описанное в [1], принятое за прототип. Устройство [1] по функциональности и алгоритму работы аналогично заявляемому устройству.

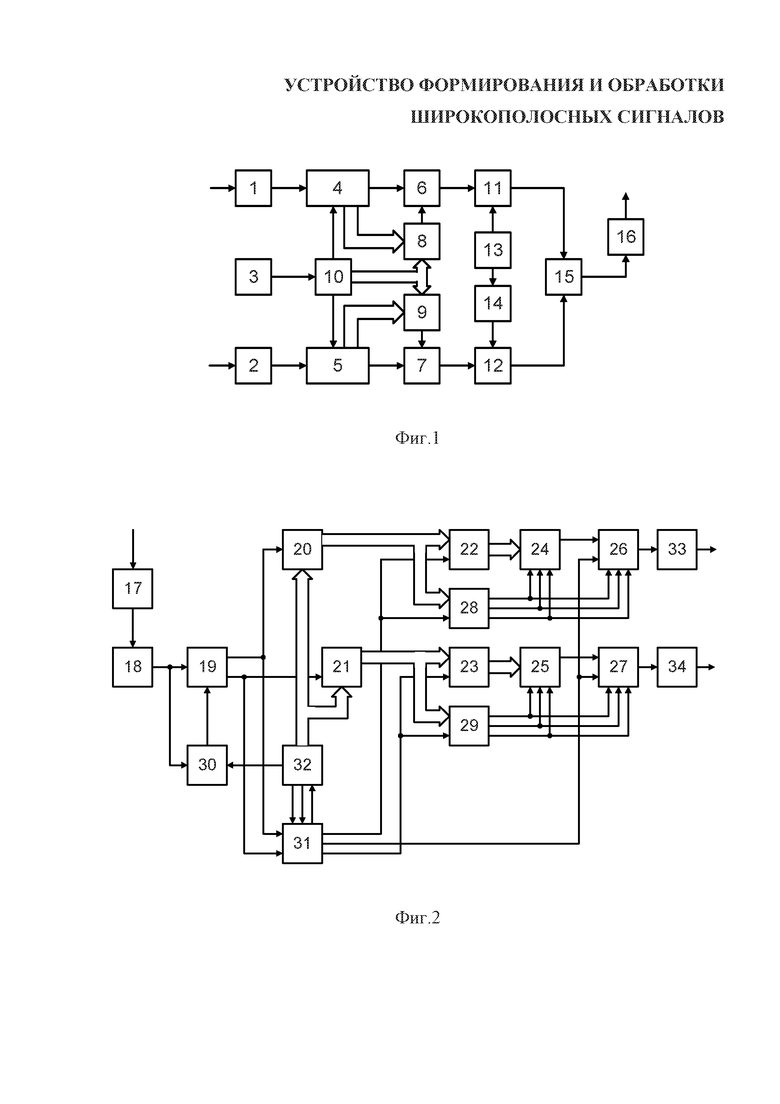

Устройство-прототип содержит передатчик и приемник, функциональные схемы которых приведены на фиг. 1 и фиг. 2 соответственно.

На фиг. 1 приняты следующие обозначения:

1, 2 – кодеры (КД);

3 – генератор чиповой частоты (ГЧЧ);

4, 5 – последовательно-параллельные преобразователи (ПР);

6, 7, 11, 12 – модуляторы (МД);

8, 9 – коммутаторы (КМ);

10 – генератор псевдослучайной последовательности (ГПСП);

13 – генератор несущей частоты (ГНЧ);

14 – фазовращатель (Ф);

15 – суммирующий усилитель (СУ);

16 – антенна (А).

Передатчик содержит генератор чиповой частоты (ГЧЧ) 3, генератор псевдослучайной последовательности (ГПСП) 10, генератор несущей частоты (ГНЧ) 13, фазовращатель (Ф) 14 на 90°, суммирующий усилитель (СУ) 15 и антенну (А) 16; кроме того, передатчик содержит два идентичных канала – синфазный и квадратурный, каждый из которых состоит из кодера (КД), первого и второго модуляторов (МД), последовательно-параллельного преобразователя (ПР) и коммутатора (КМ), соответственно.

На фиг. 2 приняты следующие обозначения:

17 – антенна (А);

18 – усилитель (У);

19 – когерентный детектор (КД);

20, 21 – N-канальные демодуляторы (ДМ);

22, 23 – решающие блоки (РБ);

24, 25 – коммутаторы (КМ);

26, 27 – параллельно-последовательные преобразователи (ПР);

28, 29 – блоки выбора максимума (БВМ);

30 – блок восстановления несущей (БВН);

31 – блок поиска и синхронизации по задержке (БПС);

32 – генератор ПСП (ГПСП);

33, 34 – декодеры (ДК).

Приемник содержит антенну (А) 17, усилитель (У) 18, когерентный детектор (КД) 19, блок восстановления несущей (БВН) 30, блок поиска и синхронизации по задержке (БПС) 31, генератор ПСП (ГПСП) 32; кроме того, приемник содержит два идентичных канала – синфазный и квадратурный, каждый из которых состоит из N-канального демодулятора (ДМ), решающего блока (РБ), коммутатора (КМ), параллельно-последовательного преобразователя (ПР), блока выбора максимума (БВМ) и декодера (ДК), соответственно.

Работа устройства-прототипа заключается в следующем.

В передатчике (фиг. 1) информационные данные поступают на входы КД 1 и КД 2 от двух независимых источников информации или от одного высокоскоростного источника через демультиплексор. После кодирования в КД 1 и КД 2 информация поступает на входы ПР 4 и ПР 5, распараллеливается на (k+1) выходов, в результате чего скорость на каждом выходе понижается в (k+1) раз. Сигналы с «k» выходов ПР 4 и ПР 5 поступают на управляющие входы КМ 8 и КМ 9 соответственно. В зависимости от вида «k» двоичных информационных символов на управляющих входах на выходах этих коммутаторов соответственно осуществляется выбор одной из N=2k ПСП, формирующихся в ГПСП 10. Сигналы с выходов (k+1) ПР 4 и ПР 5 подаются на один из входов первых модуляторов МД 6 и МД 7 соответственно, где они подвергаются псевдослучайной модуляции с помощью одной из ПСП, выбранной с помощью коммутаторов КМ 8 и КМ 9. С выходов первых модуляторов МД 6 и МД 7 двоичные ПСП в прямом или инверсном виде поступают на первые входы вторых модуляторов МД 11 и МД 12, а на их вторые входы поступает сигнал с выхода ГНЧ 13 непосредственно и через Ф 14. С выходов МД 11 и МД 12 сигналы через СУ 15 излучаются антенной А 16.

ГЧЧ 3 управляет ГПСП 10, управляющие выходы которого соединены со считывающими входами ПР 4 и ПР 5, чем обеспечивается их синхронизация, благодаря которой начало и конец каждой выбранной ПСП совпадает с началом и концом каждого бита информации.

В приемнике (фиг. 2) сигнал от А 17 после усиления в У 18 поступает на КД 19 и БВН 30. После выделения когерентной несущей и когерентного детектирования синфазной и квадратурной составляющих видеосигналы этих составляющих поступают на ДМ 20 и ДМ 21 и одновременно на БПС 31, который после вхождения в синхронизм фазирует ГПСП 32 и работу РБ 22, РБ 23, БВМ 28, БВМ 29, ПР 26 и ПР 27. N-канальные демодуляторы ДМ 20 и ДМ 21 имеют индивидуальные демодуляторы ПСП в количестве N=2k на каждую из возможных используемых ПСП на передаче. Поэтому на одном из индивидуальных демодуляторов ПСП будет осуществляться свертка сигнала по спектру, а на всех остальных (2k-1) индивидуальных демодуляторах ПСП свертки не будет. БВМ 28 и БВМ 29 определяют по максимуму энергии индивидуальный демодулятор ПСП, на котором произошла свертка, и выдают k бит информации на ПР 26 и ПР 27 соответственно для преобразования их в последовательный код и k бит информации на КМ 24 и КМ 25 для выдачи того решения с РБ 22 и РБ 23, которое соответствует индивидуальным демодуляторам ПСП, на которых произошла свертка.

Один бит информации с выхода КМ 24 и КМ 25 и k бит с выхода БВМ 28 и БВМ 29 преобразуются в ПР 26 и ПР 27 соответственно в последовательный код с повышением скорости данных в (k+1) раз и выдаются на ДК 33 и ДК 34 и далее двум получателям раздельно или после мультиплексирования в мультиплексоре одному получателю с повышенной скоростью данных.

Свертка осуществляется в одном из подканалов N-канального демодулятора. Свернутый сигнал подается на решающий блок, где интегрируется в интеграторах за длительность одного бита и результат интегрирования подается с каждого из N интеграторов соответственно на N решающих устройств своего канала РБ 22 и РБ 23.

РБ 22 и РБ 23 определяет знак передаваемого бита для «своего» канала. Одновременно свернутый сигнал с N-канального демодулятора поступает на БВМ 28 и БВМ 29 соответственно, которые также содержат по N интеграторов за длительность одного бита. БВМ 28 и БВМ 29 определяют максимальное из напряжений на выходах N интеграторов для «своего» канала и тем самым определяют, какая из N ПСП использовалась для данного конкретного набора из k бит информации.

Далее, с одной стороны, БВМ 28 и БВМ 29 через КМ 24 и КМ 25 открывает путь на выход тому решающему устройству N-канального РБ 22 и РБ 23, в канале которого наблюдается наибольший результат свертки и интегрирования. С другой стороны, БВМ 28 и БВМ 29 выдает решение о том наборе k бит информации, с помощью которых осуществлялся выбор одной ПСП из N на передаче. После этого k бит информации с выхода БВМ 28 и БВМ 29 и один бит с выхода КМ 24 и КМ 25 преобразуются в ПР 26 и ПР 27 в выходной поток синфазного или квадратурного канала соответственно, затем декодируются в ДК 33 и ДК 34 и выдаются получателю.

Недостатком устройства-прототипа является сложность его технической реализации для сигналов с большими базами (длиной ПСП), так как количество аналоговых каналов обработки в приемнике растет пропорционально N – количеству каналов демодуляторов синфазного и квадратурного каналов. Можно говорить о том, что при N > 32 техническая реализация такого устройства экономически нецелесообразна, а при N > 1024 практически невозможна.

В заявляемом изобретении решается задача адаптации устройства-прототипа для работы с сигналами с большими базами.

Достигаемый при использовании изобретения технический результат – устройство формирования и обработки широкополосных сигналов с возможностью работы с сигналами с большой базой.

Для решения поставленной задачи в устройство формирования и обработки широкополосных сигналов, содержащее в формирующей части синфазный и квадратурный каналы, выполненные идентично, в состав каждого из которых входят последовательно соединенные кодер и последовательно-параллельный преобразователь, причем вход кодера является входом информационного сигнала, последовательно соединенные первый и второй модуляторы; а также содержащее последовательно соединенные генератор чиповой частоты и генератор псевдослучайной последовательности (ПСП), управляющие выходы которого подключены к соответствующим считывающим входам последовательно-параллельных преобразователей синфазного и квадратурного каналов, последовательно соединенные генератор несущей частоты и фазовращатель на 90°, причем выход генератора несущей частоты соединен со вторым входом второго модулятора синфазного канала, а выход фазовращателя соединен со вторым входом второго модулятора квадратурного канала; суммирующий усилитель, первый и второй входы которого соединены с выходами вторых модуляторов, а выход является выходом формирующей части устройства;

содержащее в обрабатывающей части синфазный и квадратурный каналы, выполненные идентично, в состав каждого из которых входят блок выбора максимума, параллельно-последовательный преобразователь и декодер, выход которого является выходом информационного сигнала, а вход соединен с выходом параллельно-последовательного преобразователя; выходы блока выбора максимума являются входами параллельно-последовательного преобразователя; также содержащее усилитель, вход которого является входом обрабатывающей части устройства, последовательно соединенные блок поиска и синхронизации по задержке и генератор ПСП, первый и второй выходы которого соединены с первым и вторым входами блока поиска и синхронизации по задержке, второй выход которого соединен с входами синхронизации блоков выбора максимума и с управляющими входами параллельно-последовательных преобразователей;

отличающееся тем, что дополнительно, согласно изобретению, в формирующей части в состав синфазного и квадратурного каналов введен генератор М-последовательности, у которого входы записи начального состояния соединены с выходами последовательно-параллельного преобразователя, вход разрешения записи начального состояния объединен со считывающим входом последовательно-параллельного преобразователя, а выход соединен с первым входом первого модулятора, причем тактовые входы генераторов М-последовательности подключены к выходу генератора чиповой частоты, а вторые входы первых модуляторов синфазного и квадратурного каналов соединены с первым и вторым выходами генератора ПСП, в обрабатывающей части введены в состав синфазного и квадратурного каналов введены два идентичных подканала, состоящих из последовательно соединенных умножителя, блока перестановки отсчетов и блока преобразования Уолша, блок объединения квадратур, выход которого соединен с входом блока выбора максимума, а первый и второй входы соединены со выходами блоков преобразования Уолша синфазного и квадратурного каналов, также введены генератор частоты дискретизации, блок аналого-цифрового преобразования и два регистра-дециматора, причем выход генератора частоты дискретизации соединен с первым входом блока аналого-цифрового преобразования и третьим входом блока поиска и синхронизации по задержке, второй вход блока аналого-цифрового преобразования соединен с выходом усилителя, а первый и второй выходы соединены с первыми входами соответствующих регистров-дециматоров и четвертым и пятым входами блока поиска и синхронизации по задержке соответственно, третий выход блока поиска и синхронизации по задержке соединен с тактовыми входами генератора ПСП, регистров-дециматоров, блоков перестановки отсчетов, блоков преобразования Уолша и блоков выбора максимума, входы синхронизации блока выбора максимума объединены со входами синхронизации блоков преобразования Уолша, блоков перестановки отсчетов и подключены ко второму выходу блока поиска и синхронизации по задержке; кроме того, выход каждого регистра-дециматора соединен с первым входом умножителя каждого из подканалов в синфазном и квадратурном каналах, а вторые входы умножителей каждого из подканалов в синфазном и квадратурном каналах объединены и соединены с третьим и четвертым выходами генератора ПСП соответственно.

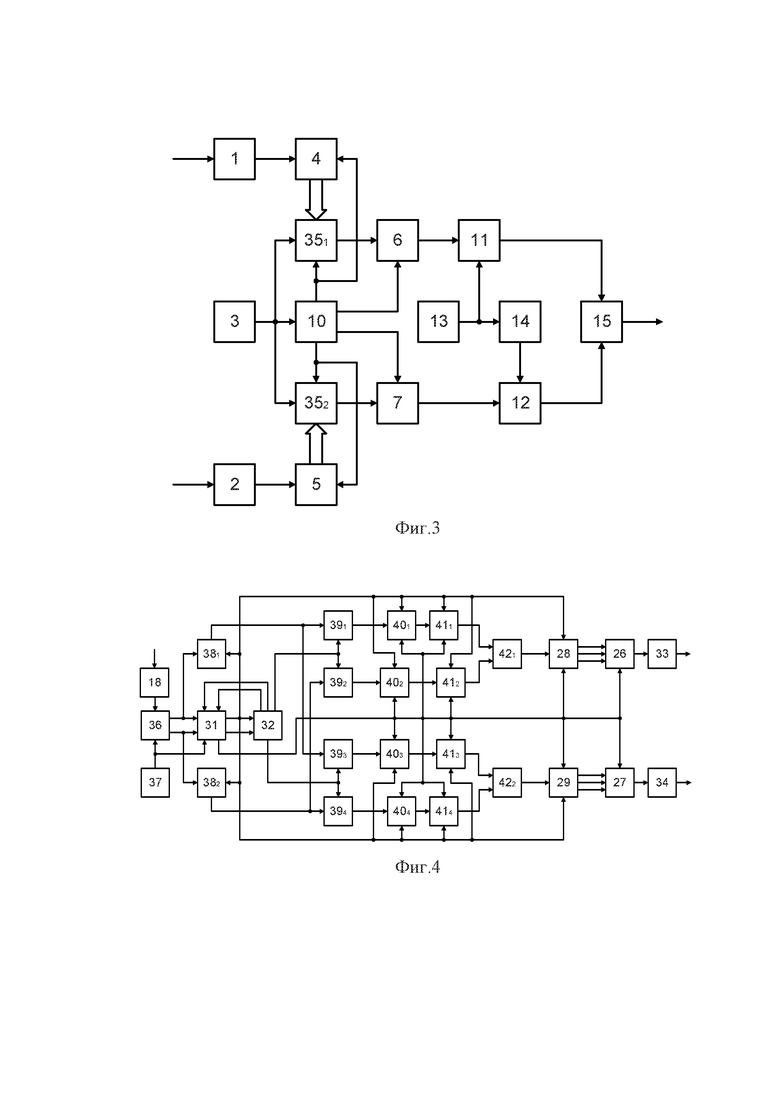

Заявляемое устройство содержит формирующую и обрабатывающую части, функциональные схемы которых приведены на фиг. 3 и фиг. 4 соответственно.

На фиг. 3 приняты следующие обозначения:

1, 2 – кодеры (КД);

3 – генератор чиповой частоты (ГЧЧ);

4, 5 – последовательно-параллельные преобразователи (ПР);

6, 7, 11, 12 – модуляторы (МД);

35, 35 – генераторы М-последовательностей (Г);

10 – генератор псевдослучайной последовательности (ГПСП);

13 – генератор несущей частоты (ГНЧ);

14 – фазовращатель (Ф);

15 – суммирующий усилитель (СУ).

На фиг. 4 приняты следующие обозначения:

18 – усилитель (У);

26, 27 – параллельно-последовательные преобразователи (ПР);

28, 29 – блоки выбора максимума (БВМ);

31 – блок поиска и синхронизации по задержке (БПС);

32 – генератор ПСП (ГПСП);

33, 34 – декодеры (ДК);

36 – блок аналого-цифрового преобразования (БАЦП);

37 – генератор частоты дискретизации (ГЧД);

381, 382 – регистр-дециматор (РД);

391, 392, 393, 394 – умножители (УМ);

401, 402, 403, 404 – блоки перестановки отсчетов (БПО);

411, 412, 413, 414 – блоки преобразования Уолша (БПУ);

421, 422 – блоки объединения квадратур (БОК).

В состав формирующей части устройства (фиг. 3) входят генератор чиповой частоты (ГЧЧ) 3, генератор псевдослучайной последовательности (ГПСП) 10, генератор несущей частоты (ГНЧ) 13, фазовращатель (Ф) 14, суммирующий усилитель (СУ) 15, выход которого является выходом формирующей части устройства,

синфазный и квадратурный каналы, выполненные идентично, в состав которых входят кодеры (КД) КД 1 и КД 2, входы которых являются входами формирующей части устройства, последовательно-параллельные преобразователи (ПР) ПР 4 и ПР 5, входы которых соединены с выходами КД 1 и КД 2 соответственно, последовательно соединенные генератор М-последовательностей (Г) Г 35, первый и второй модуляторы (МД) МД 6, МД 11, и МД 7, МД 12 синфазного и квадратурного каналов соответственно,

кроме того, выход ГЧЧ 3 соединен с тактовыми входами ГПСП 10, Г 351 и Г 352, первый и второй выходы ГПСП 10 соединены со вторыми входами МД 6 и МД 7, а управляющие выходы соединены с входами разрешения записи начального состояния Г 351 и Г 352 и со считывающими входами последовательно-параллельных преобразователей ПР 4 и ПР 5,

кроме того, выход ГНЧ 13 соединен со вторым входом МД 11 и через Ф 14 – со вторым входом МД 12, а выходы МД 11 и МД 12 соединены с первым и вторым входами СУ 15.

В состав обрабатывающей части устройства (фиг. 4) входят усилитель (У) 18, вход которой является входом обрабатывающей части устройства, последовательно соединенные блок поиска и синхронизации по задержке (БПС) 31 и генератор ПСП (ГПСП) 32, первый и второй выходы которого соединены с первым и вторым входами БПС 31, блок аналого-цифрового преобразования (БАЦП) 36, генератор частоты дискретизации (ГЧД) 37, два регистра-дециматора (РД) 381 и 382;

также, обрабатывающая часть устройства содержит синфазный и квадратурный каналы, выполненные идентично, в состав которых входят последовательно соединенные блок объединения квадратур (БОК) 42, блок выбора максимума (БВМ) (БВМ 28 и БВМ 29 синфазного и квадратурного каналов соответственно), параллельно-последовательный преобразователь (ПР) (ПР 26 и ПР 27 синфазного и квадратурного каналов соответственно) и декодер (Д) (Д 33 и Д 34 синфазного и квадратурного каналов соответственно), причем выходы Д 33 и Д 34 являются выходами информационного сигнала обрабатывающей части устройства; кроме того, в каждом из каналов содержится два идентичных подканала, в состав которых входят последовательно соединенные умножитель (УМ) 39, блок перестановки отсчетов (БПО) 40 и блок преобразования Уолша (БПУ) 41 соответственно;

причем первый и второй входы БОК 421 и БОК 422 соединены с выходами БПУ 411, БПУ 412 и БПУ 413, БПУ 414 синфазного и квадратурного каналов соответственно, выход ГЧД 37 соединен с первым входом БАЦП 36 и третьим входом БПС 31, второй вход БАЦП 36 соединен с выходом У 18, а первый и второй выходы соединены с первыми входами РД 381, РД 382, четвертым и пятым входами БПС 31 соответственно, второй выход БПС 31 соединен с входами синхронизации БВМ 28 и БВМ 29, БПО 401, БПО 402, БПО 403, БПО 404, БПУ 411, БПУ 412, БПУ 413, БПУ 414 и с управляющими входами ПР 26 и ПР 27, третий выход БПС 31 соединен с тактовыми входами ГПСП 32, РД 381, РД 382, БПО 401, БПО 402, БПО 403, БПО 404, БПУ 411, БПУ 412, БПУ 413, БПУ 414, БВМ 28 и БВМ 29; выходы РД 381 и РД 382 соединены с первым входом УМ 391, УМ 393 и УМ 392, УМ 394 в синфазном и квадратурном каналах соответственно, а вторые входы УМ 391 и УМ 392, УМ 393 и УМ 394 объединены и соединены с третьим и четвертым выходами ГПСП 32 соответственно.

Заявляемое устройство работает следующим образом.

В формирующей части устройства информационные данные могут поступать на входы КД 1 и КД 4 от двух независимых источников информации или от одного с разделением по времени. Назначение КД 1 и КД 4 и в данном устройстве, и в прототипе – выдавать информацию пакетами, причем пакет выдается за время, равное длительности периода повторения М-последовательности, формируемой Г 351 и Г 352. Пакет должен содержать количество бит информации, не превышающее длину регистра Г 351 и Г 352. Каждый пакет с выходов КД 1 и КД 4 подается на входы ПР 4 и ПР 5, где преобразовывается в параллельный код, поступающий на входы начальной установки Г 351 и Г 352.

ГЧЧ 3 формирует тактовую частоту для ГПСП 10, Г 351 и Г 352. По сигналу синхронизации КД 1 и КД 4 начинают выдавать очередные пакеты информации, ПР 4 и ПР 5 обновляют информацию на выходе, осуществляется установка начального состояния (параллельная запись информации) в Г 351 и Г 352 и установка фиксированного начального состояния ГПСП 10.

Далее Г 351 и Г 352 начинают формирование М-последовательностей, а ГПСП 10 начинает формирование ПСП, тактируемое сигналом с выхода ГЧЧ 3. Формируемые М-последовательности поступают на вторые входы МД 6 и МД 7, формируемые ПСП поступают на первые входы МД 6 и МД 7. Основное требование к формированию ПСП и М-последовательностей – соблюдение их квазиортогональности.

Затем сигналы с выходов МД 6 и МД 7 подаются на входы МД 11 и МД 12 соответственно, причем на второй вход МД 11 поступает периодический сигнал несущей (промежуточной) частоты с выхода ГНЧ 13, а на второй вход МД 12 с выхода Ф 14 поступает такой же сигнал, но сдвинутый по фазе на 90°. МД 11 и МД 12 осуществляют манипуляции фазы радиочастотных сигналов на 180°.

Выходные сигналы МД 11 и МД 12 складываются и усиливаются в СУ 15, с выхода которого поступают на следующие узлы передатчика, а затем излучаются.

В обрабатывающей части устройства входной сигнал поступает на У 18. Возможно наличие предшествующих У 18 каскадов приемника, которые могут осуществлять дополнительные операции: усиление, частотную селекцию и преобразование частоты. В функции У 18, помимо усиления, может входить и автоматическая регулировка уровня сигнала для более эффективной работы последующих АЦП.

С выхода У 18 сигнал поступает на вход БАЦП 36, на другой вход которого поступают периодические сигналы с ГЧД 37.

БАЦП 36 преобразовывает сигналы в цифровую форму, т.е. производит их дискретизацию с частотой, в целое число раз превышающей тактовую частоту ПСП. Полученные отсчеты квадратурных огибающих с выхода БАЦП 36 поступают на входы БПС 31 и входы РД 381 и РД 382 соответственно.

БПС 31 осуществляет синхронизацию ГПСП 32 с принимаемым сигналом и подстройку по тактовой частоте ПСП. Для реализации синхронизации и подстройки в передаваемую информацию периодически вставляется группа пакетов информации, состоящих из одних логических нулей. В этом случае сигнал становится детерминированным, изменяющимся по закону периодически повторяющейся ПСП.

Также БПС 31 формирует из сигнала ГЧД 37 импульсы тактовой (чиповой) частоты ПСП, наиболее близко расположенные к середине элементов принимаемых ПСП, и осуществляет их деление на число, равное числу элементов ПСП таким образом, что при установке поделенными импульсами ГПСП 32 в начальное состояние он формирует ПСП, совпадающие по задержке с принимаемыми. Импульсы тактовой (чиповой) частоты с выхода БПС 31 поступают на тактовые входы РД 381 и РД 382, где осуществляется децимация отсчетов квадратурных огибающих до одного отсчета на элементе ПСП.

С выходов РД 381 и РД 382 полученные потоки данных поступают в синфазный и квадратурный каналы обработки цифровых данных, где в умножителях УМ 39 перемножаются с ПСП, поступающей с выходов ГПСП 32. В результате перемножения изменяется знак данных в случае, если элемент ПСП равен логической "1", в противном случае данные не изменяются. С выходов умножителей данные поступают в соответствующие блоки перестановки отсчетов БПО 40.

В БПО 40 данные записываются в оперативное запоминающее устройство в одной системе адресации, а затем считываются в другой системе адресации. Суть этих перестановок – преобразовать отсчеты М-последовательностей в отсчеты функций Уолша для того, чтобы вместо вычисления корреляционных сверток воспользоваться быстрым преобразованием Уолша.

После перестановки данные поступают в БПУ 41, где происходит формирование и вывод последовательности преобразованных данных, соответствующих значениям сверток с М-последовательностью. При этом текущий номер данного в двоичном представлении соответствует возможному передаваемому пакету информации.

Далее преобразованные данные с выходов БПУ 41 синфазного и квадратурного каналов соответственно поступают в БОК 42, где вычисляются суммы квадратов модулей данных. Возможна замена этой операции на суммирование модулей данных или суммирование модулей с коэффициентами, различающимися для большего и меньшего по значению.

Результирующие данные с выходов БОК 42 поступают в БВМ 28 и БВМ 29 соответственно, где определяются номера наибольшего по значению данного, соответствующего передаваемому пакету информации. Полученные номера пересылаются в ПР 26 и ПР 27, где преобразуются в двоичные последовательности.

Далее двоичные последовательности данных поступают в ДК 33 и ДК 34, где осуществляется дальнейшее преобразование принимаемой информации для выдачи ее получателю.

Для доказательства реализуемости изобретения рассмотрим математическое описание процессов формирования и обработки сигналов в заявляемом устройстве.

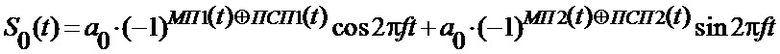

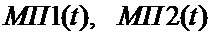

Сигнал, формируемый в передатчике, имеет следующий вид:

где a0 – амплитуда сигнала;

f – несущая (промежуточная) частота;

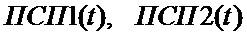

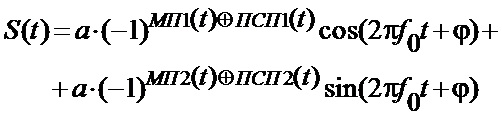

Входной сигнал усилителя имеет вид:

где f0 – промежуточная частота.

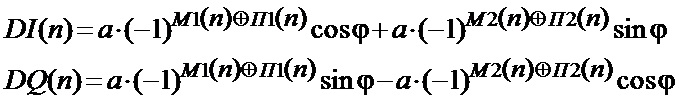

После блока аналого-цифрового преобразования и регистров-дециматоров сигналы имеют следующий вид:

где

τ – длительность периода чиповой частоты.

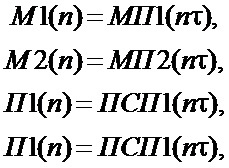

Далее рассмотрим работу одного из каналов обработки цифровых данных. После умножителей сигналы имеют следующий вид:

Если передаваемые пакеты информации интерпретировать как двоичное представление чисел

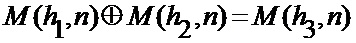

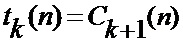

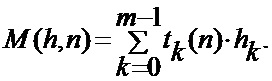

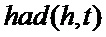

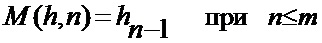

и учесть, что это начальные состояния генератора М-последовательности, то можно говорить о множестве последовательностей M(h, n) объемом 2m, причем

M(0, n) = 0,

M(h, n) = hn-1 при n ≤ m.

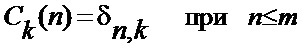

Для всех

при

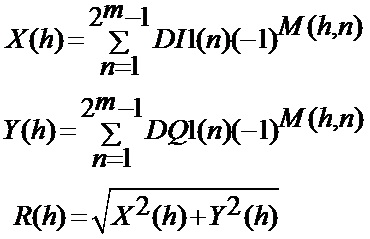

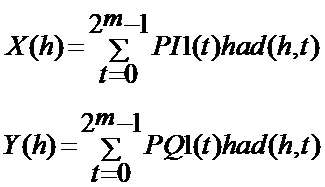

Правило оптимального различения сигналов с неизвестной фазой несущей частоты включает в себя вычисления следующего вида:

и далее определение h с максимальным значением R(h).

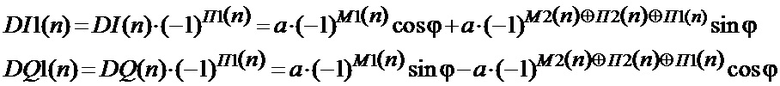

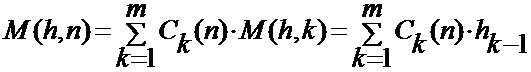

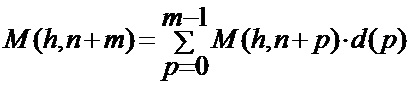

Вместо непосредственного вычисления X(h) и Y(h) используется перестановка данных DI1(n) и DQ1(n) и преобразование Уолша. Определим закон перестановки. В силу рекуррентных свойств М-последовательности

Далее рассмотрим последовательность чисел t(n), имеющих двоичное представление

Тогда:

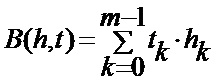

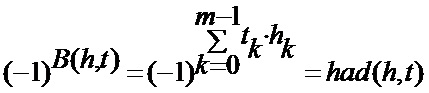

Таким образом, в результате перестановки n→t(n) образуется последовательность

а это означает, что

где

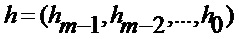

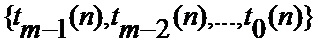

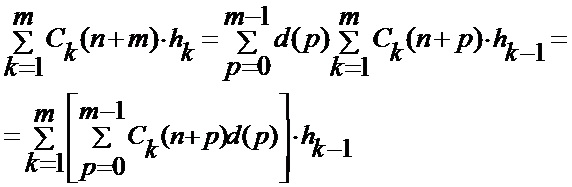

Рассмотрим более детально закон перестановки n→t(n). Задавая М-последовательность уравнением вида:

и подставляя в (8), получим:

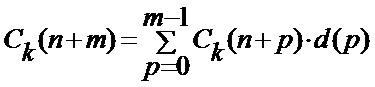

Поскольку (13) выполняется для произвольных h, то

т.е. все последовательности Ck(n) являются циклическими сдвигами исходной М-последовательности.

Определим их начальные состояния. Поскольку

то

где

Рассмотрим генератор М-последовательности, выполненный по схеме со встроенными сумматорами. Если задать ему начальное состояние {1, 0, 0, …, 0}, то на выходах его разрядов будут формироваться последовательности {С1(n), С2(n), …, Сm(n)}, соответствующие последовательностям {t0(n), t1(n), …, tm-1(n)}, т.е. его можно использовать в качестве формирователя адресов перестановок отсчетов n→t(n).

Возвращаясь к вычислению X(h) и Y(h) (7), можно увидеть, что если обозначить переставленные по закону n→t(n) последовательности отсчетов DI1(n) и DQ1(n) как PI1(t) и PQ1(t) и доопределить их при t=0, приняв PI1(0) = PQ1(0) = 0, то

т.е. вычисление X(h) и Y(h) сводится к преобразованию Уолша, а номер h функций Уолша-Адамара соответствует передаваемому символу информации.

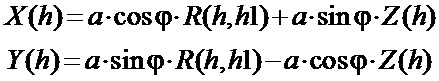

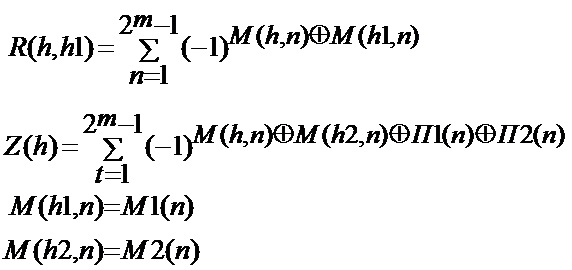

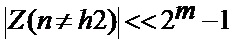

Рассмотрим взаимное влияние двух каналов передачи информации. Из (5) и (7) следует

где

Видно, что R(h, h1) – функция корреляции М-последовательности, равная 2m-1 при h = h1 и равная -1 в остальных случаях.

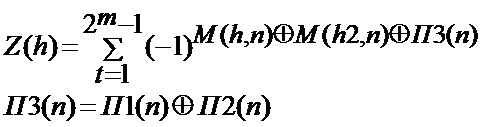

Вторые слагаемые являются взаимными помехами. Для того, чтобы оценить их уровень, будем считать, что П(n) – тоже М-последовательность, обладающая свойством (6). В этом случае:

где П3(n) – циклически сдвинутая последовательность П1(n).

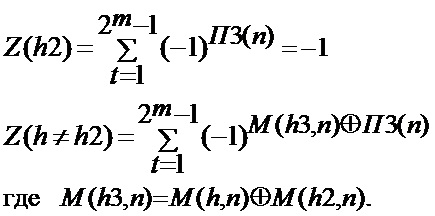

После преобразования (20) получаем

В силу квазиортогональности последовательностей

Таким образом, взаимное влияние двух каналов передачи информации определяется взаимокорреляционными свойствами используемых последовательностей и может быть сделано пренебрежимо малым.

РЕАЛИЗАЦИЯ

Блоки формирующей и обрабатывающей части устройства могут быть реализованы на базе зарубежных и отечественных изделий микроэлектроники.

В частности, МД 6, МД 7, МД 11 и МД 12 могут быть реализованы как сумматоры по модулю 2 на основе элементов цифровой логики, если в устройстве используются цифровые сигналы. Кроме того, МД 11 и МД 12 могут быть реализованы на базе аналоговых перемножителей. БПС 31 может быть реализован на основе известных технических решений, принцип действия которых описан, например, в [2, 3].

Блок БАЦП может быть реализован разными способами.

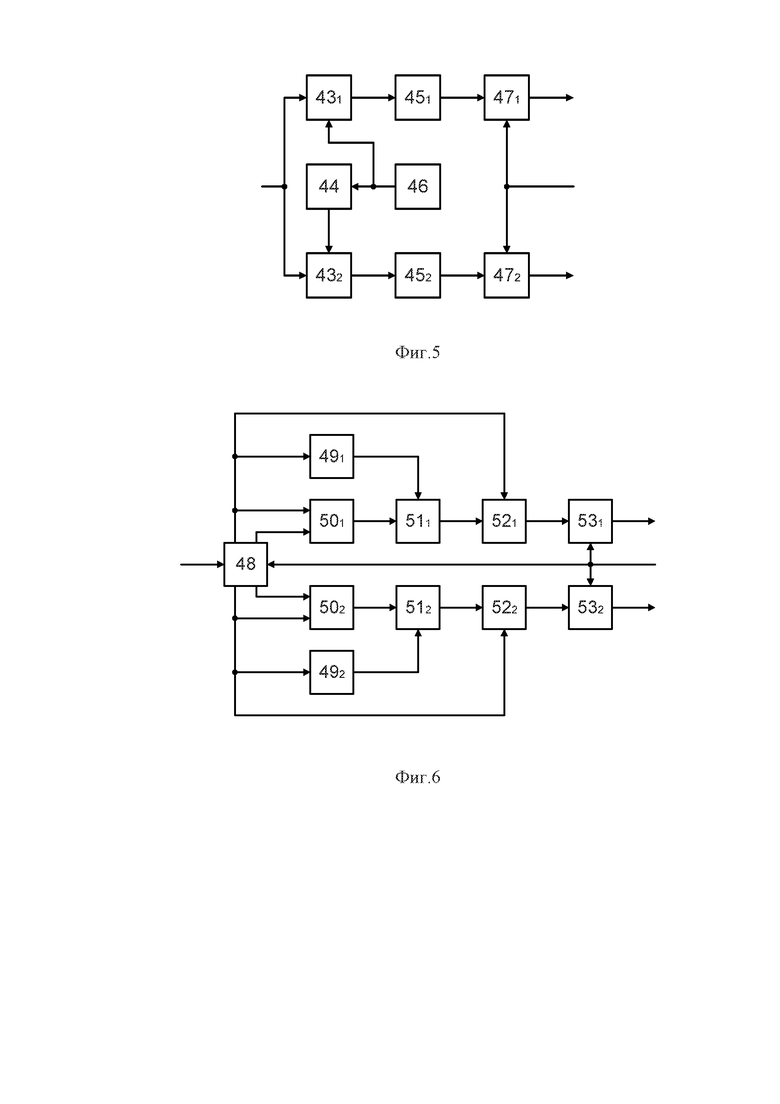

Функциональная схема одного из способов реализации БАЦП представлена на фиг. 5, где приняты следующие обозначения:

431, 432 – перемножители (П);

44 – фазовращатель (Ф);

451, 452 – фильтры нижних частот (ФНЧ);

46 – генератор промежуточной частоты (ГПЧ);

471, 472 – аналого-цифровые преобразователи (АЦП).

Устройство на фиг. 5 содержит два идентичных канала, в состав каждого из которых входят последовательно соединенные перемножитель (П) 43, фильтр нижних частот (Ф) 45 и аналого-цифровой преобразователь (АЦП) 47, выход которого является выходом БАЦП; устройство также содержит последовательно соединенные генератор промежуточной частоты (ГПЧ) 46 и фазовращатель (Ф) 44 на 90°, выход которого соединен с первым входом П 431, а первый вход П 432 подключен к выходу ГПЧ 46, вторые входы АЦП 471 и АЦП 472 объединены и являются вторым входом БАЦП, первым входом которого являются объединенные вторые входы П 431 и П 432.

Функциональная схема следующего способа реализации БАЦП представлена на фиг. 6, где приняты следующие обозначения:

48 – аналого-цифровой преобразователь (АЦП);

491, 492 – делитель частоты на два (ДЧ);

501, 502 – регистры (Р);

511, 512 – умножители (УМ);

521, 522 – коммутаторы (КМ);

531, 532 – фильтры нижних частот (ФНЧ).

Устройство на фиг. 6 содержит два идентичных канала, в состав каждого из которых входят делитель частоты на два (ДЧ) 49 и последовательно соединенные регистр (Р) 50, умножитель (УМ) 51, коммутатор (КМ) 52 и фильтр нижних частот (ФНЧ) 53, выход которого является выходом БАЦП, причем второй вход УМ 51 соединен с выходом ДЧ 49, вход которого объединен с управляющим входом КМ 52 и тактовым входом Р 50; устройство также содержит АЦП 48, первый вход которого является первым входом БАЦП и объединен со вторыми входами ФНЧ 53, а вторым входом БАЦП является второй вход АЦП 48; кроме того, выход четных выборок АЦП 48 подключен ко входу одного из Р 50, тактовый вход которого соединен с выходом тактовых импульсов четных выборок АЦП 48, а выход нечетных выборок АЦП 48 подключен ко входу другого Р 50, тактовый вход которого соединен с выходом тактовых импульсов нечетных выборок АЦП 48.

Таким образом, совокупность введенных в предлагаемом устройстве новых блоков и их связей позволяет осуществить техническую реализацию устройства формирования и обработки широкополосных сигналов с возможностью работы с сигналами с большой базой (длиной ПСП).

Источники информации:

1. Патент РФ №2221344. Устройство передачи и приема дискретной информации с использованием широкополосных шумоподобных сигналов при кодовом разделении каналов: МПК H04J 13/02 / В.Я. Архипкин (RU), К.А. Мешковский (RU), ОУНГ Да-Минг (TW), А.Г. Соколов (RU); заявитель и патентообладатель ООО «Кедах Электроникс Инжиниринг» (RU). №2001134590/09, заявл. 24.12.2001, опубл. 10.01.2004, Бюл. №1.

2. Борисов В.И., Зинчук В.М., Лимарев А.Е., Мухин Н.П., Нахмансон Г.С. Помехозащищенность систем радиосвязи с расширением спектра сигналов модуляцией несущей псевдослучайной последовательностью. М.: Радио и связь, 2003. 640 с.

3. Павлов, Б.А. «Синхронный прием»: М.: «Энергия», 1997. – 82 с.

| название | год | авторы | номер документа |

|---|---|---|---|

| Способ передачи информации в системе связи с широкополосными сигналами | 2019 |

|

RU2696021C1 |

| УСТРОЙСТВО СИНХРОНИЗАЦИИ М-ПОСЛЕДОВАТЕЛЬНОСТИ | 1985 |

|

SU1840079A1 |

| УСТРОЙСТВО ПЕРЕДАЧИ И ПРИЕМА ДИСКРЕТНОЙ ИНФОРМАЦИИ С ИСПОЛЬЗОВАНИЕМ ШИРОКОПОЛОСНЫХ ШУМОПОДОБНЫХ СИГНАЛОВ ПРИ КОДОВОМ РАЗДЕЛЕНИИ КАНАЛОВ | 2001 |

|

RU2221344C2 |

| УСТРОЙСТВО СИНХРОНИЗАЦИИ М-ПОСЛЕДОВАТЕЛЬНОСТИ | 1983 |

|

SU1840196A1 |

| ЛИНИЯ РАДИОСВЯЗИ С ПОВЫШЕННОЙ СКРЫТНОСТЬЮ ПЕРЕДАВАЕМОЙ ИНФОРМАЦИИ | 2003 |

|

RU2252485C1 |

| УСТРОЙСТВО СИНХРОНИЗАЦИИ М-ПОСЛЕДОВАТЕЛЬНОСТИ | 1984 |

|

SU1840075A1 |

| Приемное устройство широкополосных сигналов | 2021 |

|

RU2768249C1 |

| АППАРАТУРА ДЛЯ ПЕРЕДАЧИ ДИСКРЕТНОЙ ИНФОРМАЦИИ, УСТОЙЧИВАЯ К ВОЗДЕЙСТВИЮ МОЩНОЙ ЧМ ПОМЕХИ | 2001 |

|

RU2205506C1 |

| АСИНХРОННАЯ СИСТЕМА СВЯЗИ С ШИРОКОПОЛОСНЫМИ СИГНАЛАМИ | 1995 |

|

RU2127022C1 |

| ИМИТАТОР НАВИГАЦИОННЫХ РАДИОСИГНАЛОВ | 2018 |

|

RU2697811C2 |

Изобретение относится к помехозащищенным системам радиосвязи, использующим шумоподобные фазоманипулированные сигналы, и может найти применение в помехозащищенных системах радиосвязи. Достигаемый технический результат - возможность формировать и обрабатывать сигналы, объем алфавита и база которых измеряются тысячами единиц. Устройство формирования и обработки широкополосных сигналов содержит формирующую и обрабатывающую части. В состав формирующей части устройства входят два идентичных канала, содержащие кодер, последовательно-параллельный преобразователь, генератор М-последовательности и два модулятора. Кроме того, формирующая часть устройства содержит: генератор чиповой частоты, генератор ПСП, генератор несущей частоты, фазовращатель на 90° и суммирующий усилитель. В состав обрабатывающей части входят два идентичных канала, содержащие блок объединения квадратур, блок выбора максимума, параллельно-последовательный преобразователь, декодер и два идентичных подканала, содержащие умножитель, блок перестановки отсчетов и блок преобразования Уолша. Кроме того, обрабатывающая часть устройства содержит: усилитель, блок аналого-цифрового преобразования, имеющий два варианта исполнения, два регистра-дециматора, генератор частоты дискретизации, генератор ПСП и блок поиска и синхронизации. 2 з.п. ф-лы, 6 ил.

1. Устройство формирования и обработки широкополосных сигналов, содержащее в формирующей части синфазный и квадратурный каналы, выполненные идентично, в состав каждого из которых входят последовательно соединенные кодер и последовательно-параллельный преобразователь, причем вход кодера является входом информационного сигнала, последовательно соединенные первый и второй модуляторы; а также содержащее последовательно соединенные генератор чиповой частоты и генератор псевдослучайной последовательности (ПСП), управляющие выходы которого подключены к соответствующим считывающим входам последовательно-параллельных преобразователей синфазного и квадратурного каналов, последовательно соединенные генератор несущей частоты и фазовращатель на 90°, причем выход генератора несущей частоты соединен со вторым входом второго модулятора синфазного канала, а выход фазовращателя соединен со вторым входом второго модулятора квадратурного канала; суммирующий усилитель, первый и второй входы которого соединены с выходами вторых модуляторов, а выход является выходом формирующей части устройства;

содержащее в обрабатывающей части синфазный и квадратурный каналы, выполненные идентично, в состав каждого из которых входят блок выбора максимума, параллельно-последовательный преобразователь и декодер, выход которого является выходом информационного сигнала, а вход соединен с выходом параллельно-последовательного преобразователя; выходы блока выбора максимума являются входами параллельно-последовательного преобразователя; также содержащее усилитель, вход которого является входом обрабатывающей части устройства, последовательно соединенные блок поиска и синхронизации по задержке и генератор ПСП, первый и второй выходы которого соединены с первым и вторым входами блока поиска и синхронизации по задержке, второй выход которого соединен с входами синхронизации блоков выбора максимума и с управляющими входами параллельно-последовательных преобразователей;

отличающееся тем, что в формирующей части в состав синфазного и квадратурного каналов введен генератор М-последовательности, у которого входы записи начального состояния соединены с выходами последовательно-параллельного преобразователя, вход разрешения записи начального состояния объединен со считывающим входом последовательно-параллельного преобразователя, а выход соединен с первым входом первого модулятора, причем тактовые входы генераторов М-последовательности подключены к выходу генератора чиповой частоты, а вторые входы первых модуляторов синфазного и квадратурного каналов соединены с первым и вторым выходами генератора ПСП, в обрабатывающей части в состав синфазного и квадратурного каналов введены два идентичных подканала, состоящих из последовательно соединенных умножителя, блока перестановки отсчетов и блока преобразования Уолша, блок объединения квадратур, выход которого соединен с входом блока выбора максимума, а первый и второй входы соединены со выходами блоков преобразования Уолша синфазного и квадратурного каналов, также введены генератор частоты дискретизации, блок аналого-цифрового преобразования и два регистра-дециматора, причем выход генератора частоты дискретизации соединен с первым входом блока аналого-цифрового преобразования и третьим входом блока поиска и синхронизации по задержке, второй вход блока аналого-цифрового преобразования соединен с выходом усилителя, а первый и второй выходы соединены с первыми входами соответствующих регистров-дециматоров и четвертым и пятым входами блока поиска и синхронизации по задержке соответственно, третий выход блока поиска и синхронизации по задержке соединен с тактовыми входами генератора ПСП, регистров-дециматоров, блоков перестановки отсчетов, блоков преобразования Уолша и блоков выбора максимума, входы синхронизации блока выбора максимума объединены со входами синхронизации блоков преобразования Уолша, блоков перестановки отсчетов и подключены ко второму выходу блока поиска и синхронизации по задержке; кроме того, выход каждого регистра-дециматора соединен с первым входом умножителя каждого из подканалов в синфазном и квадратурном каналах, а вторые входы умножителей каждого из подканалов в синфазном и квадратурном каналах объединены и соединены с третьим и четвертым выходами генератора ПСП соответственно.

2. Устройство по п. 1, отличающееся тем, что блок аналого-цифрового преобразования содержит два идентичных канала, в состав каждого из которых входят последовательно соединенные перемножитель, фильтр нижних частот и аналого-цифровой преобразователь (АЦП), выход которого является выходом блока аналого-цифрового преобразования; а также содержит последовательно соединенные генератор промежуточной частоты и фазовращатель на 90°, выход которого соединен с первым входом одного из перемножителей, а первый вход другого перемножителя подключен к выходу генератора промежуточной частоты, вторые входы АЦП объединены и являются вторым входом блока аналого-цифрового преобразования, первым входом которого являются объединенные вторые входы перемножителей.

3. Устройство по п. 1, отличающееся тем, что блок аналого-цифрового преобразования содержит два идентичных канала, в состав каждого из которых входят делитель частоты на два и последовательно соединенные регистр, умножитель, коммутатор и фильтр нижних частот, выход которого является выходом блока аналого-цифрового преобразования, причем второй вход умножителя соединен с выходом делителя частоты на два, вход которого объединен с управляющим входом коммутатора и тактовым входом регистра, а также содержит АЦП, первый вход которого объединен со вторыми входами фильтров нижних частот и является первым входом блока аналого-цифрового преобразования, вторым входом которого является второй вход АЦП, кроме того, выход четных выборок АЦП подключен к входу одного из регистров, тактовый вход которого соединен с выходом тактовых импульсов четных выборок АЦП, а выход нечетных выборок АЦП подключен к входу второго регистра, тактовый вход которого соединен с выходом тактовых импульсов нечетных выборок АЦП.

| УСТРОЙСТВО ПЕРЕДАЧИ И ПРИЕМА ДИСКРЕТНОЙ ИНФОРМАЦИИ С ИСПОЛЬЗОВАНИЕМ ШИРОКОПОЛОСНЫХ ШУМОПОДОБНЫХ СИГНАЛОВ ПРИ КОДОВОМ РАЗДЕЛЕНИИ КАНАЛОВ | 2001 |

|

RU2221344C2 |

| КВАДРАТУРНОЕ МУЛЬТИПЛЕКСИРОВАНИЕ ДВУХ СИГНАЛОВ ДАННЫХ, РАСШИРЕННЫХ ПОСРЕДСТВОМ РАЗЛИЧНЫХ PN-ПОСЛЕДОВАТЕЛЬНОСТЕЙ | 1994 |

|

RU2120189C1 |

| US 6215777 B1, 10.04.2001 | |||

| Электрическая сигнальная установка для обнаружения хода рыбы | 1947 |

|

SU76186A1 |

| SU 1827053 A3, 07.07.1993. | |||

Авторы

Даты

2019-06-18—Публикация

2018-10-15—Подача