fc2r.ii 01

О

3150

Изобретение относится к электроизмерительной технике и может быть использовано для контроля работоспособности и определения типа цифровых металлоксиднополупроводниковых (МОП) интегральных микросхем при производстве радиоэлектронной аппаратуры. Цель изобретения - расширение функциональных возможностей достига- ется за счет контроля микросхем с запоминанием состояния.

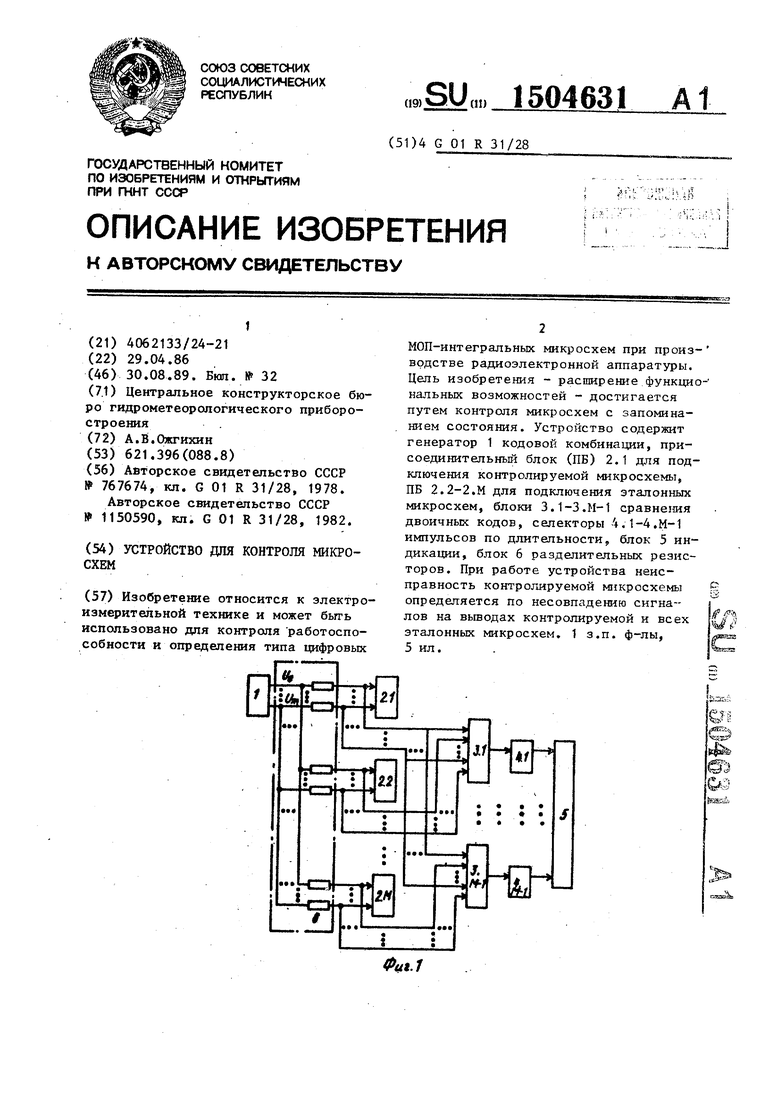

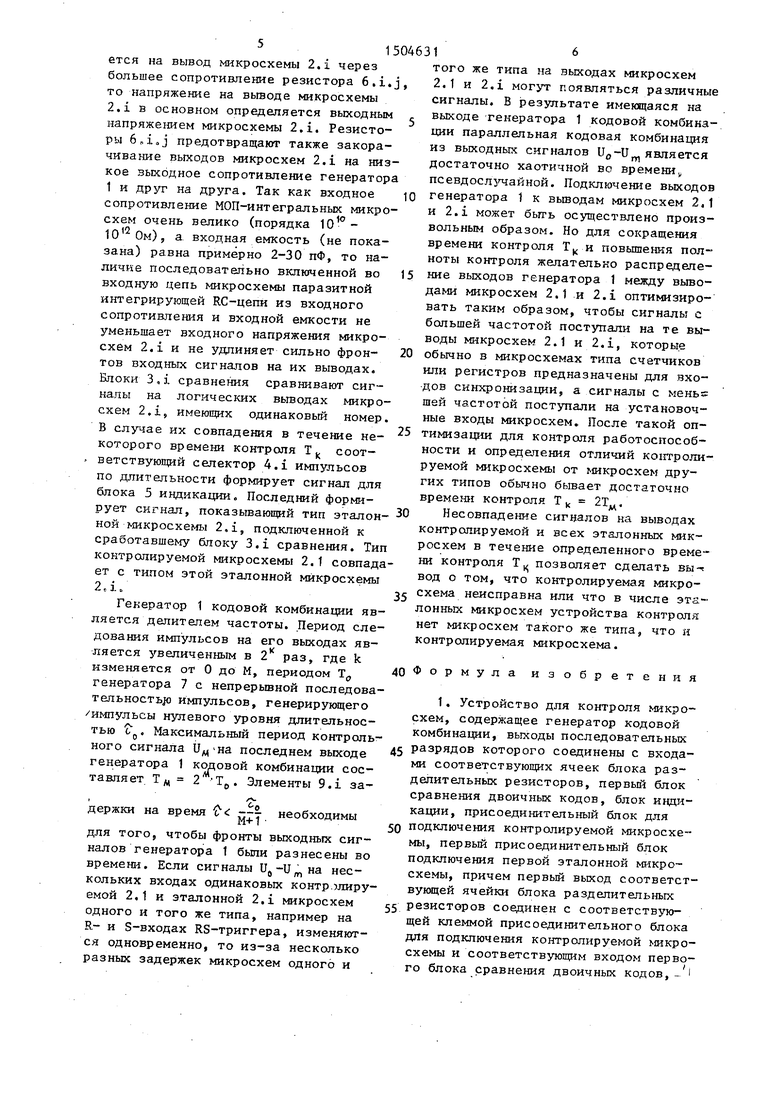

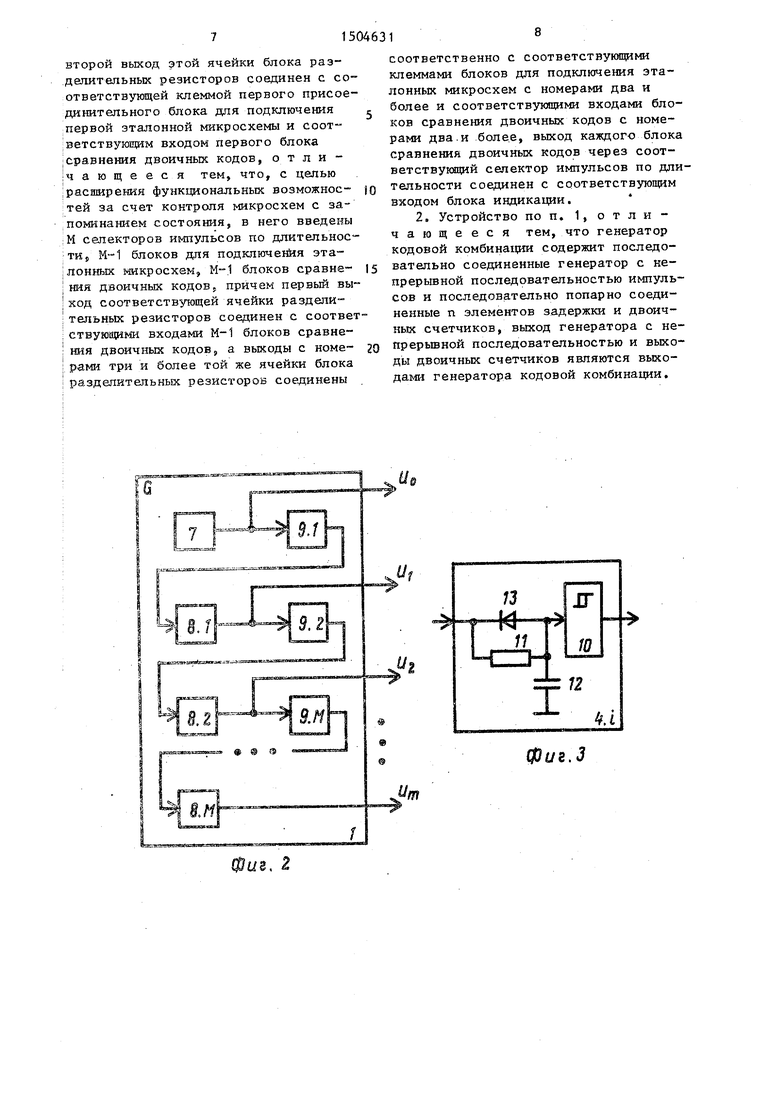

На фиг. 1 изображена функциональная электрическая схема устройстваj на фиг. 2 - функциональная электри- ческая схема генератора кодовой ком бинации; на фиг. 3 - функциональная электрическая схема селектора импульсов по длительностиJ на фиг, 4 эквивалентная электрическая схема сое- динения генератора с контролируемой или эталонной микросхемой; на фиг. 5 временные диаграммы работы генератора кодовой комбинации,

Устройство для контроля микросхем содержит генератор 1 кодовой комбинации, присоединительный блок 2,1 для подключения контролируемой микросхемы, присоединительные блоки ,2,2-2.М для подключения эталонных микросхем блоки 3.1-З.М-Т сравнения двоичных кодов, селекторы 4., импульсов по длительности5 блок 5 индикации, блок 6 разделительных резисторов, причем выходы последовательных раз рядов генератора 1 кодовой комбинации соединены, с входами соответствующих ячеек блока 6 разделительных резисторов, соответству}ощие выходы ячеек блока 6 разделительных резисторов

соединены с соответствующими входами присоединительного блока 2.1 для подключения контролируемой микросхемы, присоединительных блоков 2..М для подключения эталонных микросхем бло ков 3.1-З.М-1 сравнения двоичных ко- дов, выход каждого блока 3,,М-1 сравнения двоичных кодов через соот- ветствукяций селектор 4.1-4.М-1 импульсов по длительности соединен с соответствуюп|ям входом блока 5 индикации ,

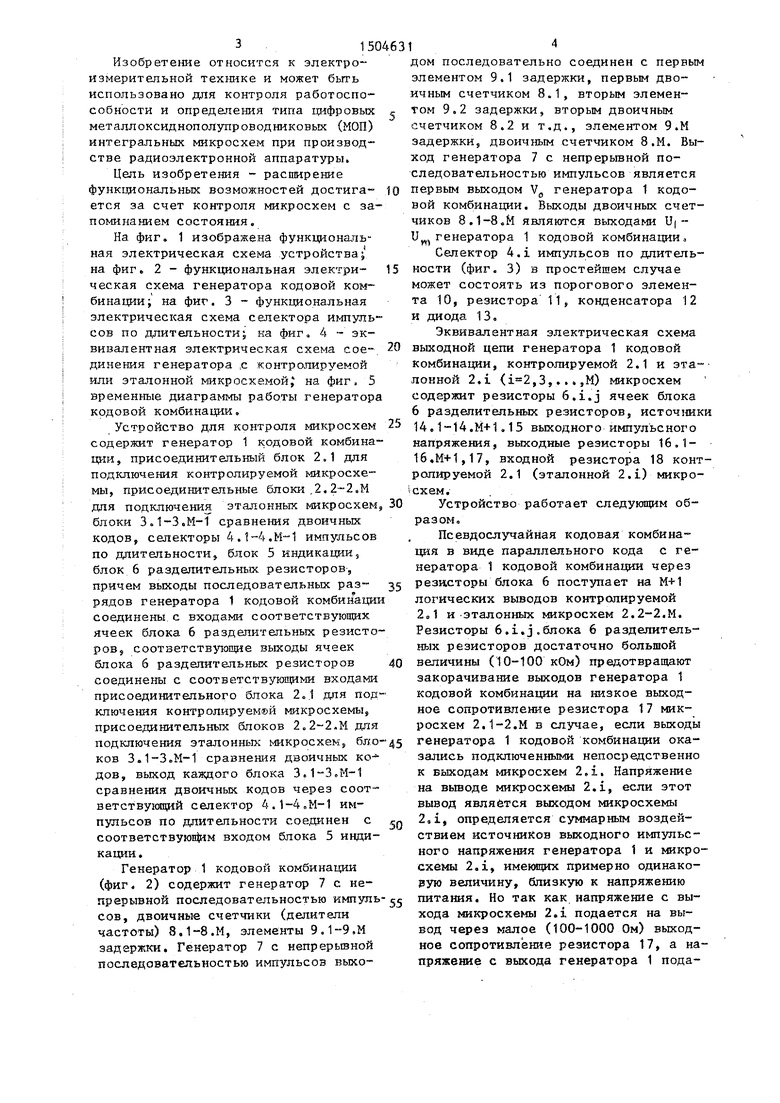

Генератор 1 кодовой комбинации (фиг. 2) содержит генератор 7 с непрерывной последовательностью импуль сов, двоичные счетчики (делители частоты) 8.1-8.М, элементы 9,1-9.М задержки. Генератор 7 с непрерьюной последовательностью импульсов выхо1

дом последовательно соединен с первым элементом 9.1 задержки, первым двоичным счетчиком 8.1, вторым элементом 9.2 задержки, вторым двоичным счетчиком 8.2 и т.д., элементом 9.М задержки, двоичным счетчиком 8.М. Выход генератора 7 с непрерьганой последовательностью импульсов является первым выходом Vg генератора 1 кодовой комбинации. Выходы двоичных счетчиков 8,1-8.И являются выходами U|- и генератора 1 кодовой комбинации,

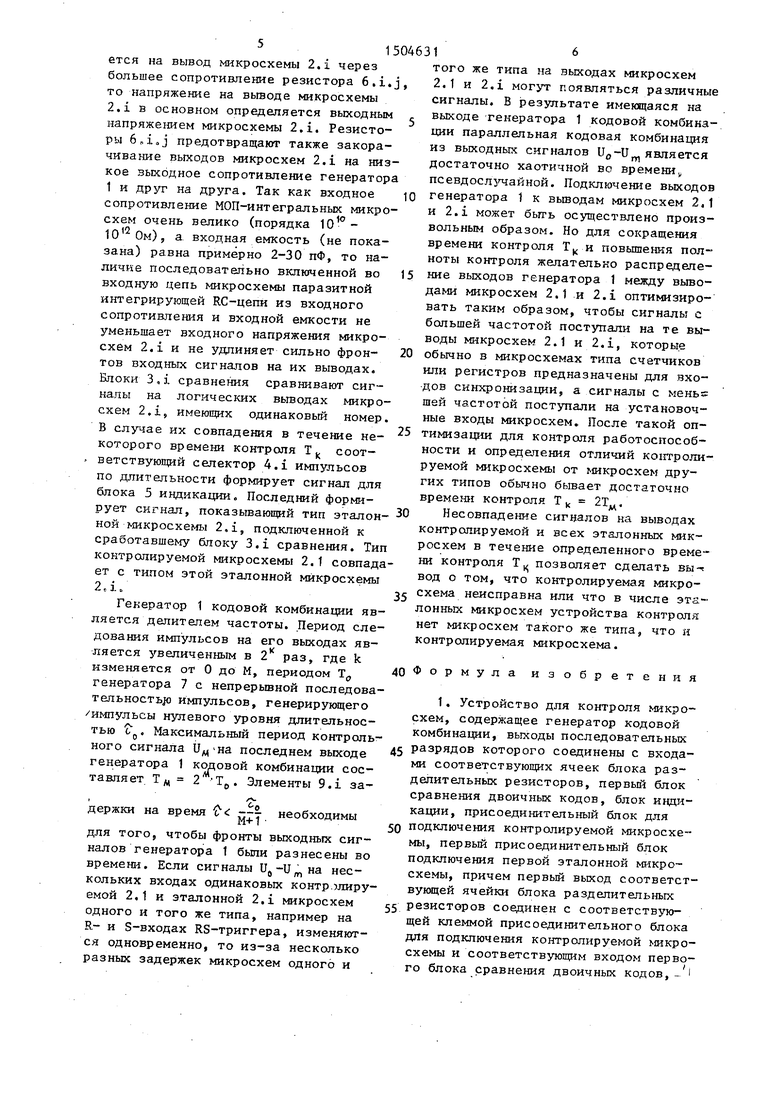

Селектор 4.1 импульсов по длительности (фиг. 3) в простейшем случае может состоять из порогового элемента 10, резистора 11, конденсатора 12 и диода 13«

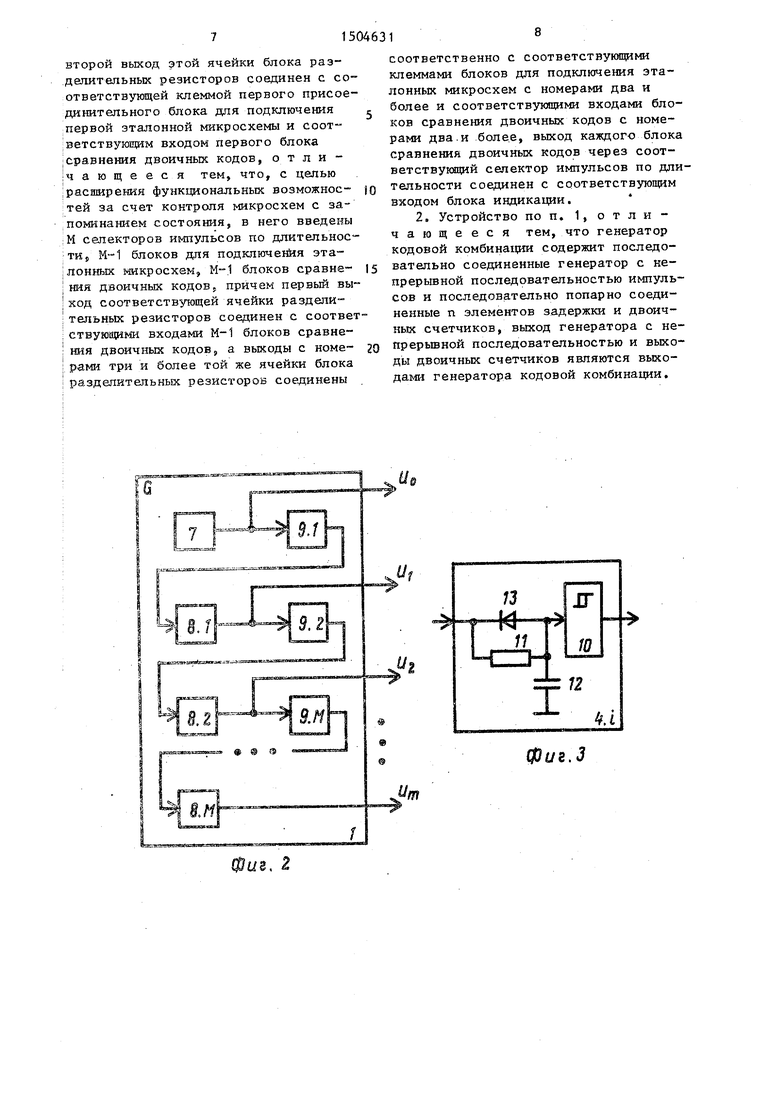

Эквивалентная электрическая схема выходной цепи генератора 1 кодовой комбинации, контролируемой 2.1 и эталонной 2.1 (,3,...,М) микросхем содержит резисторы 6.i.j ячеек блока 6 разделительных резисторов, источник 14,1-14.М+1,15 выходного импульсного напряжения, выходные резисторы 16.1- 16.М+1,17, входной резистора 18 контролируемой 2.1 (эталонной 2.1) микро- 1схем.

Устройство работает следующим образом.

Псевдослучайная кодовая комбинация в виде параллельного кода с генератора 1 кодовой комбинации через резисторы блока 6 поступает на М-И логических выводов контролируемой 2о1 и эталонных микросхем 2.2-2.М. Резисторы 6.i.j.6noKa 6 разделительных резисторов достаточно большой величины (10-100 кОм) предотвращают закорачивание выходов генератора 1 кодовой комбинации на низкое выходное сопротивление резистора 17 микросхем 2.1-2.М в сл.учае, если выходы генератора 1 кодовой комбинации оказались подключенными непосредственно к выходам микросхем 2,1. Напряжение на вьшоде микросхемы 2.1, если этот вывод являбтся выходом микросхемы , определяется суммарным воздействием источников выходного импульсного напряжения генератора 1 и микросхемы 2,1, имеющих примерно одинаковую величину, близкую к напряжению питания. Но так как напряжение с выхода микросхемы 2.1 подается на вывод через малое (100-1000 Ом) выходное сопротивление резистора 17, а напряжение с выхода генератора 1 подается на вывод микросхемы 2,1 через большее сопротивление резистора 6.i.j, то напряжение на вьшоде микросхемы 2.1 в основном определяется выходным напряжением микросхемы 2,1. Резисторы предотвращают также закорачивание выходов микросхем 2.1 на низкое выходное сопротивление генератора 1 и друг на друга. Так как входное ю сопротивление МОП-интегральных микросхем очень велико (порядка ), а входная емкость (не показана) равна примерно 2-30 пФ, то наличие последовательно включенной во 15 входную цепь микросхемы паразитной интегрирующей RC-цепи из входного сопротивления и входной емкости не уменьшает входного напряжения микросхем 2.1 и не удпиняет сильно фрон- 20 тов входных сигналов на их выводах. Блоки 3,3. сравнения сравнивают сигналы на логических вьшодах микросхем 2.ij имеющих одинаковый номер. В случае их совпадения в течение не- которого времени контроля Т соот- ветствующий селектор 4.1 импульсов по длительности формирует сигнал для блока 5 индика1щи. Последний формирует сигнал, показьгоающий тип эталон- ной микросхемы 2.i, подключенной к сработавшему блоку 3.1 сравнения. Тип контролируемой микросхемы 2.1 совпадает с типом этой эталонной микросхемы 2Л.35

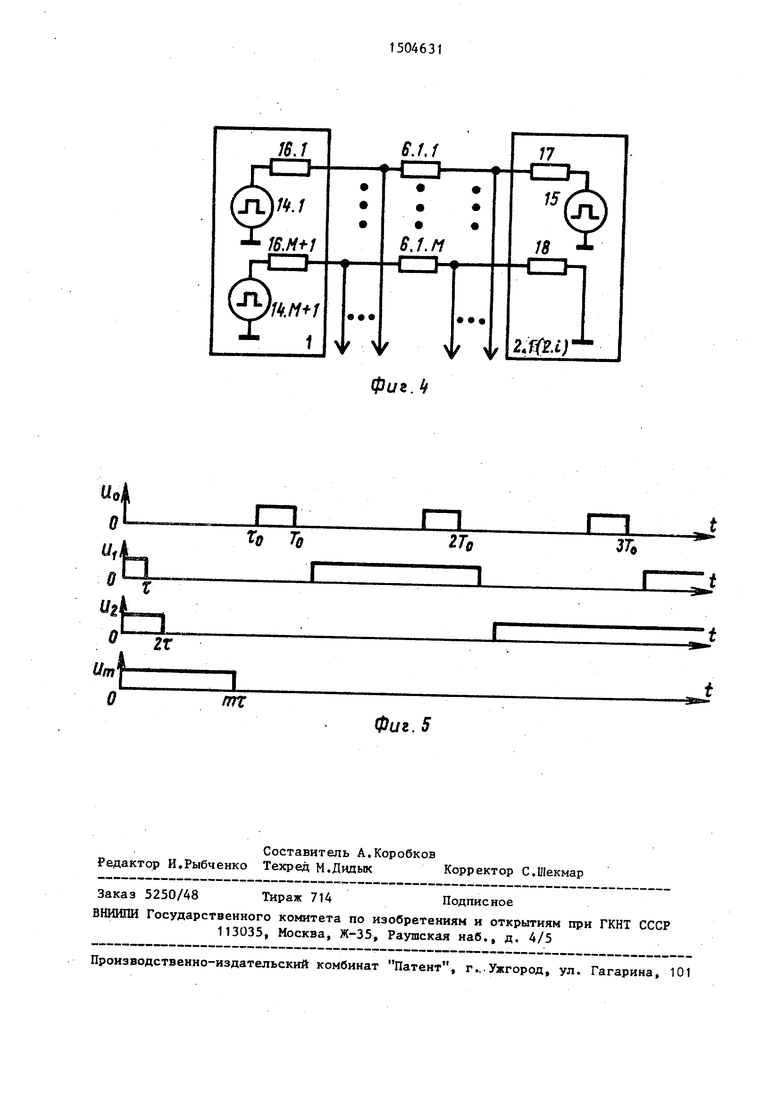

Гекератор 1 кодовой комбинации является делителем частоты. Период следования импульсов на его выходах является увеличенным в 2 раз, где k изменяется от О до М, периодом Т, генератора 7 с непрерьшной последова- тельность/о импульсов, генерирующего импульсы нулевого уровня длительностью р. Максимальный период контрольного сигнала последнем выходе генератора 1 кодовой комбинации составляет Т/ц 2 Т,,. Элементы 9.1 за40

д5

держки на время v , необходимы

М+1

для того, чтобы фронты выходных сигналов генератора 1 были разнесены во времени. Если сигналы нескольких входах одинаковых контр.5лиру- емой 2.1 и эталонной 2.1 микросхем одного и того же типа, например на R- и S-входах RS-триггера, изменяются одновременно, то из-за несколько разных задержек микросхем одного и

того же типа на выходах микросхем 2.1 и 2.1 могут появляться различные сигналы. В результате имегацаяся на выходе генератора 1 кодовой комбинации параллельная кодовая комбинация из выходных сигналов U(,-U является достаточно хаотичной во времени псевдослучайной. Подключение выходов генератора 1 к вьшодам микросхем 2,1 и 2.1 может бьп-ь осуществлено произвольным образом. Но для сокращения времени контроля Т и повьшзенкя полноты контроля желательно распределение выходов генератора 1 между выводами микросхем 2.1 и 2.1 оптимизировать таким образом, чтобы сигналы с большей частотой поступали на те выводы микросхем 2.1 и 2.1, которые обычно в микросхемах типа счетчиков или регистров предназначены для входов синхронизации, а сигналы с меньг шей частотой поступали на установочные входы микросхем После такой оптимизации для контроля работоспособности и определения отличий контролируемой микросхемы от микросхем других типов обычно бывает достаточно времени контроля Т 2Т.

Несовпадение сигналов на выводах контролируемой и всех эталонных микросхем в течение определенного времени контроля Т ц позволяет сделать вы- вод о том, что контролируемая микросхема неисправна или что в числе эталонных микросхем устройства контроля нет микросхем такого же типа, что и контролируемая микросхема.

40 Формула изобретения

1. Устройство для контроля микросхем, содержащее генератор кодовой комбинации, выходы последовательных

д5 разрядов которого соединены с входами соответствующих ячеек блока разделительных резисторов, первьй блок сравнения двоичных кодов, блок индикации, присоединительный блок для

50 подключения контролируемой микросхемы, первый присоединительный блок подключения первой эталонной микросхемы, причем первый выход соответствующей ячейки блока разделительных резисторов соединен с соответствующей клеммой присоединительного блока для подключения контролируемой микросхемы и соответствующим входом первого блока сравнения двоичных кодов, -

55

второй выход этой ячейки блока разделительных резисторов соединен с соответствующей клеммой первого присоединительного блока для подключения первой эталонной микросхемы и соот- ;ветствую1цим входом первого блока ;сравнения двоичных кодов, о т л и - |чающееся тем, что, с целью расширения функциональных возможное- :тей за счет контроля микросхем с запоминанием состояния, в него введены ;М селекторов импульсов по длительнос- -ти, М-1 блоков для подключения эта- 1 лонных микросхем, М-1 блоков сравне- iния двоичных кодов5 причем первый вы- I код соответствующей ячейки раздели- ; тельных резисторов соединен с соответ : ствующими входами М-1 блоков сравне- : ния двоичных КОДОВj а выходы с номе- рами три и более той же ячейки блока разделительных резисторов соединены

соответственно с соответствующими клеммами блоков для подключения эталонных микросхем с номерами два и более и соответствующими входами блоков сравнения двоичных кодов с номерами два.и боле,е, выход каждого блока сравнения двоичных кодов через соот- ветствукяций селектор импульсов по длительности соединен с соответствующим входом блока индикации.

2. Устройство по п. 1, о т л и - чающееся тем, что генератор кодовой комбинации содержит последовательно соединенные генератор с непрерывной последовательностью импульсов и последовательно попарно соединенные п элементов задержки и двоичных счетчиков, выход генератора с не- прерьшной последовательностью и выходы двоичных счетчиков являются выходами генератора кодовой комбинации.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для контроля КМОП-логических схем | 1987 |

|

SU1552137A1 |

| ВОЛОКОННО-ОПТИЧЕСКАЯ СИСТЕМА С БЕЗОПАСНОЙ ПЕРЕДАЧЕЙ ИНФОРМАЦИИ | 1995 |

|

RU2100906C1 |

| Устройство для контроля логических блоков | 1984 |

|

SU1367015A1 |

| УСТРОЙСТВО УПРАВЛЕНИЯ ЭЛЕКТРОННЫМ КОДОВЫМ ЗАМКОМ | 2001 |

|

RU2195541C1 |

| СИСТЕМА АВТОМАТИЗИРОВАННОГО КОНТРОЛЯ | 1991 |

|

RU2006896C1 |

| Устройство для контроля логических микросхем | 1982 |

|

SU1026096A1 |

| УСТРОЙСТВО УПРАВЛЕНИЯ КОДОВЫМ ЗАМКОМ | 2001 |

|

RU2191878C1 |

| СПОСОБ ОЦЕНКИ КАЧЕСТВА КАНАЛА ПЕРЕДАЧИ ДАННЫХ И УСТРОЙСТВО ДЛЯ ЕГО ОСУЩЕСТВЛЕНИЯ | 1995 |

|

RU2085045C1 |

| Устройство для контроля цифровых объектов | 1986 |

|

SU1319037A2 |

| ОХРАННОЕ КОДОВОЕ УСТРОЙСТВО | 1990 |

|

SU1834548A1 |

Изобретение относится к электроизмерительной технике и может быть использовано для контроля работоспособности и определения типа цифровых МОП интегральных микросхем при производстве радиоэлектронной аппаратуры. Цель изобретения - расширение функциональных возможностей - достигается путем контроля микросхем с запоминанием состояния. Устройство содержит генератор 1 кодовой комбинации, присоединительный блок (ПБ) 2.2-2.1 для подключения контролируемой микросхемы, ПБ 2.2-2.М для подключения эталонных микросхем, блоки 3.1-3.М-1 сравнения двоичных кодов, селекторы 4.1-4.М-1 импульсов по длительности, блок 5 индикации, блок 6 разделительных резисторов. При работе устройства неисправность контролируемой микросхемы определяется по несовпадению сигналов на выводах контролируемой и всех эталонных микросхем. 1 з.п. ф-лы, 5 ил.

ю

«

li,L

Фиг,3

ПМ+1

B.lf

B.f./i

f

2j{.L)

фui.ff

Фиг. 5

| Устройство для автоматического контроля интегральных схем | 1978 |

|

SU767674A1 |

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Авторское свидетельство СССР 1150590, кл | |||

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

Авторы

Даты

1989-08-30—Публикация

1986-04-29—Подача